Intersil Corporation HIP5061 Datasheet

April 1994

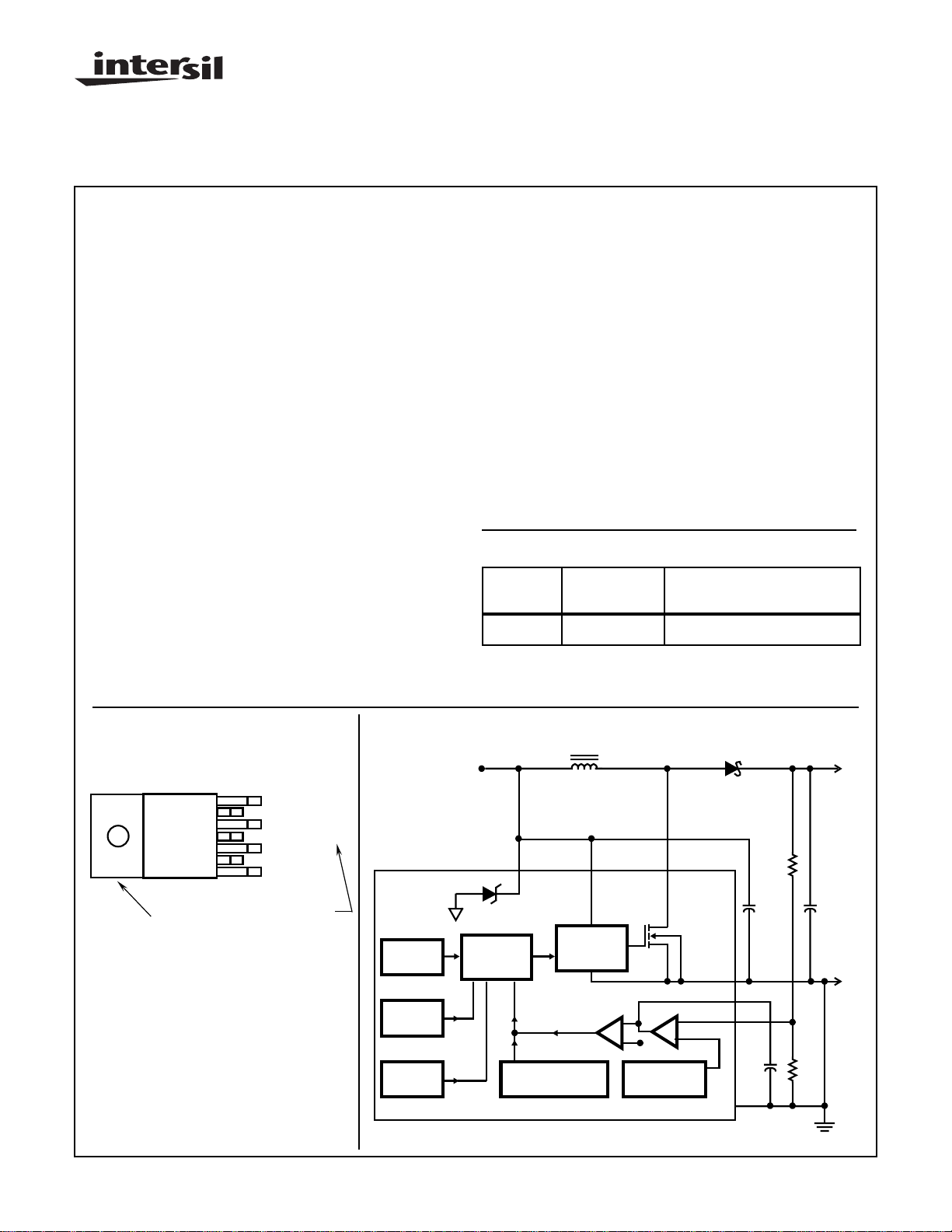

HIP5061

7A, High Efficiency Current

Mode Controlled PWM Regulator

Features

• Single Chip Current Mode Control IC

• 60V, On-Chip DMOS Power Transistor

• Thermal Protection

• Over-Current Protection

• 250kHz Operation

• Output Rise and Fall Times - 10ns

• On-Chip Reference Voltage - 5.1V

• Slope Compensation

Clamp Allows 10.8V to 60V Supply

•V

DD

• Supply Current Does Not Increase When Power

Device is On

Applications

• Distributed / Board Mounted Power Supplies

• DC - DC Converter Modules

• Voltage Inverters

• Small Uninterruptable Power Supplies

Description

The HIP5061 is a complete power control IC, incorporating

both the high power DMOS transistor, CMOS logic and low

level analog circuitry on the same Intelligent Power IC. The

standard “Boost”, “Buck-Boost”, “Cuk”, “Forward”, “Flyback”

and the “SEPIC” (Single-Ended Primary Inductance Converter) power supply topologies may be implemented with

this single control IC.

Over-temperature and rapid short-circuit recovery circuitry is

incorporated within the IC. These protection circuits disable

the drive to the power transistor to protect the transistor and

insure rapid restarting of the supply after the short circuit is

removed.

As a result of the power DMOS transistors current (7A at 30%

duty cycle, 5A DC) and 60V capability, supplies with output

power over 50W are possible.

Ordering Information

PART

NUMBER

HIP5061DS 0oC to +85oC 7 Lead Staggered “Gullwing” SIP

TEMPERATURE

RANGE PACKAGE

• Cascode Switching for Off Line SMPS

Pinout

HIP5061 (SIP)

TOP VIEW

PIN 7 V

DD

PIN 6 V

G

PIN 5 DRAIN

PIN 4 SOURCE

PIN 3 FB

PIN 2 V

C

PIN 1 GND

DO NOT

SOURCE

(TAB)

USE

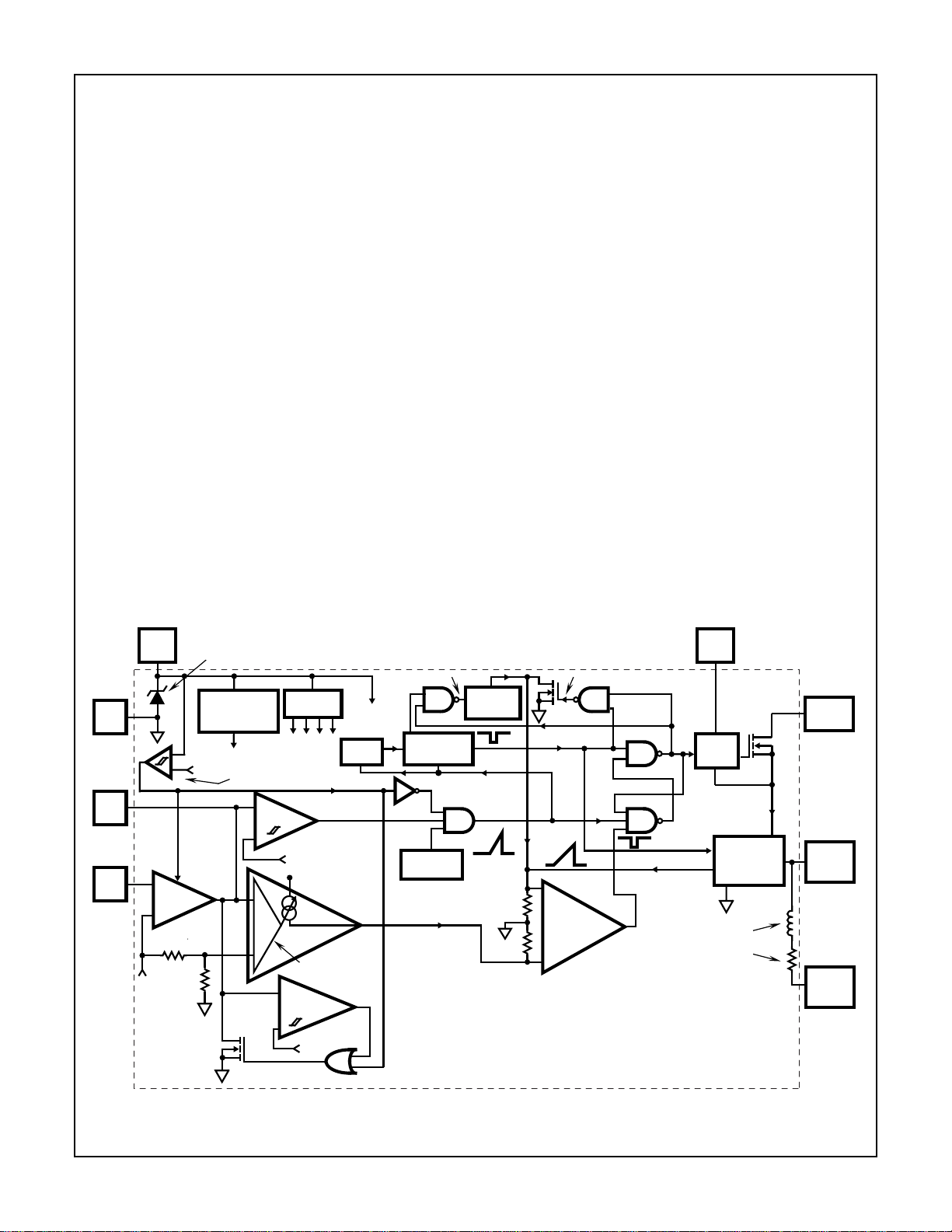

Simplified Functional Diagram

V

IN

V

HIP5061

CLOCK

OVER

TEMP

UNDER

VOLTAGE

VDD CLAMP

CONTROL

LOGIC

COMPENSATION

DD

SLOPE

GATE

DRIVER

V/I

G

DRAINV

AMP

2.5V

5.1V

REFERENCE

SOURCE

(TAB)

V

C

FB

GND

V

OUT

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

407-727-9207

| Copyright © Intersil Corporation 1999

7-53

File Number

3390.2

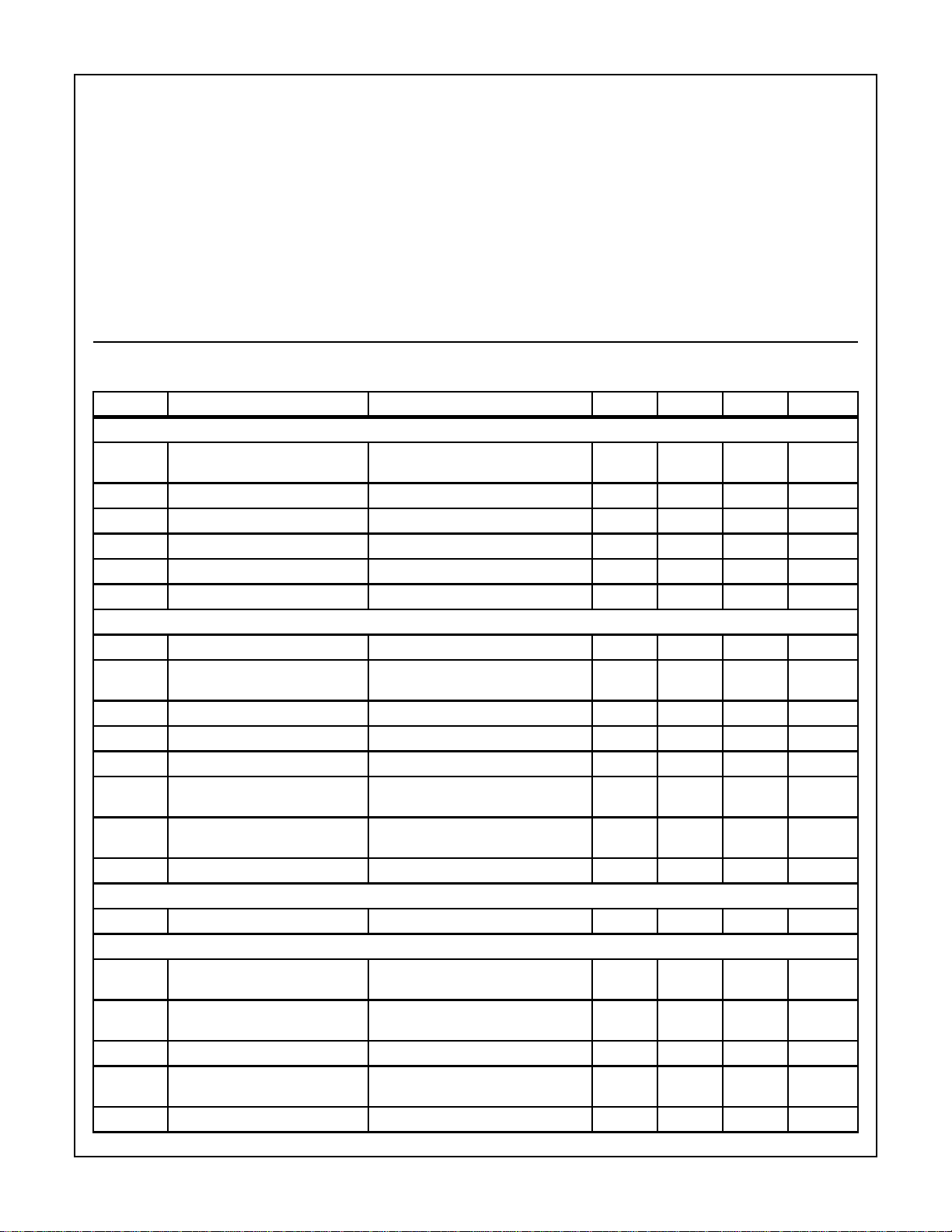

Specifications HIP5061

Absolute Maximum Ratings (Note 1) Thermal Information

DC Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 16V

DC Supply Current, IDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105mA

DMOS Drain Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 60V

Average DMOS Drain Current . . . . . . . . . . . . . . . . . . . . . . . . . . . 5A

DMOS Source Voltage, V

, TAB . . . . . . . . . . . . -0.1V to 0.1V

SOURCE

DC Supply Voltage, VG. . . . . . . . . . . . . . . . . . . .-0.3V to VDD + 0.3V

Compensation Pin Current, IVC . . . . . . . . . . . . . . . . . -5mA to 35mA

Voltage at All Other Pins. . . . . . . . . . . . . . . . . . .-0.3V to VDD + 0.3V

Operating Junction Temperature Range. . . . . . . . . . .0oC to +105oC

Storage Temperature Range . . . . . . . . . . . . . . . . . -55oC to +150oC

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 2 - 2KV

Single Pulse Avalanche Energy Rating, µs (Note 2) . . . EAS 100mJ

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Thermal Resistance θ

JC

Plastic SIP Package . . . . . . . . . . . . . . . . . . . . . . . . 2oC/W

Maximum Package Power Dissipation at +85oC

(Depends Upon Mounting, Heat Sink and Application). . . . . 10W

Max. Junction Temperature. . . . . . . . . . . . . . . . . . . . . . . . . .+105oC

(Controlled By Thermal Shutdown Circuit)

Lead Temperature (Soldering 10s) . . . . . . . . . . . . . . . . . . . . +265oC

Electrical Specifications V

= VG =12V, VC = 5V, VFB = 5.1V, SOURCE = GND = DRAIN = 0V, TJ = 0oC to +105oC,

DD

Unless Otherwise Specified

SYMBOL PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

DEVICE PARAMETERS

I

DD

Quiescent Supply Current VDD = VG = 13.2V, VC = 0V,

61218mA

VFB = 4V

V

V

I

DD

IV

IV

DDC

REF

Operating Supply Current VDD = VG = 13.2V, VC = 8.5V, VFB = 4V - 24 31 mA

Quiescent Current to Gate Driver VDD = VG = 13.2V, VC = 0V - 0 10 µA

G

Operating Current to Gate Driver VC = 3V - 1 2 mA

G

Clamp Voltage IDD = 100mA 13.3 14 15 V

Reference Voltage IVC = 0µA, VC = V

FB

5.0 5.1 5.2 V

AMPLIFIERS

|IFB| Input Current VFB = V

(VFB)VFB Transconductance

g

m

IV

IV

V

CMAX

CMAX

A

OL

CMAX

IVC/(VFB - V

REF

Maximum Source Current VFB = 4.6V -4 -1.8 -1 mA

Maximum Sink Current VFB = 5.6V 1 1.8 4 mA

Voltage Gain /IVC / = 500µA, Note 3 44 50 - dB

Short Circuit Recovery Compara-

)

/IVC / = 500µA, Note 3 20 30 43 mS

REF

- -0.85 0.5 µA

5.4 6.6 8.9 V

tor Rising Threshold Voltage

V

CHYS

Short Circuit Recovery

0.7 1.1 1.8 V

Comparator Hysteresis Voltage

IVC

OVERVC

Over-Voltage Current VDD = VG = 10.8V, VC = V

CMAX

01025mA

CLOCK

fq Internal Clock Frequency 210 250 290 kHz

DMOS TRANSISTOR

r

DS

(ON)

r

DS

(ON)

I

DSS

I

DSH

Drain-Source On-State

Resistance

Drain-Source On-State

Resistance

Drain-Source Leakage Current V

Average Drain Short Circuit

I

= 5A, VDD = VG = 10.8V

DRAIN

- 0.15 0.22 Ω

TJ = +25oC

I

= 5A, VDD = VG = 10.8V

DRAIN

- - 0.33 Ω

TJ = +105oC

= 60V - 0.5 10 µA

DRAIN

V

= 5V, Note 4 - - 5 A

DRAIN

Current

C

DRAIN

DRAIN Capacitance Note 4 - 200 - pF

7-54

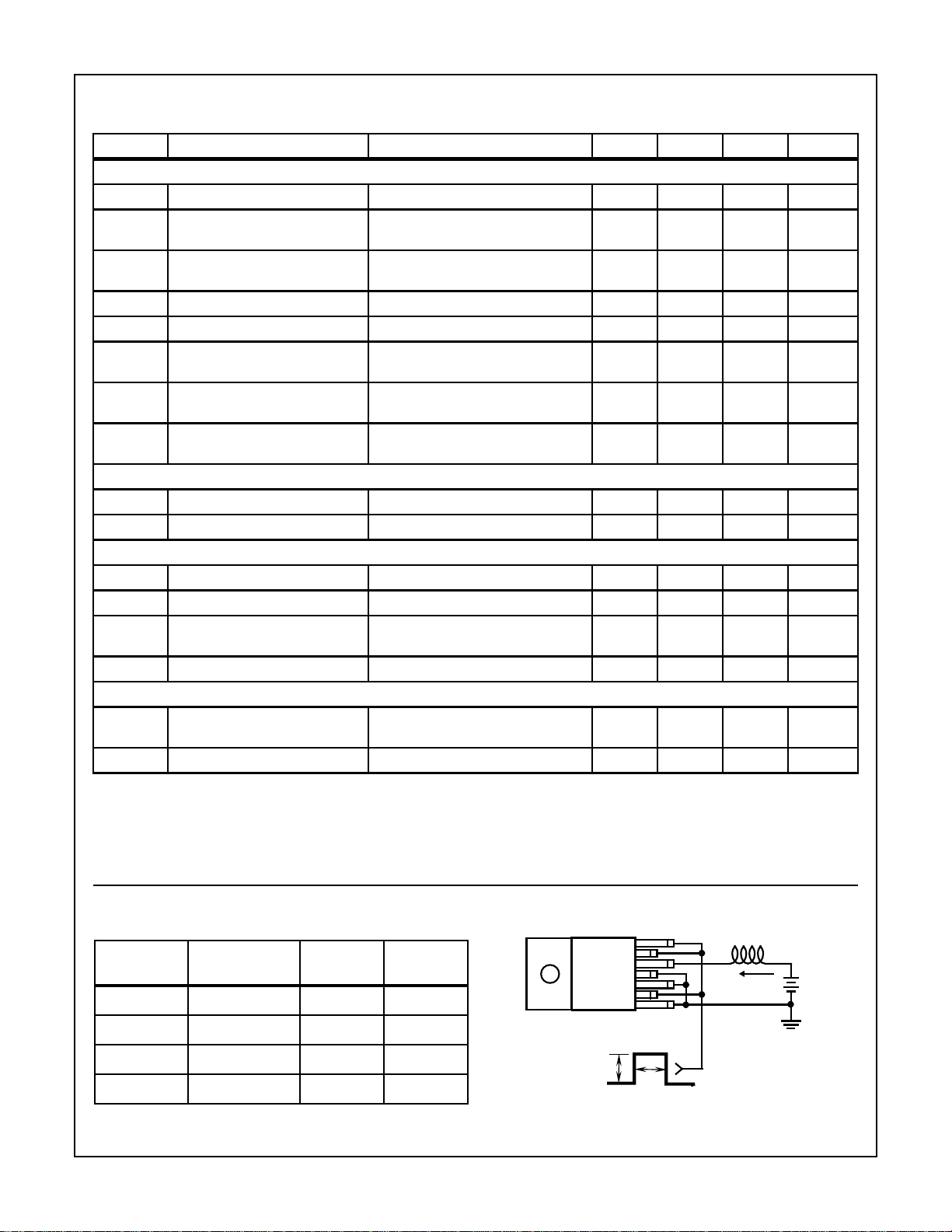

Specifications HIP5061

Electrical Specifications V

= VG =12V, VC = 5V, VFB = 5.1V, SOURCE = GND = DRAIN = 0V, TJ = 0oC to +105oC,

DD

Unless Otherwise Specified (Continued)

SYMBOL PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

CURRENT CONTROLLED PWM

g

m(VC

V/I

REF

) ∆I

DRAIN, PEAK

Voltage to Current Converter Ref-

/∆V

C

Note 3 1.4 2.2 3.0 A/V

I

= 0.25A, Note 3 2.4 2.8 3.1 V

DRAIN

erence Voltage

t

BT

Current Comparator Blanking

Note 3 40 100 175 ns

Time

t

ONMIN

t

OFFMIN

MinCI Minimum Controllable DMOS

Minimum DMOS “ON” Time Note 3 60 150 250 ns

Minimum DMOS “OFF” Time Note 3 40 125 200 ns

Note 3 - 100 250 mA

Peak Current

MaxCI Maximum Controllable DMOS

Duty Cycle = 6% to 30%, Note 3 7 9.5 12 A

Peak Current

MaxCI Maximum Controllable DMOS

Duty Cycle = 30% to 96%, Note 3 5 8 12 A

Peak Current

CURRENT COMPENSATION RAMP

∆I/∆t Compensation Ramp Rate ∆I

t

RD

Compensation Ramp Delay Note 3 1.3 1.5 1.8 µs

DRAIN, PEAK

/∆Time, Note 3 -1.4 -0.85 -0.45 A/µs

START-UP

V

DDMIN

V

DDHYS

V

CEN

Rising VDD Threshold Voltage VFB = 4V 9.3 10.3 10.8 V

Power-On Hysteresis VFB = 4V 0.3 0.45 0.6 V

Enable Comparator Threshold

1.0 1.5 2.0 V

Voltage

R

VC

Power-Up Resistance 4V < VDD < 10.8V, VC = 0.8V 50 500 3000 Ω

THERMAL MONITOR

T

Substrate Temperature for

J

Note 4 105 - 145

Thermal Monitor to Trip

T

JHY

Temperature Hysteresis Note 4 - 5 -

NOTES:

1. All Voltages relative to pin 1, GND.

= 10V, Starting TJ = +25oC, L = 4mH, I

2. V

D

PEAK

= 7A.

3. Test is performed at wafer level only.

4. Determined by design, not a measured parameter.

o

C

o

C

TABLE 1. CONDITIONS FOR UNCLAMPED ENERGY CIRCUIT

I

VD(V)

L

(PEAK AMPS) L (mH) EAS (mJ)

10 5 40 550

10 7 4TZ 120

6 10 0.33 18

6 12.5 0.14 12

NOTE: Device Selected to Obtain Peak Current without Clocking

7-55

7

HIP5061

VARY tP TO OBTAIN

REQUIRED PEAK I

12V

1

t

P

L

L

+

I

L

V

-

FIGURE 1. UNCLAMPED ENERGY TEST CIRCUIT

D

HIP5061

Definitions of Electrical Specifications

Refer to the Functional Block Diagram of Figure 1 for locations of functional blocks and devices.

Device Parameters

IDD, Quiescent Supply Current - Supply current with the

chip disabled. The Clock, Error Amplifier, Voltage-to-Current

Converter, and Current Ramp circuits draw only quiescent

current. The supply voltage must be kept lower than the

turn-on voltage of the V

increases dramatically.

I

, Operating Supply Current - Supply current with the

DD

chip enabled. The Error Amplifier is drawing its maximum

current because V

FB

voltage-to-current amplifier is drawing its maximum because

V

is at its maximum. The ramp circuit is drawing its maxi-

C

mum because it is not being disabled by the DMOS transistor turning off.

IV

, Quiescent Gate Driver Current - Gate Drivers supply

G

current with the IC disabled. The Gate Driver is not toggling

and so it draws only leakage current.

IV

, Operating Gate Driver Current - Gate Drivers supply

G

current with the IC enabled. The DMOS transistor drain is

loaded with a large resistor tied to 60V so that it is swinging

from 0V to 60V during each cycle.

V

, VDD Clamp - VDD voltage at the maximum allowed

DDC

current through the V

, Reference Voltage - The voltage on FB that sets the

V

REF

current on V

to zero. This is the reference voltage for the

C

DC/DC converter.

Amplifiers

|IFB|, Input Current - Current through FB pin when it is at its

normal operating voltage. This current must be considered

when connecting the output of a DC/DC convertor to the FB

pin via a resistor divider.

g

through the V

The g

), Transconductance - The change in current

m(VFB

times the resistance between VC and ground gives

m

pin divided by the change in voltage on FB.

C

the voltage gain of the Error Amplifier.

IV

, Maximum Source Current - The current on V

CMAX

when FB is more than a few hundred millivolts less than

V

.

REF

IV

, Maximum Sink Current - The current on VC when

CMAX

FB is more than a few hundred millivolts more than V

, Voltage Gain - Change in the voltage on VC divided by

A

OL

the change in voltage on FB. There is no resistive load on

V

. This is the voltage gain of the error amplifier when g

C

times load resistance is larger than this gain.

, VC Rising Threshold - The voltage on VC that

V

CMAX

causes the Voltage-to-Current Amplifier to reach full-scale.

When V

reaches this voltage, the VC NMOS transistor (tran-

C

sistor with its drain connected to the V

Block Diagram of Figure 2) turns on and tries to lower the voltage on V

.

C

clamp or else the supply current

DD

is less than its reference voltage. The

Clamp.

DD

.

REF

pin in the Functional

C

V

CHYS,VCMAX

Hysteresis - The voltage on VC that causes

the NMOS transistor to turnoff if it had been turned on by V

exceeding V

. At this voltage the current out of the Voltage-

CMAX

to-Current Converter is at roughly three quarters of full-scale.

IVC

OVER,VC

through the V

due to excessive voltage on V

nected to the V

Over-Voltage Current - The current drawn

pin after the NMOS transistor is turned on

C

pin draws more than enough current to

C

. The NMOS transistor con-

C

overcome the full scale source current of the Error Amplifier.

Clock

fq, Frequency - The frequency of the DC/DC converter. The

Clock actually runs faster than this value so that various control signals can be internally generated.

DMOS Transistor

r

, “On” Resistance - Resistance from DMOS transis-

DS(ON)

tor Drain to Source at maximum drain current and minimum

Gate Driver voltage, V

, Leakage Current - Current through DMOS transistor

I

DSS

.

G

at the Maximum Rated Voltage.

Current Controlled PWM

gm(VC), Transconductance - The change in the DMOS tran-

sistor peak drain current divided by the change in voltage on

V

. When analyzing DC/DC converters the DMOS transistor

C

and the inductor tied to the drain are sometimes modelled as

a voltage-controlled current source and this parameter is the

gain of the voltage-controlled current source.

V/I

, Current Control Threshold - The voltage on V

REF

that causes the DMOS transistor to shut off at the minimum

controllable current. This voltage is greater than the Enable

Comparator Threshold (V

) so that as VC rises the IC

CEN

does not jump from the disabled state to the DMOS transistor conducting a large current.

t

, Blanking Time - At the beginning of each cycle there is

BT

a blanking time that the DMOS transistor turns-on and stayson no matter how high drain the current. This blanking time

permits ringing in the external parasitic capacitances and

inductances to dampen and for the charging of the reverse

bias on the rectifier diode.

t

, Minimum DMOS Transistor “On” Time - The mini-

ONMIN

mum on-time for the DMOS transistor where small changes

C

in the V

voltage make predictable changes in the DMOS

C

transistor peak current. Converters should be designed to

avoid requiring pulse widths less than the minimum on time.

t

, Minimum DMOS Transistor “Off” Time - The min-

OFFMIN

imum off-time for the DMOS transistor that allows enough time

for the IC to get ready for the next cycle. Converters should be

designed to avoid requiring pulse widths so large that the mini-

m

mum off time is violated. (However, zero of f time is allowed, that

is, the DMOS transistor can stay on from one cycle to the next.)

MinCI , Minimum Controllable Current - When the voltage

on V

is below V/I

C

, the peak current for the DMOS tran-

REF

sistor is too small for the Current Comparator to operate reliably. Converters should be designed to avoid operating the

DMOS transistor at this low current.

C

C

7-56

HIP5061

MaxCI, Maximum Controllable Current - The peak current

for the DMOS transistor when the Voltage-to-Current Converter is at its full scale output. The DMOS transistor current

may exceed this value during the blanking time so proper

precautions should be taken. This parameter is unchanged

for the first 3/8 of the cycle and then decreases linearly with

time because of the Current Ramp becoming active.

Current Compensation Ramp

∆I/∆t, Compensation Ramp Rate - At a given voltage on V

the DMOS transistor will turn off at some current that stays

constant for about the first 1.5µs of the cycle. After 1.5µs, the

turnoff current starts to linearly decrease. This parameter

specifies the change in the DMOS transistor turnoff current.

t

, Compensation Ramp Delay - The time into each cycle

RD

that the compensation ramp turns on. The Current Compensation Ramp, used for Slope Compensation, is developed by

the Current Ramp block shown in the FUNCTIONAL BLOCK

DIAGRAM of Figure 2.

Start-Up

V

voltage on V

V

between the voltage on V

, Rising VDD Threshold Voltage - The minimum

DDMIN

DDHYS

needed to enable the IC.

DD

, Power - On Hysteresis Voltage - The difference

that enables the IC and the volt-

DD

age that disables the IC.

V

, Enable Comparator Threshold Voltage - The mini-

CEN

mum voltage on V

needed to enable the IC. The IC can be

C

shutdown from an open-collector logic gate by pulling down

the V

pin to GND.

C

, Power - Up Resistance - When VDD is below V

R

VC

the NMOS transistor connected to the V

make sure the V

node is low. Thus the voltage on VC can

C

pin is turned on to

C

gradually build up as will the trip current on the DMOS transistor. This is the only form of “soft start” included on the IC.

C

The resistance is measured between the V

and GND pins.

C

Thermal Monitor

, Rising Temperature Threshold - The IC temperature

T

J

that causes the IC to disable itself so as to prevent damage.

Proper heat-sinking is required to avoid over-temperature

conditions, especially during start-up when the DMOS transistor may stay on for a long time if an external soft-start circuit is not added.

T

, Temperature Hysteresis - The IC must cool down

JHY

this much after it is disabled by being too hot before it can

resume normal operation.

DDMIN

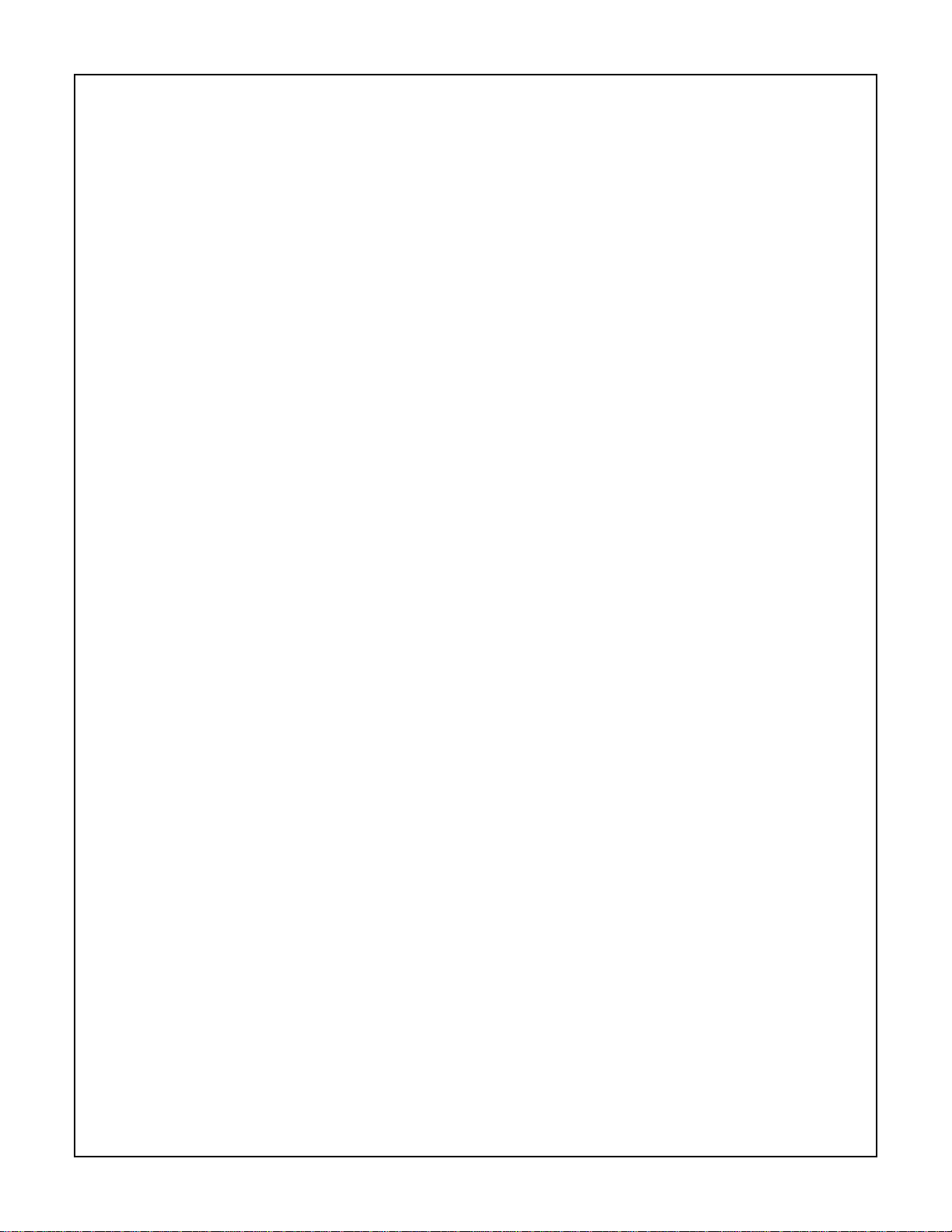

,

GND

1

V

2

FB

3

V

DD

7

C

ERROR

+

5.1V

V

REF

-

+

AMP

2KΩ

10.3V

ERROR

AMP

DISABLE

2KΩ

V

DD

CLAMP

BAND GAP

REFERENCE

REGULATOR

V

= 5.1V

REF

MONITOR

V

DD

+

+

ENABLE

-

-

+

SHORT

CIRCUIT

-

CIRCUITS

1.5V

BIAS

V

CLOCK

UNDER VOLTAGE

LOCK OUT

VOLTAGE TO

V

DD

CURRENT

CONVERTER

LIGHT LOAD

COMPARATOR

7.0V

RAMP ENABLE

DD

CONTROL

LOGIC

THERMAL

MONITOR

ERROR CURRENT

CURRENT

RAMP

ENABLE

360Ω

360Ω

-

CURRENT

COMPARE

+

HIP5061

RAMP RESET

100ns

BLANKING

CURRENT SAMPLE

AND RESISTANCE

V

G

6

GATE

DRIVER

CURRENT

MONITORING

INTERNAL LEAD

INDUCTANCE

DRAIN

5

TAB

SOURCE

SOURCE

4

FIGURE 2. FUNCTIONAL BLOCK DIAGRAM OF THE HIP5061

7-57

HIP5061

Pin Description

TERMINAL

NUMBER DESIGNATION DESCRIPTION

1 GND This is the analog ground terminal of the IC.

2V

C

3 FB Feedback from the regulator output is applied to this terminal. This terminal is the input to

4 SOURCE The terminal, labeled TAB, has a connection to this terminal, but because of the long lead

5 DRAIN Connection to the Drain of the internal power DMOS transistor is made at this terminal.

6V

7V

G

DD

TAB SOURCE This is the internal power DMOS transistor Source terminal. It should be used as the

For more information refer to Application Notes AN9208, AN9212, AN9323.

The output of the transconductance amplifier appears at this terminal. Input to the internal

voltage to current converter also appears at this node. Transconductance amplifier gain

and loop response are set at this terminal. When the VDD terminal voltage is below the

starting voltage, V

exceeds V

I

VCOVER

, 7V typical, implying an over-current condition, a typical 10mA current,

CMAX

pulls this terminal towards ground. This current remains “ON” until the voltage on

the VC terminal falls by V

, this terminal is held low. When the voltage at this terminal

DDMIN

, typically 1.1V , below the upper threshold, V

CHYS

voltage on this terminal falls below V

the transconductance amplifier. The amplifier compares the internal 5.1V reference and

the feedback signal from the regulator output.

length and resulting high inductance of this terminal, it should not be used as a means of

bypassing. Therefore, this terminal is labeled “Do Not Use.”

Gate drive supply voltage is provided at this terminal. A 10Ω to 150Ω resistor connected

between this terminal and the VDD terminal provides decoupling and the supply voltage

for the gate drivers.

External supply input to the IC. A nominal 14V shunt regulator is connected between this

terminal and the TAB. A series resistor should be connected to this terminal from the

external voltage source to supply a minimum current of 33mA and a maximum current of

105mA under the worst cast supply voltage. The series resistor is not required if the

supply voltage is 12V, ±10%.

ground return for the VDD bypass capacitor. In addition high frequency bypassing for both

the regulator output load voltage and supply input voltage should be returned to this

terminal.

, typically 1.5V, the IC is disabled.

CEN

CMAX

.When the

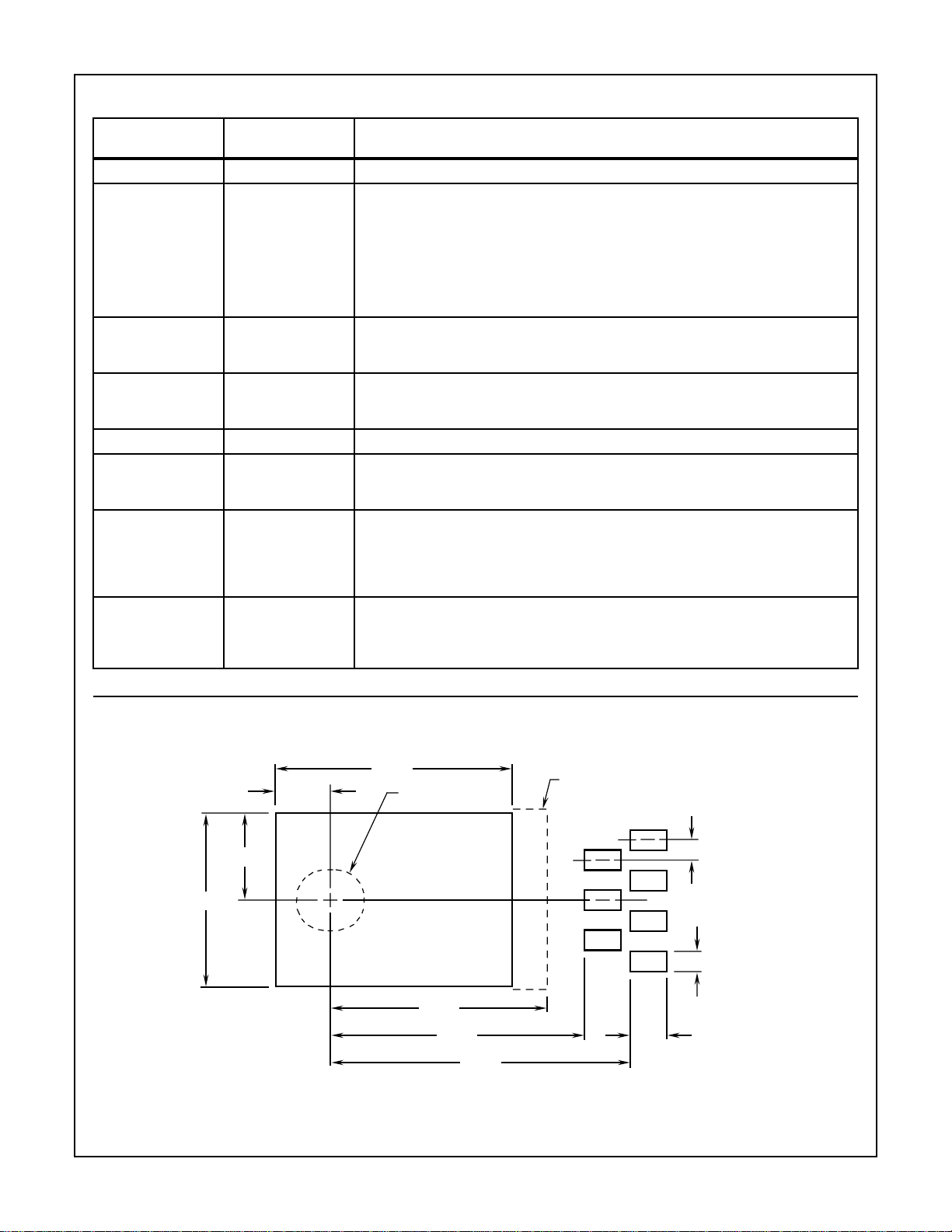

Foot Print For Soldering

0.120

0.212

0.424

0.523

OPTIONAL Ø 0.151

0.480

0.575

0.675

LIMIT OF SOLDER MASK

FOR HEADER

TO-220 STAGGERED GULL WING SIP

0.050 TYP

0.050 TYP

0.080 TYP

7-58

Loading...

Loading...