intersil HIP2100 DATA SHEET

®

www.BDTIC.com/Intersil

HIP2100

Data Sheet October 21, 2004 FN4022.13

100V/2A Peak, Low Cost, High Frequency

Half Bridge Driver

The HIP2100 is a high frequency, 100V Half Bridge

N-Channel power MOSFET driver IC. The low-side and

high-side gate drivers are independently controlled and

matched to 8ns. This gives the user maximum flexibility in

dead-time selection and driver protocol. Undervoltage

protection on both the low-side and high-side supplies force

the outputs low. An on-chip diode eliminates the discrete

diode required with other driver ICs. A new level-shifter

topology yields the low-power benefits of pulsed operation

with the safety of DC operation. Unlike some competitors,

the high-side output returns to its correct state after a

momentary undervoltage of the high-side supply.

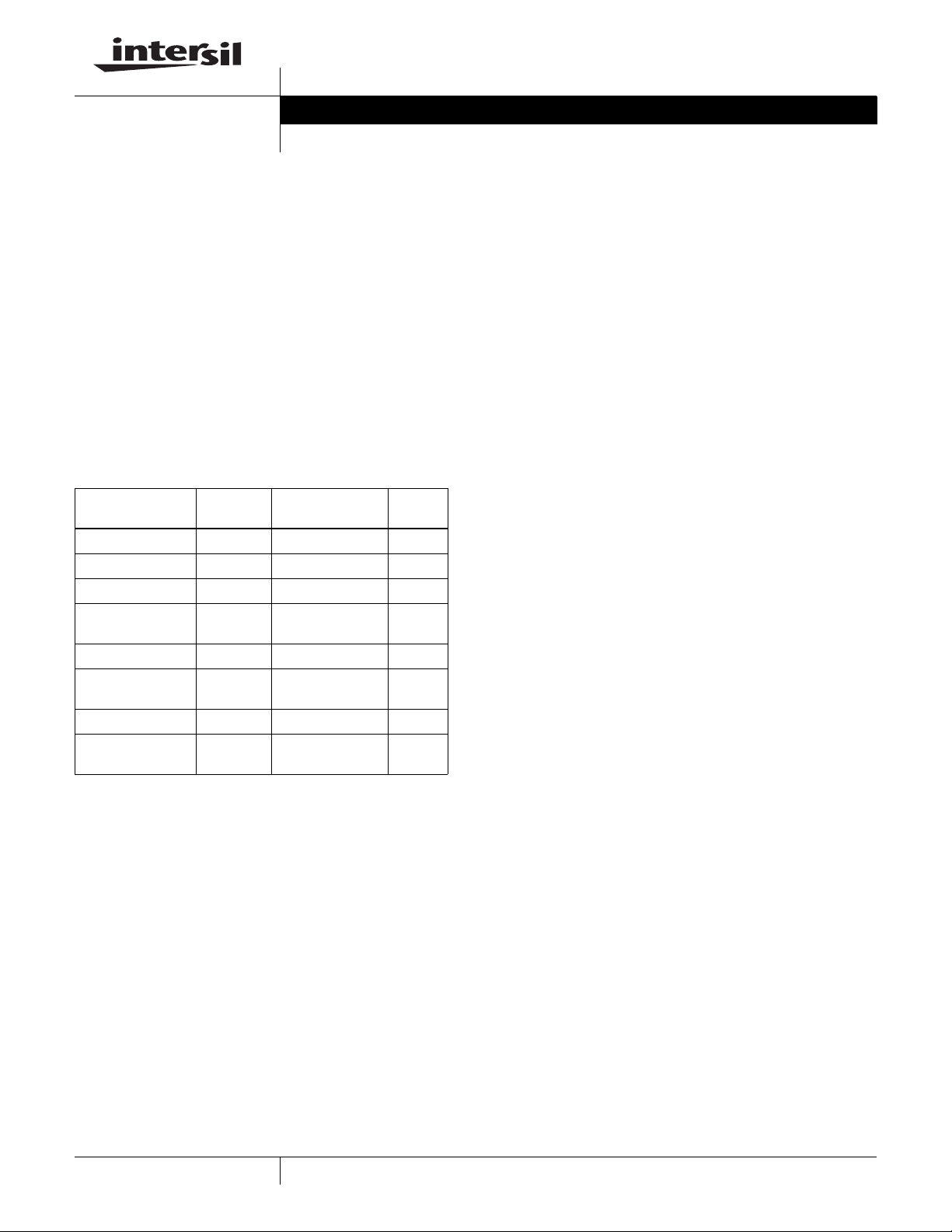

Ordering Information

PART #

HIP2100IB -40 to 125 8 Ld SOIC M8.15

HIP2100IBZ (Note 1) -40 to 125 8 Ld SOIC (Pb-free) M8.15

HIP2100EIB -40 to 125 8 Ld EPSOIC M8.15C

HIP2100EIBZ

(Note 1)

HIP2100IR -40 to 125 16 Ld 5x5 QFN L16.5x5

HIP2100IRZ (Note 1) -40 to 125 16 Ld 5x5 QFN

HIP2100IR4 -40 to 125 12 Ld 4x4 DFN L12.4x4A

HIP2100IR4Z

(Note 1)

NOTES:

1. Intersil Pb-free products employ special Pb-free material sets;

molding compounds/die attach materials and 100% matte tin

plate termination finish, which are RoHS compliant and

compatible with both SnPb and Pb-free soldering operations.

Intersil Pb-free products are MSL classified at Pb-free peak

reflow temperatures that meet or exceed the Pb-free

requirements of IPC/JEDEC J STD-020C.

2. Add “T” suffix for Tape and Reel packing option.

TEMP.

RANGE (°C) PACKAGE

-40 to 125 8 Ld EPSOIC

(Pb-free)

(Pb-free)

-40 to 125 12 Ld 4x4 DFN

(Pb-free)

PKG.

DWG. #

M8.15C

L16.5x5

L12.4x4A

Features

• Drives N-Channel MOSFET Half Bridge

• SOIC, EPSOIC, QFN and DFN Package Options

• SOIC, EPSOIC and DFN Packages Compliant with 100V

Conductor Spacing Guidelines of IPC-2221

• Pb-Free Product Available (RoHS Compliant)

• Bootstrap Supply Max Voltage to 114VDC

• On-Chip 1Ω Bootstrap Diode

• Fast Propagation Times for Multi-MHz Circuits

• Drives 1000pF Load with Rise and Fall Times Typ. 10ns

• CMOS Input Thresholds for Improved Noise Immunity

• Independent Inputs for Non-Half Bridge Topologies

• No Start-Up Problems

• Outputs Unaffected by Supply Glitches, HS Ringing Below

Ground, or HS Slewing at High dv/dt

• Low Power Consumption

• Wide Supply Range

• Supply Undervoltage Protection

•3Ω Driver Output Resistance

• QFN/DFN Package:

- Compliant to JEDEC PUB95 MO-220

QFN - Quad Flat No Leads - Package Outline

- Near Chip Scale Package footprint, which improves

PCB efficiency and has a thinner profile

Applications

• Telecom Half Bridge Power Supplies

• Avionics DC-DC Converters

• Two-Switch Forward Converters

• Active Clamp Forward Converters

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright © Intersil Americas Inc. 2004. All Rights Reserved.

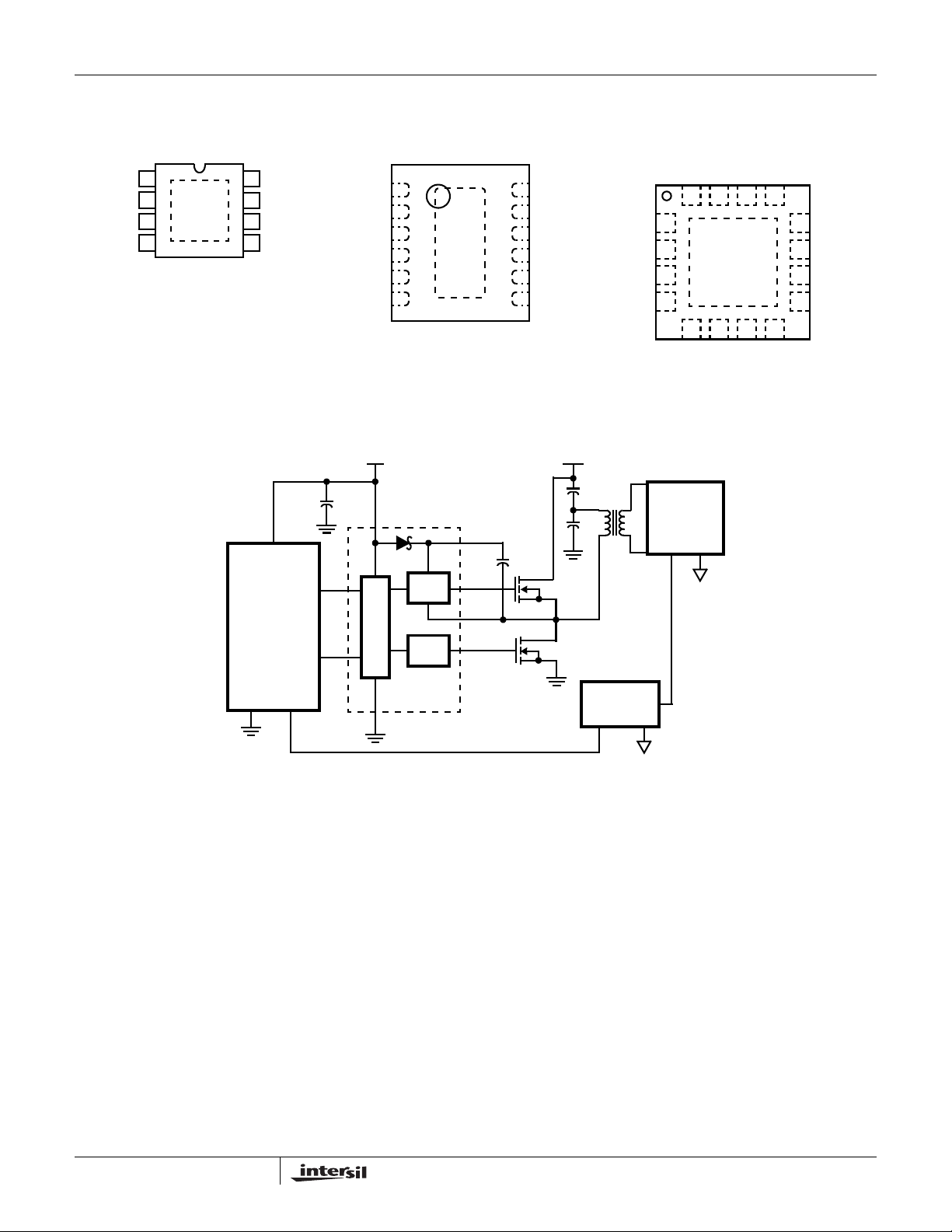

Pinouts

www.BDTIC.com/Intersil

HIP2100 (SOIC, EPSOIC)

TOP VIEW

1

V

DD

HB

2

HO

HS

EPAD

3

4

8

LO

V

7

SS

LI

6

HI

5

NOTE: EPAD = Exposed PAD.

Application Block Diagram

HIP2100

HIP2100IR4 (DFN)

TOP VIEW

V

1

DD

NC

2

NC

3

HB

4

HO

5

6 7HI

HS

EPAD

HIP2100 (QFN)

TOP VIEW

VDDLO

LO

12

11

V

SS

10

NC

9

NC

8

LI

NC

HB

HO

NC

NC

15

16 14 13

1

2

3

4

EPAD

6578

HS

NC

NC

12

NC

11

V

SS

10

LI

NC

9

HI

NC

PWM

CONTROLLER

+12V

V

DD

HB

HI

LI

DRIVE

DRIVE

CONTROL

HIP2100

V

SS

HI

LO

HO

HS

LO

+100V

REFERENCE

AND

ISOLATION

SECONDARY

CIRCUIT

2

FN4022.13

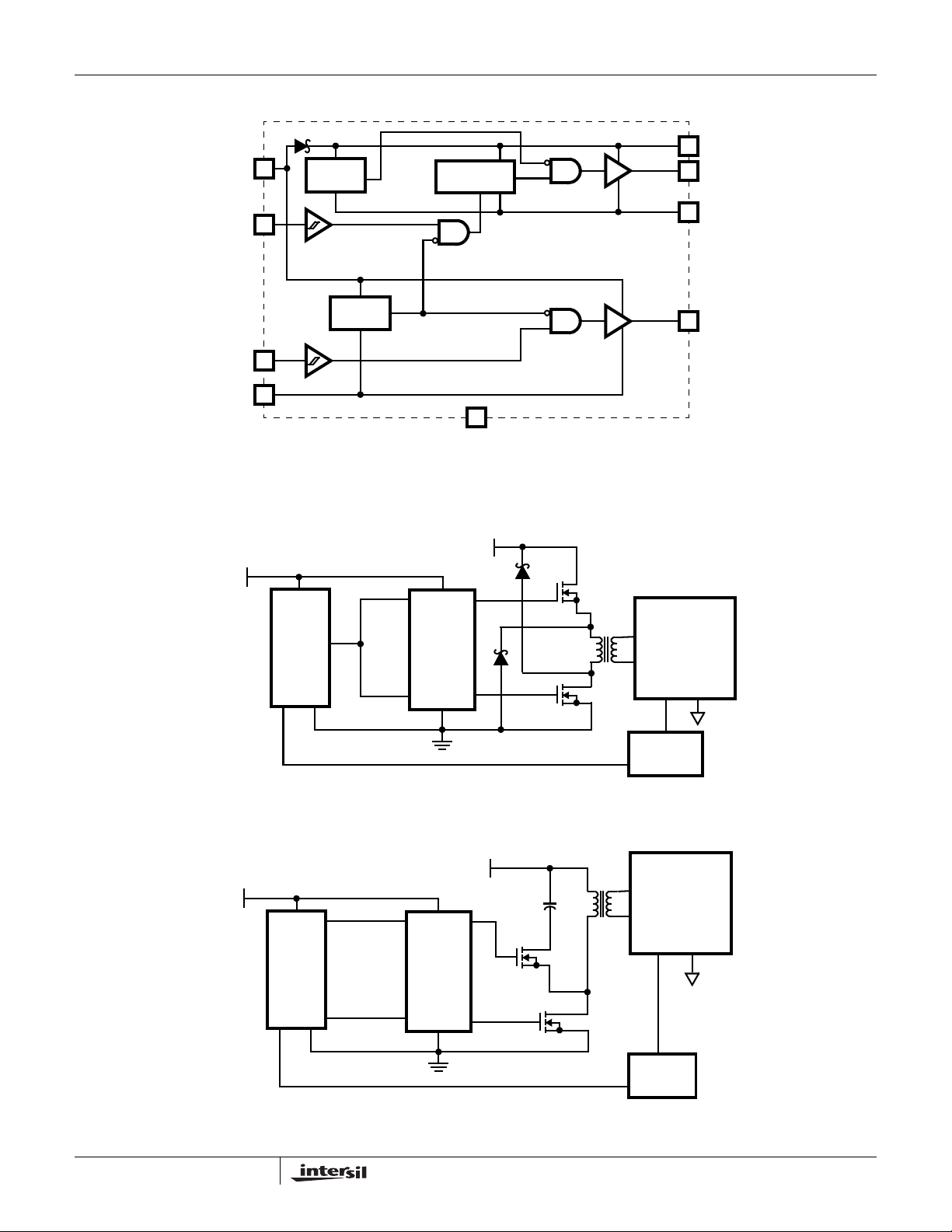

Functional Block Diagram

www.BDTIC.com/Intersil

V

DD

HI

LI

V

SS

*EPAD = Exposed Pad. The EPAD is electrically isolated from all other pins. For

best thermal performance connect the EPAD to the PCB power ground plane.

UNDER

VOLTAGE

UNDER

VOLTAGE

HIP2100

LEVEL SHIFT

EPAD (EPSOIC, QFN and DFN PACKAGES ONLY)

HB

HO

DRIVER

HS

LO

DRIVER

+12V

+12V

+48V

PWM

FIGURE 1. TWO-SWITCH FORWARD CONVERTER

PWM

HIP2100

+48V

HIP2100

SECONDARY

CIRCUIT

ISOLATION

SECONDARY

CIRCUIT

FIGURE 2. FORWARD CONVERTER WITH AN ACTIVE CLAMP

3

ISOLATION

FN4022.13

HIP2100

www.BDTIC.com/Intersil

Absolute Maximum Ratings Thermal Information

Supply Voltage, V

LI and HI Voltages (Note 4) . . . . . . . . . . . . . . . . -0.3V to V

Voltage on LO (Note 4) . . . . . . . . . . . . . . . . . . . -0.3V to V

Voltage on HO (Note 4) . . . . . . . . . . . . . . . V

Voltage on HS (Continuous) (Note 4) . . . . . . . . . . . . . . -1V to 110V

Voltage on HB (Note 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +118V

Average Current in V

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1 (1kV)

DD, VHB-VHS

DD

Maximum Recommended Operating Conditions

Supply Voltage, VDD . . . . . . . . . . . . . . . . . . . . . . . . +9V to 14.0VDC

Voltage on HS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -1V to 100V

Voltage on HS. . . . . . . . . . . . . . . .(Repetitive Transient) -5V to 105V

Voltage on HB . . . V

HS Slew Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . <50V/ns

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the recommended operating conditions of this specification is not implied.

NOTES:

3. The HIP2100 is capable of derated operation at supply voltages exceeding 14V. Figure 16 shows the high-side voltage derating curve for this

mode of operation.

4. All voltages referenced to V

is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

5. θ

JA

is measured in free air with the component mounted on a high effective thermal conductivity test board with “direct attach” features. θ

6. θ

JA

“case temp” is measured at the center of the exposed metal pad on the package underside. See Tech Brief TB379.

+8V to VHS+14.0V and VDD-1V to VDD+100V

HS

(Notes 3, 4) . . . . . . . . -0.3V to 18V

-0.3V to VHB +0.3V

HS

to HB diode . . . . . . . . . . . . . . . . . . . 100mA

unless otherwise specified.

SS

DD

DD

+0.3V

+0.3V

Thermal Resistance (Typical) θ

SOIC (Note 5) . . . . . . . . . . . . . . . . . . . 95 N/A

EPSOIC (Note 6) . . . . . . . . . . . . . . . . . 40 3.0

QFN (Note 6) . . . . . . . . . . . . . . . . . . . . 37 6.5

DFN (Note 6) . . . . . . . . . . . . . . . . . . . . 40 3.0

Max Power Dissipation at 25°C in Free Air (SOIC, Note 5). . . . . . 1.3W

Max Power Dissipation at 25°C in Free Air (EPSOIC, Note 6) . . . 3.1W

Max Power Dissipation at 25°C in Free Air (QFN, Note 6) . . . . . . 3.3W

Storage Temperature Range . . . . . . . . . . . . . . . . . . . -65°C to 150°C

Junction Temperature Range. . . . . . . . . . . . . . . . . . . -55°C to 150°C

Lead Temperature (Soldering 10s - SOIC Lead Tips Only) . . 300°C

For Recommended soldering conditions see Tech Brief TB389.

(°C/W) θJC (°C/W)

JA

JC,

the

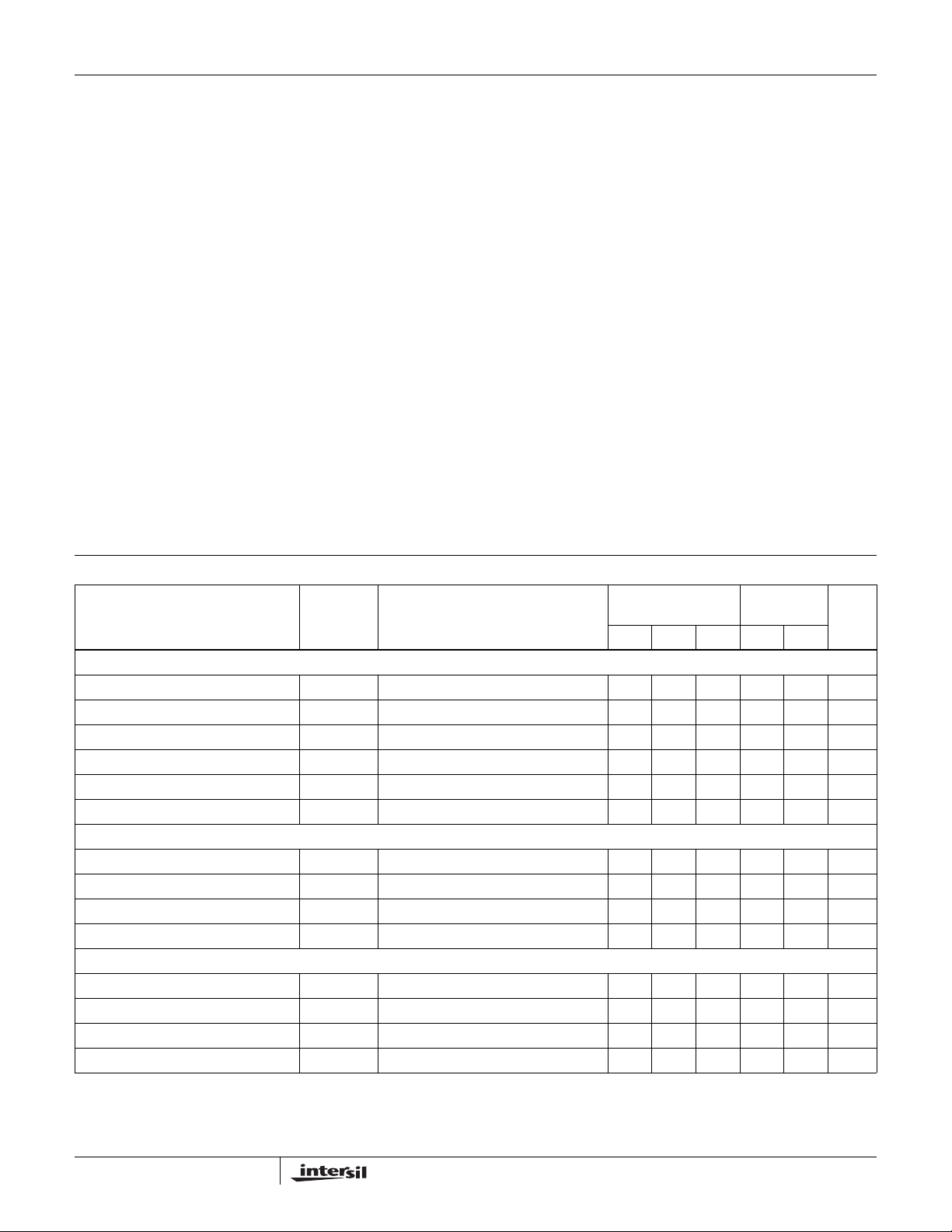

Electrical Specifications V

PARAMETERS SYMBOL TEST CONDITIONS

SUPPLY CURRENTS

Quiescent Current I

V

DD

VDD Operating Current I

Total HB Quiescent Current I

Total HB Operating Current I

HB to V

HB to V

INPUT PINS

Low Level Input Voltage Threshold V

High Level Input Voltage Threshold V

Input Voltage Hysteresis V

Input Pulldown Resistance R

UNDERVOLTAGE PROTECTION

V

V

HB Rising Threshold V

HB Threshold Hysteresis V

Current, Quiescent I

SS

Current, Operating I

SS

Rising Threshold V

DD

Threshold Hysteresis V

DD

DD

= V

HB

= 12V, V

DD

DDO

HB

HBO

HBS

HBSO

IL

IH

IHYS

I

DDR

DDH

HBR

HBH

= V

SS

LI = HI = 0V - 0.1 0.15 - 0.2 mA

f = 500kHz - 1.5 2.5 - 3 mA

LI = HI = 0V - 0.1 0.15 - 0.2 mA

f = 500kHz - 1.5 2.5 - 3 mA

VHS = VHB = 114V - 0.05 1 - 10 µA

f = 500kHz - 0.7 - - - mA

= 0V, No Load on LO or HO, Unless Otherwise Specified

HS

= 25°C

T

J

45.4 - 3 - V

-5.87 - 8 V

-0.4---V

- 200 - 100 500 kΩ

7 7.3 7.8 6.5 8 V

-0.5---V

6.5 6.9 7.5 6 8 V

-0.4---V

T

= -40°C TO

J

125°C

UNITSMIN TYP MAX MIN MAX

4

FN4022.13

Loading...

Loading...