Intersil Corporation HIP2060 Datasheet

HIP2060

April 1998

Features

• Two 10A Power MOS N-Channel Transistors

• Output Voltage to 60V

•r

•r

DS(ON)

DS(ON)

. . . . . 0.135Ω Max Per Transistor at VGS= 15V

. . . . . . 0.15Ω Max Per Transistor at VGS= 10V

• Pulsed Current. . . . . . . . . . . . . . . .25A Each Transistor

• Avalanche Energy . . . . . . . . . . 100mJ Each Transistor

• Grounded Tab Eliminates Heat Sink Isolation

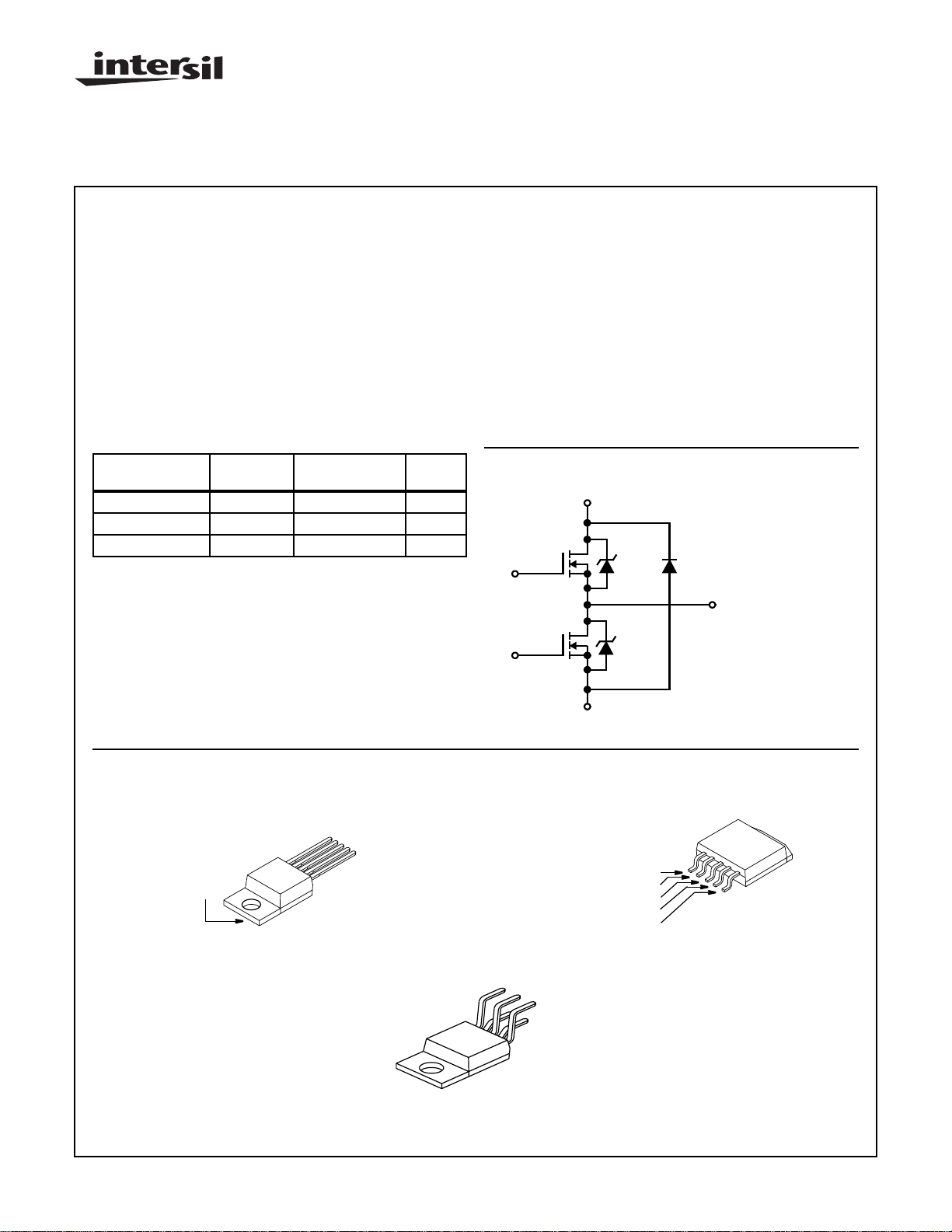

Ordering Information

TEMP.

PART NUMBER

HIP2060AS1 -40 to 125 5 Ld SIP Z5.067C

HIP2060AS2 -40 to 125 5 Ld Gullwing SIP Z5.067A

HIP2060AS3 -40 to 125 5 Ld SIP Z5.067B

NOTE: When ordering use the entire part number.

RANGE (oC) PACKAGE

60V, 10A Half Bridge Power MOSFET Array

Description

The HIP2060 is a power half-bridge MOSFET array that consists of two matched N-Channel enhancement-mode MOS

transistors. The advanced Intersil PASIC2 process technology used in this product utilizes efficient geometries that provides outstanding device performance and ruggedness.

The HIP2060 is designed to integrate two power devices in

one chip thus providing board layout area and heat sink savings for applications such as Motor Controls, Uninterruptable

Power Supplies, Switch Mode Power Supplies, Voice Coil

Motors, and Class D Power Amplifier.

PKG.

NO.

Symbol

DRAIN1

GATE1

1

GATE2

2

5

Z1

Z2

D1

SOURCE1 = DRAIN2

4

Packages

JEDEC TS-001AA (ALTERNATE VERSION)

(TAB)

HIP2060 AS1

SOURCE2

5

4

3

2

1

Z5.067B (SIP)

HIP2060 AS3

3, TAB

JEDEC MO-169

HIP2060 AS2

1 GATE1

2 GATE2

3 SOURCE2

4 SOURCE1-DRAIN2

5 DRAIN1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

1

File Number 3983.5

HIP2060

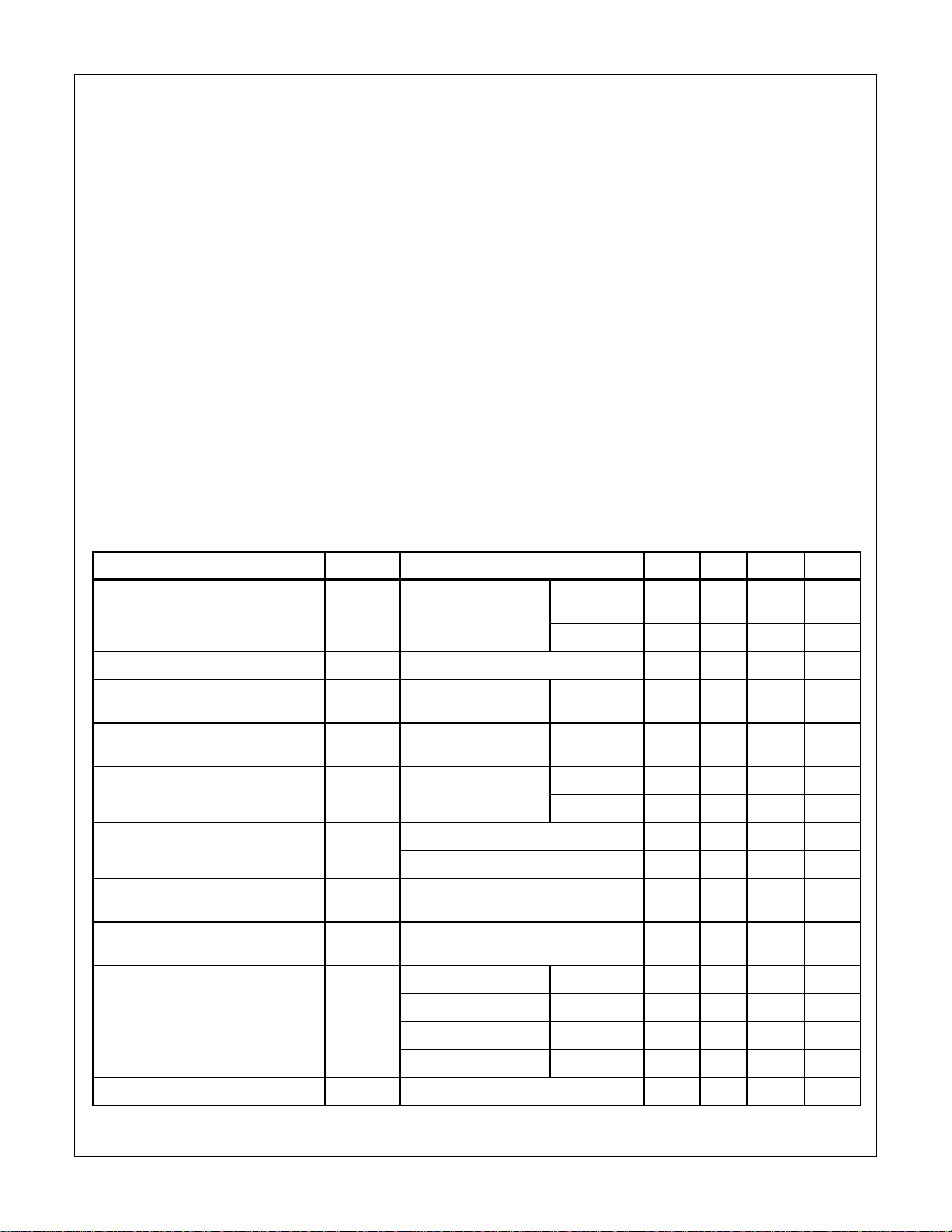

Absolute Maximum Ratings T

= 25oC, Unless Otherwise Specified

C

HIP2060 UNITS

Continuous Drain-Source V oltage Over Operating Junction and Case Temperature Range. . . . . .V

Drain-Gate Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .V

DGR

Gate-Source Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

Continuous Source-Drain Diode Current (Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .I

Pulsed Drain Current, each Output, all Outputs on (Notes 1, 2) . . . . . . . . . . . . . . . . . . . . . . . I

Continuous Drain Current, each Output, all Outputs on (Note 2). . . . . . . . . . . . . . . . . . . . . . . .I

Single Pulse Avalanche Energy (Note 3) Refer to UIS Curve . . . . . . . . . . . . . . . . . . . . . . . . . E

Continuous Power Dissipation at TC = 25oC (Infinite Heatsink). . . . . . . . . . . . . . . . . . . . . . . . . P

DS

GS

SD

DM

DS

AS

D

60 V

60 V

±20 V

10 A

25 A

10 A

100 mJ

46 W

Continuous Power Dissipation, Derate above TC = 25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.37 W/oC

Thermal Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . θ

Operating Case Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

Junction and Storage Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . TJ, T

STG

Lead Temperature (For Soldering, 10s)(Lead Tips Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . T

Continuous Drain1-Source2 Voltage Over Operating Junction Temperature Range. . . . . . V

D1S2

JA

60

C

-40 to 125

-40 to 150

L

300

60 V

o

C/W

o

C

o

C

o

C

NOTES:

1. Pulse width limited by maximum junction temperature.

2. Drain current limited by package construction.

3. VDD = 25V, Start TJ = 25oC, L = 1.5mH, RGS = 50Ω, R = 0. See Figures 2, 12, and 13.

Electrical Specifications T

= 25oC, Unless Otherwise Specified

C

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Drain-Source Breakdown Voltage BV

Gate Threshold Voltage V

Drain1-Source2 Breakdown Voltage

GS(TH)VGS

BV

(Across D1)

Zero Gate Voltage Drain Current I

Drain1-Source2 Current (Through D1) I

Drain-Source On-State Voltage

V

DS(ON)ID

(Note 4)

Forward Gate Current, Drain Short

I

Circuited to Source

Reverse Gate Current, Drain Short

I

Circuited to Source

Drain-Source On Resistance (Note 4) r

DS(ON)VGS

DSSID

D1S2ID1S2

V

DSS

VDS= 60V

VGS = 0V

D1S2

V

V

ID = 10A, VGS = 10V - 1.1 1.5 V

GSSF

GSSR

VDS = 0V, VGS = 20V - - 100 nA

VDS = 0V, VGS = -20V - - -100 nA

VGS = 15V, ID = 10A TC = 125oC - 0.15 0.21 Ω

VGS = 10V, ID = 10A TC = 25oC - 0.11 0.15 Ω

= 100µA, VGS = 0V TC = -40oC to

60 - - V

125oC

TC = 25oC-70-V

= VDS, ID = 250µA 1.5 2.3 2.7 V

= 1µA,

G1S1,VG2S2

= 0V

TC = 25oC - 105 - V

TC = 25oC--1µA

D1S2

G1S1

= 60V

= 0V, V

G2S2

TC = 25oC - 0.3 1 µA

=0V

TC = 125oC-1-µA

= 10A, VGS = 15V - 0.9 1.25 V

= 15V, ID = 10A TC = 25oC - 0.09 0.135 Ω

Forward Transconductance (Note 4) g

VGS = 10V, ID = 10A TC = 125oC - 0.19 0.25 Ω

VDS = 15V, ID = 5A - 4.5 - S

fs

2

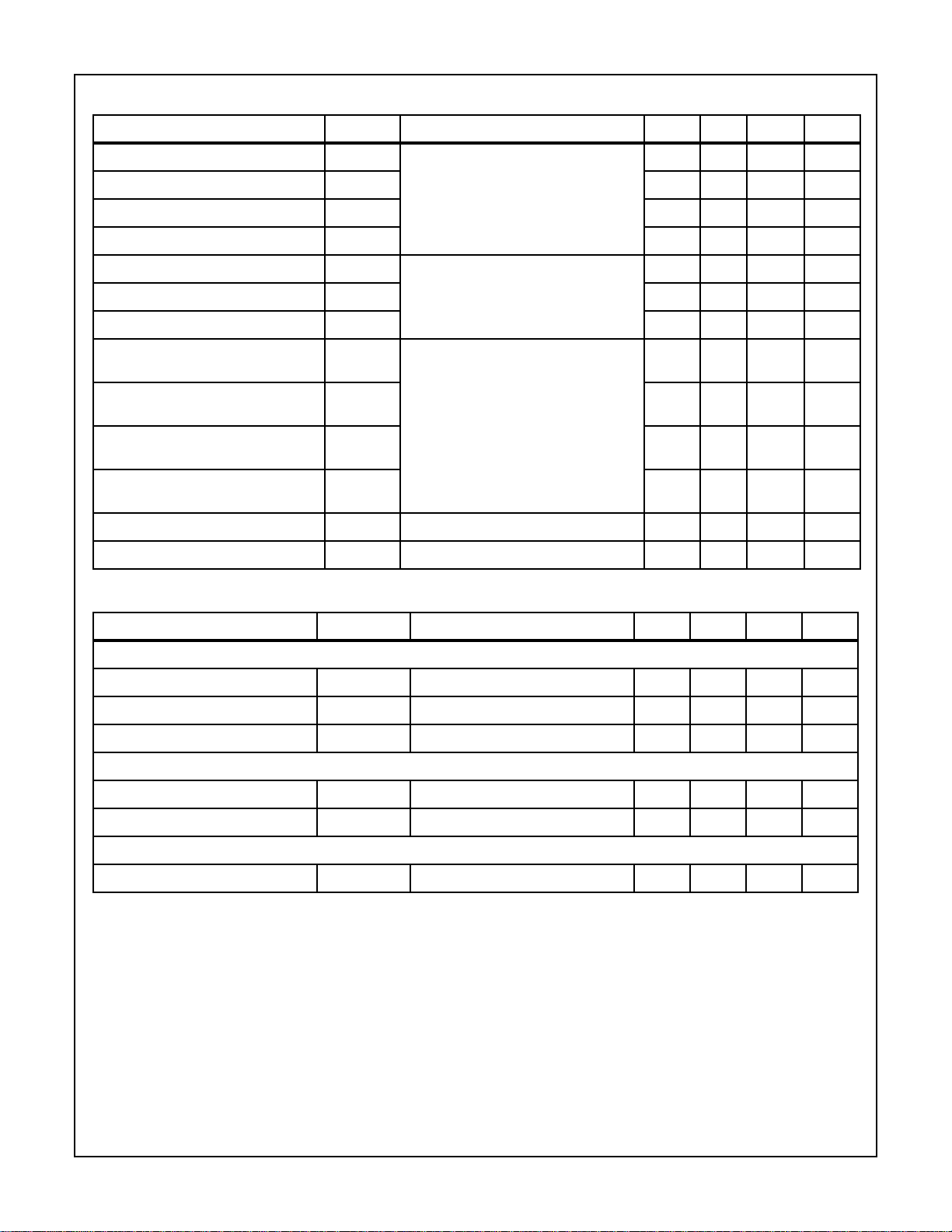

HIP2060

Electrical Specifications T

= 25oC, Unless Otherwise Specified (Continued)

C

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Turn-On Delay Time (Note 5) t

Rise Time (Note 5) t

Turn-Off Delay Time (Note 5) t

Fall Time (Note 5) t

Total Gate Charge (Note 5) Q

Gate-Source Charge (Note 5) Q

Gate-Drain Charge (Note 5) Q

Short-Circuit Input Capacitance,

Common Source

Short-Circuit Output Capacitance,

Common Source for Upper FET

Short Circuit Output Capacitance

Common Source for Lower FET

Short-Circuit Reverse Transfer

Capacitance, Common Source

Thermal Resistance Junction to Case R

Thermal Resistance Junction to Ambient R

d(ON)

r

d(OFF)

f

g(TOT)VDS

gs

gd

C

ISS

C

OSS(U)

C

OSS(L)

C

RSS

θJC

θJA

VDD = 30V, RL = 3Ω

- 4 - ns

ID = 10A, VGS= 10V, RG= 50Ω

See Figure 14

- 5 - ns

-12 - ns

-6- ns

= 50V, VGS = 10V, ID = 10A

- 10.5 12.0 nC

See Figures 16 and 17

- 1.4 2.0 nC

- 4.9 5.5 nC

VDS = 25V, VGS = 0V, f = 1MHz - 230 - pF

- 150 - pF

- 225 - pF

-40 - pF

- - 2.7

o

C/W

- -60oC/W

Source-Drain Diode Specifications

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

SOURCE-TO-DRAIN DIODE SPECIFICATIONS (Across Z1 and Z2)

Forward Voltage (Note 4) V

Reverse Recovery Time (Across Z1) t

Reverse Recovery Time (Across Z2) t

SD

rr(S1-D1)

rr(S2-D2)

SOURCE2-TO-DRAIN1 DIODE SPECIFICATIONS D (Across D1)

Forward Voltage (Note 4) V

Reverse Recovery Time t

SD

rr

DEVICE MATCHING

Drain-Source On Resistance Match r

DS(ON)M

NOTES:

4. Pulse test: Pulse Width ≤ 300µs, Duty Cycle ≤ 2%.

5. Independent of operating temperature.

ISD = 10A, VGS = 0V - 1.05 1.25 V

ISD = 10A, dISD/dt = 100A/µs -50 -ns

ISD = 10A, dISD/dt = 100A/µs -75 -ns

ISD = 10A, VGS = 0V - 8.5 9.5 V

ISD = 10A, dISD/dt = 100A/µs - 200 - ns

VGS = 10V, ID = 10A, TC= 25oC-90-%

3

Loading...

Loading...