®

HIN232, HIN236, HIN237,HIN238,

HIN239, HIN240, HIN241

Data Sheet May 2002

+5V Powered RS-232

Transmitters/Receivers

The HIN232-HIN241 family of RS-232 transmitters/receivers

interface circuits meet all ElA RS-232E and V.28 specifications,

and are particularly suited for those applications where ±12V is

not available. They require a single +5V power supply (except

HIN239) and feature onboard charge pump voltage converters

which generate +10V and

The family of devices offer a wide variety of RS-232

transmitter/rec eiver c ombinations to accomm odate various

applications (see Selection Table).

The drivers feature true TTL/ CMOS input compati bili ty, slewrate-limited output, and 300Ω power-off source imp edance.

The receivers can handle up to ±30V, and have a 3kΩ to 7kΩ

input impedance. The receivers also feature hysteresis to

greatly improve noise rejection.

-10V supplies from the 5V supply.

FN3138.11

Features

• Meets All RS-232E and V.28 Specifications

• Requires Only Single +5V Power Supply

- (+5V and +12V - HIN239)

• High Data Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . 120kbps

• Onboard Voltage Double r/ Inverter

• Low Power Consumption

• Low Power Shutdown Function

• Three-State TTL/CMOS Receiver Outputs

• Multiple Drivers

- ±10V Output Swing for 5V lnput

-300Ω Power-Off Source Impeda nce

- Output Current Limiting

- TTL/CM OS C om pa t ib le

-30V/µs Maximum Slew Rate

• Multiple Receivers

- ±30V Input Voltage Range

-3kΩ to 7kΩ Input Impedance

- 0.5V Hysteresis to Improve Noise Rejecti on

Applications

• Any System Requiring RS-232 Commun ication Ports

- Computer - Portable, Mainframe, Laptop

- Peripheral - Printers and Terminals

- Instrumentation

- Modems

Selection Table

NUMBER OF

PART

NUMBER

HIN232 +5V 2 2 4 Capacitors NO/NO 16

HIN236 +5V 4 3 4 Capacitors YES/YES 24

HIN237 +5V 5 3 4 Capacitors NO/NO 24

HIN238 +5V 4 4 4 Capacitors NO/NO 24

HIN239 +5V and +7.5V to 13.2V 3 5 2 Capacitors NO/YES 24

HIN240 +5V 5 5 4 Capacitors YES/YES 44

HIN241 +5V 4 5 4 Capacitors YES/YES 28

POWER SUPPLY

VOLTAGE

RS-232

DRIVERS

NUMBER OF

RS-232

RECEIVERS

EXTERNAL

COMPONENTS

LOW POWER

SHUTDOWN/TTL

THREE-STATE

NUMBER OF

LEADS

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Intersil (and design) is a trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2002. All Rights Reserved

HIN232 thru HIN241

Ordering Information

PART

NUMBER

HIN23 2C B 0 to 70 16 Ld SOIC M16.3

HIN23 2C B- T 0 to 70 Tape and Ree l

HIN23 2C P 0 to 70 16 Ld PDIP E16.3

HIN232IB -40 to 85 16 Ld SOIC M16.3

HIN232IP -40 to 85 16 Ld PDIP E16.3

HIN23 6C B 0 to 70 24 Ld SOIC M24.3

HIN23 6C P 0 to 70 24 Ld PDIP E24.3

HIN236IB -40 to 85 24 Ld SOIC M24.3

HIN23 7C B 0 to 70 24 Ld SOIC M24.3

HIN23 7C B- T 0 to 70 Tape and Ree l

HIN23 8C B 0 to 70 24 Ld SOIC M24.3

TEMP.

RANGE (

o

C) PACKAGE PKG. NO.

Ordering Information (Continued)

PART

NUMBER

HIN23 8C B- T 0 to 70 Tape and Ree l

HIN23 8C P 0 to 70 24 Ld PDIP E24.3

HIN238IB -40 to 85 24 Ld SOIC M24.3

HIN23 9C B 0 to 70 24 Ld SOIC M24.3

HIN23 9C B- T 0 to 70 Tape and Ree l

HIN23 9C P 0 to 70 24 Ld PDIP E24.3

HIN239IB -40 to 85 24 Ld SOIC M24.3

HIN24 0C N 0 to 70 44 Ld MQFP Q44.10 X1 0

HIN24 1C A 0 to 70 28 Ld SSOP M28.20 9

HIN24 1C B 0 to 70 28 Ld SOIC M28.3

HIN241IB -40 to 85 28 Ld SOIC M28.3

TEMP.

RANGE (

o

C) PACKAGE PKG. NO.

Pin Descriptions

PIN FUNCTION

V

CC

V+ Internally generated positive supply (+10V nominal), HIN239 requires +7.5V to +13.2V.

V- Internally genera ted negative supply (-10V nomina l).

GND Ground lead. Connect to 0V.

C1+ External capacitor (+ terminal) is connected to this lead.

C1- External capacitor (- terminal) is connected to this lead.

C2+ External capacitor (+ terminal) is connected to this lead.

C2- External capacitor (- terminal) is connected to this lead.

T

IN

T

OUT

R

IN

R

OUT

EN

SHUTDOWN Shutdown Input. With SHUTDOWN = 5V, the charge pump is disabled, the receiver outputs are in a high impedance state

NC No Connect. No connection s are made t o these leads.

Power Supply Input 5V ±10%.

Transmitter Inputs. These leads accept TTL/CMOS levels. An internal 400kΩ pull-up resistor to V

Transmitter Outputs. These are RS-232 levels (nominally ±10V).

Receiver Inputs. These inputs accept RS-232 input levels. An internal 5kΩ pull-down resistor to GND is connected to each input.

Receiver Outputs. These are TTL/CMOS levels.

Enable input. This is an active low input which enables the receiver outputs. With EN = 5V, the outputs are placed in a high

impedance state.

and the transmitters are shut off.

is connected to each lead.

CC

2

Pinouts

HIN232 (PDIP, SOIC)

TOP VIEW

HIN232 thru HIN241

HIN236 (PDIP, SOIC)

TOP VIEW

NOTE 1

NOTE 1

T1

T2

R1

OUT

R2

OUT

24

T4

23

R2

22

R2

21

SHUTDOWN

20

EN

19

T4

18

T3

17

R3

R3

16

15

V-

14

C2-

13

C2+

OUT

IN

OUT

IN

IN

OUT

IN

T2

C1+

C2+

OUT

R2

V+

C1-

C2-

V-

1

1

2

3

4

5

6

7

8

IN

16

V

CC

15

GND

14

T1

OUT

13

R1

IN

12

R1

OUT

11

T1

IN

10

T2

IN

9

R2

OUT

T3

T1

T2

R1

OUT

OUT

OUT

R1

OUT

T2

T1

GND

V

CC

C1+

V+

C1-

2

3

4

IN

5

6

IN

7

IN

8

9

10

11

12

+5V

+

1µF

1

C1+

+

3

4

+

5

11

IN

10

IN

VOLTAGE DOUBLER

C1C2+

VOLTAGE INVERTER

C2-

+5V

400kΩ

+5V

400kΩ

16

V

CC

+5V TO 10V

+10V TO -10V

T1

T2

R1

R2

5kΩ

5kΩ

V+

V-

10

C1+

+

1µF

12

NOTE 1

+

2

1µF

6

T1

R1

R2

T2

T3

T4

OUT

OUT

IN

IN

IN

IN

NOTE 1

+

14

7

1312

89

T1

T2

R1

R2

OUT

OUT

IN

IN

C1-

13

C2+

+

14

C2-

+5V

7

+5V

6

+5V

18 1

+5V

19 24

+5V

9

V

CC

+5V TO 10V

VOLTAGE DOUBLER

+10V TO -10V

VOLTAGE INVERTER

400kΩ

400kΩ

400kΩ

400kΩ

T1

T2

T3

T4

R1

R2

5kΩ

5kΩ

V+

V-

1µF

+

11

15

1µF

+

2

3

T1

OUT

T2

OUT

T3

OUT

T4

R1

R2

OUT

IN

IN

45

2322

15

NOTE:

1. Either 0.1µF or 1µF capacitors may be used. The V+ capacitor

may be terminated to V

or to GND.

CC

3

R3

OUT

EN

1617

R3

20

R3

5kΩ

21

IN

SHUTDOWN

8

Pinouts (Continued)

T3

1

OUT

T1

2

OUT

T2

3

OUT

R1

4

IN

R1

5

OUT

T2

6

IN

T1

7

IN

8

GND

V

9

CC

C1+

10

V+

11

12

C1-

HIN237 (SOIC)

TOP VIEW

HIN232 thru HIN241

HIN238 (PDIP, SOIC)

TOP VIEW

24

T4

OUT

R2

23

IN

R2

22

OUT

T5

21

IN

T5

20

OUT

T4

19

IN

T3

18

IN

R3

17

OUT

R3

16

IN

V-

15

14

C2-

13

C2+

R2

R1

T2

T1

OUT

OUT

R2

OUT

T1

OUT

R1

GND

V

CC

C1+

V+

C1-

T3

1

2

3

IN

4

5

IN

6

7

IN

8

9

10

11

12

24

OUT

R3

23

IN

R3

22

OUT

T4

21

IN

T4

20

OUT

T3

19

IN

T2

18

IN

R4

17

OUT

R4

16

IN

V-

15

C2-

14

C2+

13

R1

R2

R3

+5V

10

C1+

+

1µF

12

C1-

13

C2+

+

1µF

14

C2-

+5V

400kΩ

T1

T2

T3

T4

T5

OUT

7

IN

+5V

400kΩ

6

IN

+5V

400kΩ

18 1

IN

+5V

400kΩ

19 24

IN

+5V

400kΩ

21 20

IN

V

+5V TO 10V

VOLTAGE DOUBLER

+10V TO -10V

VOLTAGE INVERTER

T1

T2

T3

T4

T5

R1

OUT

R2

OUT

R3

CC

9

V+

V-

5kΩ

5kΩ

5kΩ

1µF

+

11

15

1µF

+

2

3

45

T1

T2

T3

T4

T5

R1

OUT

OUT

OUT

OUT

OUT

IN

T1

T2

T3

T4

R1

R2

2322

R2

IN

R3

1617

R3

IN

R4

10

C1+

+

1µF

12

C1-

13

+

1µF

14

5

IN

18

IN

19 24

IN

21 20

IN

OUT

OUT

OUT

OUT

VOLTAGE DOUBLER

C2+

VOLTAGE INVERTER

C2-

+5V

400kΩ

+5V

400kΩ

+5V

400kΩ

+5V

400kΩ

8

9

V

CC

+5V TO 10V

+10V TO -10V

T1

T2

T3

T4

R1

R2

R3

R4

8

5kΩ

5kΩ

5kΩ

5kΩ

V+

V-

1µF

+

11

15

1µF

+

2

1

76

34

2322

1617

T1

T2

T3

T4

R1

R2

R3

R4

OUT

OUT

OUT

OUT

IN

IN

IN

IN

+5V

4

Pinouts (Continued)

HIN239 (PDIP, SOIC)

R1

1

OUT

R1

2

IN

3

GND

V

4

CC

5

V+

6

C1+

7

C1-

8

V-

9

R5

IN

R5

10

OUT

R4

11

OUT

R4

12

IN

TOP VIEW

HIN232 thru HIN241

HIN240 (MQFP)

OUT

IN

OUT

NC

SHUTENT5

DOWN

T1

24

IN

T2

23

IN

R2

22

OUT

R2

21

IN

T2

20

OUT

T1

19

OUT

R3

18

IN

R3

17

OUT

T3

16

IN

15

NC

14

EN

T3

13

OUT

R3

T4

T3

T1

T2

T5

R3

R2

NC

IN

OUT

IN

OUT

OUT

OUT

OUT

NC

IN

NC

44 43 42 41 40

1

2

3

4

5

6

7

8

9

10

11

12 13 14 15 16 17

NC

OUT

T2INT1

R2

R4

R4

39 38 37 36 35 34

IN

IN

OUT

R1

R1

T4INT3INR5

CC

NCNCNC

V

GND

OUTR5IN

NC

33

32

31

30

29

28

27

26

25

24

23

2221201918

NC

NC

NC

VC2C2+

C1V+

C1+

NC

NC

+5V

4

V

CC

+10V TO -10V

T1

T2

T3

1µF

(NOTE)

T1

T2

T3

R1

OUT

6

C1+

+

7

C1-

VOLTAGE INVERTER

+5V

400kΩ

24

IN

+5V

400kΩ

23

IN

+5V

400kΩ

16 13

IN

1

R1

R2

OUT

R2

R3

OUT

R3

R4

OUT

R4

R5

OUT

R5

EN

14

3

NOTE: For V+ > 11V, use C1 ≤ 0.1µF.

+7.5V TO +13.2V (NOTE)

5

V+

8

V-

1µF

+

19

20

2

5kΩ

2122

5kΩ

1817

5kΩ

1211

5kΩ

910

5kΩ

T1

T2

T3

R1

R2

R3

R4

R5

OUT

OUT

OUT

IN

IN

IN

IN

IN

R1

R2

R3

R4

R5

1µF

1µF

T1

T2

T3

T4

T5

OUT

OUT

OUT

OUT

OUT

+5V

25

C1+

+

27

C1-

28

+

29

15

IN

14

IN

37 6

IN

38 5

IN

241

IN

VOLTAGE DOUBLER

C2+

VOLTAGE INVERTER

C2-

+5V

400kΩ

+5V

400kΩ

+5V

400kΩ

+5V

400kΩ

+5V

400kΩ

16

42

EN

19

V

CC

+5V TO 10V

+10V TO -10V

T1

T2

T3

T4

T5

R1

R2

R3

R4

R5

5kΩ

5kΩ

5kΩ

5kΩ

5kΩ

V+

V-

+

26

30

7

8

17

1013

43

4039

3536

43

SHUTDOWN

1µF

1µF

T1

T2

T3

T4

T5

R1

R2

R3

R4

R5

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

18

5

Pinouts (Continued)

HIN232 thru HIN241

HIN241 (SOIC, SSOP)

TOP VIEW

R1

R2

R3

R4

R5

1µF

1µF

T1

T2

T3

T4

OUT

OUT

OUT

OUT

OUT

T3

1

OUT

T1

2

OUT

T2

3

OUT

R2

4

IN

R2

5

OUT

T2

6

IN

T1

7

IN

R1

8

OUT

R1

9

IN

GND

10

11

V

CC

C1+

12

13

V+

14

C1-

+5V

12

C1+

+

14

C1-

15

+

16

7

IN

6

IN

20 1

IN

21 28

IN

8

VOLTAGE DOUBLER

C2+

VOLTAGE INVERTER

C2-

+5V

400kΩ

+5V

400kΩ

+5V

400kΩ

+5V

400kΩ

11

V

CC

+5V TO 10V

+10V TO -10V

T1

T2

T3

T4

R1

R2

R3

R4

R5

EN

24

10

5kΩ

5kΩ

5kΩ

5kΩ

5kΩ

28

T4

27

R3

R3

26

SHUTDOWN

25

24

EN

R4

23

R4

22

T4

21

20

T3

R5

19

R5

18

V-

17

16

C2-

15

C2+

13

V+

17

V-

2

3

9

45

2726

2322

1819

25

OUT

IN

OUT

IN

OUT

IN

IN

OUT

IN

1µF

+

1µF

+

SHUTDOWN

T1

T2

T3

T4

R1

R2

R3

R4

R5

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

6

HIN232 thru HIN241

Absolute Maximum Ratings Thermal Information

VCC to Ground. . . . . . . . . . . . . . . . . . . . . . (GND -0.3V) < VCC < 6V

V+ to Ground (Note 2) . . . . . . . . . . . . . . . (V

-0.3V) < V+ < 13.2V

CC

V- to Ground . . . . . . . . . . . . . . . . . . . . . . .-12V < V- < (GND +0.3V)

V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24V

Input Voltages

T

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V < VIN < (V+ +0.3V)

IN

R

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±30V

IN

Output Voltages

T

. . . . . . . . . . . . . . . . . . . .(V- -0.3V) < V

OUT

R

. . . . . . . . . . . . . . . . . (GND -0.3V) < V

OUT

Short Cir c ui t Du rat i o n

T

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Continuous

OUT

R

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Continuous

OUT

TXOUT

RXOUT

< (V+ +0.3V)

< (V+ +0.3V)

Thermal Resistance (Typical, Note 3) θ

16 Ld PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . 90

24 Ld PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . 70

16 Ld SOIC (W) Package. . . . . . . . . . . . . . . . . . . . . 100

24 Ld SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . 75

28 Ld SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . 70

28 Ld SSOP Package . . . . . . . . . . . . . . . . . . . . . . . 95

44 Ld MQFP Package . . . . . . . . . . . . . . . . . . . . . . . 80

Maximum Junction Temperature (Plastic Package) . . . . . . . .150

Maximum Storage Temperature Range . . . . . . . . . -65

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . .300

(SOIC, SSOP, MQFP - Lead Tips Only)

Operating C o ndi t io ns

Temperature R an ge

HIN2XXCX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0

HIN2XXIX. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40

CAUTION: Stress es abov e thos e lis ted in “ A bsolute Max imum R a tings” ma y cause per manen t dam age to th e de vice. This is a s tress on ly rating and ope rat ion of th e

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

2. Only HIN239. For V+ > 11V, C1 must be ≤0.1µF.

is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

3. θ

JA

o

C to 70oC

o

C to 85oC

(oC/W)

JA

o

C to 150oC

o

o

C

C

Electrical Specifications Test Conditions: V

= +5V ±10%, TA = Operating Temperature Range

CC

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

SUPPLY CURRENTS

Power Supply Current, I

CC

V+ Power Supply Current, I

No Load, TA = 25oC

Shutdown Supply Current, I

CC

(SD) TA = 25oC-110µA

CC

No Load,

T

= 25oC

A

No Load,

TA = 25oC

LOGIC AND TRANSMITTER INPUTS, RECEIVER OUTPUTS

Input Logic Low, V

Input Logic High, V

Transmitte r Inp ut Pullu p Curre nt , I

lL

lH

P

TTL/CMOS Receiver Output Voltage Low, V

TTL/CMOS Receiver Output Voltage High, V

TIN, EN, Shutdown - - 0.8 V

T

IN

EN

, Shutdown 2.4 - - V

TIN = 0V - 15 200 µA

OLIOUT

OHIOUT

= 1.6mA - 0.1 0.4 V

= -1.0mA 3.5 4.6 - V

RECEIVER INPUTS

RS-232 Input Voltage Range V

Receiver Input Impedance R

Receiver Input Low Threshold, V

Receiver Input High Threshold, V

Receiver Input Hysteresis V

IN

IN

(H-L) VCC = 5V, TA = 25oC0.81.2-V

lN

(L-H) VCC = 5V, TA = 25oC-1.72.4V

IN

HYST

VIN = ±3V 3.0 5.0 7.0 kΩ

TIMING CHARACTERISTICS

Baud Rate (1 Transmitter Switching) R

= 3kΩ 120 - - kbps

L

HIN232 - 5 10 mA

HIN236-238, HIN240-241 - 7 15 mA

HIN239 - 0.4 1 mA

HIN239 - 5.0 15 mA

2.0 - - V

-30 - +30 V

0.2 0.5 1.0 V

7

HIN232 thru HIN241

Electrical Specifications Test Conditions: V

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Output Enable Time, t

Output Disable Time, t

Propagation Delay, t

Instantaneou s Slew Rate SR C

Transition Region Slew Rate, SR

TRANSMITTER OUTPUTS

Output Voltage Swing, T

Output Resistance, R

RS-232 Output Short Circuit Current, I

NOTE:

4. Guaranteed by design.

V

CC

GND

EN

DIS

PD

T

OUT

OUT

SC

VOLTAGE DOUBLER

S1 S2

S3

C1

C1-

+

+

-

C1

HIN236, 239, 240, 241 - 400 - ns

HIN236, 239, 240, 241 - 250 - ns

RS-232 to TTL - 0.5 - µs

RL = 3kΩ , CL = 2500 pF Measu red from +3 V to -3V or

-3V to +3V, 1 Transmitter Switching

Transm it t er Out p ut s, 3kΩ to Ground ±5 ±9 ±10 V

VCC = V+ = V- = 0V, V

T

S4

= +5V ±10%, TA = Operating Temperature Range (Continued)

CC

= 10pF, RL = 3kΩ , TA = 25oC (Note 4) - - 30 V/µs

L

-3-V/µs

= ±2V 300 - - Ω

OUT

shorted to GND - ±10 - mA

OUT

VOLTAGE INVERTER

C2

C2

+

S6

+

C2

-

-

S8

+

C4

-

GND

V- = -(V+)

GND

CC

S5

S7

V+ = 2V

+

C3

V

CC

RC

OSCILLATOR

FIGURE 1. CHARGE PUMP

Detailed Description

The HIN232 thru HIN241 family of RS-232

transmitters/receivers are powered by a single +5V power

supply (except HIN239), feature low power consumption, and

meet all ElA RS-232C and V.28 specifications. The circuit is

divided into three sections: The charge pump, transmitter, and

receiver.

Charge Pump

An equivalent circuit of the charge pump is illustrated in Figure

1. The charge pump contains two sections: the voltage

doubler and the voltage inverter. Each section is driven by a

two phase, internally generated clock to generate +10V and

-10V. The nominal clock frequency is 16kHz. During phase

one of the clock, capacitor C1 is charged to V

phase two, the voltage on C1 is added to V

signa l ac r oss C3 eq ual to t wic e V

also charged to 2V

, and then during phase two, it is

CC

. Duri ng ph a se one, C 2 is

CC

inverted with respect to ground to produce a signal across C4

equal to -2V

. The charge pump accepts input voltages up

CC

to 5.5V. The output impedance of the voltage doubler section

(V+) is approximately 200Ω, and the output impedance of the

voltage inverter section (V-) is approximately 450Ω. A typical

. During

CC

, producin g a

CC

appli catio n uses 1µF capacitors for C1-C4, however, the value

is not criti cal. Incr easi ng the v alues of C1 and C2 wi ll lowe r the

output impedance of the volta ge doubler an d inver ter,

increasing the values of the reservoir capacitors, C3 and C4,

lowers the ripple on the V+ and V- supplies.

During shutdown mode (HI N236, 240 and 241),

SHUTDOWN control li ne set to logic “1”, the charge pump is

turned off, V+ is pull ed down to V

, V- is pulled up to GND,

CC

and the supply current is reduced to less than 10µA. The

transmitt er outpu ts are di sabled and th e receiv er outpu ts are

placed in the high impedance state.

Transmitters

The transmitters are TTL/CMOS compatible inverters which

translate the inputs to RS-232 outputs. The input logic threshold

is about 26% of V

input results in a voltage of between -5V and V- at the output,

and a logic 0 results in a voltage between +5V and (V+ -0.6V).

Each transmitter input has an internal 400kΩ pullup resistor so

any unused input can be left unconnected and its output

remains in its low state. The output voltage swing meets t he

RS-232C specifications of ±5V minimum with the worst case

conditions of: all transmitters driving 3kΩ minimum load

, or 1.3V for VCC = 5V. A logic 1 at the

CC

8

HIN232 thru HIN241

impedance, V

= 4.5V, and maximum allowable operating

CC

temperature. The transmitters have an internally limited output

slew rate which is less than 30V/µs. The outputs are short

circuit protected and can be shorted to ground indefinitely. The

powered down output impedance is a minimum of 300Ω with

±2V applied to the outputs and V

V+

V

GND < T

CC

T

XIN

XIN

V-

400kΩ

< V

CC

FIGURE 2. TRANSMITTER

CC

= 0V.

300Ω

V- < V

T

OUT

TOUT

< V+

Receivers

The receiver in puts accept up to ±30V while presenting the

required 3kΩ to 7 k Ω input i mpedanc e even if the power is of f

T

IN

OR

R

IN

T

OUT

OR

R

OUT

t

PHL

= 0V). The receivers have a typical input threshold of

(V

CC

1.3V which is within the ±3V limits, known as the transition

region, of the RS-232 specifications. The receiver output is

0V to V

. The output will be low whenever the input is

CC

greater than 2.4V and high whenever the input is flo ati ng or

driven between +0.8V and -30V. The receivers feature 0.5V

hysteresis to improve noise reject ion. The receiver Enable

, when set to logic “1”, (HI N 236, 239, 240, and 241)

line EN

disables the receiver outputs, pl acing them in the high

impedance mode. The recei ver outputs are also pl aced in

the high impedance st ate when in shutdown mode.

V

CC

R

t

PLH

-30V < R

XIN

< +30V

XIN

GND

5kΩ

FIGURE 3. RECEIVER

V

OL

V

OL

GND < V

R

OUT

ROUT

< V

CC

Average Propagation Delay =

FIGURE 4. PROPAGATION DELAY DEFINITION

Typical Performance Curves

12

10

8

6

4

V- SUPPLY VOLTAGE

2

0

3.0

3.5

4.0 4.5 6.0

V

CC

FIGURE 5. V- SUPPLY VOLTAGE vs VCC, VARYING

CAPACITORS

5.0 5.5

1µF

0.47µF

0.10µF

t

PHL + tPLH

2

TA = 25oC

12

TRANSMITTER OUTPUTS

OPEN CIRCUIT

10

8

6

4

SUPPLY VOLTAGE (|V|)

2

0

V- (VCC = 4.5V)

V+ (VCC = 5V)

V- (VCC = 5V)

| (mA)

|I

LOAD

V+ (VCC = 4.5V)

FIGURE 6. V+, V- OUTPUT VOLTAGE vs LOAD (HIN232)

302520151050

35

9

Test Circuits (HIN232)

-

1µF

C3

1µF

C1

1µF

C2

3kΩ

T2

OUTPUT

RS-232

±30V INPUT

+

+

-

+

-

+

1µF C4

C1+

1

V+

2

C1-

3

C2+

4

C2-

5

-

V-

6

T2

7

OUT

8

R2

IN

T1

R1

R2

V

CC

GND

OUT

R1

OUT

T1

T2

OUT

HIN232 thru HIN241

+4.5V TO

+5.5V INPUT

16

15

14

13

IN

12

11

IN

10

IN

9

3kΩ

T1 OUTPUT

RS-232 ±30V INPUT

TTL/CMOS OUTPUT

TTL/CMOS INPUT

TTL/CMOS INPUT

TTL/CMOS OUTPUT

1

2

3

4

5

6

7

8

R

OUT

VIN = ±2V

C1+

V+

C1C2+

C2V-

T2

OUT

R2

IN

= VIN/1

R1

R2

T2

T1

V

CC

GND

OUT

R1

OUT

T1

T2

OUT

OUT

T1

A

IN

IN

IN

16

15

14

13

12

11

10

9

OUT

FIGURE 7. GENERAL TEST CIRCUIT FIGURE 8. POWER-OFF SOURCE RESISTANCE

Applications

The HIN2XX may be used for all RS-232 data terminal and

communication links. It is particularly useful in applications

where ±12V power supplies are not available for

conventional RS-232 interface circuits. The applicati ons

presented represent typical interface configurations.

A simple duplex RS-232 port with CTS/RTS handshaking is

illustrat ed in Fi gure 9. Fixed output signals such as DTR

(data terminal ready) and DSRS (data signaling rate select)

is generated by drivi ng them through a 5kΩ resist or

connected to V+.

In applications requiring four RS-232 i nputs and outputs

(Figure 10), note that each circuit requires two charge pump

capacitors (C1 and C2) but can share common reservoir

capacitors (C3 and C4). The benefit of sharing common

reservoir capacitors is the elimination of two capacitors and

the reduction of the charge pump source impedance which

effectiv ely increases the outpu t swi ng of the transmitters.

CONFIGURATION

TTL/CMOS

INPUTS AND

OUTPUTS

C1

1µF

C2

1µF

+5V

RTS

RD

CTS

TD

16

1

+

3

-

+

-

HIN232

4

5

T1

11

10

12

R2

9

R1

T2

-

+

DTR (20) DATA

2

6

-

+

14

TD (2) TRANSMIT DATA

7

RTS (4) REQUEST TO SEND

13

RD (3) RECEIVE DATA

8

CTS (5) CLEAR TO SEND

SIGNAL GROUND (7)15

TERMINAL READY

DSRS (24) DATA

SIGNALING RATE

SELECT

RS-232

INPUTS AND OUTPUTS

FIGURE 9. SIMPLE DUPLEX RS-232 PORT WITH CTS/RTS

HANDSHAKING

10

HIN232 thru HIN241

TTL/CMOS

INPUTS AND

OUTPUTS

TTL/CMOS

INPUTS AND

OUTPUTS

C1

1µF

TD

RTS

RD

CTS

2µF

C1

1µF

DTR

DSRS

DCD

R1

1

+

-

C4

+

+

-

HIN232

3

T1

11

10

12

R2

9

-

V- V+

6

HIN232

1

3

T1

11

10

12

R2

9

R1

R1

T2

T2

4

+

C2

5

1µF

-

14

TD (2) TRANSMIT DATA

7

RTS (4) REQUEST TO SEND

13

RD (3) RECEIVE DATA

8

CTS (5) CLEAR TO SEND

15

16

26

C3

+

2µF

2

16

4

+

C2

5

1µF

-

14

DTR (20) DATA TERMINAL READY

7

DSRS (24) DATA SIGNALING RATE SELECT

13

DCD (8) DATA CARRIER DETECT

8

R1 (22) RING INDICATOR

+5V

-

RS-232

INPUTS AND OUTPUTS

SIGNAL GROUND (7)15

FIGURE 10. COMBINING TWO HIN232s FOR 4 PAIRS OF RS-232 INPUTS AND OUTPUTS

11

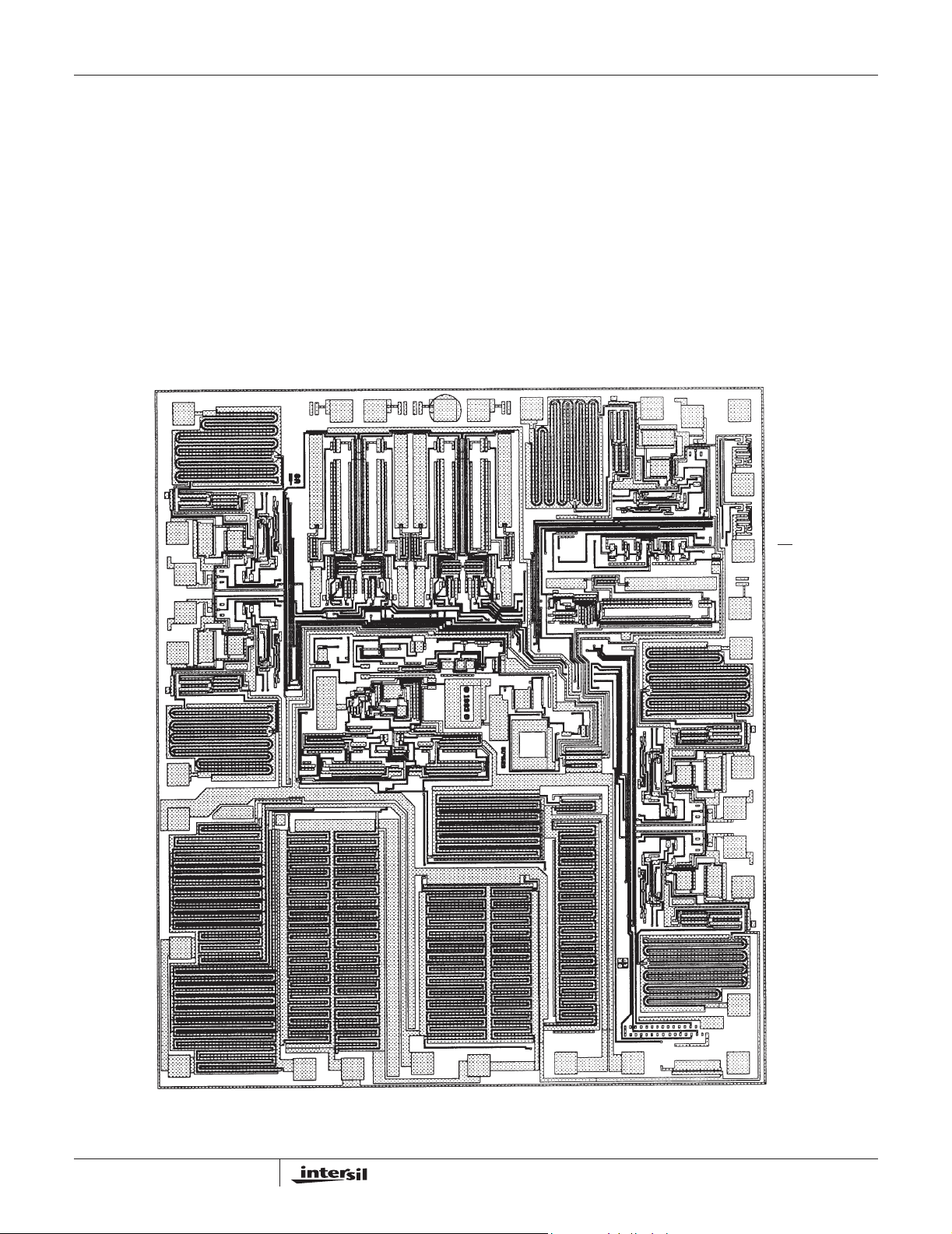

Die Characteristics

HIN232 thru HIN241

DIE DIMENSIONS

160 mils x 140 mils

METALLIZATION

Type: Al

Thickness: 10k

Å ±1kÅ

SUBSTRATE POTENTIAL

V+

Metallization Mask Layout

R2

IN

R2

OUT

T2

IN

PASSIVATION

Type: Nitride over Silox

Nitride Thickness: 8k

Å

Silox Thickness: 7kÅ

TRANSISTOR COUNT

238

PROCESS

CMOS Metal Gate

HIN240

T4

T1

T2

OUT

OUT

T3

OUT

OUT

R3

IN

R3

OUT

T5

IN

SHUTDOWN

EN

R1

T1

OUT

R1

GND

V

CC

T5

R4

R4

T4

T3

R5

R5

OUT

IN

OUT

IN

IN

OUT

IN

IN

IN

12

C1+ V+ C1-

V-C2-C2+

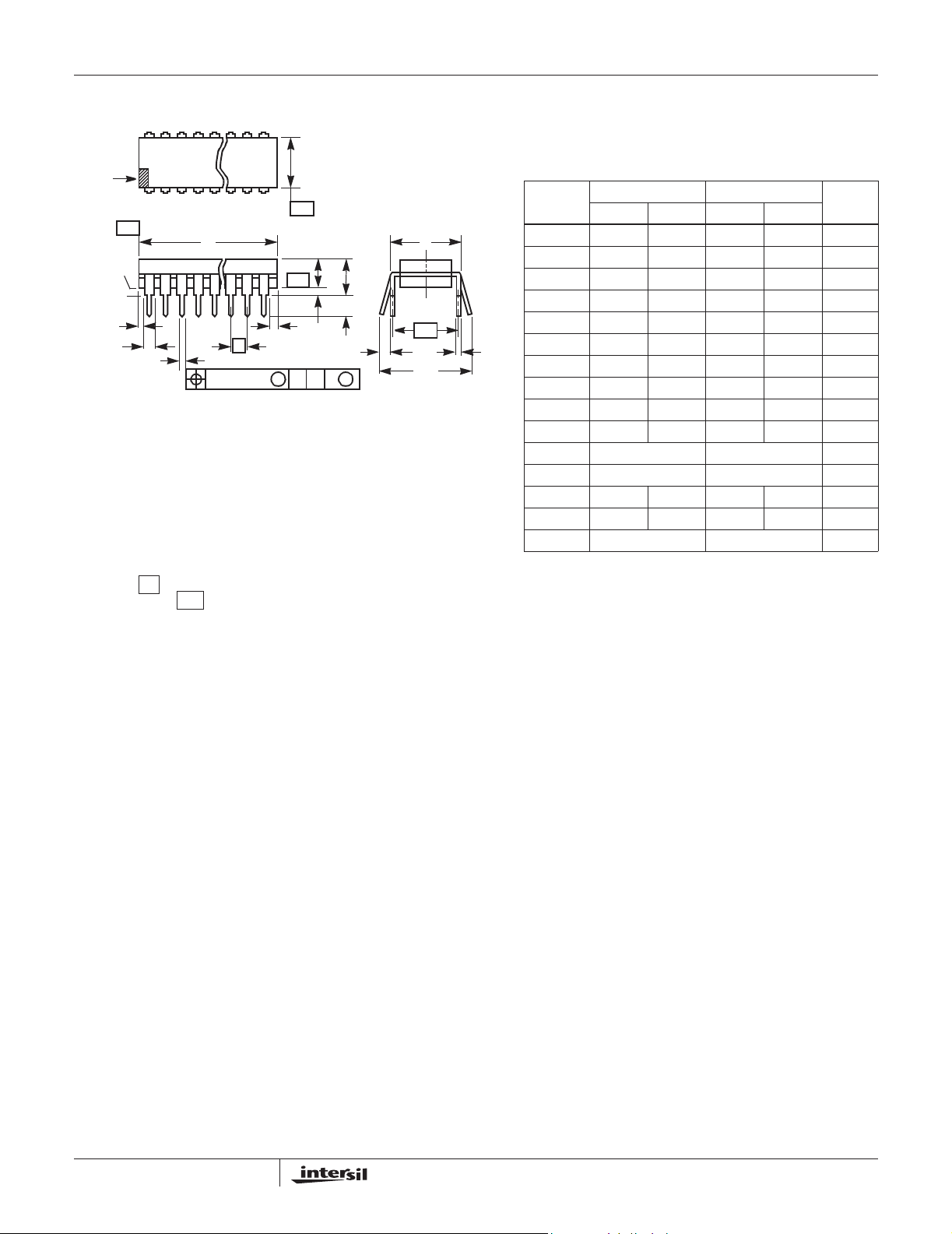

Dual-In-Line Pla stic Pac kages (PDIP )

HIN232 thru HIN241

N

D1

-C-

E1

-B-

A1

A2

E

A

L

e

C

C

L

e

A

C

e

B

INDEX

AREA

BASE

PLANE

SEATING

PLANE

D1

B1

12 3 N/2

-AD

e

B

0.010 (0.25) C AM BS

NOTES:

1. Controlling Dimensions: INCH. In case of conflict between English and

Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbol s are defined in the “MO Series Symbol List” in Section 2.2 of

Publication No. 95.

4. Dimensions A, A1 and L are measured with the package seated in JEDEC sea ting plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and are measur ed wit h the lea ds con str ained t o be per pendi c-

7. e

e

A

ular to dat u m .

and eC are measu red at the l ead tip s wi th the l eads uncon strai ned.

B

e

must be zero or greater.

C

-C-

8. B1 maximum dimensions do not include dambar protrusions. Dambar

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner lea ds (1, N, N /2 and N/2 + 1) fo r E8. 3, E1 6. 3, E1 8. 3, E2 8. 3 ,

E42.6 w ill ha ve a B1 di men si on of 0 .0 30 - 0. 04 5 in ch ( 0 .76 - 1.14 mm) .

E16.3 (JED EC MS-00 1-BB ISSUE D)

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.210 - 5.33 4

A1 0.015 - 0.39 - 4

A2 0.115 0.195 2.93 4.95 -

B 0.014 0.022 0.356 0.558 B1 0.045 0.070 1.15 1.77 8, 10

C 0.008 0.014 0.204 0.355 -

D 0.735 0.775 18.66 19.68 5

D1 0.005 - 0.13 - 5

E 0.300 0.325 7.62 8.25 6

E1 0.240 0.280 6.10 7.11 5

e 0.100 BSC 2.54 BSC -

e

A

e

B

0.300 BSC 7.62 BSC 6

- 0.430 - 10.92 7

L 0.115 0.150 2.93 3.81 4

N16 169

NOTESMIN MAX MIN M AX

Rev. 0 12 /93

13

Dual-In-Line Pla stic Pac kages (PDIP )

HIN232 thru HIN241

N

D1

-C-

E1

-B-

A1

A2

E

A

L

e

C

C

L

e

A

C

e

B

INDEX

AREA

BASE

PLANE

SEATING

PLANE

D1

B1

12 3 N/2

-AD

e

B

0.010 (0.25) C AM BS

NOTES:

1. Controlling Dimensions: INCH. In case of conflict between English and

Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbol s are defined in the “MO Series Symbol List” in Section 2.2 of

Publication No. 95.

4. Dimensio ns A, A1 and L ar e meas ur e d wit h the pack ag e sea ted in

JEDEC seating pl ane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and are measured with the leads constrained to be perpendic-

7. e

e

A

ular to dat u m .

and eC are meas ur e d at th e lead t ip s wi t h th e l ea ds un const r ain ed .

B

e

must be zero or greater.

C

-C-

8. B1 maxim um dime ns io ns do n ot in cl ud e da mbar prot r usi ons . Damba r

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner lea ds (1, N, N /2 and N/2 + 1) fo r E8. 3, E1 6. 3, E1 8. 3, E2 8. 3 ,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E24.3 (JEDEC MS-001-AF ISSUE D)

24 LEAD NARROW BODY DUAL-IN-LINE PLASTIC

PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.210 - 5.33 4

A1 0.015 - 0.39 - 4

A2 0.115 0.195 2.93 4.95 -

B 0.014 0.022 0.356 0.558 B1 0.045 0.070 1.15 1.77 8

C 0.008 0.014 0.204 0.355 -

D 1.230 1.280 31.24 32.51 5

D1 0.005 - 0.13 - 5

E 0.300 0.325 7.62 8.25 6

E1 0.240 0.280 6.10 7.11 5

e 0.100 BSC 2.54 BSC -

e

A

e

B

0.300 BS C 7 .62 BS C 6

- 0.430 - 10.92 7

L 0.115 0.150 2.93 3.81 4

N24 249

NOTESMIN MAX MIN MAX

Rev. 0 12 /93

14

HIN232 thru HIN241

Small Outline Plastic Packages (SOIC)

N

INDEX

AREA

123

SEATING PLANE

-AD

e

B

0.25(0.010) C AM BS

M

E

-B-

A

-C-

0.25(0.010) BM M

H

α

µ

A1

0.10(0.004)

L

h x 45

o

C

NOTES:

1. Symbol s are defined in the “MO Series Symbol List” in Section 2.2 of

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimensio n “ D” does no t in cl ud e mold fl ash , pr ot rus io ns or ga t e bu rrs .

Mold fla sh, pr otru sio n an d gate burrs shal l not excee d 0. 15mm (0. 006

inch) per side.

4. Dimensio n “ E” doe s no t incl u de i nter l ea d fla sh or prot rus io ns . Int er lea d

flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamf er on the body is opti on al . If it is no t pre sen t , a visua l in de x

feature must be located within the crosshat ched area .

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The le ad w id th “ B” , as meas ur ed 0 .36m m ( 0. 014 i nch ) or grea t er a bo ve

the seat in g p lane , sh all n ot e xce ed a ma xi mu m va lue o f 0.61 mm ( 0 .024

inch)

10. Contro lling di mensi on: MILLI METER. Conver ted inch dimensi ons are

not nec essarily exact.

M16.3 (JEDEC MS-013-AA ISSUE C)

16 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.0926 0.1043 2.35 2.65 -

A1 0.0040 0.0118 0.10 0.30 -

B 0.013 0.0200 0.33 0.51 9

C 0.0091 0.0125 0.23 0.32 D 0.3977 0.4133 10.10 10.50 3

E 0.2914 0.2992 7.40 7.60 4

e 0.0 50 BSC 1.2 7 BSC H 0.394 0.419 10.00 10.65 h 0.010 0.029 0.25 0.75 5

L 0.016 0.050 0.40 1.27 6

N16 167

o

α

0

o

8

o

0

o

8

Rev. 0 12 /93

NOTESMIN MAX MIN MAX

-

15

HIN232 thru HIN241

Small Outline Plastic Packages (SOIC)

N

INDEX

AREA

123

SEATING PLANE

-AD

e

B

0.25(0.010) C AM BS

M

E

-B-

A

-C-

0.25(0.010) BM M

H

α

µ

A1

0.10(0.004)

L

h x 45

o

C

NOTES:

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimensio n “D” does n ot incl ude mo ld flas h, pr otru sion s or gate burr s.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm

(0.006 inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead flash and pr otrusi ons shall not exce ed 0.25mm (0.010 inch) per

side.

5. The chamfe r on th e body is op tio nal. If it is not pres ent, a vi sual index

feature must be located within the crosshat ched area .

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater

above the seating plane, shall not exceed a maximum value of

0.61m m (0.024 inch)

10. Contro lling d imens ion: MILLIMETER. Conver ted in ch dime nsio ns

are not necessarily exact.

M24.3 (JEDEC MS-013-AD ISSUE C)

24 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.0926 0.1043 2.35 2.65 -

A1 0.0040 0.0118 0.10 0.30 -

B 0.013 0.020 0.33 0.51 9

C 0.0091 0.0125 0.23 0.32 D 0.5985 0.6141 15.20 15.60 3

E 0.2914 0.2992 7.40 7.60 4

e 0.05 BSC 1.27 BSC -

H 0.394 0.419 10.00 10.65 -

h 0.010 0.029 0.25 0.75 5

L 0.016 0.050 0.40 1.27 6

N24 247

o

α

0

o

8

o

0

o

8

Rev. 0 12 /93

NOTESMIN MAX MIN MAX

-

16

HIN232 thru HIN241

Small Outline Plastic Packages (SOIC)

N

INDEX

AREA

123

SEATING PLANE

-AD

e

B

0.25(0.010) C AM BS

M

E

-B-

A

-C-

0.25(0.010) BM M

H

α

µ

A1

0.10(0.004)

L

h x 45

o

NOTES:

1. Symbol s are define d in the “MO Seri es Symb ol L ist” in S ection 2. 2

of Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimensio n “ D” does no t inc lu de m old f la sh, pro tru si on s or ga te

burrs. Mold flash, protrusion and gate burrs shall not exceed

0.15m m (0.006 inch) pe r sid e.

4. Dimension “E” does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010

inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual

index feature must be locat ed within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater

above the seating pl ane, shal l not exceed a maximum va lue of

0.61m m (0.024 inch)

10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M28.3 (JEDEC MS-013-AE ISSUE C)

28 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.0926 0.1043 2.35 2.65 -

A1 0.0040 0.0118 0.10 0.30 -

B 0.013 0.0200 0.33 0.51 9

C 0.0091 0.0125 0.23 0.32 D 0.6969 0.7125 17.70 18.10 3

E 0.2914 0.2992 7.40 7.60 4

e 0.05 BSC 1.27 BSC H 0.394 0.419 10.00 10.65 -

C

h 0.01 0.029 0.25 0.75 5

L 0.016 0.050 0.40 1.27 6

N28 287

o

α

0

o

8

o

0

o

8

Rev. 0 12 /93

NOTESMINMAXMINMAX

-

17

HIN232 thru HIN241

Shrink Small Outline Plastic Packages (SSO P)

N

INDEX

AREA

123

SEATING PLANE

-AD

e

B

0.25(0.010) C AM BS

M

E

-B-

A

-C-

0.25(0.010) BM M

H

α

µ

A1

0.10(0.004)

GAUGE

PLANE

0.25

0.010

A2

L

C

NOTES:

1. Symbols ar e def ined in the “MO Serie s Symbol List ” in Sec tion 2. 2

of Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimensio n “ D” does no t inc lu de m old f la sh, pro tru si on s or ga te

burrs. Mold flash, protrusion and gate burrs shall not exceed

0.20m m (0. 0 07 8 in ch) per side .

4. Dimension “E” does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.20mm (0.0078 inch)

per side.

5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. Dimension “B” does not include dambar protrusion. Allowable dambar pro trusion shall be 0 .1 3m m ( 0.0 05 inch) tot a l i n ex c es s o f “ B”

dimension at maximum mater ial condition.

10. Contro lling dime nsion: MILLIMETER. Converted inch dime nsions

are not necessarily exact.

M28.209 (JEDEC MO-150-AH ISSUE B)

28 LEAD SHRINK SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.078 - 2.00 A1 0.002 - 0.05 - A2 0.065 0.072 1.65 1.85 -

B 0.009 0.014 0.22 0.38 9

C 0.004 0.009 0.09 0.25 -

D 0.390 0.413 9.90 10.50 3

E 0.197 0.220 5.00 5.60 4

e 0.026 BSC 0.65 BSC -

H 0.292 0.322 7.40 8.20 -

L 0.022 0.037 0.55 0.95 6

N28 287

o

α

0

o

8

o

0

o

8

Rev. 1 3/95

NOTESMIN MAX MIN MAX

-

18

HIN232 thru HIN241

Metric Plastic Quad Flatpack Packages (MQFP)

E

E1

0.40

0.016

0o MIN

0o-7

-H-

-A-

o

MIN

D

D1

-D-

Q44.10x10 (JEDEC MS-022AB ISSUE B)

44 LEAD METRIC PLASTIC QUAD FLATPACK PACKAGE

INCHES MILLIMETERS

SYMBOL

NOTESMINMAXMINMAX

A - 0.096 - 2.45 -

A1 0.004 0.010 0.10 0.25 -

-B-

A2 0.077 0.083 1.95 2.10 -

b 0.012 0.018 0.30 0.45 6

b1 0.012 0.016 0.30 0.40 -

D 0.515 0.524 13.08 13.32 3

D1 0.389 0.399 9.88 10.12 4, 5

E 0.516 0.523 13.10 13.30 3

e

PIN 1

E1 0.390 0.398 9.90 10.10 4, 5

L 0.029 0.040 0.73 1.03 -

N44 447

e 0 .03 2 BSC 0. 80 BSC -

12o-16

A2

SEATING

PLANE

A

0.076

b1

0.003

-C-

b

o

A1

0.20

0.008

A-B SD SCM

NOTES:

1. Controlling dimension: MILLIMETER. Converted inch

dimensions are not necessarily exact.

2. All dimensions and tolerances per ANSI Y14.5M-1982.

3. Dimens ions D and E to be de ter mined at seat ing p lane .

4. Dimens ions D1 and E1 to be de ter mi ne d at da t um pl a ne

-H-

.

5. Dimens ions D1 an d E1 do no t i nclu de mol d pr otr u sion .

Rev. 2 4/9 9

-C-

Allowable protrusio n is 0.25mm (0.010 inch) per s ide.

0.13/0.17

o

L

12o-16

0.005/0.007

BASE METAL

WITH PLATING

0.13/0.23

0.005/0.009

6. Dimensio n b do es n ot i ncl ud e d amb ar p rot r us ion. A llow a ble

dambar protrusion shall be 0.08mm (0.003 inch) total.

7. “N” is the number of terminal positions.

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality cert if ications can be viewed at websit e www.intersil.com/quality/i so.asp

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice.

Accordingly, the reader i s cauti oned to ver ify that data sheet s are c urrent before pl acing orders . Information f urnis hed by Intersil is beli eved to be acc urate and r eliabl e. However, no responsibility is assumed by Intersil or its subsi d iaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

19

Loading...

Loading...