TM

www.BDTIC.com/Intersil

HI-574A, HI-674A

itle

I4A,

4A,

-

4)

bjec

omp

e,

-Bit

D

nver

s

th

crop

esso

erfa

utho

)

eyw

s

tersi

rpor

on,

ico

ucto

/D,

C,

sh,

nver

, bit,

le

dem

Data Sh eet June 200 1

Complete, 12-Bit A/D Converters with

Microprocessor Interface

The HI-X74(A) is a complete 12-bit, Analog-to-Digital

Converter, including a +10V reference clock, three-state

outputsand a digital i nterface for microprocessor control.

Successive approximation conversion is performed by two

monolithic dice housed in a 28 lead package. The bipolar

analog die features the Intersil Dielectric Isolation process,

which provides enhanced AC performance and freedom

from latch-up.

Custom design of each IC (bipolar analog and CMOS digital)

has yielded improved performance over existing versions of

this converter. The voltage comparatorfeatures high PSRR

plus a high speed current-mode latch, and provides precise

decisionsdown t o 0.1 LSB of input overdrive. More than 2X

reduction in noise has been achieved by using current

insteadof voltage for transmission of all signals between the

analog and digital ICs. Also, the clock oscillator is current

controlled for excellent stability over temperature.

The HI-X74(A) offers standard unipolar and bipolar input

ranges, laser trimmed for specified linearity,gain and offset

accuracy. The low noise buried zener reference c ircuit is

trimmed for minimum temperature coefficient.

Power requirements are +5V and ±12V to ±15V, with typical

dissipation of 385mW (HI-574A/674A) at 12V.

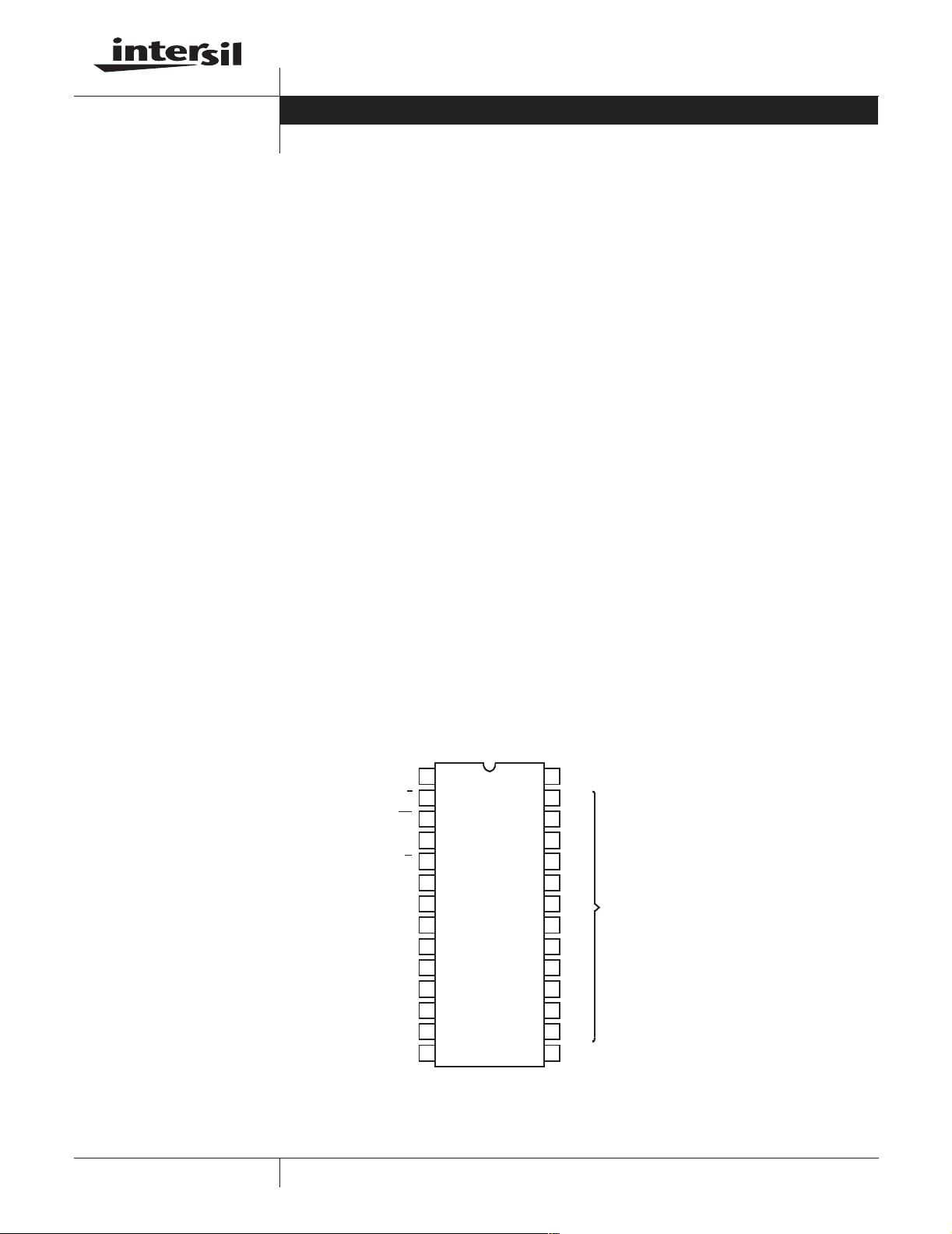

Pinout

+5V SUPPLY, V

DA TAMODE SEL, 12/8

CHIP SEL, CS

BYTEADDR/SHORT

CYCLE,A

READ/CONVERT, R/C

CHIP ENABLE, CE

+12V/+15V SUPPLY, V

+10VREF,REF OUT

ANALOG

COMMON,AC

REFERENCEINPUT

-12V/-15V SUPPLY, V

BIPOLAR OFFSET

BIP OFF

10V INPUT

20V INPUT

LOGIC

CC

EE

1

2

3

4

O

5

6

7

8

9

10

11

12

13

14

(PDIP, SBDIP)

TOP VIEW

File Number 3096.5

Features

• Complete 12-Bit A/D Converter with Reference and Clock

• Full 8-Bit, 12-Bit or 16-Bit Microprocessor Bus Interface

• BusAccessTime...........................150ns

• No Missing Codes Over Temperature

• Minimal Setup Time for Control Signals

• Fast Conversion Times

- HI-574A(Max) ............................25µs

- HI-674A(Max) ............................15µs

• Low Noise, via Current-Mode Signal Transmission

Between Chips

• Byte Enable/Short Cycle (A

O

Input)

- Guaranteed Break-Before-Make Action, Eliminating Bus

Contention During Read Operation. Latched by Start

Convert Input (T oSet the Conversion Length)

• Supply Voltage. ..................... ±12V to ±15V

Applications

• Military and Industrial Data Acquisition Systems

• Electronic Testand Scientific Instrumentation

• Process Control Systems

28

STATUS, STS

27

DB11

MSB

26

DB10

25

DB9

24

DB8

23

DB7

22

21

20

19

18

17

16

15

DIGITAL

DATA

DB6

OUTPUTS

DB5

DB4

DB3

DB2

DB1

DB0

LSB

DIG COMMON,

DC

1

1-888-INTERSIL or 321-724-7143

CAUTION: These devices aresensitiveto electrostatic discharge;followproperIC Handling Procedures.

| Intersil and Design is a trademark of IntersilAmericasInc. | Copyright © Intersil Americas Inc. 2001

HI-574A, HI-674A

www.BDTIC.com/Intersil

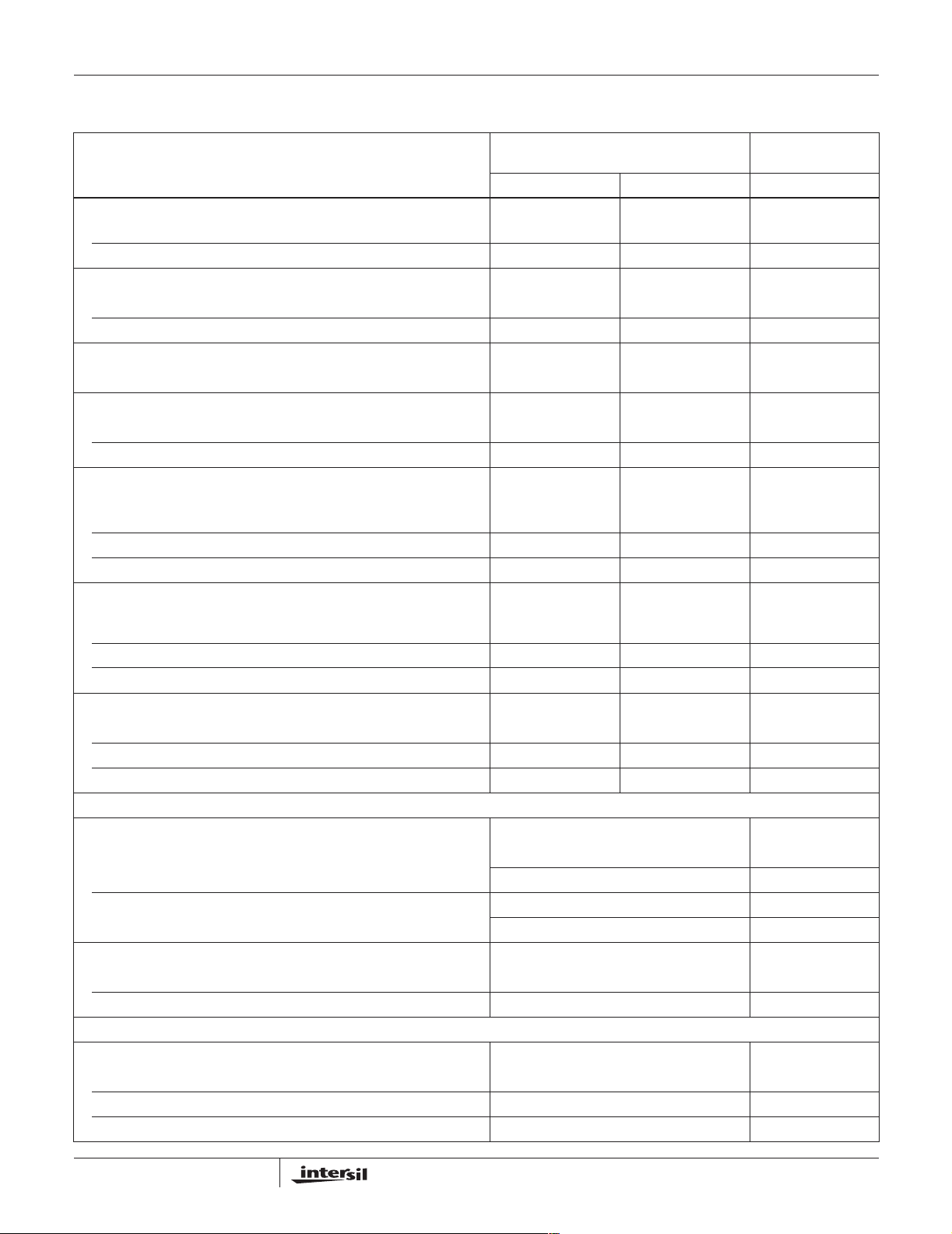

Ordering Information

PART NUMBER INL

HI3-574AJN-5 ±1.0LSB 0to75 28LdPDIP E28.6

HI3-574AKN-5 ±0.5LSB 0to75 28LdPDIP E28.6

HI1-574AJD-5 ±1.0LSB 0to75 28LdSBDIP D28.6

HI1-574AKD-5 ±0.5LSB 0to75 28LdSBDIP D28.6

HI1-574ASD-2 ±1.0LSB -55to125 28LdSBDIP D28.6

HI1-574ATD-2 ±0.5LSB -55to125 28LdSBDIP D28.6

HI1-574ASD/883 ±1.0LSB -55to125 28LdSBDIP D28.6

HI1-574ATD/883 ±0.5LSB -55to125 28LdSBDIP D28.6

HI3-674AJN-5 ±1.0LSB 0to75 28LdPDIP E28.6

HI3-674AKN-5 ±0.5LSB 0to75 28LdPDIP E28.6

HI1-674AJD-5 ±1.0LSB 0to75 28LdSBDIP D28.6

HI1-674AKD-5 ±0.5LSB 0to75 28LdSBDIP D28.6

HI1-674ASD-2 ±1.0LSB -55to125 28LdSBDIP D28.6

HI1-674ATD/883 ±0.5LSB -55to125 28LdSBDIP D28.6

TEMPERATURE RANGE

(oC) PACKAGE PKG. NO.

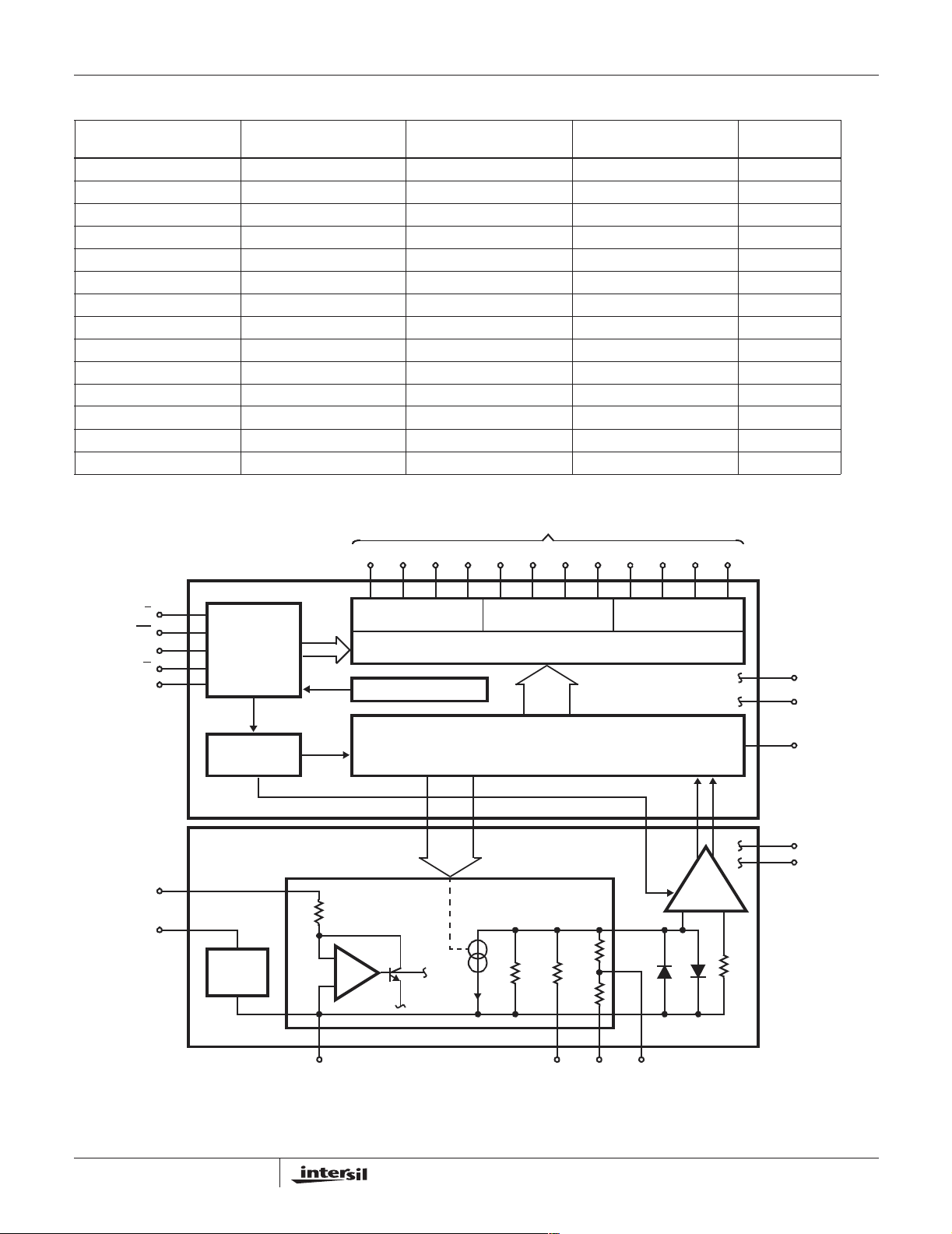

Functional Block Diagram

BIT OUTPUTS

MSB LSB

12/8

CS

A

O

R/C

CE

IN

V

REF

V

OUT

REF

CONTROL

LOGIC

OSCILLATOR

DIGITAL CHIP

ANALOG CHIP

+10V

REF

THREE-STATE BUFFERS AND CONTROL

POWER-UP RESET

CLK

12 BITS

10K

+

-

5K

NIBBLE B (NOTE) NIBBLE C (NOTE)NIBBLE A (NOTE)

12 BITS

SAR

DAC

10K

STROBE

5K

5K

-

COMP

+

2.5K

V

LOGIC

DIGITAL

COMMON

STS

V

CC

V

EE

ANALOG

COMMON

BIP

OFF

INPUT

INPUT

10V

20V

NOTE: “Nibble”is a 4-bit digital w ord.

2

HI-574A, HI-674A

www.BDTIC.com/Intersil

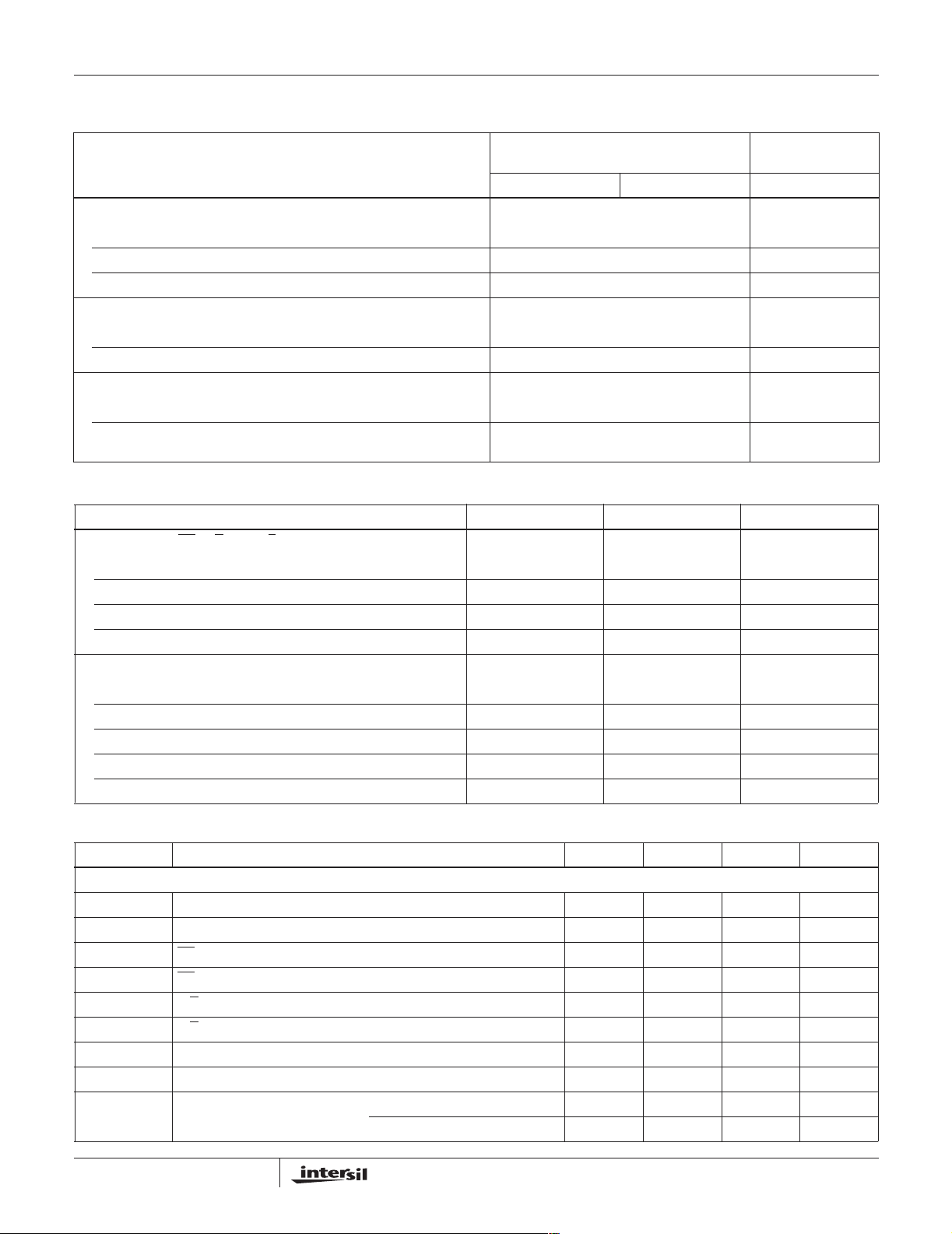

Absolute M axi m um Rati ng s Thermal Information

Supply Voltage

toDigitalCommon......................0Vto+16.5V

V

CC

toDigitalCommon.......................0Vto-16.5V

V

EE

V

toDigitalCommon ......................0Vto+7V

LOGIC

Analog Common to Digital Common. . . . . . . . . . . . . . . . . . . . . . ±1V

Control Inputs

Analog Inputs

REFOUT.....Indefinite Short ToCommon, Momentary Short To V

,AO,12/8,R/C) to Digital Common . . -0.5V to V

(CE, CS

(REFIN,BIPOFF,10VIN)toAnalogCommon..........±16.5V

20VINtoAnalogCommon..........................± 24V

LOGIC

+0.5V

CC

Operating Conditions

TemperatureRange

HI3-574Axx-5,HI1-674Axx-5...................0

HI1-574AxD-2,HI1-674AxD-2............... -55

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationofthe

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θ

is measured with the component mountedon a low effectivethermalconductivity test boardin free air. See Tech B rief TB379 for details.

JA

o

Cto75oC

o

Cto125oC

Thermal Resistance (Typical, Note 1) θ

SBDIPPackage.................. 55 18

PDIPPackage................... 60 N/A

Maximum JunctionTemperature

PDIPPackage...................................150

SBDIPPackage..................................175

Maximum Storage TemperatureRange

PDIPPackage.............................-40

SBDIPPackage...........................-65

MaximumLeadTemperature(Soldering,10s)............300

(oC/W) θJC(oC/W)

JA

o

Cto85oC

o

Cto150oC

Die Characteristics

TransistorCount

HI-574A,HI-674A..................................1117

o

C

o

C

o

C

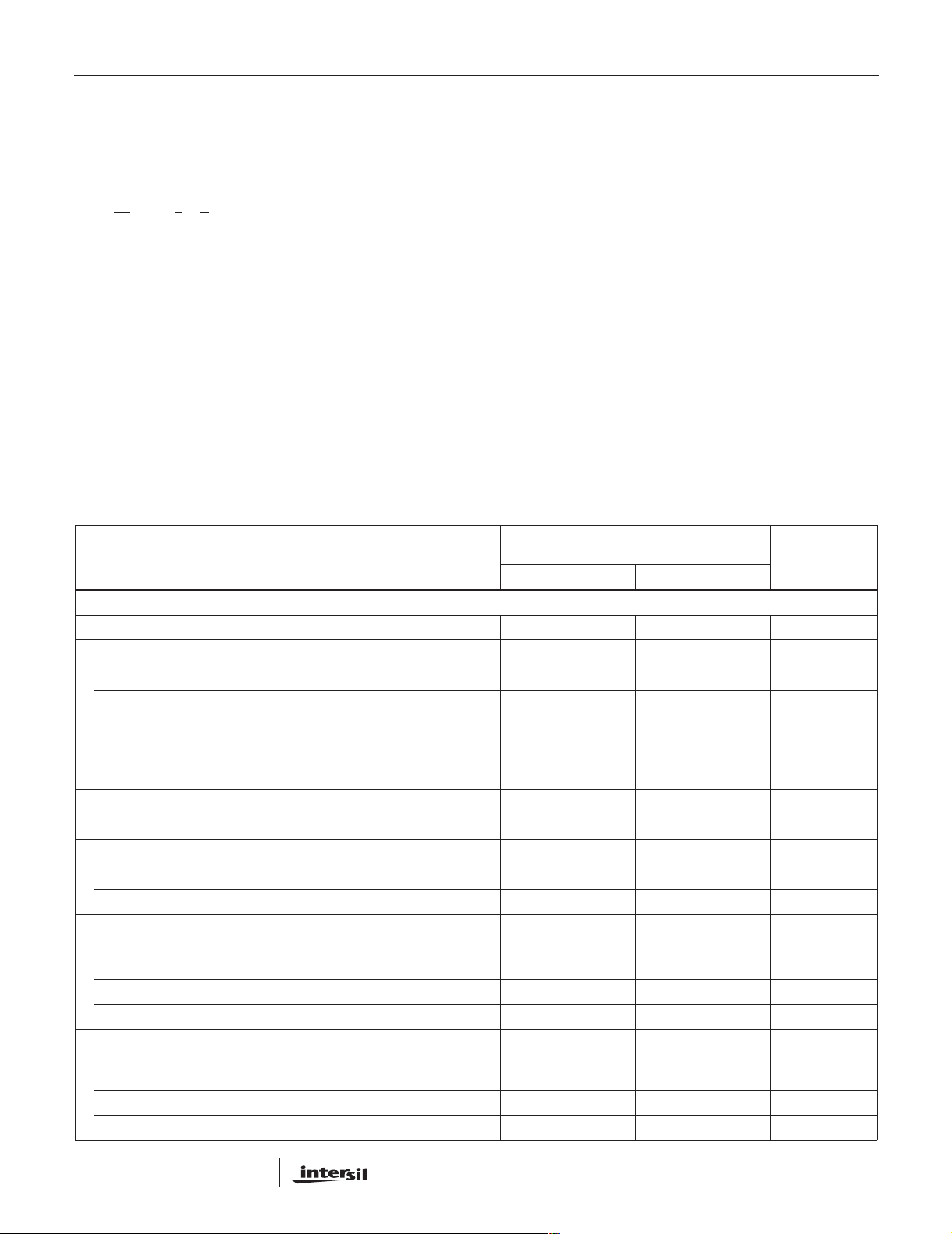

DC and Transfer Accuracy Specifications Typical at 25

UnlessOtherwise Specified

PARAMETER

DYNAMIC CHARACTERISTICS

Resolution (Max) 12 12 Bits

Linearity Error

o

25

C(Max) ±1 ±1/

o

0

Cto75oC(Max) ±1 ±1/

Max Resolution For Which No Missing Codes Is Guaranteed

o

25

C 12 12 Bits

T

to T

MIN

MAX

Unipolar Offset (Max)

Adjustable to Zero ±2 ±1.5 LSB

Bipolar Offset (Max)

V

= 0V (Adjustable to Zero) ±4 ±4LSB

IN

VIN=-10V ±0.15 ±0.1 % of FS

Full Scale Calibration Error

o

25

C (Max), With Fixed 50Ω Resistor From REF OUT To REF IN

(Adjustableto Zero)

to T

T

MIN

T

to T

MIN

Temperature Coefficients

Guaranteed Max Change, T

Unipolar Offset ±2 ±1LSB

Bipolar Offset ±2 ±1LSB

Full Scale Calibration ±9 ±2LSB

(No Adjustment At 25oC) ±0.475 ±0.375 %of FS

MAX

(WithAdjustment To Zero 25oC) ±0.22 ±0.12 % of FS

MAX

MIN

to T

(Using Internal Reference)

MAX

o

CwithVCC= +15V or +12V, V

TEMPERATURE RANGE

-5 (0

11 12 Bits

±0.25 ±0.25 % of FS

LOGIC

o

Cto75oC)

=+5V,VEE=-15Vor-12V,

UNITSJ SUFFIX K SUFFIX

2

2

LSB

LSB

3

HI-574A, HI-674A

www.BDTIC.com/Intersil

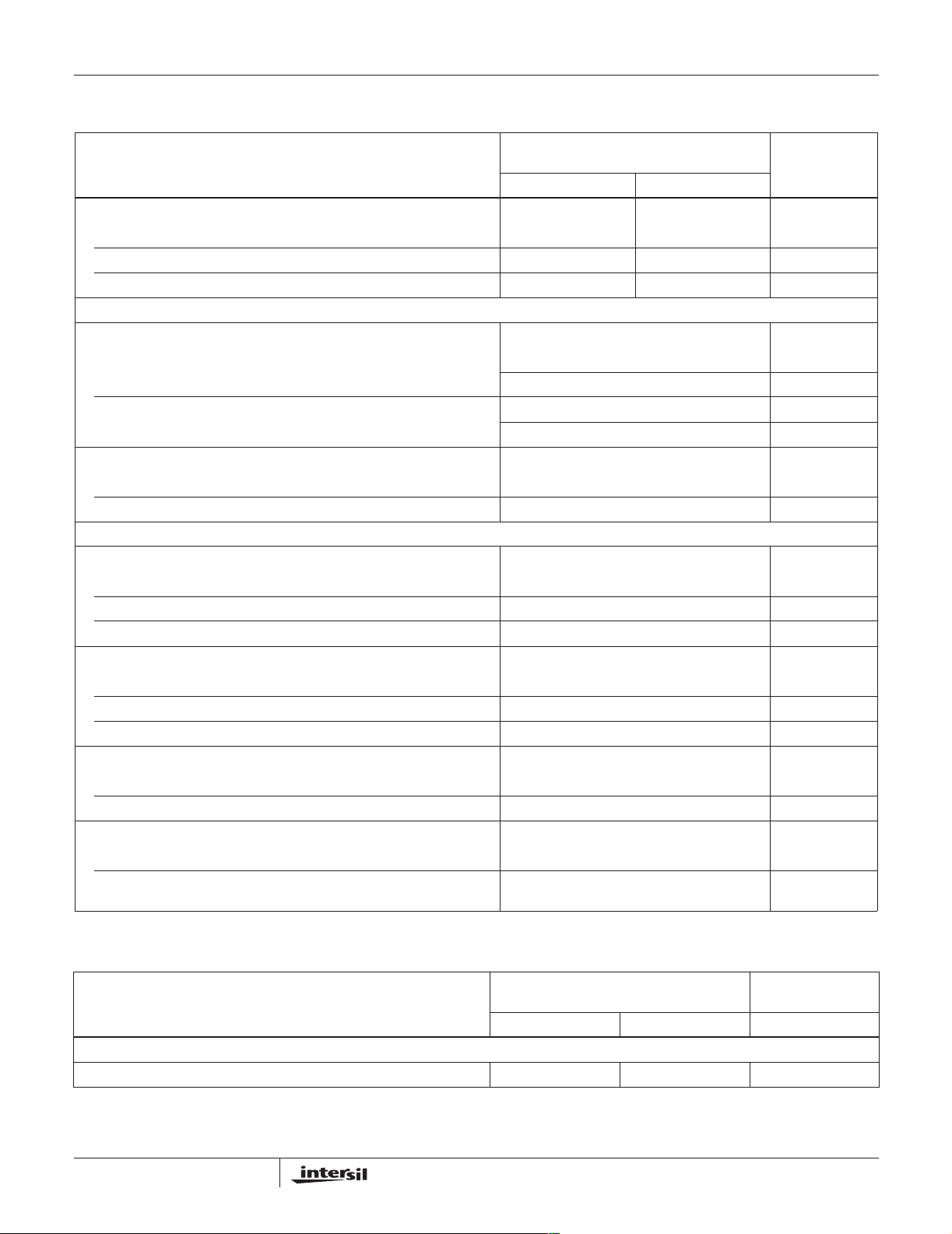

DC and Transfer Accuracy Specifications Typical at 25

UnlessOtherwise Specified (Continued)

PARAMETER

Power Supply Rejection Max Change In Full ScaleCalibration

+13.5V < V

+4.5V < V

-16.5V< VEE< -13.5Vor -12.6V < VEE<-11.4V ±2 ±1LSB

ANALOG INPUTS

Input Ranges

Bipolar -5 to +5 (Note 3) V

Unipolar 0to+10(Note3) V

Input Impedance

10V Span 5K, ±25% Ω

20V Span 10K, ±25% Ω

POWER SUPPLIES

Operating Voltage Range

V

LOGIC

V

CC

V

EE

Operating Current

I

LOGIC

I

+15V Supply 11 Typ, 15 Max mA

CC

IEE-15V Supply 21 Typ, 28 Max mA

Power Dissipation

±15V, +5V 515 Typ, 720 Max mW

±12V, +5V 385 Typ mW

Internal Reference Voltage

T

to T

MIN

Output Current, Available For External Loads (External Load Should Not

Change During Conversion).

< +16.5V or +11.4V < VCC<+12.6V ±2 ±1LSB

CC

<+5.5V ±1/

LOGIC

MAX

o

CwithVCC= +15V or +12V, V

TEMPERATURE RANGE

-5 (0

2

-10 to +10 (Note 4) V

0to+20(Note4) V

+4.5to +5.5 V

+11.4to+16.5 V

-11.4to-16.5 V

7Typ,15Max mA

+10.00 ±0.05 Max V

=+5V,VEE=-15Vor-12V,

LOGIC

o

Cto75oC)

UNITSJ SUFFIX K SUFFIX

±1/

2

2.0 Max mA

LSB

8

DC and Transfer Accuracy SpecificationsTypical at 25

UnlessOtherwise Specified (Continued)

PARAMETER

DYNAMIC CHARACTERISTICS

Resolution (Max) 12 12 Bits

o

CwithVCC= +15V or +12V, V

TEMPERATURE RANGE

-2 (-55

S SUFFIX T SUFFIX UNITS

LOGIC

o

Cto125oC)

=+5V,VEE=-15Vor-12V,

4

HI-574A, HI-674A

www.BDTIC.com/Intersil

DC and Transfer Accuracy SpecificationsTypical at 25

UnlessOtherwise Specified (Continued)

PARAMETER

Linearity Error

o

25

C ±1 ±1/

o

-55

Cto125oC(Max) ±1 ±1LSB

Max ResolutionFor Which No Missing Codes Is Guaranteed

o

25

C 12 12 Bits

T

to T

MIN

MAX

Unipolar Offset ( Max)

Adjustable to Zero ±2 ±1.5 LSB

Bipolar Offset (Max)

V

= 0V (Adjustable to Zero) ±4 ±4LSB

IN

=-10V ±0.15 ±0.1 % of FS

V

IN

Full Scale Calibration Error

o

25

C(Max),WithFixed50Ω Resistor From REF OUT To REF IN

(Adjustable To Zero)

to T

T

MIN

T

to T

MIN

Temperature Coefficients

Guaranteed Max Change,T

Unipolar Offset ±2 ±1LSB

Bipolar Offset ±2 ±2LSB

Full Scale Calibration ±20 ±10 LSB

Power Supply RejectionMax Change In Full Scale Calibration

+13.5V< V

+4.5V< V

-16.5V < V

ANALOG INPUTS

InputRanges

Bipolar -5 to +5 (Note 3) V

Unipolar 0to+10(Note3) V

Input Impedance

10V Span 5K, ±25% Ω

20V Span 10K, ±25% Ω

POWER SUPPLIES

Operating Voltage Range

V

LOGIC

V

CC

V

EE

(No Adjustment At 25oC) ±0.75 ±0.50 % of FS

MAX

(With Adjustment To Zero At 25oC) ±0.50 ±0.25 % of FS

MAX

to T

MIN

< +16.5V or +11.4V < VCC<+12.6V ±2 ±1LSB

CC

< +5.5V ±1/

LOGIC

< -13.5V or -12.6V < VEE<-11.4V ±2 ±1LSB

EE

(Using Internal Reference)

MAX

o

CwithVCC= +15V or +12V, V

TEMPERATURE RANGE

-2 (-55

S SUFFIX T SUFFIX UNITS

11 12 Bits

±0.25 ±0.25 % of FS

2

-10to+10(Note4) V

0to+20(Note4) V

+4.5 to +5.5 V

+11.4to+16.5 V

-11.4to-16.5 V

LOGIC

o

Cto125oC)

=+5V,VEE=-15Vor-12V,

2

±1/

2

LSB

LSB

5

HI-574A, HI-674A

www.BDTIC.com/Intersil

DC and Transfer Accuracy SpecificationsTypical at 25

UnlessOtherwise Specified (Continued)

PARAMETER

Operating Current

I

LOGIC

I

+15V Supply 11 Typ, 15 Max mA

CC

IEE-15V Supply 21 Typ, 28 Max mA

Power Dissipation

±15V, +5V 515 Typ, 720 Max mW

±12V, +5V 385 Typ mW

Internal Reference Voltage

T

to T

MIN

MAX

Output current, available for external loads (external load should not

change duringconversion).

o

CwithVCC= +15V or +12V, V

TEMPERATURE RANGE

-2 (-55

S SUFFIX T SUFFIX UNITS

7Typ,15Max mA

+10.00±0.05 Max V

=+5V,VEE=-15Vor-12V,

LOGIC

o

Cto125oC)

2.0 Max mA

Digital Specifications All Models, Over Full T emperature Range

PARAMETER MIN TYP MAX

LogicInputs (CE, CS

Logic “1” +2.4V - +5.5V

Logic “0” -0.5V - +0.8V

Current - ±0.1µA ±5µA

Capacitance - 5pF -

LogicOutputs(DB11-DB0, STS)

Logic “0” (I

Logic “1” (I

Logic “1” (I

Leakage (High-Z State, DB11-DB0 Only) - ±0.1µA ±5µA

Capacitance - 5pF -

,R/C,AO,12/8)

- 1.6mA) - - +0.4V

SINK

SOURCE

SOURCE

-500µA) +2.4V - -

-10µA) +4.5V - -

Timing Specification s (HI-574A)25

SYMBOL PARAMETER MIN TYP MAX UNITS

CONVERT MODE

t

DSC

t

HEC

t

SSC

t

HSC

t

SRC

t

HRC

t

SAC

t

HAC

t

C

STS Delay from CE - - 200 ns

CE Pulse Width 50 - - ns

CSto CE Setup 50 - - ns

CSLow During CE High 50 - - ns

R/Cto CE Setup 50 - - ns

R/CLow During CE High 50 - - ns

AOto CE Setup 0 - - ns

AOValidDuringCEHigh 50 - - ns

Conversion T ime 12-Bit Cycle T

o

C, Note 2, Unless Other wise Specified

to T

MIN

MAX

8-Bit Cycle T

MIN

to T

MAX

15 20 25 µs

10 13 17 µs

6

Loading...

Loading...