Intersil Corporation HI5710A Datasheet

HI5710A

August 1997

Features

• Resolution ±0.5 LSB (DNL) . . . . . . . . . . . . . . . . . . 10-Bit

• Maximum Sampling Frequency . . . . . . . . . . . 20 MSPS

• Low Power Consumption

(Reference Current Excluded) . . . . . . . . . . . . . .150mW

• Standby Mode Power . . . . . . . . . . . . . . . . . . . . . . .5mW

• No Sample and Hold Required

• TTL Compatible Inputs

• Three-State TTL Compatible Outputs

• Single +5V Analog Power Supply

• Single +3.3V or +5V Digital Power Supply

Applications

• Video Digitizing - Multimedia

• Data Communications

• Image Scanners

• Medical Imaging

• Video Recording Equipment

• Camcorders

• QAM Demodulation

10-Bit, 20 MSPS A/D Converter

Description

The HI5710A is a low power, 10-bit, CMOS analog-to-digital

converter. The use of a 2-step architecture realizes low

power consumption, 150mW, and a maximum conversion

speed of 20MHz with only a 3 clock cycle data latency. The

HI5710A can be powered down, disabling the chip and the

digital outputs, reducing power to less than 5mW. A built-in,

user controllable, calibration circuit is used to provide low

linearity error, 1 LSB. The low power, high speed and small

package outline make the HI5710A an ideal choice for CCD,

battery, and high channel count applications.

The HI5710A does not require an external sample and hold

but requires an external reference and includes force and

sense reference pins for increased accuracy. The digital outputs can be inverted, with the MSB controlled separately,

allowing for various digital output formats. The HI5710A

includes a test mode where the digital outputs can be set to

a fixed state to ease in-circuit testing.

Ordering Information

TEMP.

PART NO.

HI5710AJCQ -20 to 75 48 Ld MQFP Q48.7x7-S

RANGE (oC) PACKAGE PKG. NO.

Pinout

DV

DV

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

SS

DD

SS

NC

DV

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16

TO

TIN

HI5710A (MQFP)

TOP VIEW

DD

SS

SS

AV

SEL

TS

AV

DD

AV

TESTMODE

NC

DV

SS

DV

RESET

CAL

LINV

NC

MINV

IN

V

CLK

AT

OE

373839404142434445464748

2423222120191817

TSTR

36

35

34

33

32

31

30

29

28

27

26

25

CE

AVss

V

RB

V

RB

NC

NC

NC

V

RT

V

RT

AV

AV

AV

AV

SS

SS

DD

DD

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

4-1531

File Number 3921.5

Functional Block Diagram

HI5710A

V

V

RT

V

RT

V

RB

V

RB

CLK

OE

CE

39

IN

29

30

34

35

22

23

24

S/H

AMP

COURSE

COMPARATOR

AND

ENCODE

TIMING GEN

+

∑

DAC

8 x

-

CALIBRATION

UNIT

FINE

COMPARATOR

AND

ENCODE

AUTO CALIBRATION

PULSE GENERATOR

COURSE

CORRECTION

AND

LATCH

FINE

LATCH

12

D9 (MSB)

11

D8

10

D7

9

D6

8

D5

5

D4

4

D3

3

D2

2

D1

1

D0 (LSB)

21

MINV

20

LINV

19

TESTMODE

41

CAL

17

SEL

15

RESET

4-1532

HI5710A

Absolute Maximum Ratings T

Supply Voltage, AVDD, DVDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7V

Reference Voltage, VRT, VRB . . . . . . . . . VDD + 0.5V to VSS - 0.5V

Analog Input Voltage, VIN. . . . . . . . . . . . . VDD + 0.5V to VSS - 0.5V

Digital Input Voltage, VIH, VIL. . . . . . . . . . VDD + 0.5V to VSS - 0.5V

Digital Output Voltage, VOH, VOL. . . . . . . VDD + 0.5V to VSS - 0.5V

=25oC Thermal Information

A

Thermal Resistance (Typical, Note 1) θJA (oC/W)

MQFP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range, T

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

(Lead Tips Only)

. . . . .-65oC to 150oC

STG

Operating Conditions

Supply Voltage

AVDD, AVSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +5V ±0.25V

DVDD, DVSS. . . . . . . . . . . . . . . . . . . . . . . . . .+3.3V to 5V ±0.25V

|DGND-AGND| . . . . . . . . . . . . . . . . . . . . . . . . . . . .0mV to 100mV

Reference Input Voltage

VRB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.8V to 2.8V

VRT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3.6V to 4.6V

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

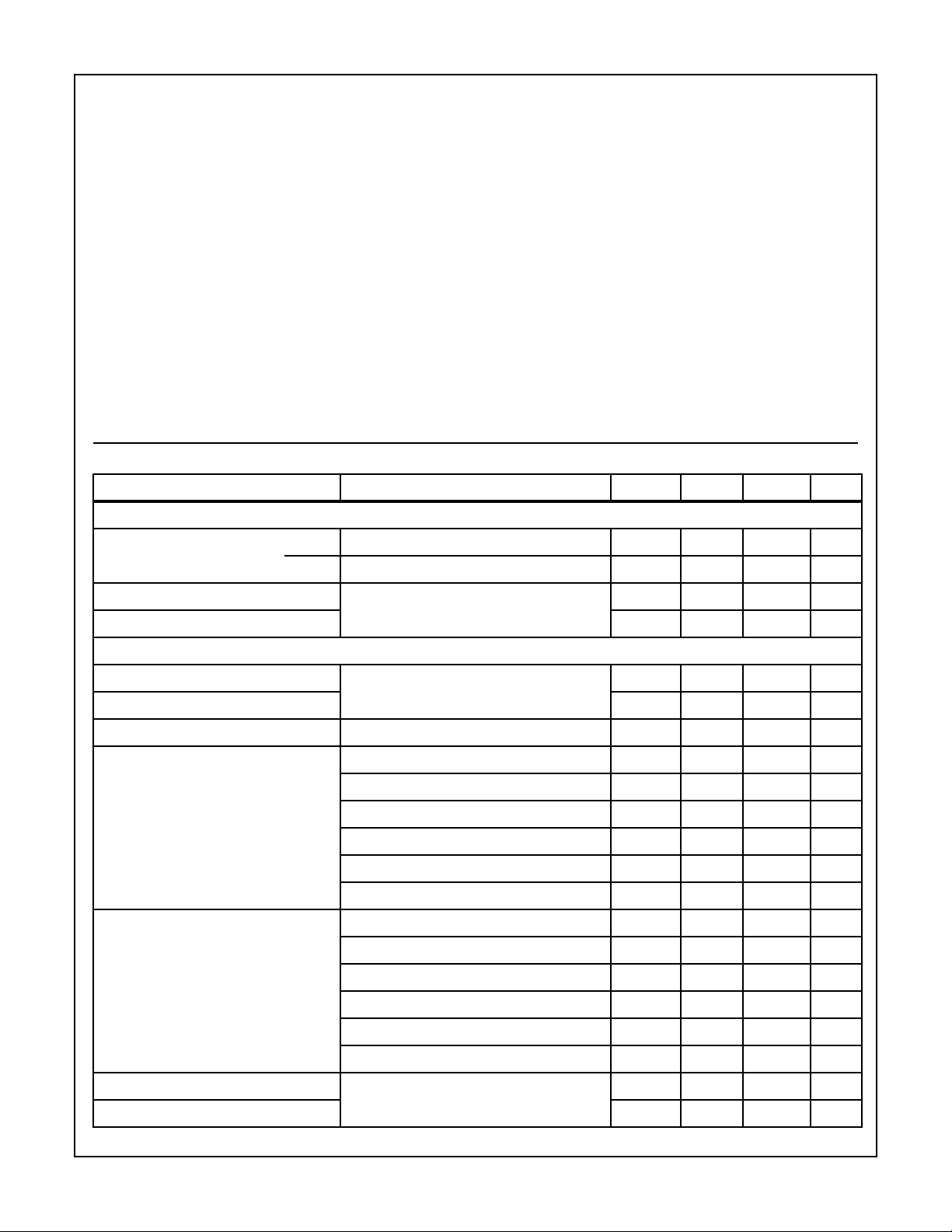

Electrical Specifications f

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SYSTEM PERFORMANCE

Offset Voltage E

Integral Non-Linearity, INL VIN = 2.0V to 4.0V - ±1.3 ±2.0 LSB

= 20 MSPS, AVDD = +5V, DVDD = +3.3V, VRB = 2.0V, VRT = 4.0V, TA = 25oC (Note 2)

C

OT

E

OB

Analog Input Range, VIN. . . . . . . .(VRT - VRB) (1.8V

Clock Pulse Width

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25ns (Min)

PW1

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25ns (Min)

PW0

Temperature, TA . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-20oC to 75oC

40 90 140 mV

-120 -70 -20 mV

P-P

to 2.8V

P-P

)

Differential Non-Linearity, DNL - ±0.5 ±1.0 LSB

DYNAMIC CHARACTERISTICS

Maximum Conversion Speed, f

Minimum Conversion Speed, f

Effective Number of Bits, ENOB fIN = 3MHz - 8.7 - BIts

Signal to Noise and Distortion, SINAD fIN = 100kHz - 53 - dB

Spurious Free Dynamic Range, SFDR fIN = 100kHz - 60 - dB

C

C

fIN = 1kHz Ramp 20 - - MSPS

- - 0.5 MSPS

fIN = 500kHz - 52 - dB

fIN = 1MHz - 53 - dB

fIN = 3MHz - 54 - dB

fIN = 7MHz - 47 - dB

fIN = 10MHz - 45 - dB

fIN = 500kHz - 59 - dB

fIN = 1MHz - 60 - dB

fIN = 3MHz - 65 - dB

fIN = 7MHz - 50 - dB

fIN = 10MHz - 49 - dB

Differential Gain Error, DG NTSC 40 IRE Mod Ramp, fC = 14.3 MSPS - 1.0 - %

Differential Phase Error, DP - 0.3 - Degree

4-1533

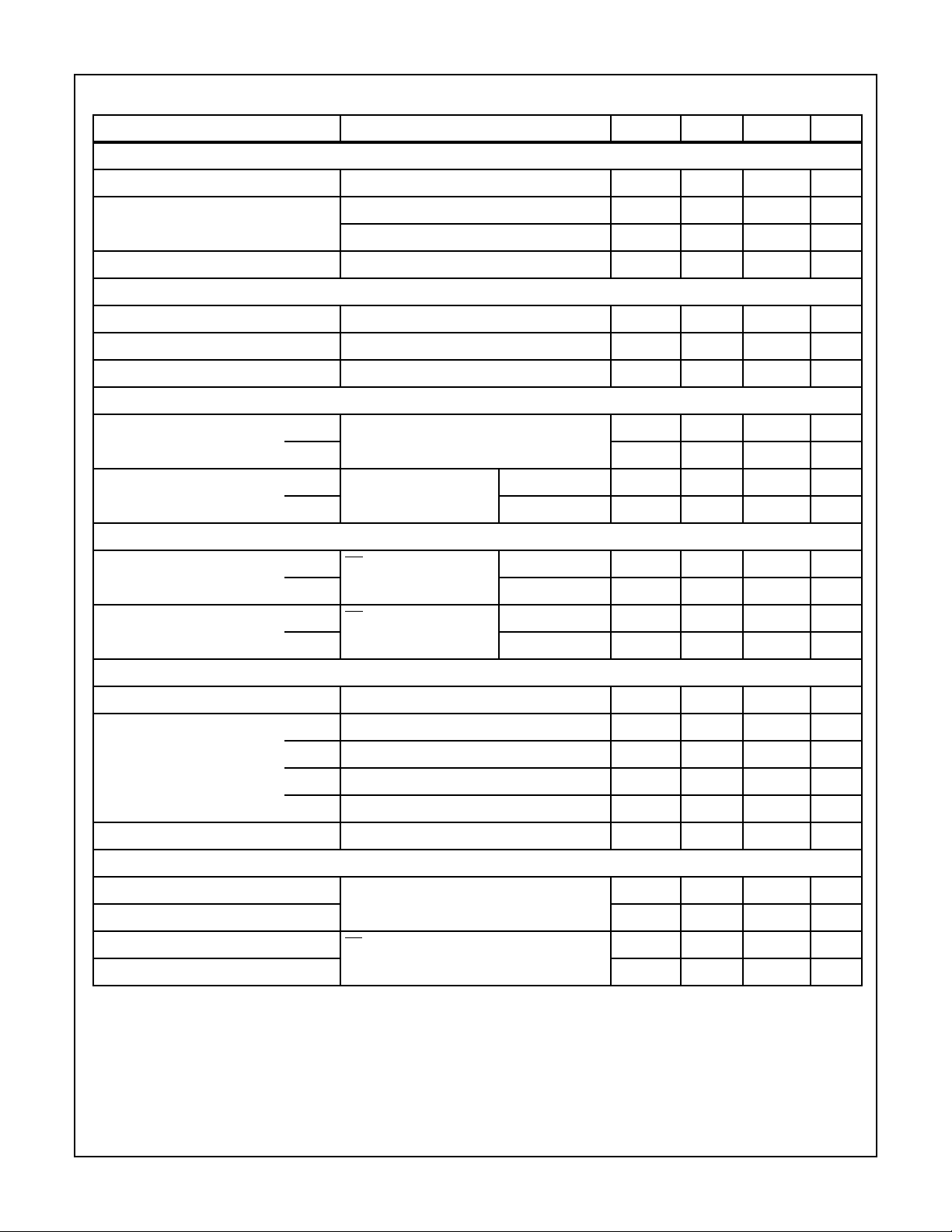

HI5710A

Electrical Specifications f

= 20 MSPS, AVDD = +5V, DVDD = +3.3V, VRB = 2.0V, VRT = 4.0V, TA = 25oC (Note 2) (Continued)

C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

ANALOG INPUTS

Analog Input Bandwidth (-3dB), BW - 100 - MHz

Analog Input Current VIN = 4V - - 50 µA

VIN = 2V -50 - - µA

Analog Input Capacitance, C

IN

VIN = 2.5V + 0.07V

RMS

-9-pF

REFERENCE INPUT

Reference Pin Current, I

Reference Pin Current, I

RT

RB

Reference Resistance (VRT to VRB), R

RESET = Low 5 7 11 mA

RESET = Low -11 -7 -5 mA

REF

180 280 380 Ω

DIGITAL INPUTS

Digital Input Voltage V

Digital Input Current I

IH

V

IL

IH

I

IL

AVDD = 4.75V to 5.25V 2.3 - - V

- - 0.80 V

DVDD = Max VIH = DV

DD

--5µA

VIL = 0V - - 5 µA

DIGITAL OUTPUTS

Digital Output Current I

Digital Output Leakage Current I

OH

I

OL

OZH

I

OZL

OE = AVSS, DVDD = Min VOH = DVDD -0.5V 3.5 - - mA

VOL = 0.4V 3.5 - - mA

OE = AVDD, DVDD = Max VOH = DV

DD

--1µA

VOL = 0V - - 1 µA

TIMING CHARACTERISTICS

Output Data Delay, t

DL

Output Enable/Disable Delay t

Sampling Delay, t

SD

PZL

t

PLZ

t

PZH

t

PHZ

Load is One TTL Gate 8 13 18 ns

10 15 20 ns

20 25 30 ns

10 15 20 ns

20 25 30 ns

246ns

POWER SUPPLY CHARACTERISTIC

Analog Supply Current, IA

Digital Supply Current, ID

DD

DD

fIN = 1kHz Ramp Wave Input 20 27 34 mA

-35mA

Analog Standby Current CE = High - - 1.0 mA

Digital Standby Current - - 1.0 µA

NOTE:

2. Electrical specifications guaranteed only under the stated operating conditions.

4-1534

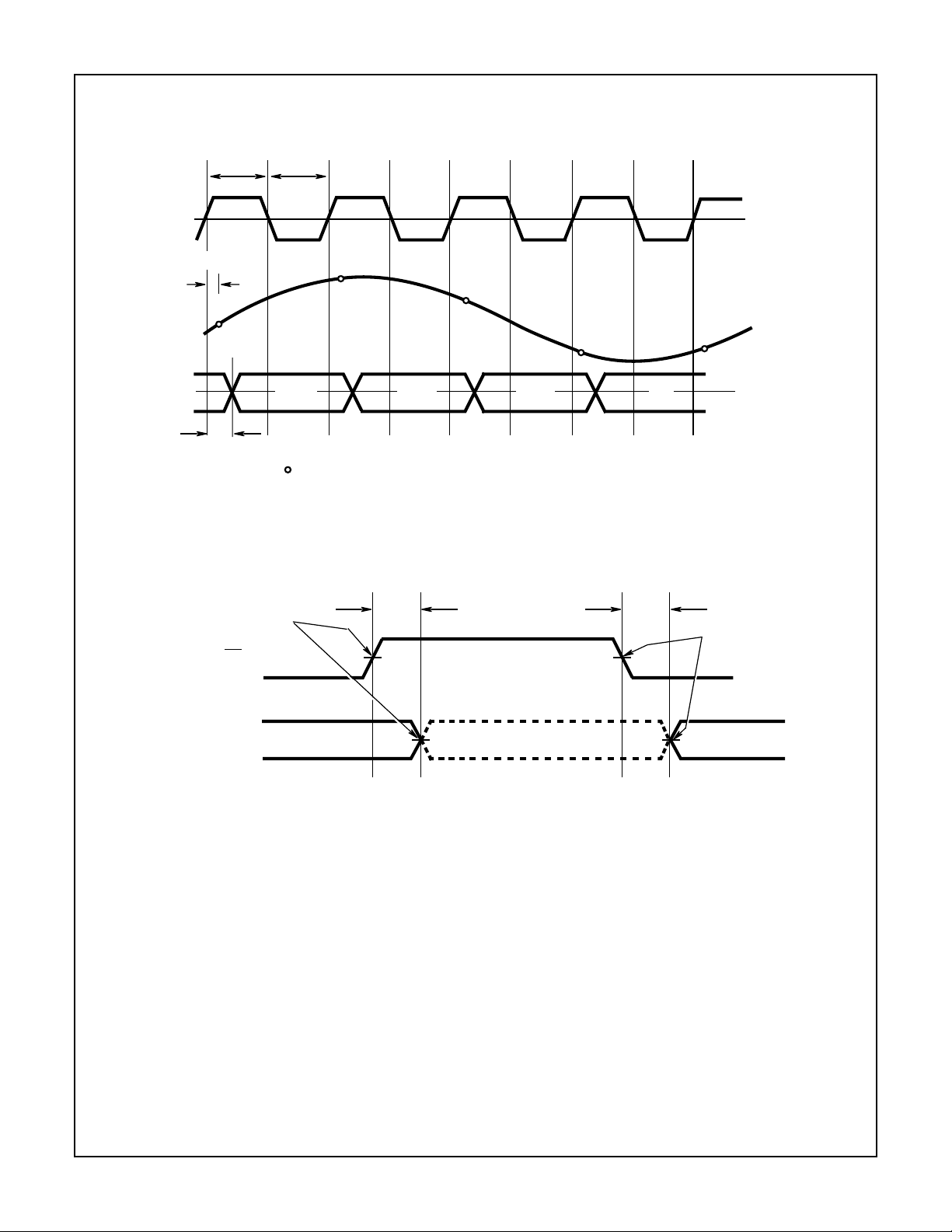

Timing Diagrams

HI5710A

CLOCK

ANALOG INPUT

DATA OUTPUT

OUTPUT ENABLE (

t

PW1

t

SD

N

t

DL

1.65V (DVDD = 3.3V)

2.5V (DV

OE)

DD

= 5.0V)

t

PW0

N + 1

N - 3 N - 2 N - 1 N

= INDICATES POINT AT WHICH ANALOG DATA IS SAMPLED

N + 2

N + 3

FIGURE 1.

t

PLZ

t

PHZ

t

t

PZL

PZH

1.65V1.65V

N + 4

1.65V (DV

2.5V (DVDD = 5.0V)

1.65V (DVDD = 3.3V)

2.5V (DV

DD

= 5.0V)

DD

= 3.3V)

DATA OUTPUT ACTIVE HIGH IMPEDANCE

FIGURE 2.

4-1535

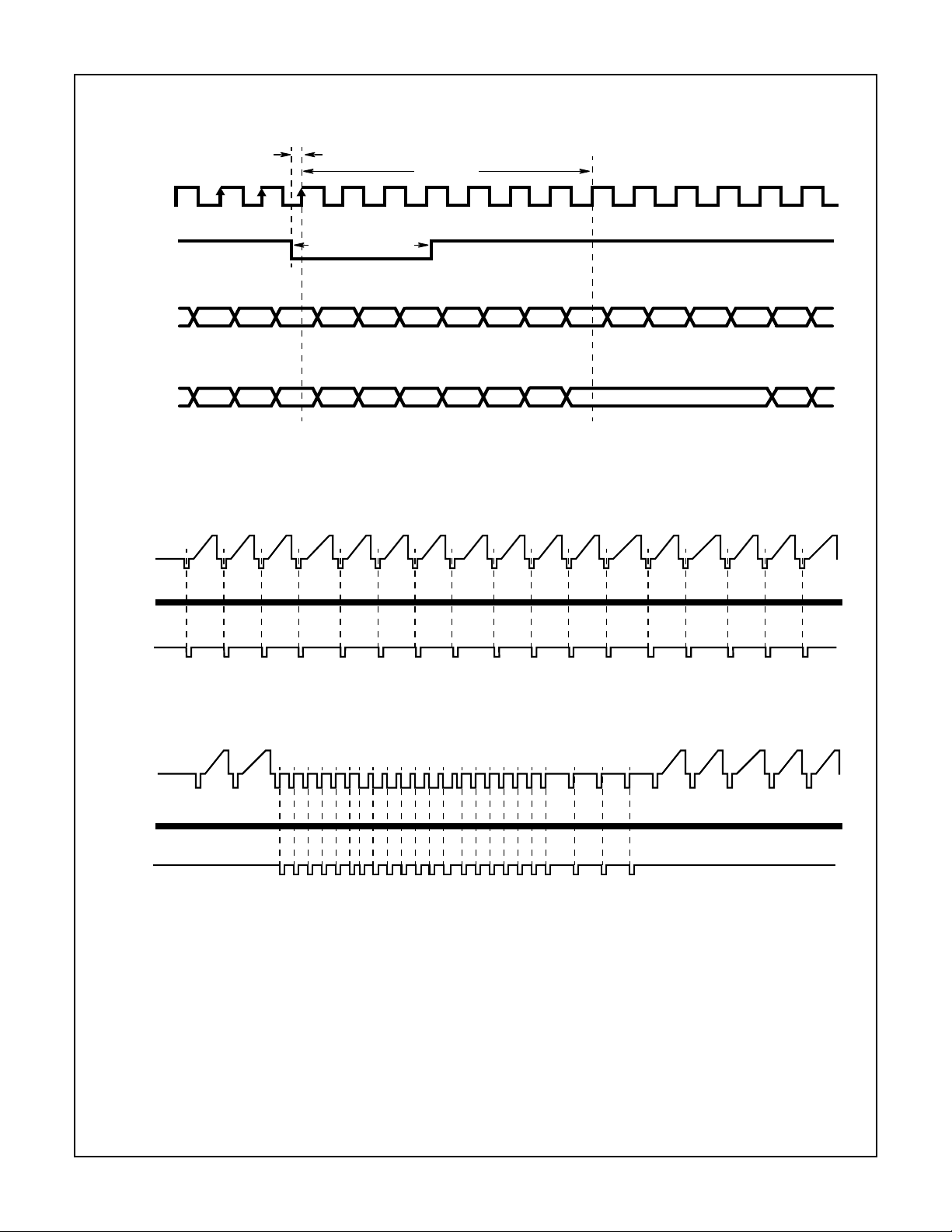

Calibration Timing Diagrams

10ns

OR MORE

CLK

HI5710A

7 CLOCKS

CAL

D5 TO D9

D0 TO D4

INPUT

CLK

CAL

1 CLOCK OR MORE

FIGURE 3. EXTERNAL CALIBRATION PULSE TIMING DIAGRAM

FIGURE 4A. CALIBRATION DURING H SYNC

INPUT

CLK

CAL

FIGURE 4B. CALIBRATION DURING V SYNC

FIGURE 4. EXAMPLES OF EXTERNAL CALIBRATION PULSE INPUT FOR VIDEO APPLICATIONS

4-1536

Loading...

Loading...