Intersil Corporation HI-549, HI-547, HI-546 Datasheet

HI-546, HI-547, HI-548, HI-549

Data Sheet June 1999

Single 16 and 8, Differential 8-Channel

and 4-Channel CMOS Analog MUXs with

Active Overvoltage Protection

The HI-546, HI-547, HI-548 and HI-549 are analog

multiplexers with active overvoltage protection and

guaranteed r

exceed either power supply without damaging the device or

disturbing the signal path of other channels. Active

protection circuitry assures that signal fidelity is maintained

even under fault conditions that would destroy other

multiplexers.

Analog inputs can withstand constant 70V

±15V supplies. Digital inputs will also sustain continuous

faults up to 4V greater than either supply. In addition, signal

sources are protected from short circuiting should

multiplexer supply loss occur. Each input presents 1kΩ of

resistance under this condition. These features make the

HI-546, HI-547, HI-548 and HI-549 ideal for use in systems

where the analog inputs originate from external equipment

or separately powered circuitry. All devices are fabricated

with 44V Dielectrically Isolated CMOS technology. The

HI-546 is a single 16-Channel, the HI-547 is an 8-Channel

differential, the HI-548 is a single 8-Channel and the HI-549

is a 4-Channel differential device. If input overvoltage

protection is not needed the HI-506/507/508/509

multiplexers are recommended. For further information see

Application Notes AN520 and AN521.

For MIL-STD-883 compliant parts, request the HI-546/883,

HI-547/883, HI-548/883 and HI-549/883 datasheets.

matching. Analog input levels may greatly

ON

levels with

P-P

File Number

3150.2

Features

• Analog Overvoltage Protection. . . . . . . . . . . . . . . . . . 70V

• No Channel Interaction During Overvoltage

• Guaranteed r

Matching

ON

• Maximum Power Supply. . . . . . . . . . . . . . . . . . . . . . . 44V

• Break-Before-Make Switching

• Analog Signal Range . . . . . . . . . . . . . . . . . . . . . . . . ±15V

• Access Time (Typical) . . . . . . . . . . . . . . . . . . . . . . .500ns

• Standby Power (Typical). . . . . . . . . . . . . . . . . . . . . 7.5mW

P-P

Applications

• Data Acquisition

• Industrial Controls

• Telemetry

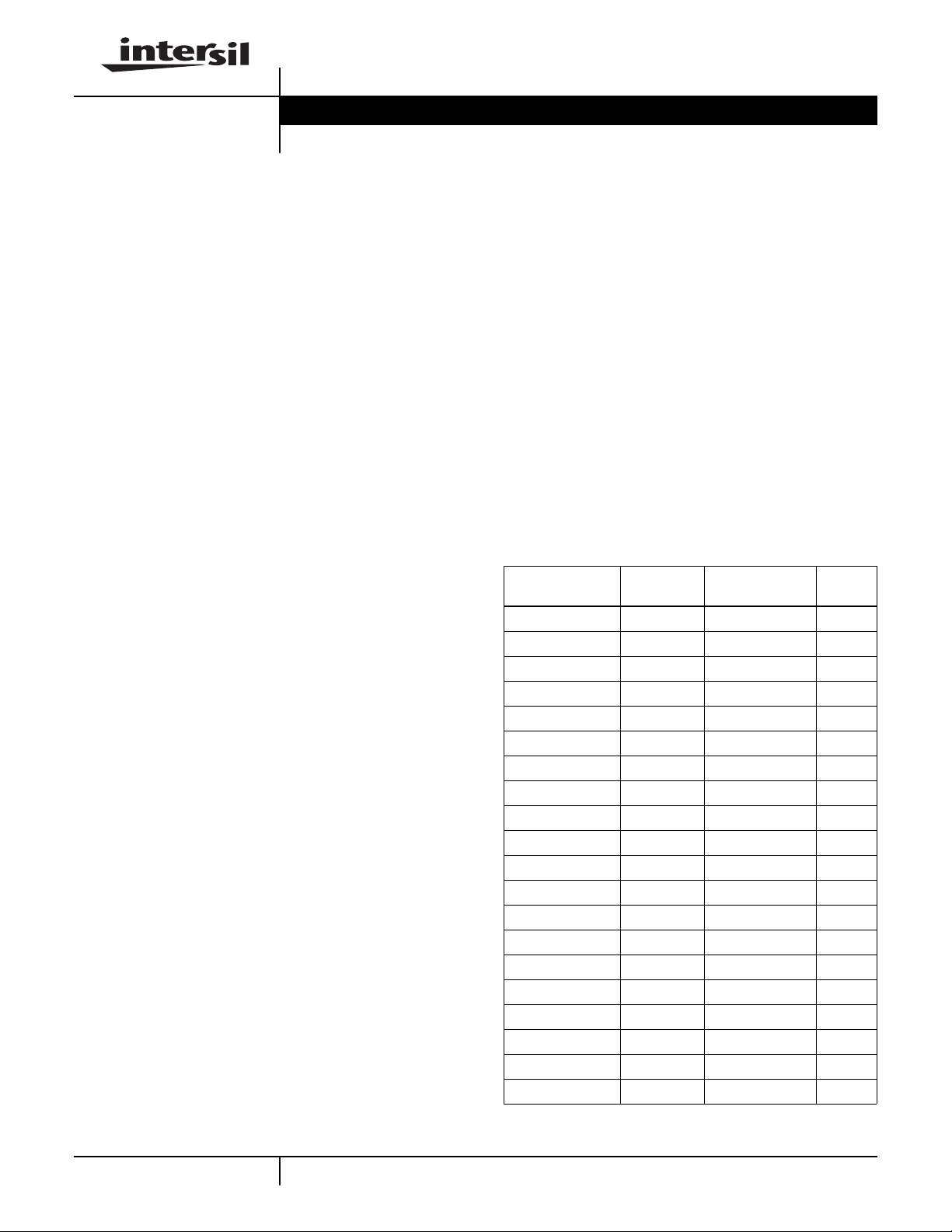

Ordering Information

TEMP.

PART NUMBER

HI1-0546-5 0 to 75 28 Ld CERDIP F28.6

HI1-0546-2 -55 to 125 28 Ld CERDIP F28.6

HI3-0546-5 0 to 75 28 Ld PDIP E28.6

HI4P0546-5 0 to 75 28 Ld PLCC N28.45

HI9P0546-9 -40 to 85 28 Ld SOIC M28.3

HI1-0547-5 0 to 75 28 Ld CERDIP F28.6

HI3-0547-5 0 to 75 28 Ld PDIP E28.6

HI4P0547-5 0 to 75 28 Ld PLCC N28.45

HI9P0547-9 -40 to 85 28 Ld SOIC M28.3

HI1-0548-2 -55 to 125 16 Ld CERDIP F16.3

HI1-0548-5 0 to 75 16 Ld CERDIP F16.3

HI3-0548-5 0 to 75 16 Ld PDIP E16.3

HI4P0548-5 0 to 75 20 Ld PLCC N20.35

HI9P0548-5 0 to 75 16 Ld SOIC M16.15

HI9P0548-9 -40 to 85 16 Ld SOIC M16.15

HI1-0549-2 -55 to 125 16 Ld CERDIP F16.3

HI3-0549-5 0 to 75 16 Ld PDIP E16.3

HI4P0549-5 0 to 75 20 Ld PLCC N20.35

HI9P0549-5 0 to 75 16 Ld SOIC M16.15

HI9P0549-9 -40 to 85 16 Ld SOIC M16.15

RANGE (oC) PACKAGE

PKG.

NO.

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

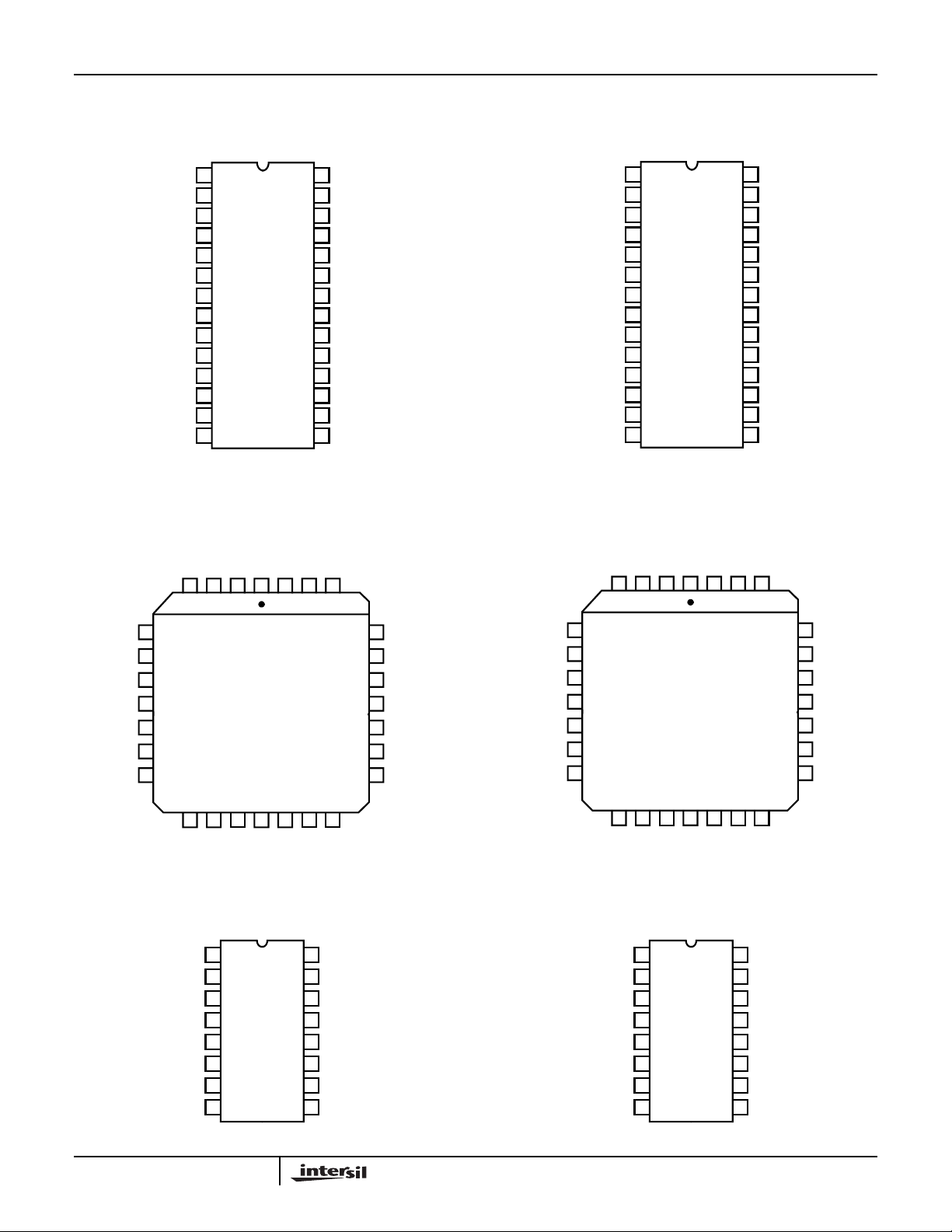

Pinouts

ADDRESS A

HI-546 (CERDIP, PDIP, SOIC)

TOP VIEW

+V

SUPPLY

NC

NC

IN 16

IN 15

IN 14

IN 13

IN 12

IN 11

IN 10

IN 9

GND

V

REF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

3

HI-546, HI-547, HI-548, HI-549

28

OUT

-V

27

SUPPLY

26

IN 8

25

IN 7

24

IN 6

23

IN 5

IN 4

22

21

IN 3

20

IN 2

19

IN 1

18

ENABLE

17

ADDRESS A

16

ADDRESS A

ADDRESS A

15

0

1

2

HI-547 (CERDIP, PDIP, SOIC)

TOP VIEW

+V

SUPPLY

OUT B

NC

IN 8B

IN 7B

IN 6B

IN 5B

IN 4B

IN 3B

IN 2B

IN 1B

GND

V

REF

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

OUT A

-V

27

SUPPLY

26

IN 8A

25

IN 7A

IN 6A

24

IN 5A

23

IN 4A

22

IN 3A

21

20

IN 2A

IN 1A

19

ENABLE

18

ADDRESS A

17

16

ADDRESS A

ADDRESS A

15

0

1

2

IN 15

IN 14

IN 13

IN 12

IN 11

IN 10

IN 9

HI-546 (PLCC)

TOP VIEW

IN 16NCNC

5

6

7

8

9

10

11

12 13 14 15 16 17 18

A3A2A

REF

GND

V

HI-548 (CERDIP, PDIP, SOIC)

TOP VIEW

HI-547 (PLCC)

TOP VIEW

REF

NC

SUPPLY

+V

1234

2A1

A

OUT A

SUPPLY

-V

0

A

IN 8A

262728

ENABLE

25

IN 7A

24

IN 6A

23

IN 5A

22

IN 4A

21

IN 3A

20

IN 2A

19

IN 1A

SUPPLY

+V

1234

OUT

1

SUPPLY

-V

0

A

IN 8

262728

ENABLE

IN 8BNCOUT B

5

25

IN 7

24

IN 6

23

IN 5

22

IN 4

21

IN 3

20

IN 2

19

IN 1

IN 7B

IN 6B

IN 5B

IN 4B

IN 3B

IN 2B

IN 1B

6

7

8

9

10

11

12 13 14 15 16 17 18

GND

V

HI-549 (CERDIP, PDIP, SOIC)

TOP VIEW

ENABLE

-V

SUPPLY

OUT

A

IN 1

IN 2

IN 3

IN 4

16

1

0

2

3

4

5

6

7

8

A

1

15

A

2

14

GND

13

+V

SUPPLY

12

IN 5

IN 6

11

IN 7

10

9

IN 8

ENABLE

-V

SUPPLY

A

IN 1A

IN 2A

IN 3A

IN 4A

OUT A

1

0

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

A

1

GND

+V

SUPPLY

IN 1B

IN 2B

IN 3B

IN 4B

OUT B

2

HI-546, HI-547, HI-548, HI-549

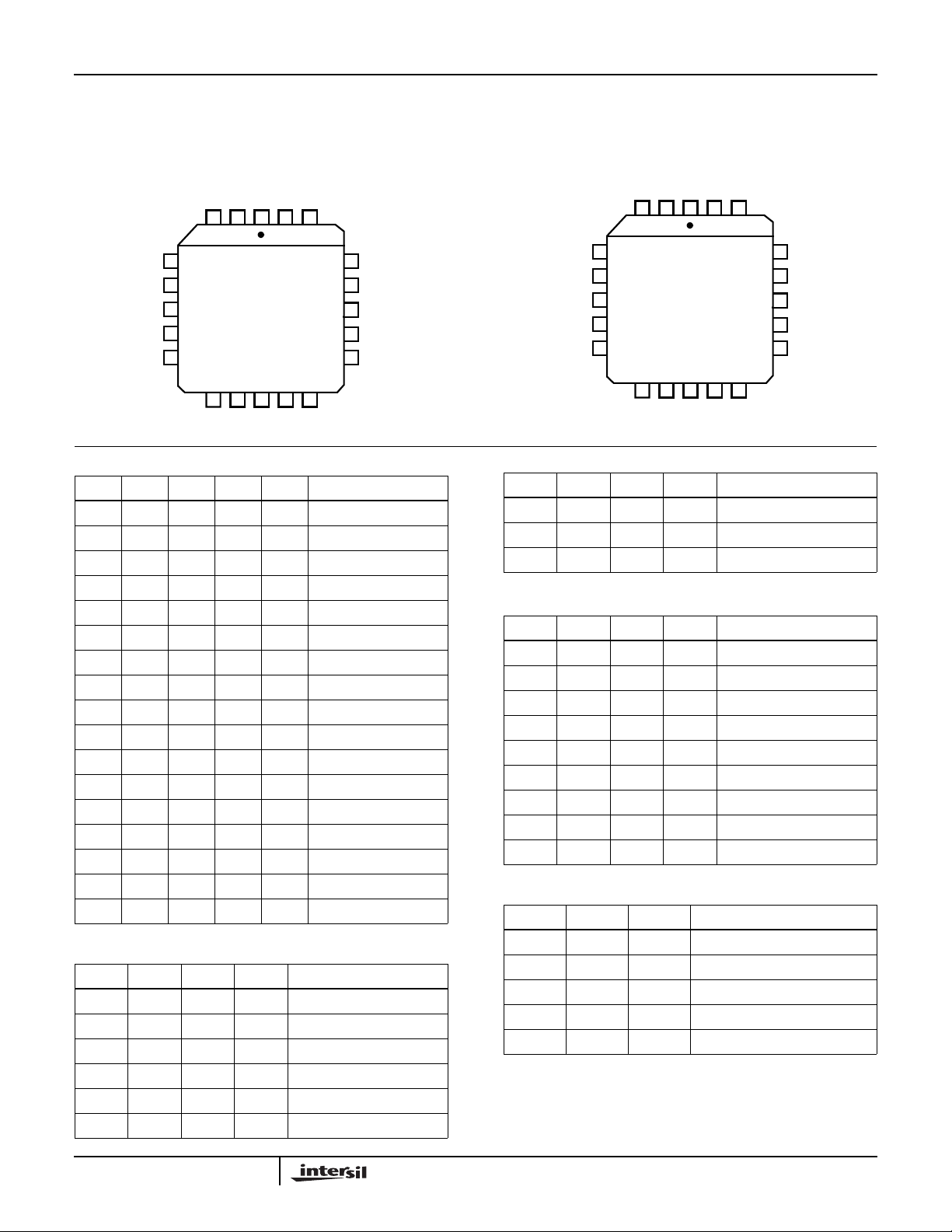

Pinouts

(Continued)

HI-548 (PLCC)

TOP VIEW

A1A

193 2 201

IN 8

2

IN 7

18

GND

17

+V

16

NC

15

IN 5

14

IN 6

-V

SUPPLY

IN 1

NC

IN 2

IN 3

ENABLE

A0NC

4

5

6

7

8

9

10 11 12 13

OUT

NC

IN 4

TRUTH TABLE HI-546

A

A

3

A

2

A

1

EN “ON” CHANNEL

0

XXXXL None

LLLLH 1

LLLHH 2

LLHLH 3

LLHHH 4

LHLLH 5

LHLHH 6

LHHLH 7

LHHHH 8

HLLLH 9

HLLHH 10

HLHLH 11

HLHHH 12

HHLLH 13

HHLHH 14

HHHLH 15

HHHHH 16

TRUTH TABLE HI-547

A

A

2

A

1

EN “ON” CHANNEL PAIR

0

X X X L None

LLLH 1

LLHH 2

LHLH 3

LHHH 4

HLLH 5

SUPPLY

HI-549 (PLCC)

TOP VIEW

ENABLE

-V

SUPPLY

IN 1A

NC

IN 2A

IN 3A

A0NC

4

5

6

7

8

9

10 11 12 13

IN 4A

OUT ANCOUT B

A1GND

193 2 201

IN 4B

+V

18

SUPPLY

IN 1B

17

NC

16

IN 2B

15

14

IN 3B

TRUTH TABLE HI-547 (Continued)

A

A

2

A

1

EN “ON” CHANNEL PAIR

0

HLHH 6

HHLH 7

HHHH 8

TRUTH TABLE HI-548

A

A

2

A

1

EN “ON” CHANNEL

0

X X X L None

LLLH 1

LLHH 2

LHLH 3

LHHH 4

HLLH 5

HLHH 6

HHLH 7

HHHH 8

TRUTH TABLE HI-549

A

1

A

0

EN “ON” CHANNEL PAIR

X X L None

LLH 1

LHH 2

HLH 3

HHH 4

3

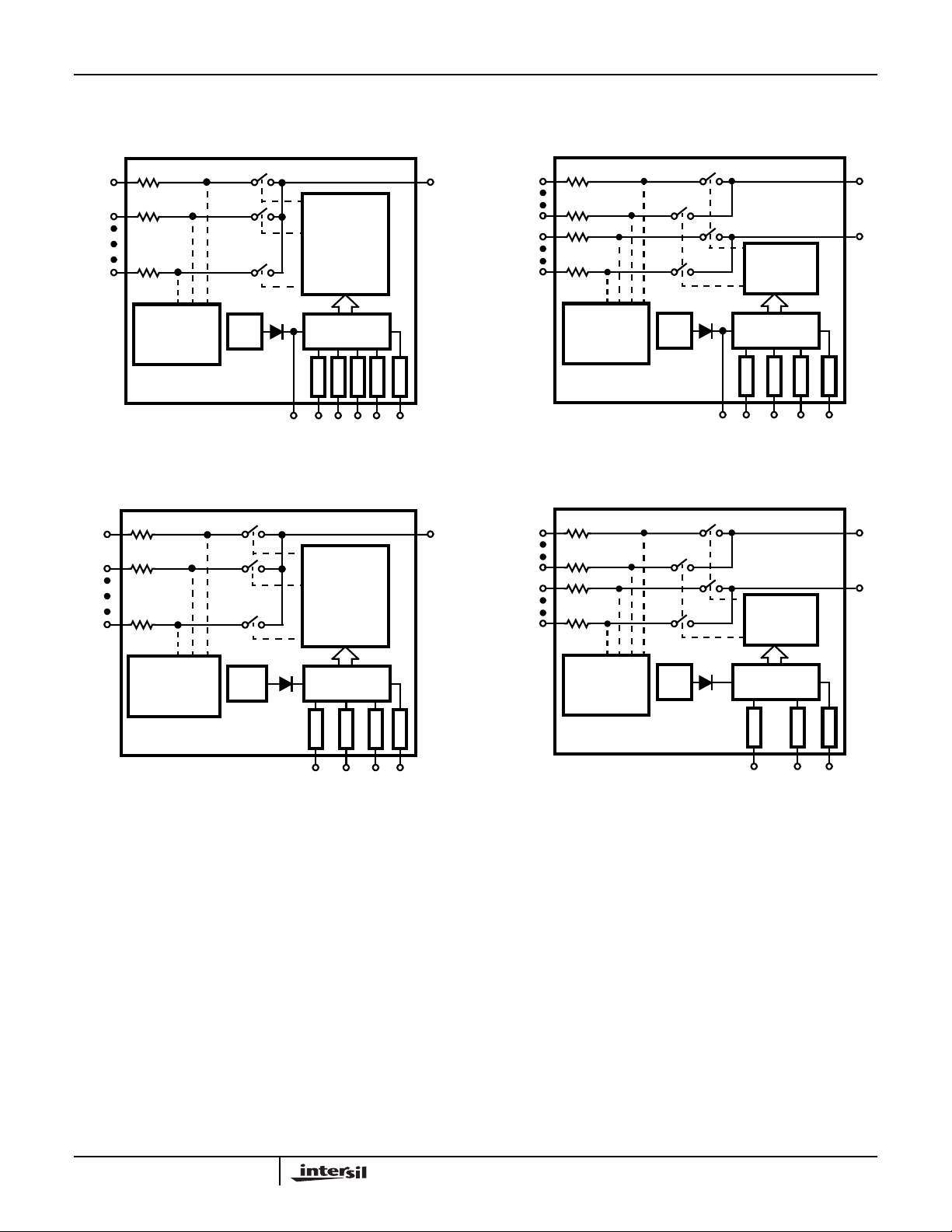

Functional Diagrams

HI-546 HI-547

IN 1

IN 2

IN 16

1K

1K

1K

HI-546, HI-547, HI-548, HI-549

DECODER/

DRIVER

OUT

IN 1A

IN 8A

IN 1B

IN 8B

1K

1K

1K

1K

DECODER/

DRIVER

OUT

A

OUT

B

IN 1

IN 2

IN 8

OVERVOLTAGE

CLAMP AND

SIGNAL

ISOLATION

† DIGITAL INPUT

PROTECTION

1K

1K

1K

OVERVOLTAGE

CLAMP AND

SIGNAL

ISOLATION

† DIGITAL INPUT

PROTECTION

5V

REF

LEVEL

SHIFT

† † † †

V

REFA0A1A2

OVERVOLTAGE

CLAMP AND

SIGNAL

ISOLATION

†

EN

A

3

† DIGITAL INPUT

PROTECTION

5V

REF

HI-548 HI-549

5V

REF

DECODER/

DRIVER

LEVEL

SHIFT

† † †

OUT

IN 1A

IN 4A

IN 1B

IN 4B

†

1K

1K

1K

1K

OVERVOLTAGE

CLAMP AND

SIGNAL

ISOLATION

† DIGITAL INPUT

PROTECTION

5V

REF

LEVEL

SHIFT

† † †

V

REFA0A1A2

DECODER/

DRIVER

LEVEL

SHIFT

† †

EN

†

OUT

A

OUT

B

†

A

A

0A1A2

EN

A

0

EN

1

4

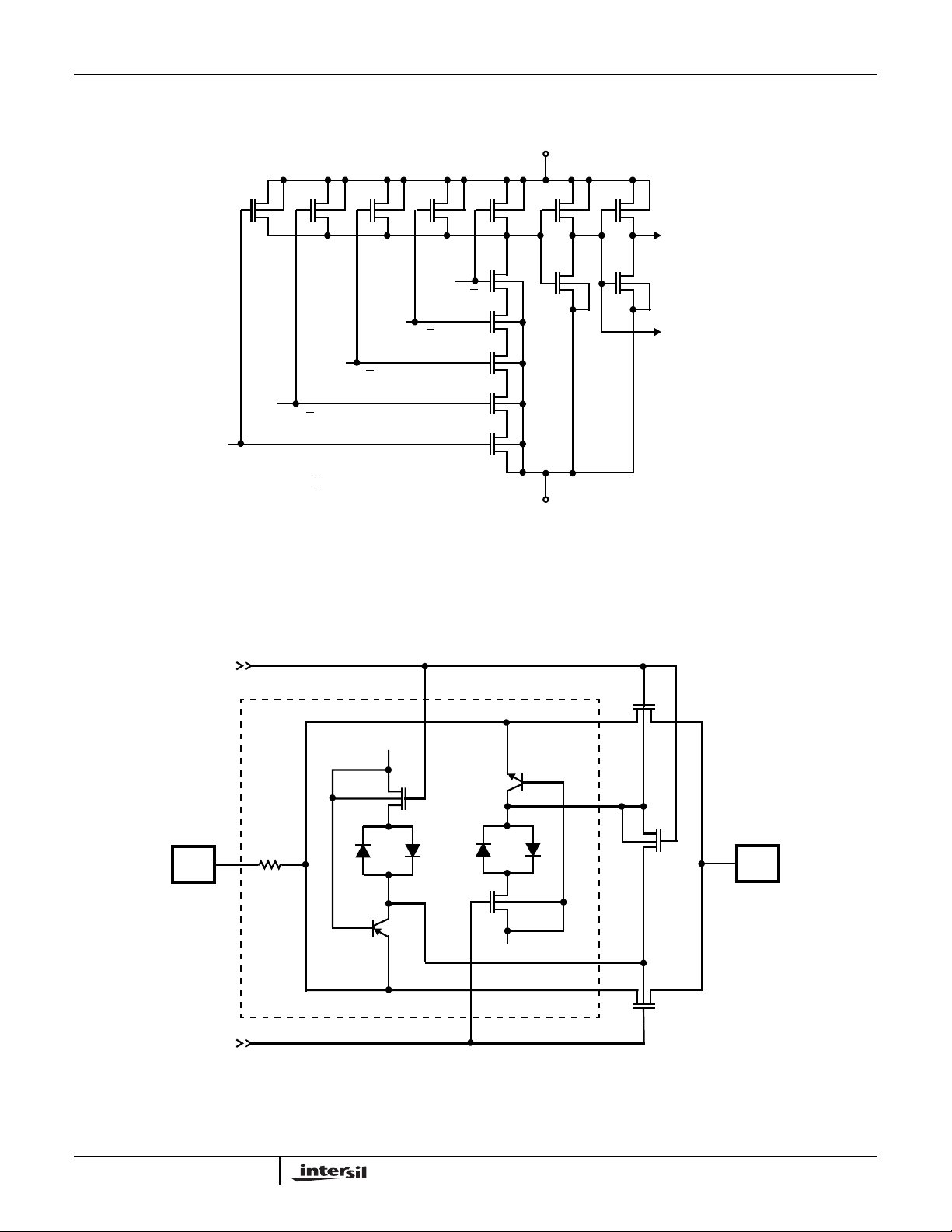

Schematic Diagrams

HI-546, HI-547, HI-548, HI-549

ADDRESS DECODER

V+

FROM

DECODE

P

ENABLE

DELETE A

DELETE A

OVERVOLTAGE PROTECTION

PP PP P P

A2 OR A

A3 OR A

3

OR A3 INPUT FOR HI-547, HI-548, HI-549

3

OR A2 INPUT FOR HI-549

2

A

0

A1 OR A

1

2

MULTIPLEX SWITCH

OR A

TO P-CHANNEL

N

0

N

N

N

N

NN

V-

DEVICE OF

THE SWITCH

TO N-CHANNEL

DEVICE OF

THE SWITCH

N

IN

FROM

DECODE

R11

1K

5

V+

P

D6 D7

Q6

Q5

D4 D5

N

V-

N

P

OUT

Loading...

Loading...