Intersil Corporation HI-524 Datasheet

HI-524

Data Sheet July 1999

4-Channel Wideband and Video

Multiplexer

The HI-524 is a 4-Channel CMOS analog multiplexerdesigned

to process single-ended signals with bandwidths up to 10MHz.

The chipincludesa1of 4 decoder for channel selection and an

enable input to inhibit all channels (chip select).

Three CMOS transmission gates are used in each channel,

as compared to the single gate in more conventional CMOS

multiplexers. This provides a double barrier to the unwanted

coupling of signals from each input to the output. In addition,

Dielectric Isolation (DI) processing helps to insure the

Crosstalk is less than -60dB at 10MHz.

The HI-524 is designed to operate into a wideband buffer

amplifier such as the Intersil HA-2541. The multiplexer chip

includes two “ON” switches in series, for use as a feedback

element with the amplifier. This feedback resistance

matches and tracks the channel ON resistance, to minimize

the amplifier V

and its variation with temperature.

OS

The HI-524 is well suited to the rapid switching of video and

other wideband signals in telemetry, instrumentation, radar

and video systems.

Ordering Information

PART

NUMBER

HI1-0524-5 0 to 75 18 Ld CERDIP F18.3

HI3-0524-5 0 to 75 18 Ld PDIP E18.3

TEMP. RANGE

(oC) PACKAGE PKG. NO.

File Number 3148.2

Features

• Crosstalk (10MHz) . . . . . . . . . . . . . . . . . . . . . . . . <-60dB

• Fast Access Time . . . . . . . . . . . . . . . . . . . . . . . . . 150ns

• Fast Settling Time . . . . . . . . . . . . . . . . . . . . . . . . . 200ns

• TTL Compatible

Applications

• Wideband Switching

• Radar

• TV Video

• ECM

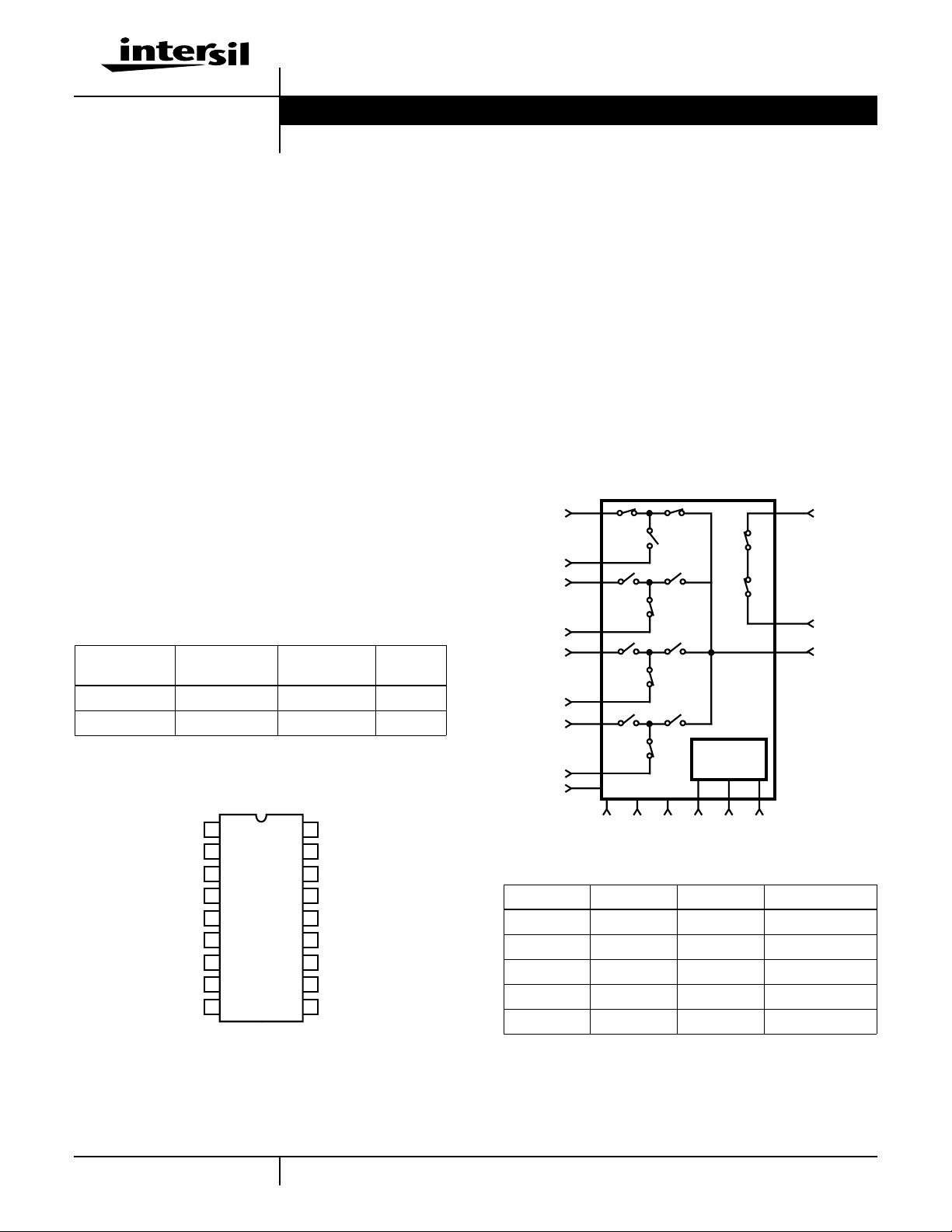

Functional Diagram

IN1

SIG GND

IN2

SIG GND

IN3

SIG GND

IN4

FB (IN)

FB (OUT)

OUTPUT

Pinout

+V

OUT

SIG GND

SIG GND

IN4

SIG GND

IN3

SUPPLY GND

A

HI-524 (CERDIP, PDIP)

TOP VIEW

1

2

3

4

5

6

7

8

9

1

18

17

16

15

14

13

12

11

10

1

FB (IN)

-V

FB (OUT)

SIG GND

IN2

SIG GND

IN1

EN

A

0

1 OF 4

SIG GND

SIG GND

-15V SUP

A

1

X X L None

L L H 1 (Note)

LHH 2

HLH 3

HHH 4

NOTE: Channel 1 is shown selected in the Functional Diagram.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

1

+15V EN A0A

GND

TRUTH TABLE

A

0

DECODER

1

EN ON CHANNEL

| Copyright © Intersil Corporation 1999

HI-524

Absolute Maximum Ratings Thermal Information

V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33V

Digital Input Voltage (VEN, VA) . . . . . . . . . . . . . . . . . . . . -6V to +6V

Analog Signal (VIN, V

). . . . . . . . . . . . . . . . . (V-) -2V to (V+) +2V

OUT

Either Supply to Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16.5V

Operating Conditions

Temperature Range

HI-524-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 75oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

CERDIP Package. . . . . . . . . . . . . . . . . 75 20

PDIP Package . . . . . . . . . . . . . . . . . . . 80 N/A

Maximum Junction Temperature

Ceramic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175oC

Plastic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature. . . . . . . . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering, 10s). . . . . . . . . . . . 300oC

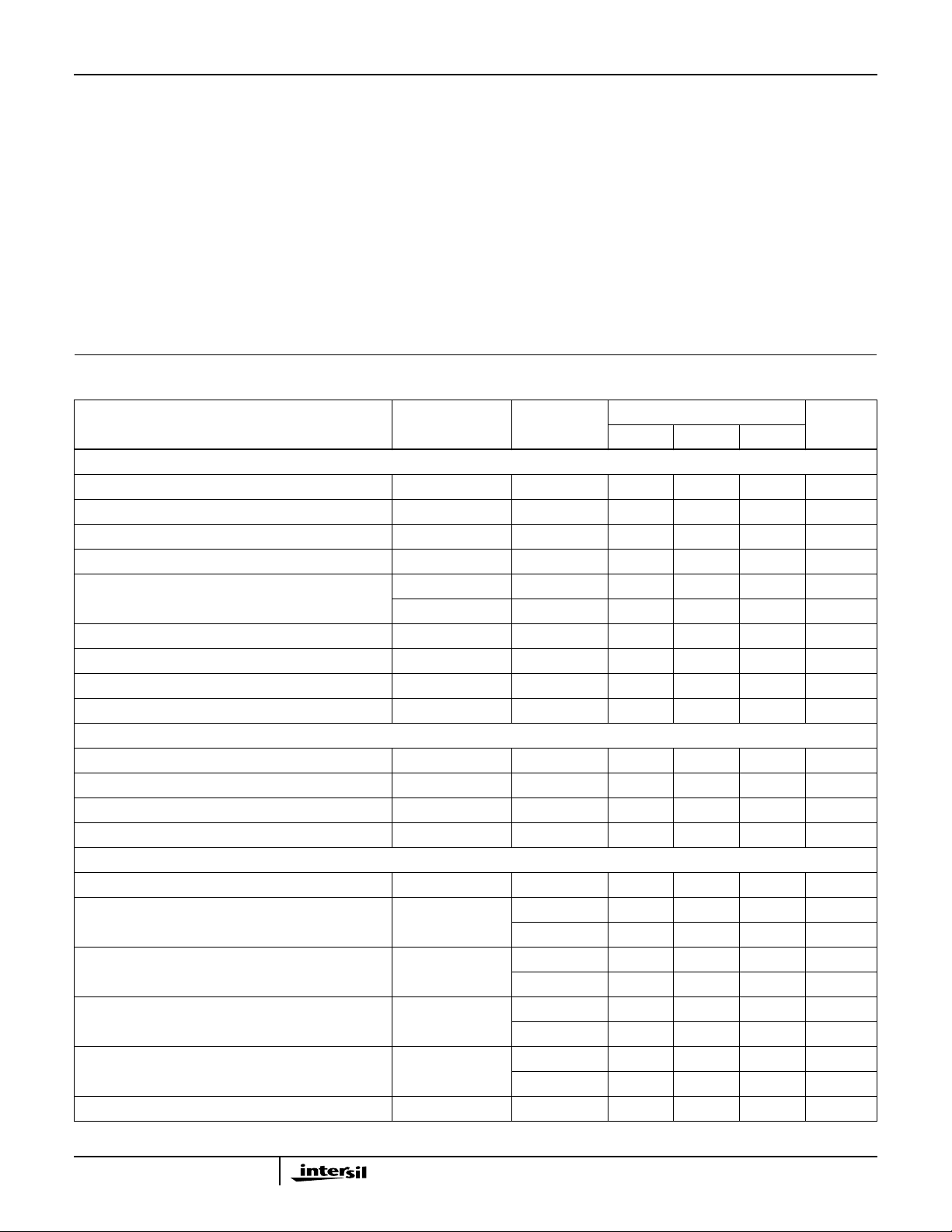

Electrical Specifications Supplies = +15V, -15V; V

(Logic Level High) = 2.4V, VAL (Logic Level Low) = 0.5V; VEN = 2.4V,

AH

Unless Otherwise Specified

-5

UNITSMIN TYP MAX

PARAMETER

TEST

CONDITIONS

TEMP

(oC)

DYNAMIC CHARACTERISTICS

Access Time, t

A

Break-Before-Make Delay, t

Enable Delay (ON), t

Enable Delay (OFF), t

ON (EN)

OFF (EN)

OPEN

Note 5 25 - 150 300 ns

Note 5 25 - 20 - ns

RL = 500Ω 25 - 180 - ns

RL = 500Ω 25 - 180 - ns

Settling Time (Note 5) To 0.1% 25 - 200 - ns

To 0.01% 25 - 600 - ns

Crosstalk Note 6 25 - -65 - dB

Channel Input Capacitance, C

Channel Output Capacitance, C

Digital Input Capacitance, C

A

S(OFF)

D(OFF)

25 - 4 - pF

25 - 10 - pF

25 - 5 - pF

DIGITAL INPUT SPECIFICATIONS

Input Low Threshold (TTL), V

Input High Threshold (TTL), V

Input Leakage Current (High), I

Input Leakage Current (Low), I

AL

AH

AH

AL

Full - - 0.8 V

Full 2.4 - - V

Full - 0.05 1 µA

Full - - 25 µA

ANALOG CHANNEL SPECIFICATIONS

Analog Signal Range, V

On Resistance, r

ON

lN

Note 2 25 - 700 - Ω

Full -10 - +10 V

Full - - 1.5 kΩ

Off Input Leakage Current, I

S (OFF)

Note 3 25 - 0.2 - nA

Full - - 50 nA

Off Output Leakage Current, I

D (OFF)

Note 3 25 - 0.2 - nA

Full - - 50 nA

On Channel Leakage Current, I

D (ON)

Note 3 25 - 0.7 - nA

Full - - 50 nA

-3dB Bandwidth Note 4 25 - 8 - MHz

2

Loading...

Loading...