Intersil Corporation HI-509, HI-508, HI-507, HI-506 Datasheet

HI-506, HI-507, HI-508, HI-509

Data Sheet June 1999

Single 16 and 8/Differential 8-Channel and

4-Channel CMOS Analog Multiplexers

The HI-506/HI-507 and HI-508/HI-509 monolithic CMOS

multiplexers each include an array of sixteen and eight

analog switches respectively, a digital decoder circuit for

channel selection, voltagereferencefor logic thresholds,and

an enable input for device selection when several

multiplexers are present. The Dielectric Isolation (DI)

process used in fabrication of these devices eliminates the

problem of latchup. DI also offers much lower substrate

leakage and parasitic capacitance than conventional

junction isolated CMOS (see Application Notes AN520 and

AN521).

The switching threshold for each digital input is established by

an internal +5V reference, providing a guaranteed minimum

2.4V for logic “1” and maximum 0.8V for logic “0”. This allows

direct interface without pullup resistors to signals from most

logic families: CMOS, TTL, DTL and some PMOS. For

protection against transient overvoltage, the digital inputs

include a series 200Ω resistor and diode clamp to each

supply.

File Number

3142.2

Features

• Low ON Resistance . . . . . . . . . . . . . . . . . . . . . . . . . 180Ω

• Wide Analog Signal Range . . . . . . . . . . . . . . . . . . . . . ±15V

• TTL/CMOS Compatible

• Access Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 250ns

• Maximum Power Supply. . . . . . . . . . . . . . . . . . . . . . . .44V

• Break-Before-Make Switching

• No Latch-Up

• Replaces DG506A/DG506AA and DG507A/DG507AA

• Replaces DG508A/DG508AA and DG509A/DG509AA

Applications

• Data Acquisition Systems

• Precision Instrumentation

• Demultiplexing

• Selector Switch

The HI-506 is a single 16-Channel, the HI-507 is an

8-Channel differential, the HI-508 is a single 8-Channel and

the HI-509 is a 4-Channel differential multiplexer.

If input overvoltages are present, the HI-546/HI-547/HI-548/

HI-549 multiplexers are recommended.

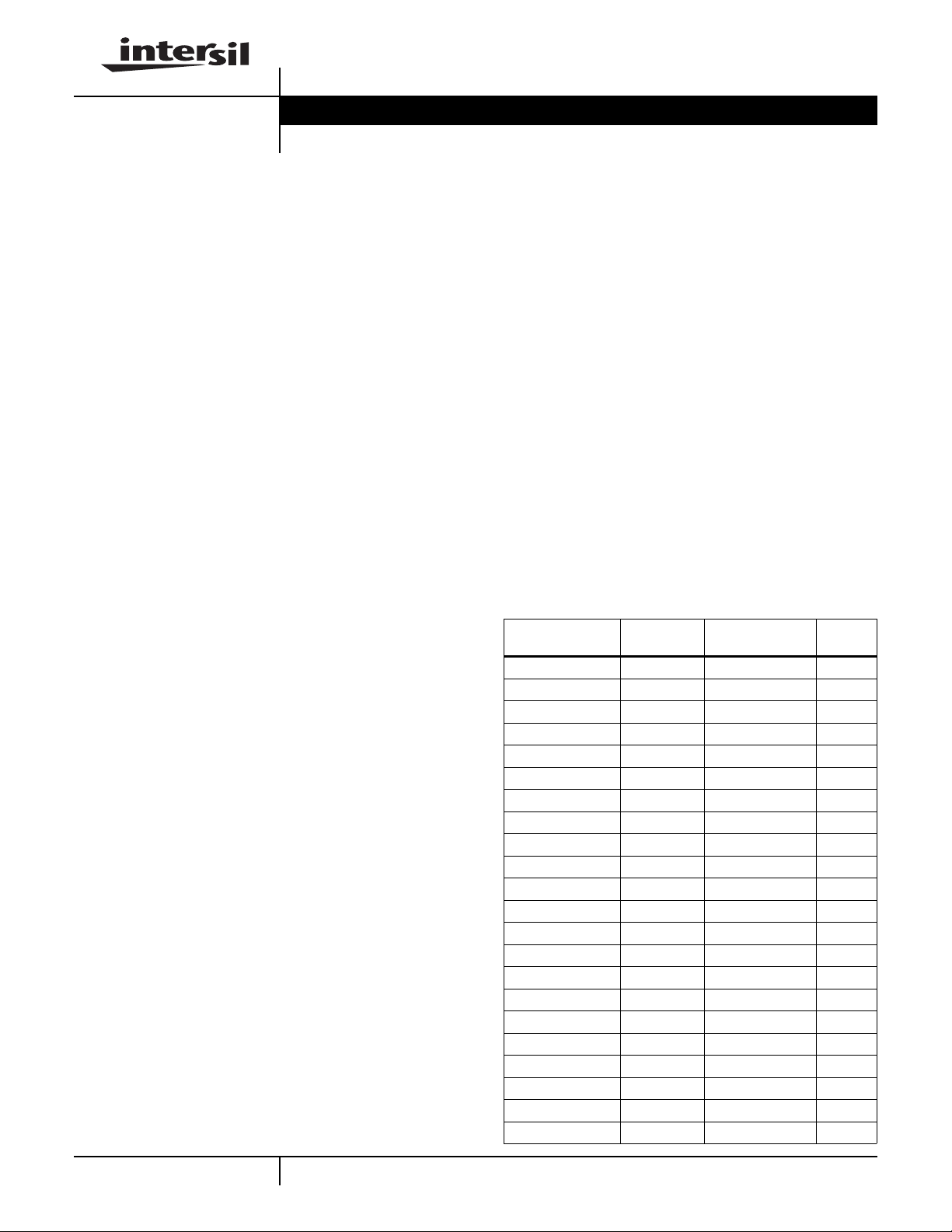

Ordering Information

TEMP.

PART NUMBER

HI9P0506-9 -40 to 85 28 Ld SOIC M28.3

HI3-0506-5 0 to 75 28 Ld PDIP E28.6

HI4P0506-5 0 to 75 28 Ld PLCC N28.45

HI1-0506-5 0 to 75 28 Ld CERDIP F28.6

HI1-0506-4 -25 to 85 28 Ld CERDIP F28.6

HI1-0506-2 -55 to 125 28 Ld CERDIP F28.6

HI4P0507-5 0 to 75 28 Ld PLCC N28.45

HI3-0507-5 0 to 75 28 Ld PDIP E28.6

HI1-0507-2 -55 to 125 28 Ld CERDIP F28.6

HI1-0508-5 0 to 75 16 Ld CERDIP F16.3

HI3-0508-5 0 to 75 16 Ld PDIP E16.3

HI1-0508-4 -25 to 85 16 Ld CERDIP F16.3

HI1-0508-2 -55 to 125 16 Ld CERDIP F16.3

HI4P0508-5 0 to 75 20 Ld PLCC N20.35

HI9P0508-9 -40 to 85 16 Ld SOIC M16.15

HI9P0508-5 0 to 75 16 Ld SOIC M16.15

HI9P0509-5 0 to 75 16 Ld SOIC M16.15

HI1-0509-4 -25 to 85 16 Ld CERDIP F16.3

HI1-0509-5 0 to 75 16 Ld CERDIP F16.3

HI3-0509-5 0 to 75 16 Ld PDIP E16.3

HI4P0509-5 0 to 75 20 Ld PLCC N20.35

HI1-0509-2 -55 to 125 16 Ld CERDIP F16.3

RANGE (oC) PACKAGE

PKG.

NO.

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

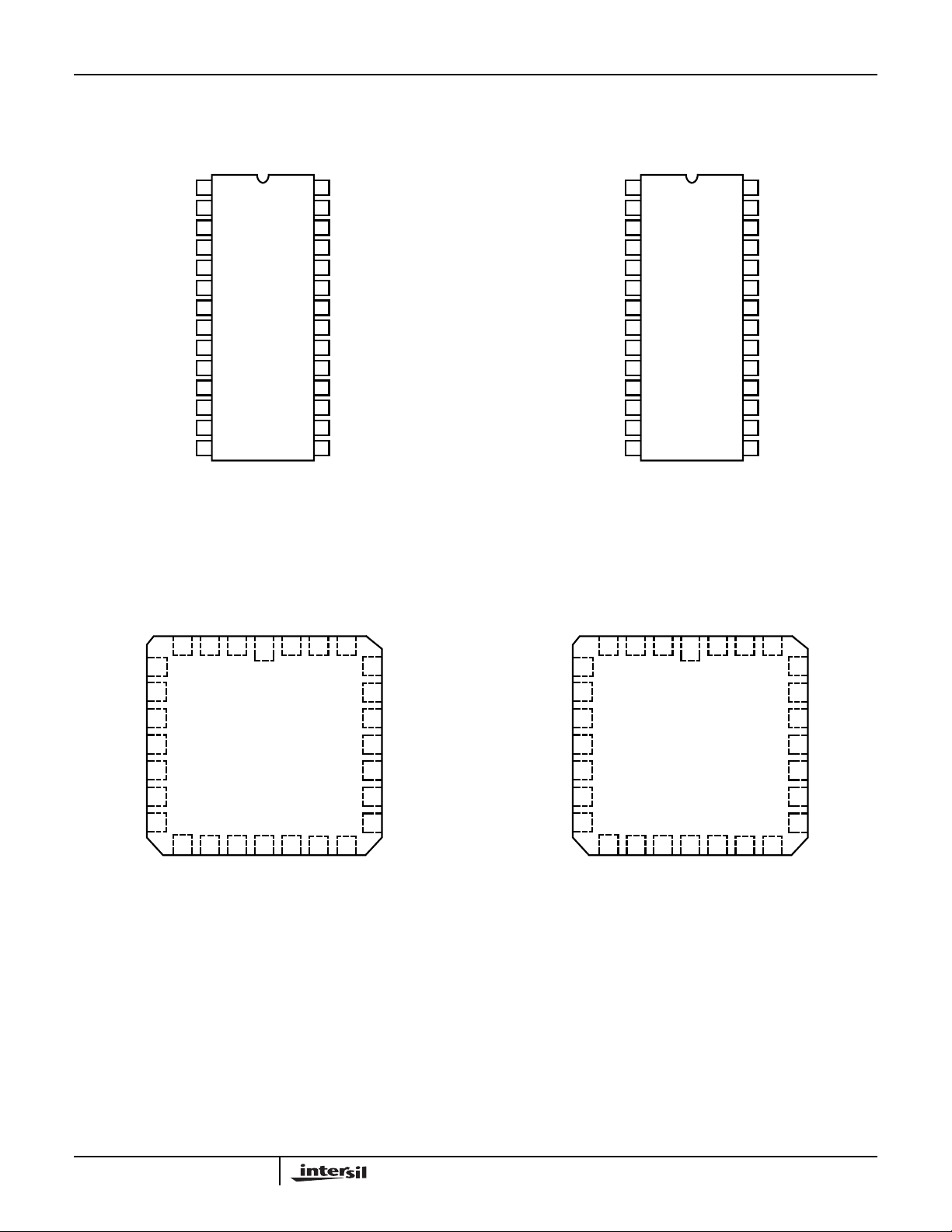

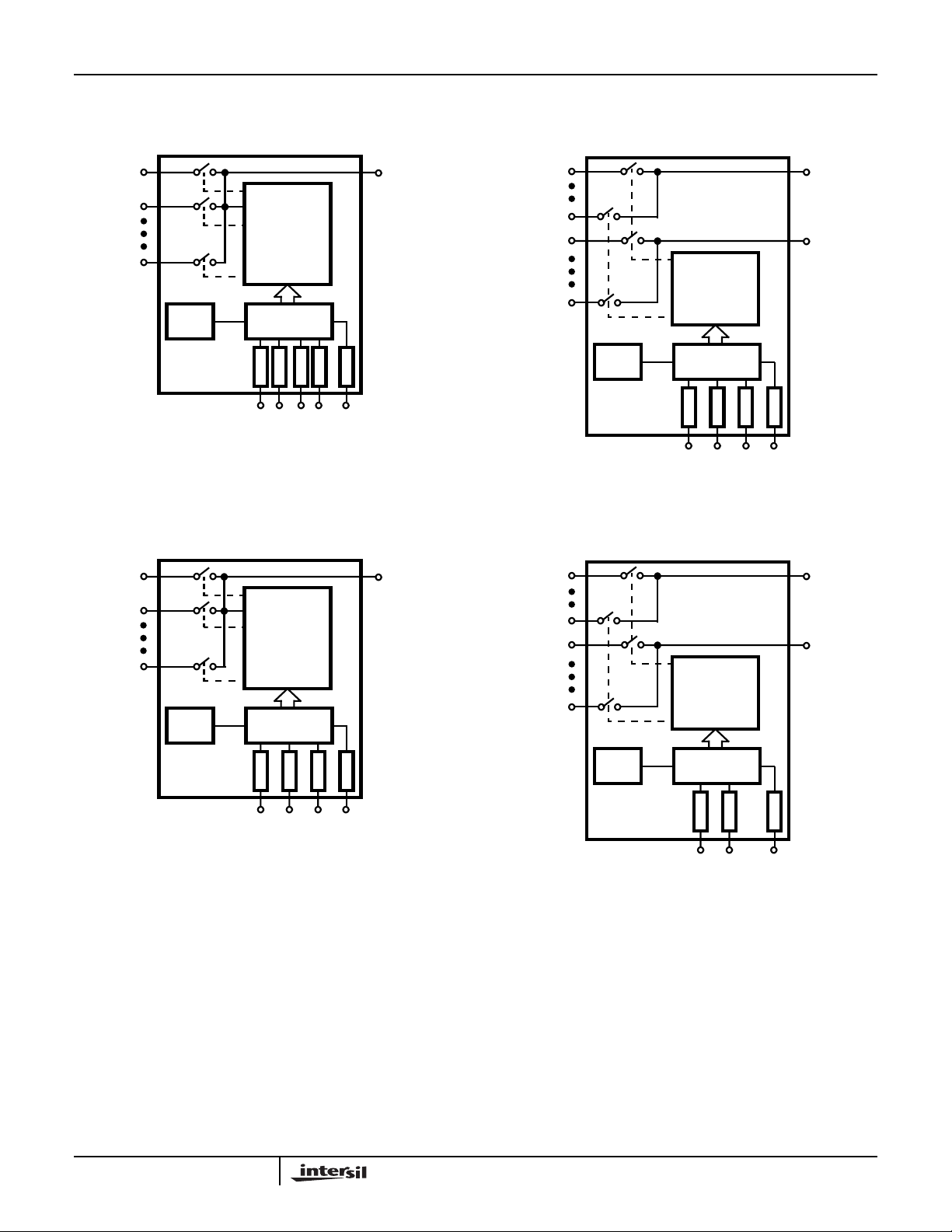

Pinouts

HI-506

(PDIP, CERDIP, SOIC)

TOP VIEW

HI-506, HI-507, HI-508, HI-509

HI-507

(PDIP, CERDIP)

TOP VIEW

+V

ADDRESS A

IN 15

IN 14

IN 13

IN 12

IN 11

10

IN 10

11

IN 9

SUPPLY

NC

NC

IN 16

IN 15

IN 14

IN 13

IN 12

IN 11

IN 10

IN 9

GND

NC

5

6

7

8

9

28

1

2

3

4

5

6

7

8

9

10

11

12

13

14

3

OUT

-V

27

SUPPLY

26

IN 8

25

IN 7

24

IN 6

23

IN 5

IN 4

22

21

IN 3

20

IN 2

19

IN 1

18

ENABLE

17

ADDRESS A

16

ADDRESS A

ADDRESS A

15

0

1

2

HI-506

(PLCC)

TOP VIEW

IN 16NCNC

3214282726

NC

GND

SUPPLY

+V

14 15 16 17 1812 13

3A2A1

A

OUT

-V

0

A

SUPPLY

IN 8

25

24

23

22

21

20

19

ENABLE

IN 7

IN 6

IN 5

IN 4

IN 3

IN 2

IN 1

IN 7B

IN 6B

IN 5B

IN 4B

IN 3B

IN 2B

IN 1B

+V

5

6

7

8

9

10

11

SUPPLY

OUT B

IN 8B

IN 7B

IN 6B

IN 5B

IN 4B

IN 3B

IN 2B

IN 1B

GND

28

OUT A

-V

27

SUPPLY

26

IN 8A

25

IN 7A

24

IN 6A

23

IN 5A

IN 4A

22

21

IN 3A

20

IN 2A

19

IN 1A

18

ENABLE

17

ADDRESS A

16

ADDRESS A

ADDRESS A

15

NC

NC

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

HI-507

(PLCC)

TOP VIEW

IN 8BNCOUT B

3214282726

NC

GND

SUPPLY

+V

14 15 16 17 1812 13

2A1

A

NC

OUT A

SUPPLY

-V

IN 8A

25

24

23

22

21

20

19

0

A

ENABLE

0

1

2

IN 7A

IN 6A

IN 5A

IN 4A

IN 3A

IN 2A

IN 1A

2

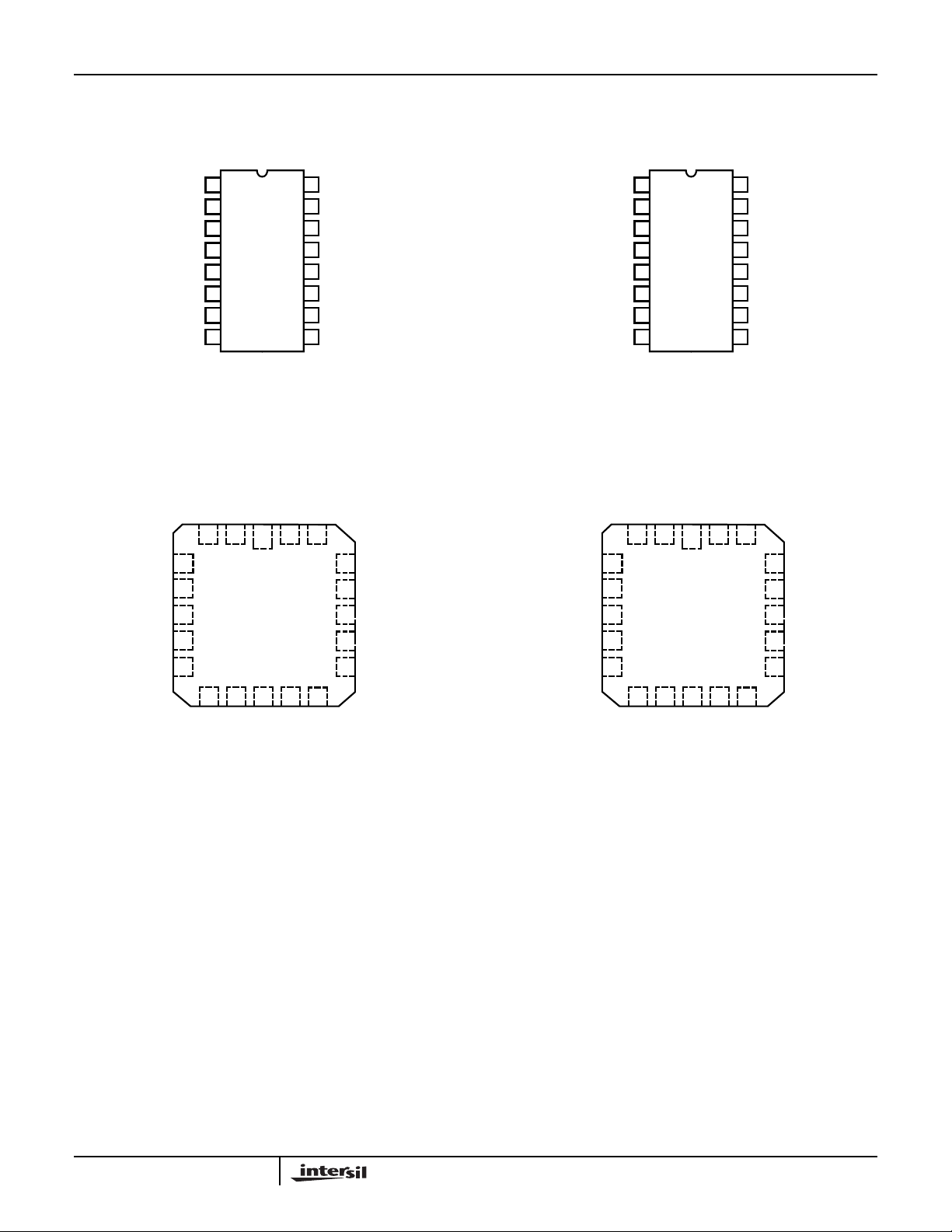

HI-506, HI-507, HI-508, HI-509

Pinouts

-V

SUPPLY

(Continued)

(PDIP, CERDIP, SOIC)

A

0

ENABLE

-V

SUPPLY

IN 1

IN 2

IN 3

IN 4

OUT

4

IN 1

5

NC

6

IN 2

7

IN 3

8

HI-508

TOP VIEW

A

1

2

3

4

5

6

7

8

16

1

A

15

2

14

GND

13

+V

12

IN 5

IN 6

11

10

IN 7

9

IN 8

HI-508

(PLCC)

TOP VIEW

ENABLE

A0NC

3212019

A1A

2

SUPPLY

GND

18

+V

17

NC

16

IN 5

15

IN 6

14

SUPPLY

-V

SUPPLY

ENABLE

-V

IN 1A

NC

IN 2A

IN 3A

HI-509

(PDIP, CERDIP, SOIC)

TOP VIEW

1

A

0

2

IN 1A

IN 2A

IN 3A

IN 4A

OUT A

3

4

5

6

7

8

SUPPLY

HI-509

(PLCC)

TOP VIEW

ENABLE

A0NC

3212019

4

5

6

7

8

A

16

1

GND

15

14

+V

13

IN 1B

IN 2B

12

IN 3B

11

IN 4B

10

OUT B

9

A1GND

SUPPLY

+V

18

IN 1B

17

NC

16

IN 2B

15

IN 3B

14

SUPPLY

IN 4

10 11 12 139

NC

IN 8

OUT

IN 7

10 11 12 139

IN 4A

OUT ANCOUT B

IN 4B

3

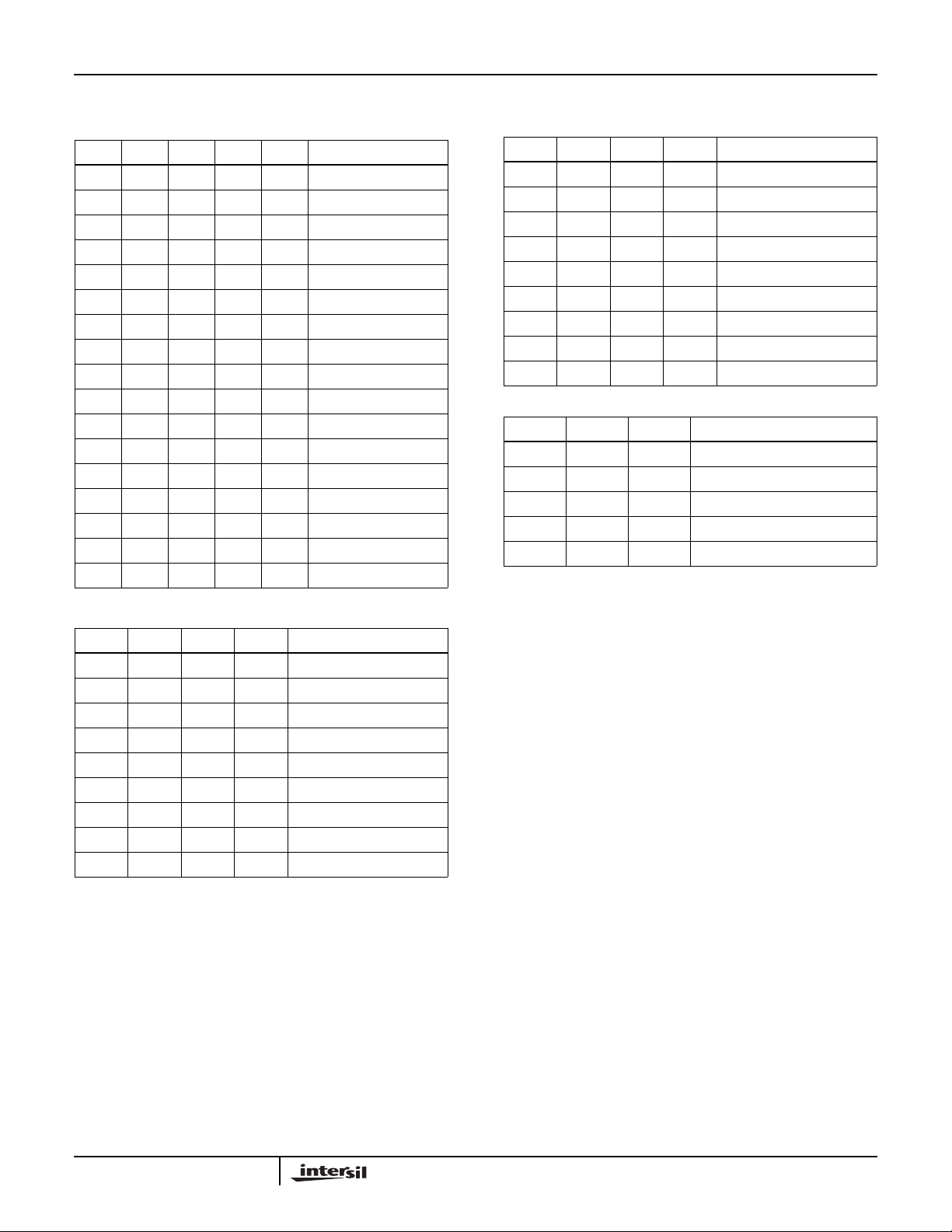

HI-506, HI-507, HI-508, HI-509

Truth Tables

HI-506

A

A

3

XXXXL None

LLLLH 1

LLLHH 2

LLHLH 3

LLHHH 4

LHLLH 5

LHLHH 6

LHHLH 7

LHHHH 8

HLLLH 9

HLLHH 10

HLHLH 11

HLHHH 12

HHLLH 13

HHLHH 14

HHHLH 15

HHHHH 16

A

A

2

1

EN “ON” CHANNEL

0

HI-508

A

X X X L None

LLLH 1

LLHH 2

LHLH 3

LHHH 4

HLLH 5

HLHH 6

HHLH 7

HHHH 8

A

A

2

1

X X L None

LLH 1

LHH 2

HLH 3

HHH 4

A

1

A

0

EN “ON” CHANNEL

0

HI-509

EN “ON” CHANNEL PAIR

HI-507

A

X X X L None

LLLH 1

LLHH 2

LHLH 3

LHHH 4

HLLH 5

HLHH 6

HHLH 7

HHHH 8

A

2

A

1

EN “ON” CHANNEL

0

4

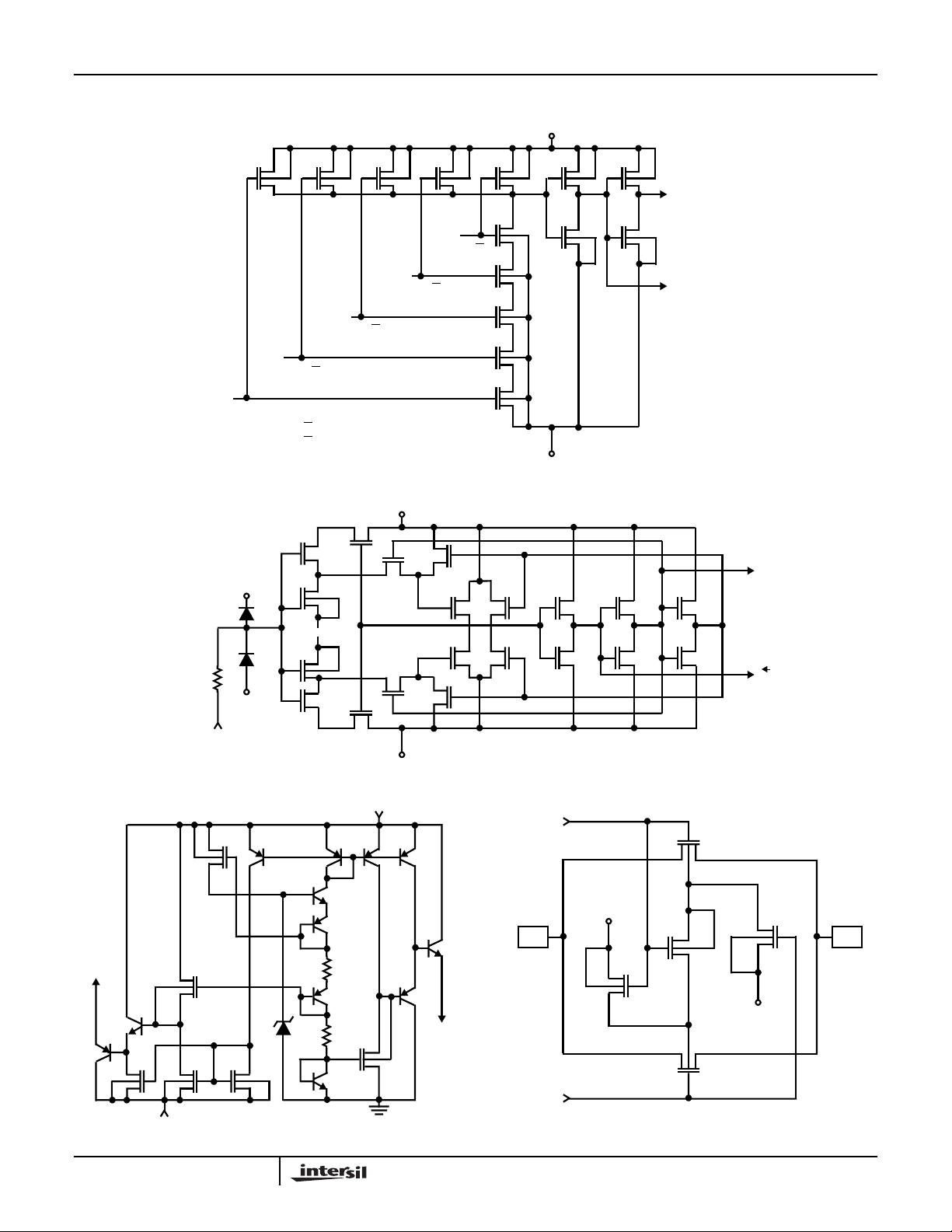

Functional Diagrams

HI-506 HI-507

HI-506, HI-507, HI-508, HI-509

IN 1

IN 2

IN 16

IN 1

IN 2

IN 8

5V

REF

DIGITAL

†

INPUT

PROTECTION

5V

REF

IN 1A

IN 8A

IN 1B

IN 8B

5V

REF

DIGITAL

†

INPUT

PROTECTION

DECODER/

DRIVER

† † †

A

0A1A2

DECODER/

DRIVER

LEVEL

SHIFT

† † † †

A

0A1A2A3

OUT

†

EN

HI-508 HI-509

IN 1A

IN 4A

IN 1B

IN 4B

DECODER/

DRIVER

DECODER/

DRIVER

LEVEL

SHIFT

OUT

LEVEL

SHIFT

OUT A

OUT B

†

EN

OUT A

OUT B

DIGITAL

†

INPUT

PROTECTION

† † †

A

0A1A2

5

†

EN

5V

REF

DIGITAL

†

INPUT

PROTECTION

LEVEL

SHIFT

† †

A

0A1

†

EN

HI-506, HI-507, HI-508, HI-509

Schematic Diagrams

ENABLE

DELETE A

DELETE A

V+

D1

ADDRESS DECODER

P

PP PP P P

A1 OR A

A2 OR A

2

A3 OR A

3

OR A3 INPUT FOR HI-507, HI-508, HI-509

3

OR A2 INPUT FOR HI-509

2

ADDRESS INPUT BUFFER LEVEL SHIFTER

P3

P1

N1

V+

P5

P4

A

1

OR A

0

P6

V+

N

0

N

N

N

N

P7

NN

V-

P8 P9 P10

TO P-CHANNEL

DEVICE OF

THE SWITCH

TO N-CHANNEL

DEVICE OF

THE SWITCH

A

Q9P

V

L

Q10N

200Ω

TTL REFERENCE CIRCUIT MULTIPLEX SWITCH

N13 N14

A

N12

IN

P15

N15

D2

V

L

V

R

P2

V-

Q1P

D3

N2

Q2PV+Q3P Q4P

Q5N

Q6N

R2

16.8K

Q11P

R3

6.8K

Q12N

N3

N4

P16

N5

V-

Q8N

Q7P

V

R

N7

N6

ALL N-CHANNEL BODIES TO VALL P-CHANNEL BODIES TO V+

UNLESS OTHERWISE INDICATED

N8 N9 N10

FROM DECODE

IN

V+

P17

N19

P18

A

N18

N17

OUT

V-

V- GND

6

FROM DECODE

HI-506, HI-507, HI-508, HI-509

Absolute Maximum Ratings Thermal Information

V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +44V

V+ to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +22V

V- to GND. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -25V

Digital Input Voltage (VEN, VA) . . . . . (V-) -4V to (V+) +4V or 20mA,

Whichever Occurs First

Analog Signal (VIN, V

Continuous Current, In or Out . . . . . . . . . . . . . . . . . . . . . . . . . 20mA

Peak Current, In or Out (Pulsed 1ms, 10% Duty Cycle Max) . 40mA

, Note 2) . . . . . . . . . . (V-) -2V to (V+) +2V

OUT

Operating Conditions

Temperature Ranges

HI-506/507/508/509-2 . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

HI-506/508/509-4 . . . . . . . . . . . . . . . . . . . . . . . . . . -25oC to 85oC

HI-506/507/508/509-5 . . . . . . . . . . . . . . . . . . . . . . . .0oC to 75oC

HI-506/508-9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationofthe

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

2. Signals on IN or OUT exceeding V+ or V- are clamped by internal diodes. Limit resulting current to maximum current ratings. If an overvoltage

condition is anticipated (analog input exceeds either power supply voltage), the Harris HI-546/HI-547/HI-548/HI-549 multiplexers are

recommended.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

16 Ld CERDIP Package. . . . . . . . . . . . 85 32

16 Ld SOIC Package . . . . . . . . . . . . . . 115 N/A

16 Ld PDIP Package . . . . . . . . . . . . . . 100 N/A

20 Ld PLCC Package. . . . . . . . . . . . . . 80 N/A

28 Ld CERDIP Package. . . . . . . . . . . . 55 18

28 Ld PDIP Package . . . . . . . . . . . . . . 60 N/A

28 Ld SOIC Package . . . . . . . . . . . . . . 70 N/A

28 Ld PLCC Package. . . . . . . . . . . . . . 70 N/A

Maximum Junction Temperature

Ceramic Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175oC

Plastic Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC and PLCC - Lead Tips Only)

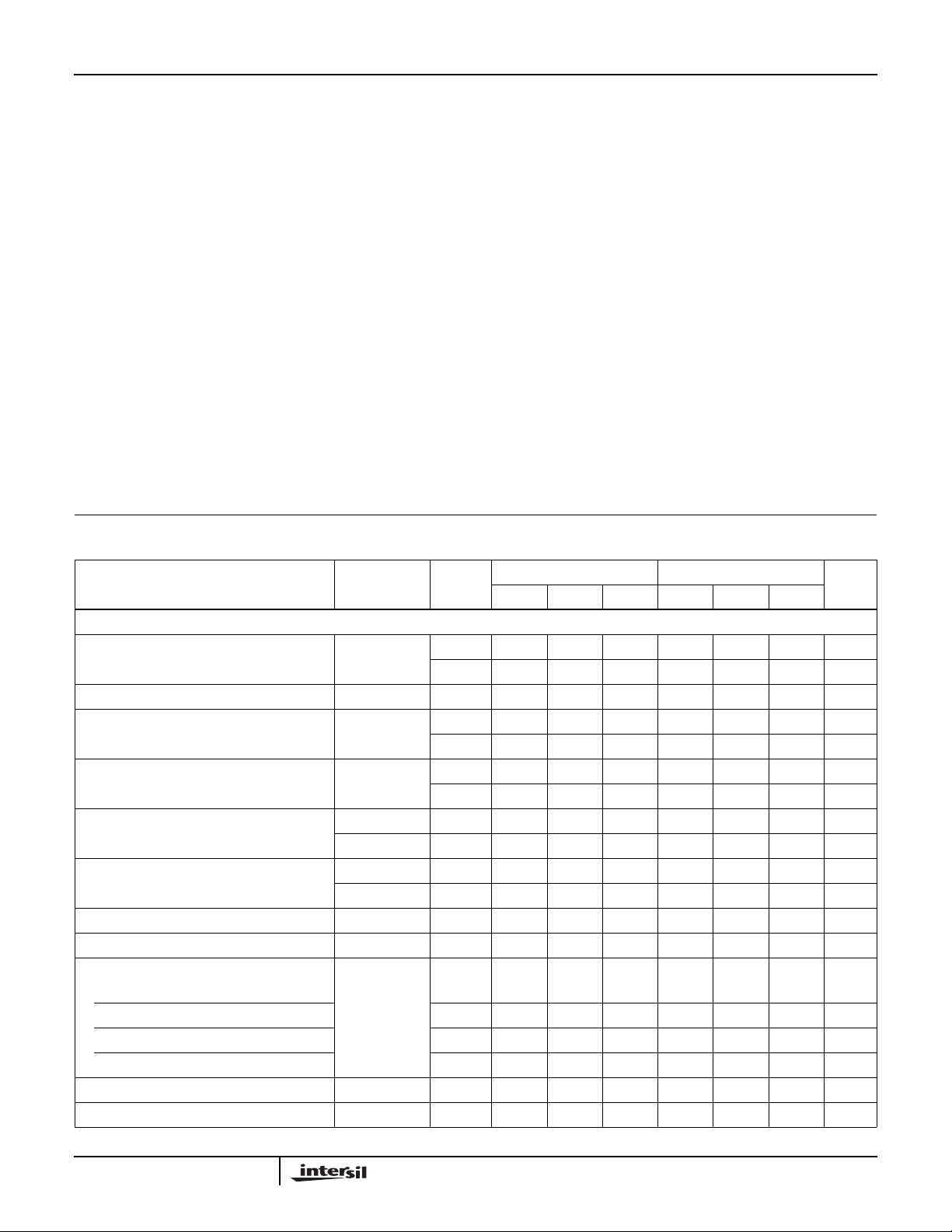

Electrical Specifications Supplies = +15V, -15V; V

Unless Otherwise Specified. For Test Conditions, Consult Test Circuits Section

TEST

PARAMETER

DYNAMIC CHARACTERISTICS

Access Time, t

Break-Before-Make Delay, t

Enable Delay (ON), t

Enable Delay (OFF), t

Settling Time, t

(HI-506 and HI-507)

Settling Time, t

(HI-508 and HI-509)

Off Isolation Note 6 25 50 68 - 50 68 - dB

Channel Input Capacitance, C

Channel Output Capacitance, C

HI-506 25 - 52 - - 52 - pF

HI-507 25 - 30 - - 30 - pF

HI-508 25 - 17 - - 17 - pF

HI-509 25 - 12 - - 12 - pF

Digital Input Capacitance, C

Input to Output Capacitance, C

A

OPEN

ON(EN)

OFF(EN)

S

S

S(OFF)

D(OFF)

A

DS(OFF)

CONDITIONS

To 0.1% 25 - 1.2 - - 1.2 - µs

To 0.01% 25 - 2.4 - - 2.4 - µs

To 0.1% 25 - 360 - - 360 - ns

To 0.01% 25 - 600 - - 600 - ns

(Logic Level High) = 2.4V; VAL (Logic Level Low) = 0.8V,

AH

TEMP

(oC)

25 - 250 500 - 250 - ns

Full - - 1000 - - 1000 ns

25 25 80 - 25 80 - ns

25 - 250 500 - 250 - ns

Full - - 1000 - - 1000 ns

25 - 250 500 - 250 - ns

Full - - 1000 - - 1000 ns

25 -10- -10-pF

25 - 6 - - 6 - pF

25 - 0.08 - - 0.08 - pF

-2 -4, -5, -9

UNITSMIN TYP MAX MIN TYP MAX

7

Loading...

Loading...