Intersil Corporation HI3197 Datasheet

HI3197

Data Sheet October 1998 File Number 4356.1

10-Bit, 125 MSPS D/A Converter

The HI3197 is a high-speed D/A converter which can

perform the multiplexedinputofthetwosystem10-bitdata.

The maximum conversion rate achieves 125 MSPS. The

multiplexed operation is possible by the 1/2 frequencydivided clock or by halving the frequency of the clock with

the clock frequency divider circuit having the reset pin in

the IC. The data input is TTL; the clock input pin and reset

input pin can select either TTL or PECL according to the

application.

Ordering Information

TEMP.

PART NUMBER

HI3197JCQ -20 to 75 48 Ld MQFP/

RANGE (oC) PACKAGE PKG. NO.

Q48.7x7-S

PQFP

Pinout

Features

• Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Bits

• Conversion Rate 125 MSPS (PECL)

• Data Input Level. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .TTL

• Low Power Consumption . . . . . . . . . . . . . . . 400mW (Typ)

• Low Glitch Energy . . . . . . . . . . . . . . . . . . . . . . . . 1.5pV•s

• Clock, Reset Input Level: TTL and PECL Compatible 2:1

•

• Voltage Output (50Ω Load Drive Possible)

• Single Power Supply or ±Dual Power Supplies

• Polarity Switching Function of Reset Signal

Applications

• LCD

• DDS

• HDTV

• Communications (QPSK, QAM)

HI3197 (MQFP)

TOP VIEW

100 MSPS (TTL)

Multiplexed Input Function

1

/2 Frequency-Divided Clock Output Possible by the Built-

In Clock Frequency Divider Circuit

AGND2

VOCLP

R POLARITY

INV

PS

DV

CC1

NC

DGND1

(MSB) DA9

DA8

DA7

DA6

CC2

SETVREF

V

AV

37

38

39

40

41

42

43

44

45

46

47

48

1234

DA4

DA5

CC2

CC0

AV

DV

AOUTN

AOUTP

AGND2

DA3

DA2

DA1

(LSB) DA0

(MSB) DB9

DB8

C3

DB7

C2

DB6

C1

12111098765

DB5

DGND2

252627282930313233343536

24

23

22

21

20

19

18

17

16

15

14

13

DB4

RESETN/E

RESETP/E

RESET/T

CLKN/E

CLKP/E

CLK/T

DIV2OUT

DIV2IN

DB0 (LSB)

DB1

DB2

DB3

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Copyright © Intersil Corporation 1999

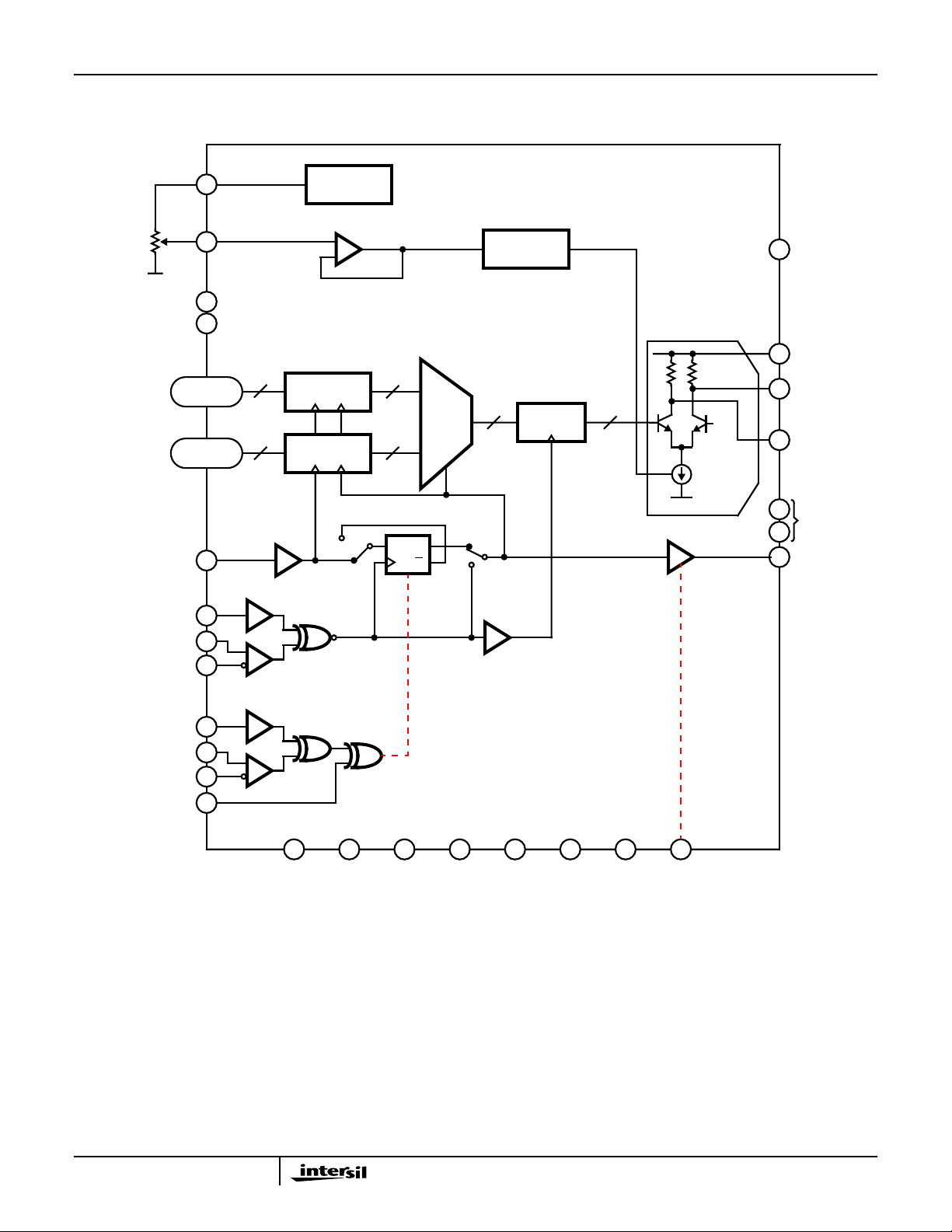

Block Diagram

V

REF

V

SET

AGND2

DV

CC1

DV

CC2

DA0 TO DA9

DB0 TO DB9

1 TO 6

45 TO 48

35

42

29

10-BIT 10-BIT

INPUT LATCH

INPUT LATCH7 TO 16

HI3197

BGR34

10-BIT

CURRENT

CONT.

LATCH

10-BIT

D/A

RO = 50Ω

36 AV

AV

30

32

A

31 A

CC2

CC0

OUTP

OUTN

+

-

10-BIT10-BIT

MUX

DIV2IN

CLK/T

CLKP/E

CLKN/E

RESET/T

RESETP/E

RESETN/E

R POLARITY

AGND2

17

19

20

21

22

23

24

39

44 25 26 27 28 41 40 38

DGND1 DGND2 C1 C2 C3 PS INV VOCLP

D Q

Q

AGND2

3337AGND2

18 DIV2OUT

2

HI3197

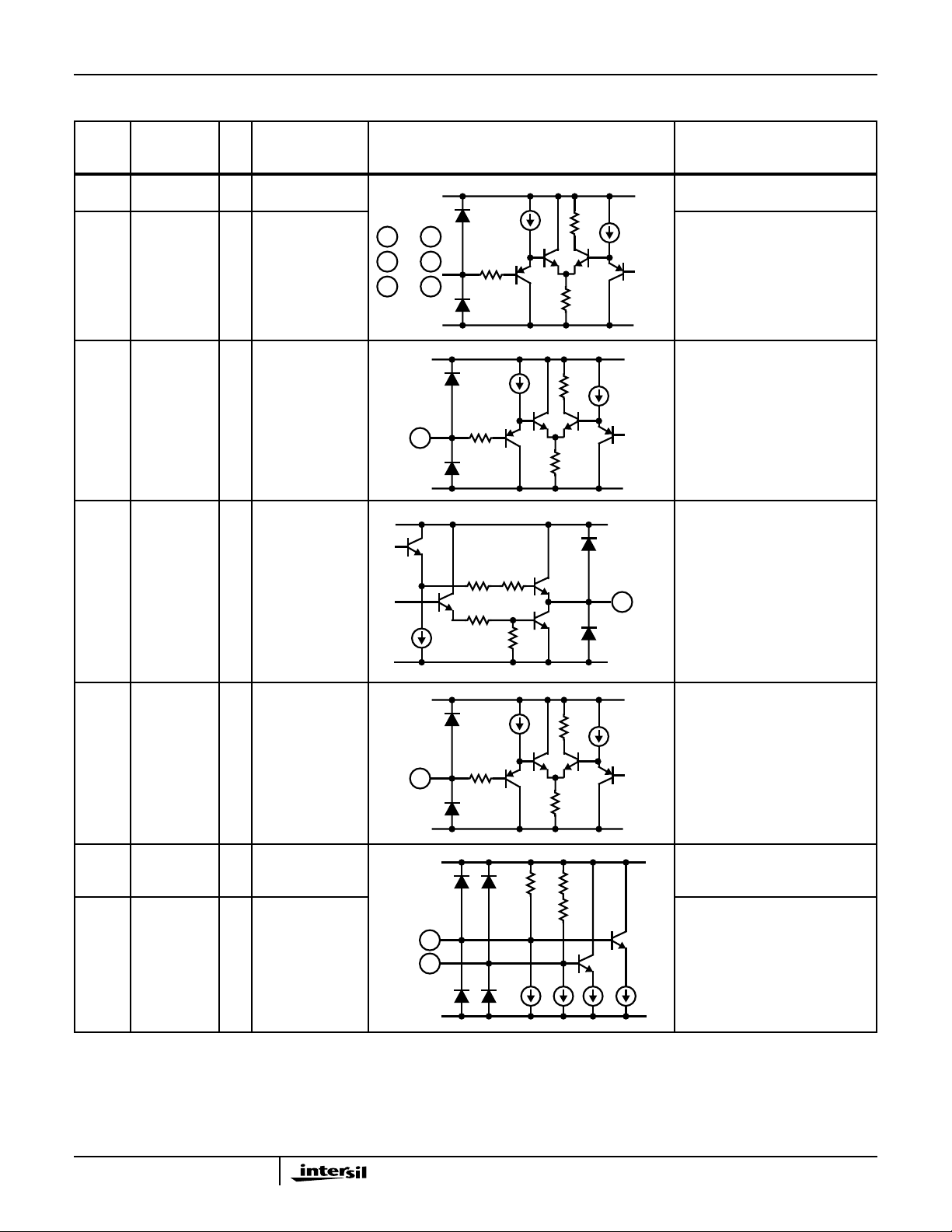

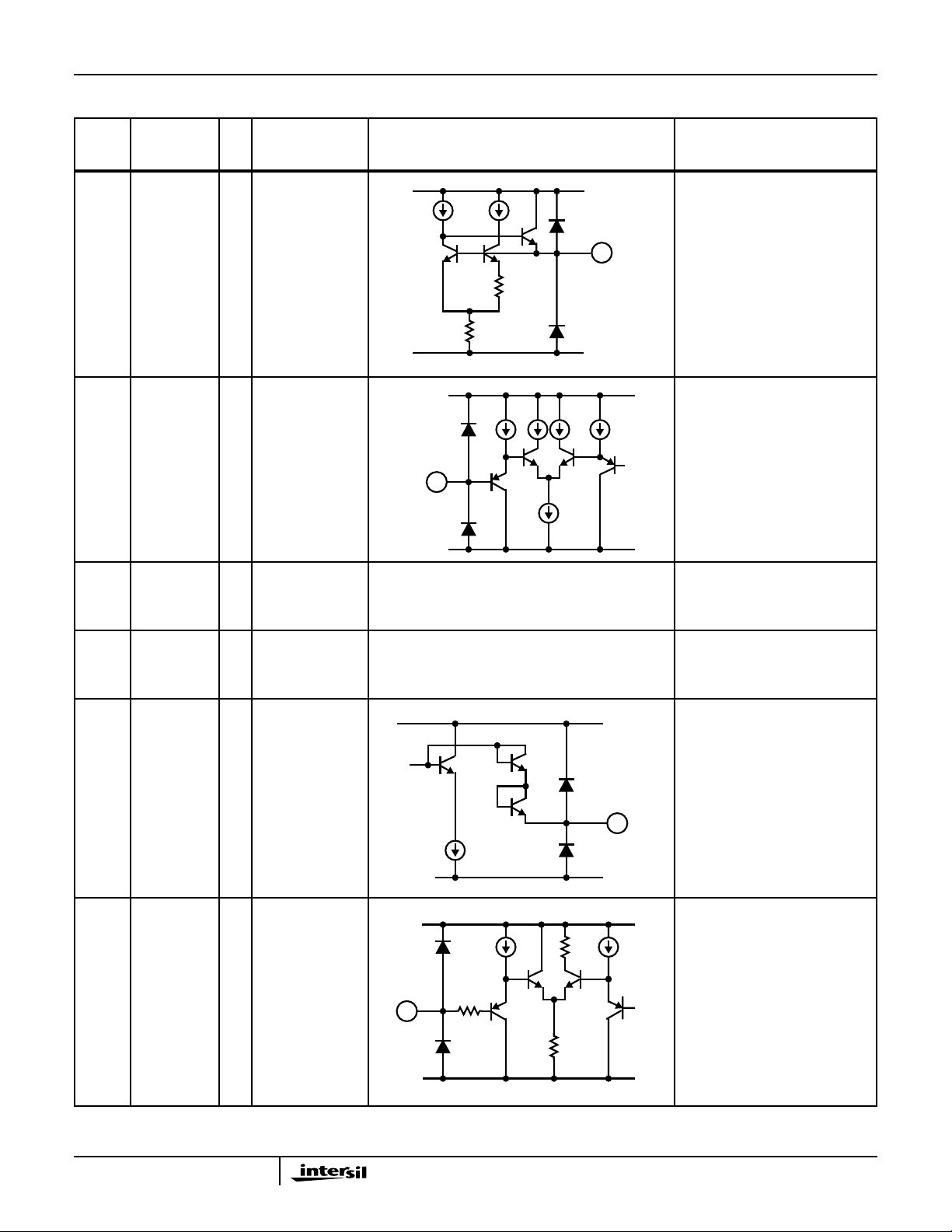

Pin Descriptions and I/O Pin Equivalent Circuits

TYPICAL

VOLTAGE

PIN NO SYMBOL I/O

1 to 6

DA0 to DA9 I TTL Side A Data Input.

45 to48

7 to 16 DB0 to DA9 I TTL Side B Data Input.

17 DIV2IN I TTL

18 DIV2OUT O TTL

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

DV

CC1

6

1

TO

48

45

7

DV

TO

TO

DGND1

CC1

16

V

REF

1

/2Frequency-Divided Clock Input.

Use this pin for MUX.1A or MUX.2

mode. Leave openfor othermodes .

V

DV

CC1

REF

1

/2Frequency-Divided Clock Output. The signal with the1/2fre-

17

DGND1

quency dividedclock (DIV2OUT) is

output for MUX.1A mode. Leave

open for other modes.

18

DGND1

19 CLK/T I TTL Clock Input. Use this pin when the

DV

CC1

clock is input in the TTL level. At

this time, leave Pins 20 and 21

open.

V

19

DGND1

20 CLKP/E I PECL Clock Input. Use this pin when the

DV

CC1

REF

clock is input in PECL level.Atthis

time, leave Pin 19 open.

21 CLKN/E I PECL CLKP/E Complementary Input.

When left open, this pin goes to

20

21

the threshold potential. Operation

is possible only with CLKP/E, but

complementary input is recommended to attain fast and stable

operation.

DGND1

3

HI3197

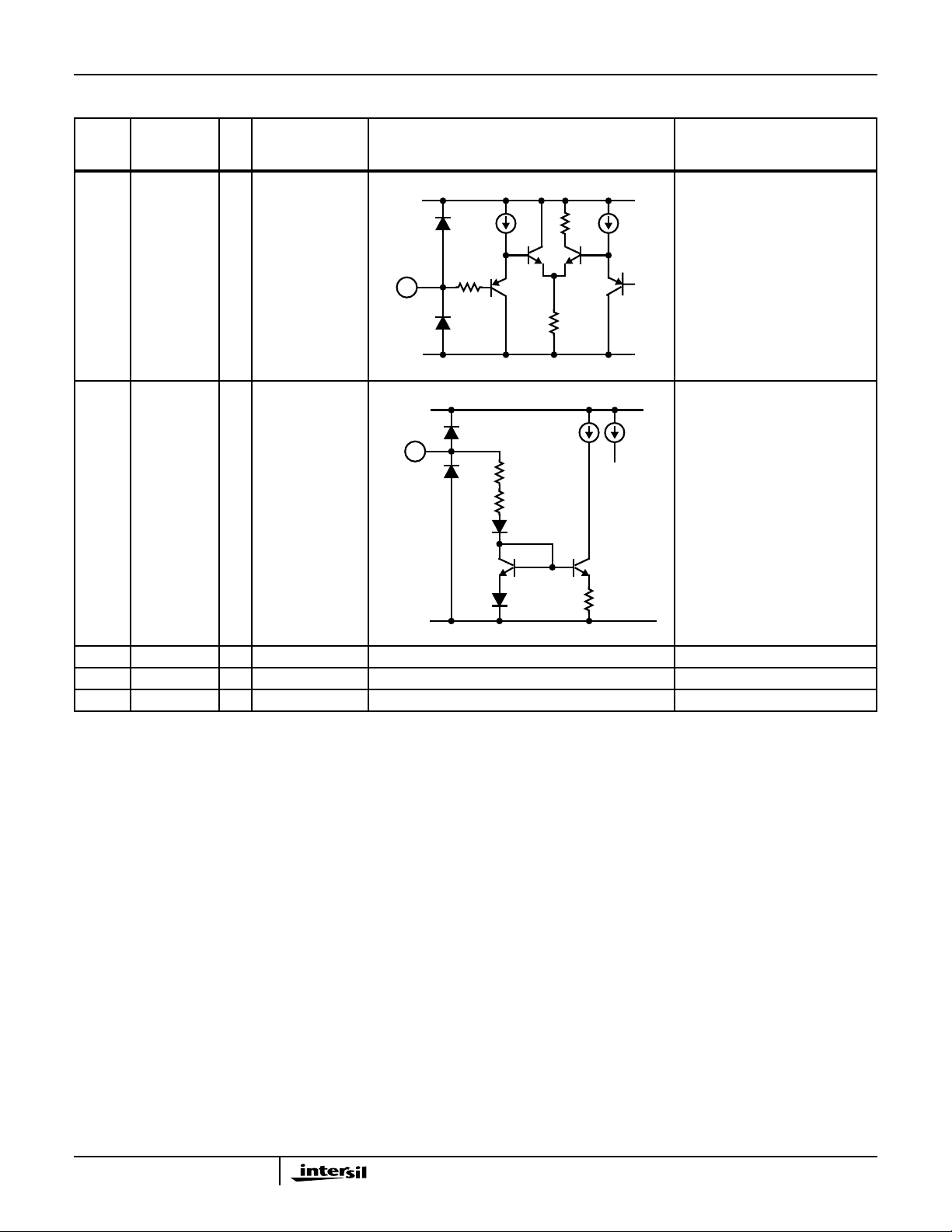

Pin Descriptions and I/O Pin Equivalent Circuits (Continued)

TYPICAL

VOLTAGE

PIN NO SYMBOL I/O

22 RESET/T I TTL Reset signalinput. When the multi-

23 RESETP/E I PECL

24 RESETN/E I PECL

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

DV

CC1

ple HI3197 are operated at a time

for MUX.1A or MUX.1B mode, the

start timing of the internal1/2frequency divider circuits should be

matched.

V

22

REF

At this time, the reset signal is

used; when the reset signal is the

TTL level, Pin 22 is used and Pins

DGND1

DV

CC1

23 and 24 are left open. When the

reset signal is the PECL level, Pins

23 and 24 are used and Pin 22 is

left open. For the PECL level, operation is possible only with RESETP/E as with the case for the

clock. The reset signal polarity can

23

24

be set by Pin 39 (RPOLARITY).

Leave the reset pin open when the

other modes are used.

DGND1

25 DGND2 Single Power

Digital Power Supply.

Supply: GND Dual

Power Supplies:

-5V

26 C1 I TTL Function setting.

27 C2 I TTL

DV

CC1

28 C3 I TTL

26

V

REF

Digital Power Supply.

29 DV

CC2

27

28

DGND1

Single Power

Supply: +5V Dual

Power Supplies:

GND

30 AV

CC0

31 OUTN O AV

CC0

- V

FS

RO RO

AV

CC0

31

32

Analog Output Power Supply.

D/A Negative Output. The inversion

of the D/A positive output pin is output. Terminate the inversion without

pin with 50Ω when the inversion output is not used and the positive output is terminated with 50Ω.

32 AOUTP O AV

CC0

- V

FS

D/A positive output.

33 AGND2 Single Power

Supply: GND

Dual Power

Supplies: -5V

4

AGND2

Analog Ground.

HI3197

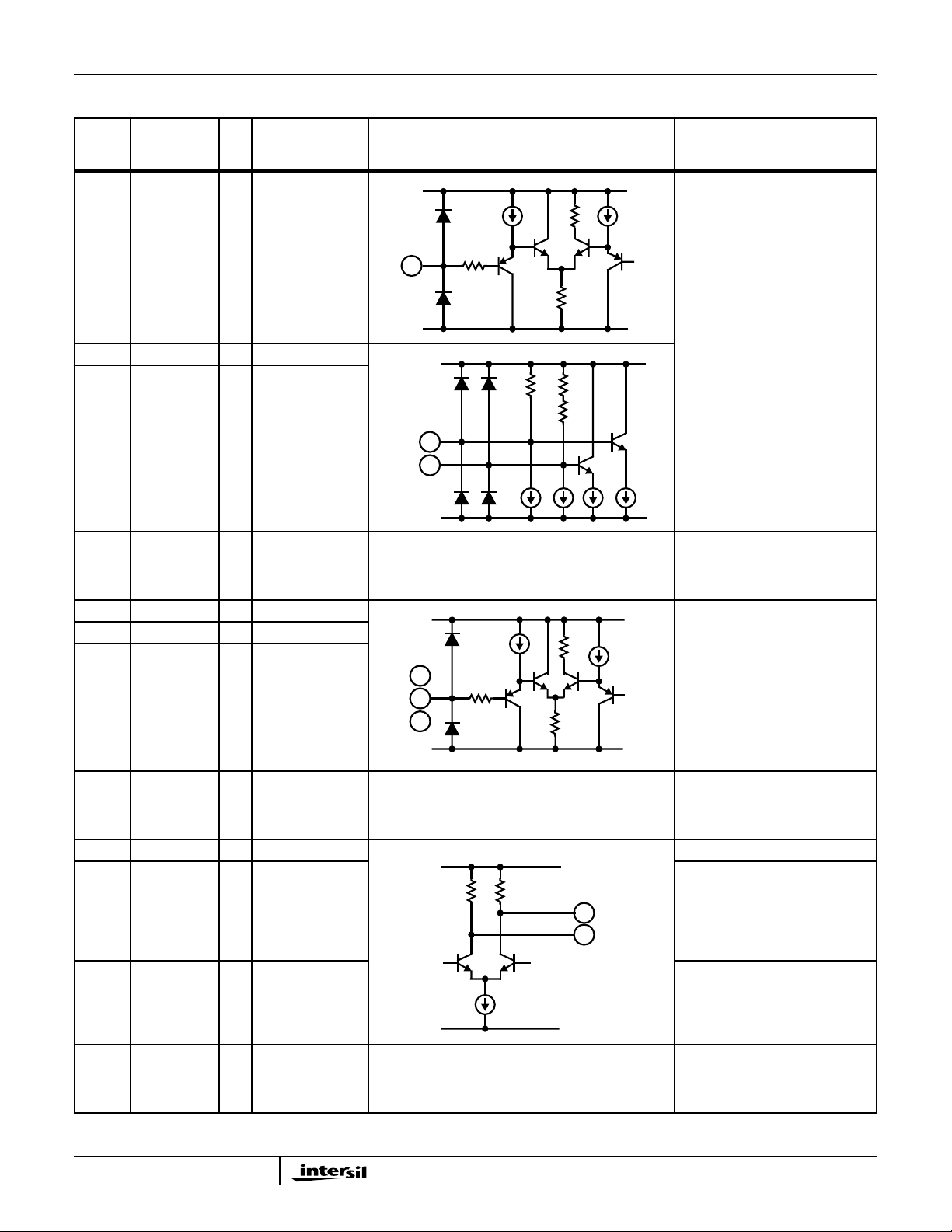

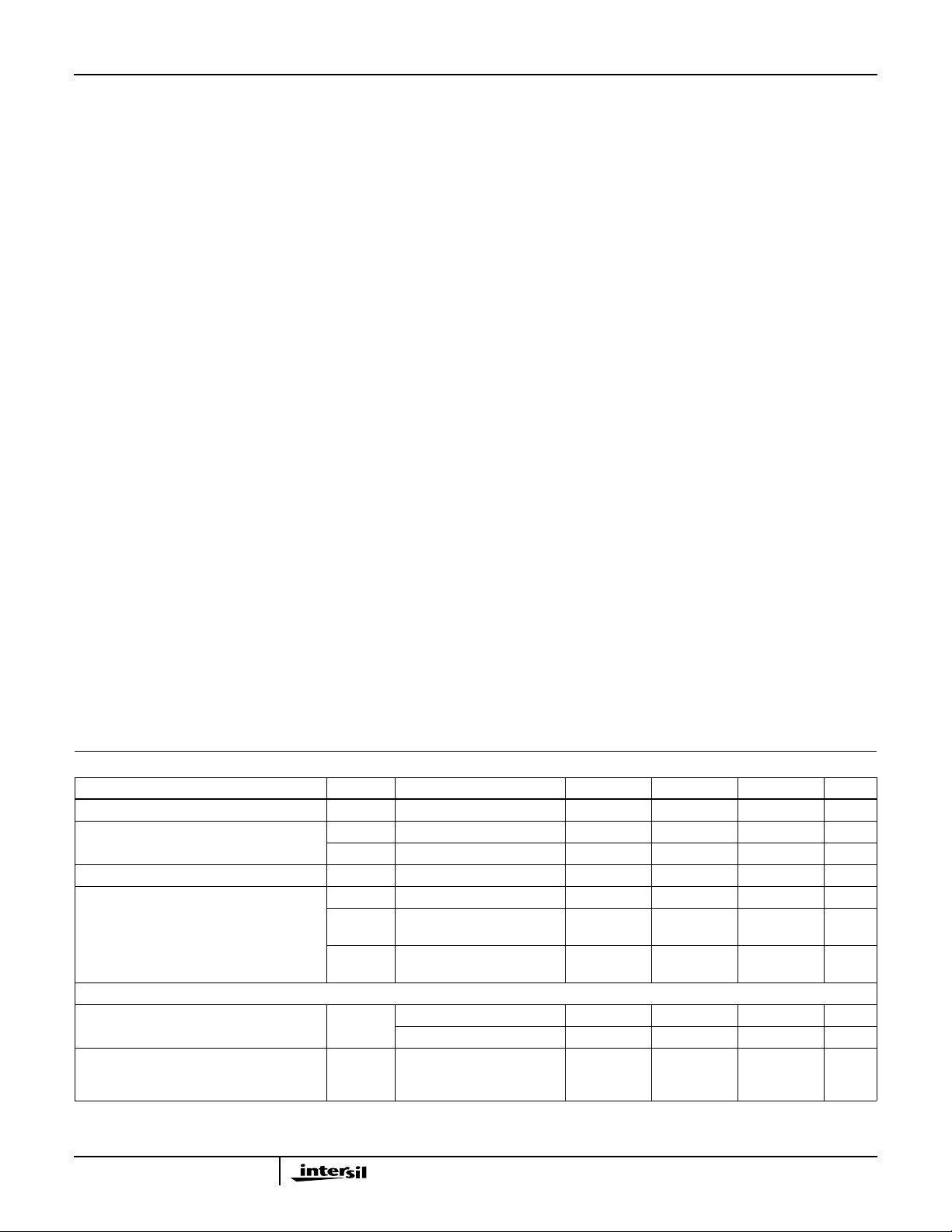

Pin Descriptions and I/O Pin Equivalent Circuits (Continued)

TYPICAL

VOLTAGE

PIN NO SYMBOL I/O

34 V

REF

O AGND +1.2V Analog Reference Voltage Output.

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

AV

CC2

34

AGND2

35 V

36 AV

SET

CC2

I AGND2 + 0.7V to

AGND2 + 1.03V

Single Power

AV

CC2

Full scale adjustment.

35

Analog Power Supply.

Supply: +5V

Dual Power

Supplies: GND

37 AGND2 Single Power

Analog Power Supply

Supply: GND

Dual Power

Supplies: -5V

38 VOCLP I Clamp Voltage TTL Output High LevelClamp. The

DV

CC1

TTL level signal is output from the

DIV2OUT pin for MUX.1A mode.

The TTL high level voltage is

clamped to the value approximate-

ly equivalent to the voltage sup-

plied to this pin. Leave the VOCLP

38

pin open for other modes.

DGND1

39 P Polarity I TTL Reset signal polarity switching. At

DV

CC1

39

DGND1

high level, the reset polarity is ac-

tive high; at low level, active low.

V

REF

5

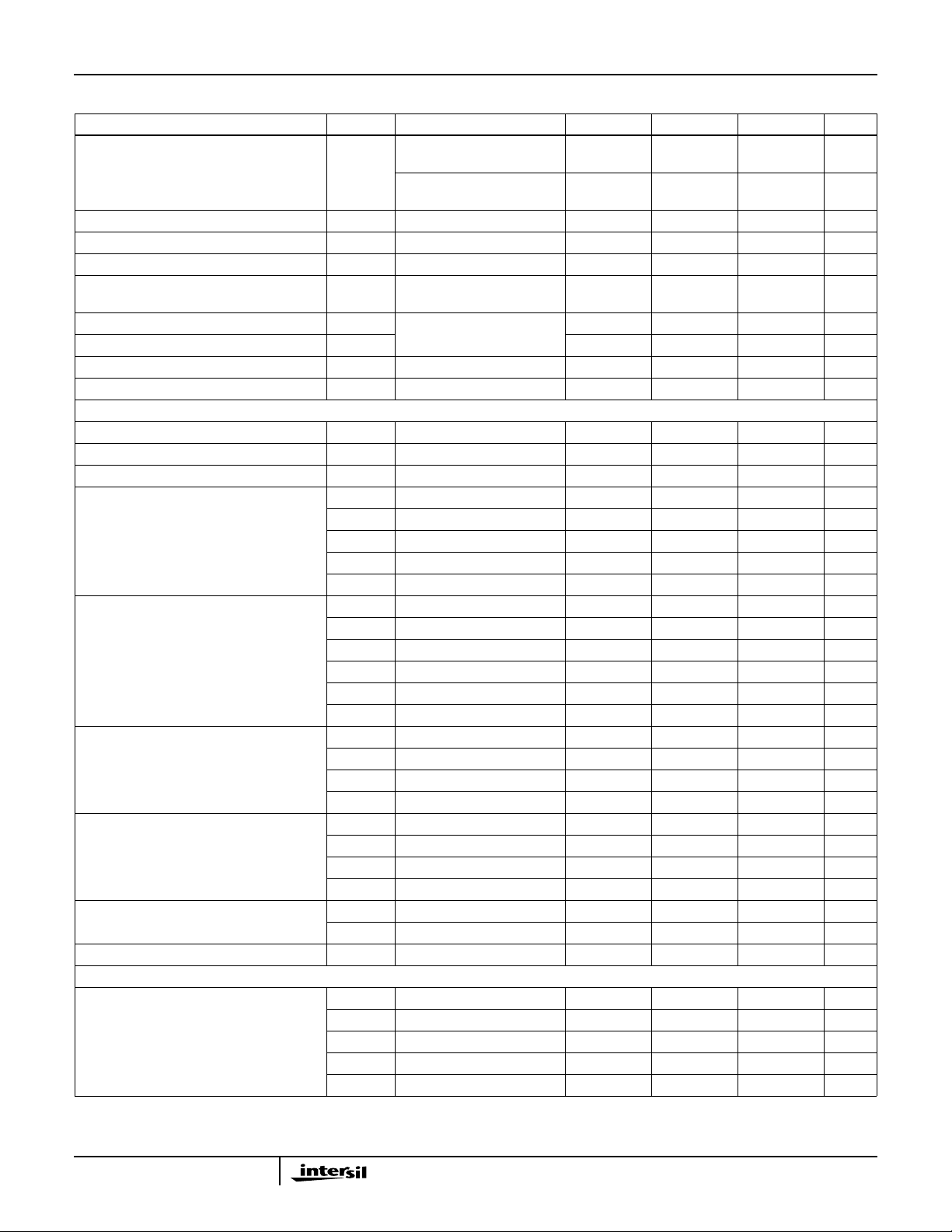

HI3197

Pin Descriptions and I/O Pin Equivalent Circuits (Continued)

TYPICAL

VOLTAGE

PIN NO SYMBOL I/O

40 INV I TTL Analog Output polarity in version.

41 PS I TTL Power saving. Power saving at low

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

DV

CC1

40

DGND1

DV

CC1

41

The analog output is inverted at low

level.

V

REF

level. Normally pull up the PS pin

to high levelas this pin is open low.

DGND1

42 DV

CC1

5V Digital Power Supply.

43 NC No connection.

44 DGND1 0V Digital Ground.

6

HI3197

Absolute Maximum Ratings T

Supply Voltage (AV

AGND2, DGND2 . . . . . . . . . . . . . . . . . . . . . . . . . . . -7.0 to +0.5V

DV

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5 to +7.0V

CC1

AV

- AGND2. . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5 to +7.0V

CC2

AV

- AGND2. . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5 to +7.0V

CC0

DV

- DGND2 . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5 to +7.0V

CC2

Input Voltage

V

, . . . . . . . . . . . . . . . . . . . . . . . .AGND2 -05 to AV

SET

TTL Pin . . . . . . . . . . . . . . . . . . . . . DGND1 -0.5 to DV

PECL Pin, . . . . . . . . . . . . . . . . . . . DGND1 -0.5 to DV

PS. . . . . . . . . . . . . . . . . . . . . . . . . . DGND1 -0.5 to DV

(Others), VOCLP . . . . . . . . . . . . . . . . . DGND1 -0.5 to DV

CC0

, AV

CC2

, DV

=25oC Thermal Information

A

) . . . . . . . . . . -0.5 to +7.0V

CC2

Thermal Resistance (Typical, Note 1) θJA (oC/W)

MQFP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Maximum Power Dissipation, PD. . . . . . . . . . . . . . . . . . . . . . . .1.4W

(When mounted on a glass fabric base epoxy board with 76mm x

114mm, 1.6mm thick)

Maximum Junction Temperature (Hermetic Pac kage or Die) . . .175oC

Maximum Junction Temperature (Plastic Package) . . . . . . . .150oC

+ 0.5V

CC2

CC1

CC1

CC1

+ 0.5V

+ 0.5V

+ 0.5V

CC1

+ 5V

Maximum Storage Temperature Range, T

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

Recommended Operating Conditions

WITH A SINGLE POWER SUPPLY MIN TYP MAX

Supply Voltage

AV

, AV

CC0

. . . . . . . . . . . . . . . . . . . . . +4.75 +5.0 +5.25V

CC2

AGND2. . . . . . . . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

DV

. . . . . . . . . . . . . . . . . . . . . . . . . . . +4.75 +5.0 +5.25V

CC1

DGND1. . . . . . . . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

DV

. . . . . . . . . . . . . . . . . . . . . . . . . . . -4.75 +5.0 +5.25V

CC2

DGND2. . . . . . . . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

WITH DUAL POWER SUPPLIES MIN TYP MAX

Supply Voltage

AV

, AV

CC0

. . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

CC2

AGND2. . . . . . . . . . . . . . . . . . . . . . . . . . . -5.50 -5.0 -4.75V

DV

. . . . . . . . . . . . . . . . . . . . . . . . . . . 4.75 5.0 +5.25V

CC1

DGND1. . . . . . . . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

DV

. . . . . . . . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

CC2

DGND2. . . . . . . . . . . . . . . . . . . . . . . . . . . -5.50 -5.0 -4.75V

Recommended Operating Conditions (Applying to Single and Dual Power Supplies)

MIN TYP MAX

Analog Input Voltage , V

. . .AGND2 + 0.7 - AGND2 + 1.03V

SET

Digital Input Voltage

PECL, VIH . . . . . . . . . . . . . . .DGND1 + 2.6 DV

CC1

PECL, VIL . . . . . . . . . . . . . . . - VIH - 0.8 VIH - 0.4V

TTL, VIH. . . . . . . . . . . . . . . . .DGND1 + 2.0 - -

TTL, VIL. . . . . . . . . . . . . . . . . - - DGND1 + 0.8V

PS, VIH. . . . . . . . . . . . . . . . . .DGND1 + 2.0 - -

PS, VIL. . . . . . . . . . . . . . . . . . - - DGND1 + 0.8V

Other, V

. . . . . . . . . . . .DGND1 + 2.7 - DV

OCLP

CC1

Ambient Temperature (TA). . . . . . . . . . . . . . . . . . . . . -20oC to 75oC

Clock Pulse Width

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4ns (Min)

PW1

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4ns (Min)

PW0

Load Resistance, RL . . . . . . . . . . . . . . . . . . 50 50 ≥10kΩ

Analog Output Full Scale Voltage

RL≥ 10kΩ, VFS . . . . . . . . . . . . . . . . . . . . . 1.5 2.0 2.2V

RL = 50Ω, VFS. . . . . . . . . . . . . . . . . . . . . . 0.75 1.0 1.2V

. . . . -65oC to 150oC

STG

MIN TYP MAX

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications V

= ±5V, AV = +1, RL = 100Ω

SUPPLY

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Resolution n - 10 - Bit

Maximum Conversion Rate f

CECL

f

CTTL

PECL Operation - - 125 MSPS

TTL Operation - - 100 MSPS

Integral Linearity Error INL VFS = 1V - - ±1.2 LSB

Differential Linearity Error DNL - - -0.85 to 0.5 LSB

DNL AOUTP Transitions from

- - -1.2 to 0.5 LSB

0000111111 - 0001000000

DNL AOUTN Transitions from

- - -1.2 to 0.5 LSB

1111000000 - 1110111111

ANALOG OUTPUT

Output Full-Scale Voltage V

RL = 50Ω 0.75 1 1.05 V

FS

RL ≥ 10kΩ 1.5 2.0 2.2 V

Compliance Voltage

V

V

OC(MIN)

OC(MAX)

: (AV

CC0-VFS -DVCC2

: (AV

CC0-VOF -DVCC2

) ≥ -2.V,

) ≥ 1.5

V

OC

Measured to DV

CC2

-2.1 - 1.5 V

7

HI3197

Electrical Specifications V

= ±5V, AV = +1, RL = 100Ω (Continued)

SUPPLY

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Output Zero Offset Voltage V

Output Resistance R

Output Capacitance C

Absolute Amplitude Error EG V

Absolute Amplitude Error

TCG VFS = 1V at 25oC - - 60 ppm/oC

OF

O

O

RL ≥ 10kΩ,

V

= AGND2 + 0.9375V

SET

RL = 50Ω,

V

= AGND2 + 0.9375V

SET

0 - 20 mV

0 - 10 mV

-50-Ω

-10-pF

= AGND2 + 0.9375V -4 - 4 % of FS

SET

Temperature Characteristics

Analog Output Rise Time t

Analog Output Fall Time t

Settling Time t

SET

RL = 50Ω, VFS = 1V,

r

10 - 90%

f

0.85 - 1.05 ns

0.75 - 0.85 ns

- - 3.5 ns

Glitch Energy GE - 1.5 5.0 pVS

REFERENCE

V

Pin Voltage V

REF

V

Temperature Drift - - 250 ppm/oC

REF

V

Multiplying Bandwidth 100mV

REF

Digital Input (TTL Pin) V

Digital Output (DIV2OUT TTL Pin) V

Digital Input (PECL Pin) V

Digital Input Current (PS) V

Clamp Pin Input Current (V

)I

OCLP

Digital Input Capacitance C

REFIREF

IH

V

IL

V

TH

I

IH

I

IL

OHIOH

V

OL

I

OZ

I

OZ

t

r

t

f

IH

V

IL

I

IH

I

IL

IH

V

IL

I

IH

I

IL

CCLP

I

CCLP

IN

= 1mA AGND2+1.18 AGND2+1.25 AGND2+1.32 V

Sinewave at -3dB 50 - - MHz

P-P

2--V

- - 0.8 V

- 1.5 - V

VIH = 3.5V -1 - 1 µA

VIL = 0.2V -2 - 0 µA

= -2mA 2.4 - - V

IOL= 1mA - - 0.5 V

VO= 5V 10 - 100 µA

VO= 0V -1 - 1 µA

0.8 to 2.4V (CL = 10pF) 1.0 - 1.5 ns

2.4 to 0.8V (CL = 10pF) 0.6 - 1.2 ns

DV

VIH = DV

VIL= DV

- 1.5 - DV

CC1

DV

- 3.2 - DV

CC1

- 0.8V 0 - 20 µA

CC1

- 1.5V -30 - 0 µA

CC1

- 0.5 V

CC1

- 1.4 V

CC1

2--V

- - 0.8 V

VIH = 3.5V -1 - 100 µA

VIL = 0.2V -1 - 0 µA

V

= DV

CCLP

V

CCLP

CC1

= 2.4V -60 - -10 µA

--5µA

-35pF

CURRENT CONSUMPTION

Supply Current (Operating) I

CC

DI

DI

AI

AI

Total Operating 63 96 129 mA

CC1

CC2

CC2

CC0

7 15.5 24 mA

13 19 25 mA

6 8.5 11 mA

37 53 68 mA

8

Loading...

Loading...