HI3086

August 1997

Features

• Differential Linearity Error. . . . . . . . . . . . . . . . . ±0.2 LSB

• Integral Linearity Error . . . . . . . . . . . . . . . . . . ±0.2 LSB

• Single +5V Power Supply Operation Available

• Low Input Capacitance . . . . . . . . . . . . . . . . . . . . . . . 7pF

• Wide Analog Input Bandwidth . . . . . . . . . . . . . 200MHz

• Low Power Consumption . . . . . . . . . . . . . . . . . .360mW

• CLK/2 Clock Output Pin

• Excellent Temperature Characteristics

• 1:2 Demultiplexed Output

1

• Internal

/2 Frequency Divider Circuit

(With Reset Function)

• Compatible with ECL, PECL and TTL Digital Input Levels

• Direct Replacement for Sony CXA3086

Applications

• RGB Graphics Processing (LCD, PDP)

• Digital Communications (QPSK, QAM)

• Magnetic Recording (PRML)

6-Bit, 140 MSPS, Flash A/D Converter

Description

The HI3086 is a 6-bit, high-speed, flash analog-to-digital converter optimized for high speed, low power, and ease of use.

With a 140 MSPS encode rate capability and full-power analog

bandwidth of 200MHz, this component is ideal for applications

requiring the highest possible dynamic performance.

To minimize system cost and power dissipation, only a +5V

power supply is required. The HI3086’s clock input interfaces

directly to TTL, ECL, or PECL logic and will operate with singleended inputs. The user may select 16-bit demultiplexed output

or 8-bit single-channel digital outputs. The demultiplexed mode

interleaves the data through two 8-bit channels at

rate. Operation in demultiplexed mode reduces the speed and

cost of external digital interfaces, while allowing the A/D

converter to be clocked to the full 140 MSPS conv ersion r ate .

Fabricated with an advanced bipolar process, the HI3086 is

provided in a space-saving 48-lead MQFP surface mount

plastic package and is specified over the -20

temperature range.

Ordering Information

PART

NUMBER

HI3086JCQ -20 to 75 48 Ld MQFP Q48.12x12-S

HI3086EVAL 25 Evaluation Board

TEMP.

RANGE (oC) PACKAGE PKG. NO.

1

/2 the clock

o

C to 75oC

Pinout

DGND2

P2D0 (LSB)

P2D1

P2D2

P2D3

P2D4

P2D5 (MSB)

DGND2

DV

CC2

RESETN/T

RESET/E

RESETN/E

CC2

DV

DV

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16

EE3

AGND

DV

HI3086 (MQFP)

TOP VIEW

CC1

DGND1

PS

NC

CC

RB

RBS

V

V

AV

CLKOUT

NC

INV

IN

V

NC

SELECT

RT

CC

V

AV

CC1

DV

DGND1

RTS

V

AGND

CC2

DV

373839404142434445464748

36

35

34

33

32

31

30

29

28

27

26

25

2423222120191817

DGND3

DGND2

P1D5 (MSB)

P1D4

P1D3

P1D2

P1D1

P1D0 (LSB)

DGND2

DV

CC2

CLK/T

CLKN/E

CLK/E

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

4-1406

File Number 4110.1

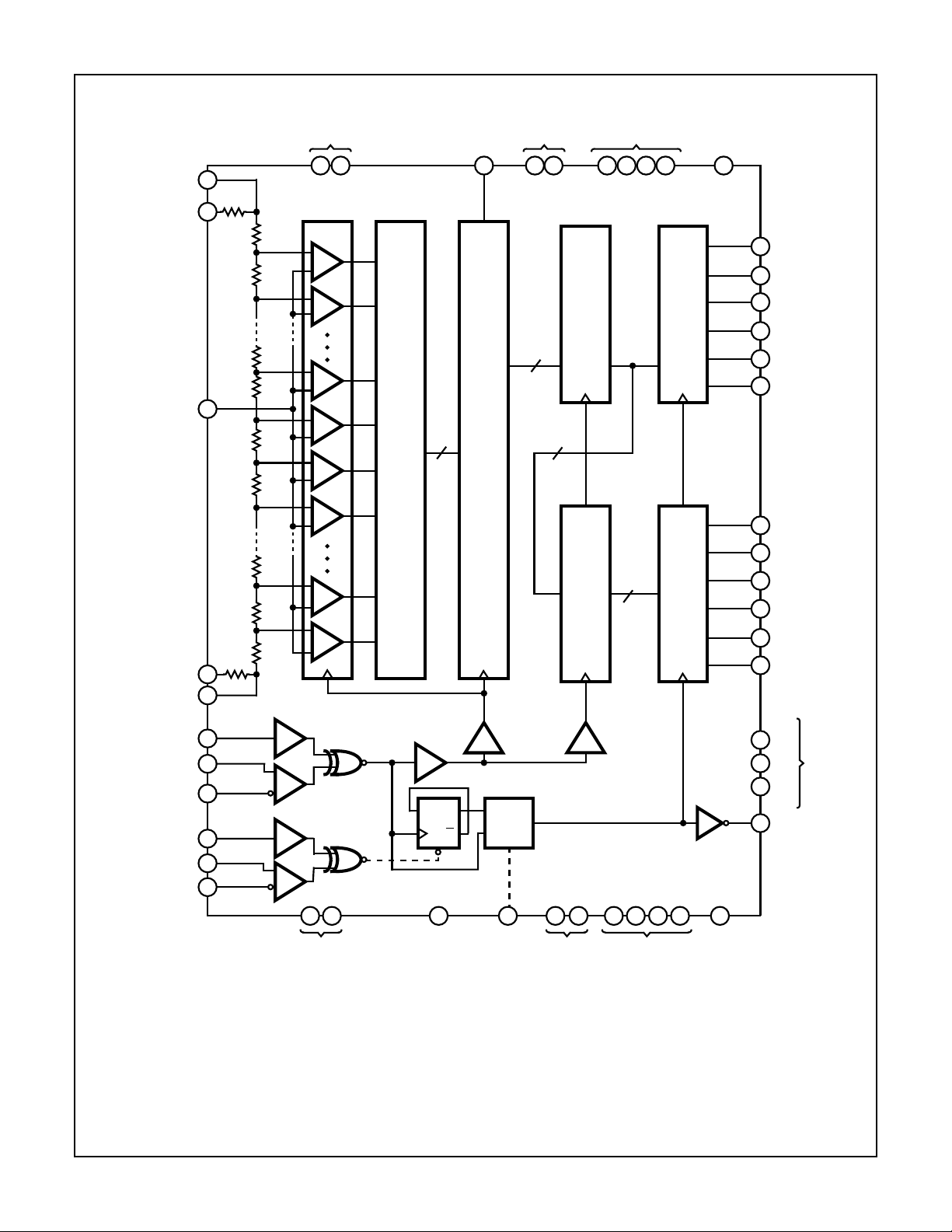

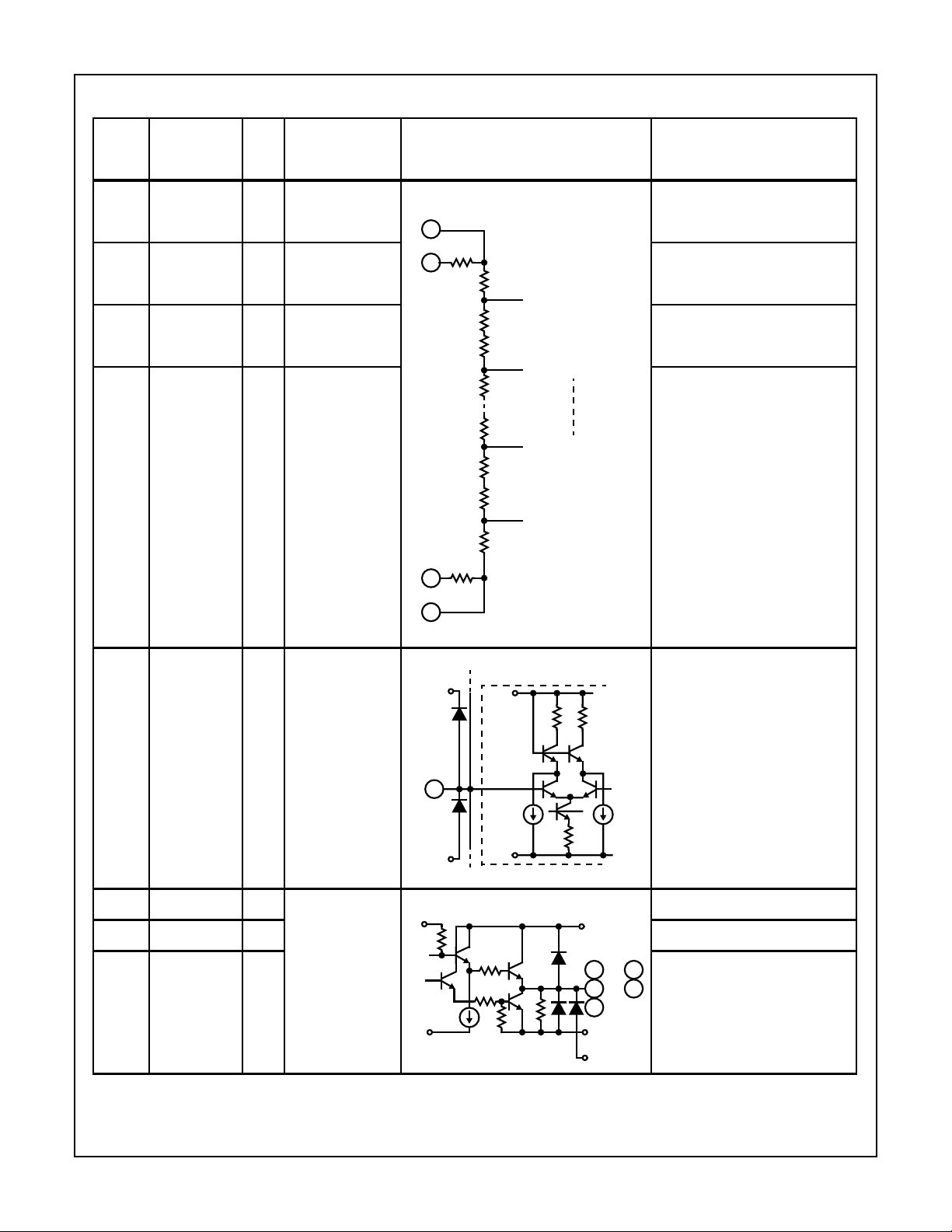

Functional Block Diagram

HI3086

V

V

RTS

V

V

V

RB

RBS

RT

AV

CC

22

R1

21

19

IN

16

15

R2

R

R

R

R

R

R

R

R

R

17 20 42 38 9 28 37 24

1

2

30

31

32

33

62

63

6-BIT

ENCODER

6-BIT LATCH

DV

CC1

47 48

6-BIT

6-BIT

LATCH B LATCH A

DV

CC2

6-BIT

DGND3INV

TTLOUT

TTLOUT

(MSB)

35

P1D5

34

P1D4

33

P1D3

32

P1D2

31

P1D1

30

P1D0

(LSB)

(MSB)

P2D5

7

6

P2D4

P2D3

5

P2D2

4

P2D1

3

P2D0

2

(LSB)

CLK/T

CLK/E

RESETN/T

RESETN/E

RESET/E

27

25

26CLKN/E

10

12

11

14 23 8 29 36 13141 463944

DELAY

DQ

18

40

45

SELECT

Q

DGND2DGND1AGND PS SELECT

DV

43NCCLKOUT

EE3

4-1407

HI3086

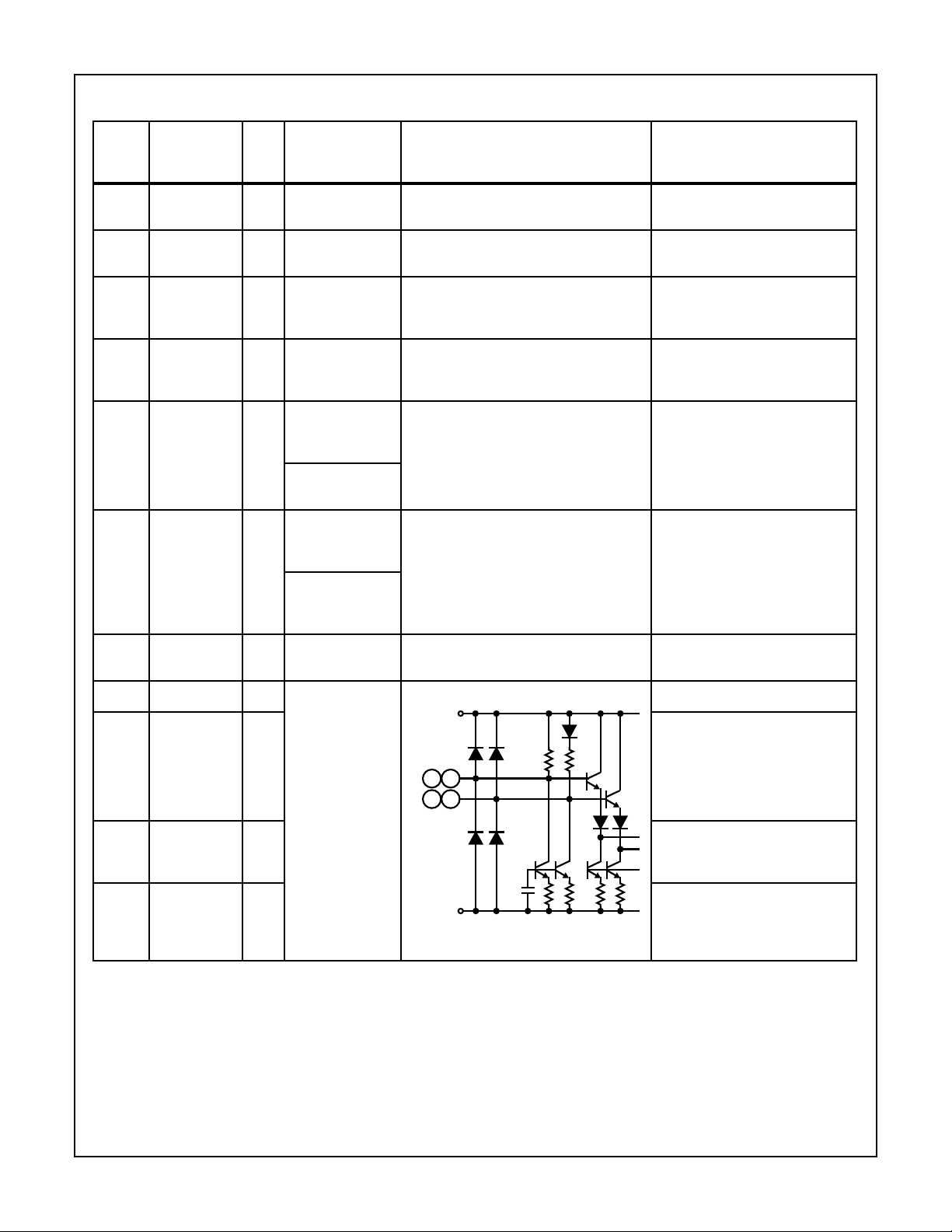

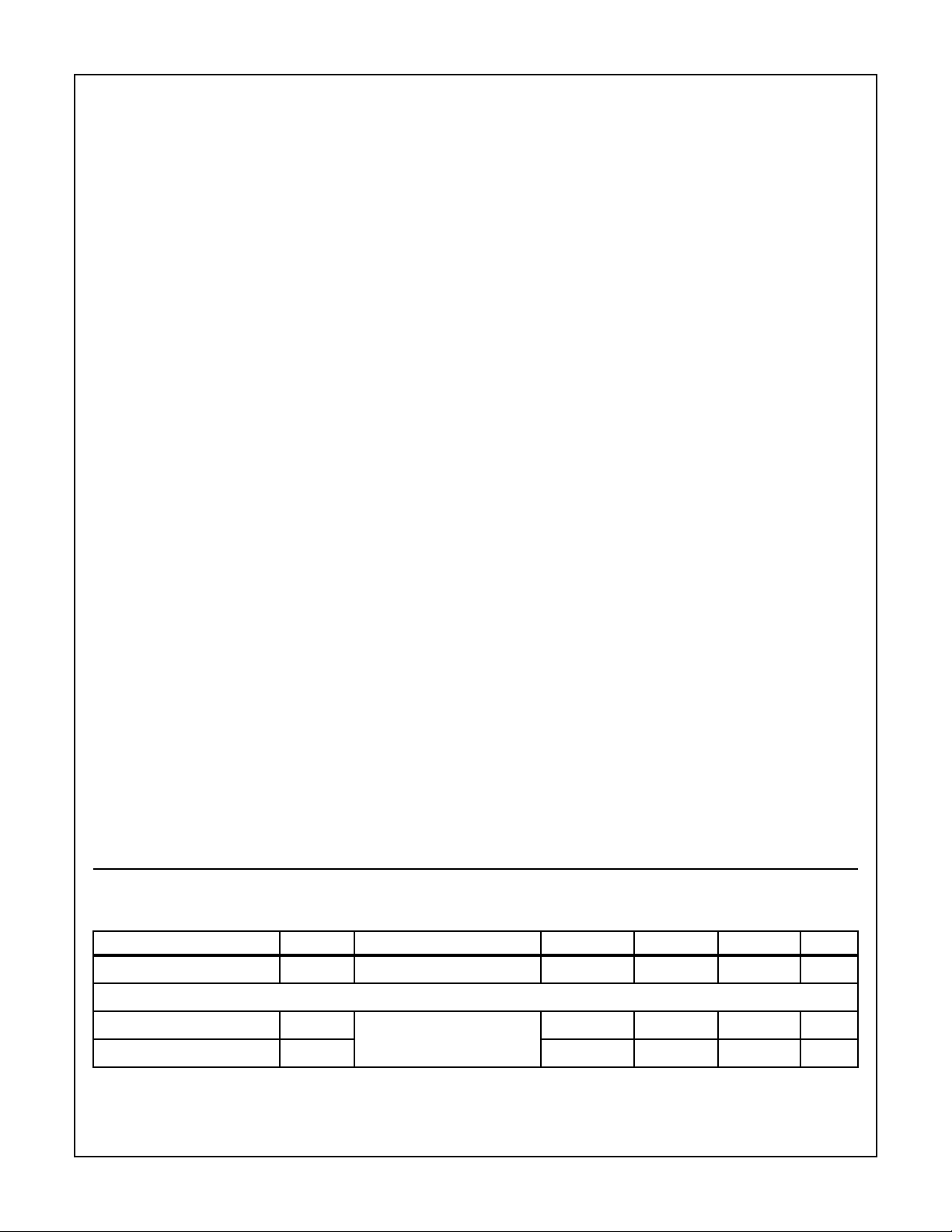

Pin Descriptions

TYPICAL

PIN

NO. SYMBOL I/O

14, 23 AGND GND Analog Ground. Separated from

VOLTAGE

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

the digital ground.

17, 20 AV

CC

+5V (Typ) Analog Power Supply. Separated

from the digital power supply.

1, 8, 29,

36, 39,

DGND1

DGND2

GND Digital Ground.

46

9, 28,

37, 38,

DV

DV

CC1

CC2

+5V (Typ) Digital Power Supply.

47, 48

24

DGND3

+5V (Typ) (With a

Single Power

Supply)

Digital Power Supply. Ground for

ECL input. +5V for PECL and TTL

input.

GND (With Dual

Power Supplies)

13

D

VEE3

GND (With a

Single Power

Supply)

Digital Power Supply. Ground for

ECL input. -5V for PECL and TTL

input.

-5V (Typ) (With

Dual Power

Supplies)

18, 40,

45

NC No Connect pin. Not connected

with the internal circuits.

25 CLK/E I ECL/PECL Clock input.

26

I CLK/E Complementary Input. When

DGND3

left open, this pin goes to the thresh-

CLKN/E

RR

12 25

2611

old potential. Only CLK/E can be

used for operation, but complementary input is recommended to attain

fast and stable operation.

12

11

RESETN/E

RESET/E

I Reset Input. When the input is set to

low level, the built-in CLK frequency

divider circuit can be reset.

1.2V

I RESETN/E Complementary Input.

DV

EE3

RR

When left open, this pin goes to the

threshold voltage. Only RESETN/E

can be used for operation.

4-1408

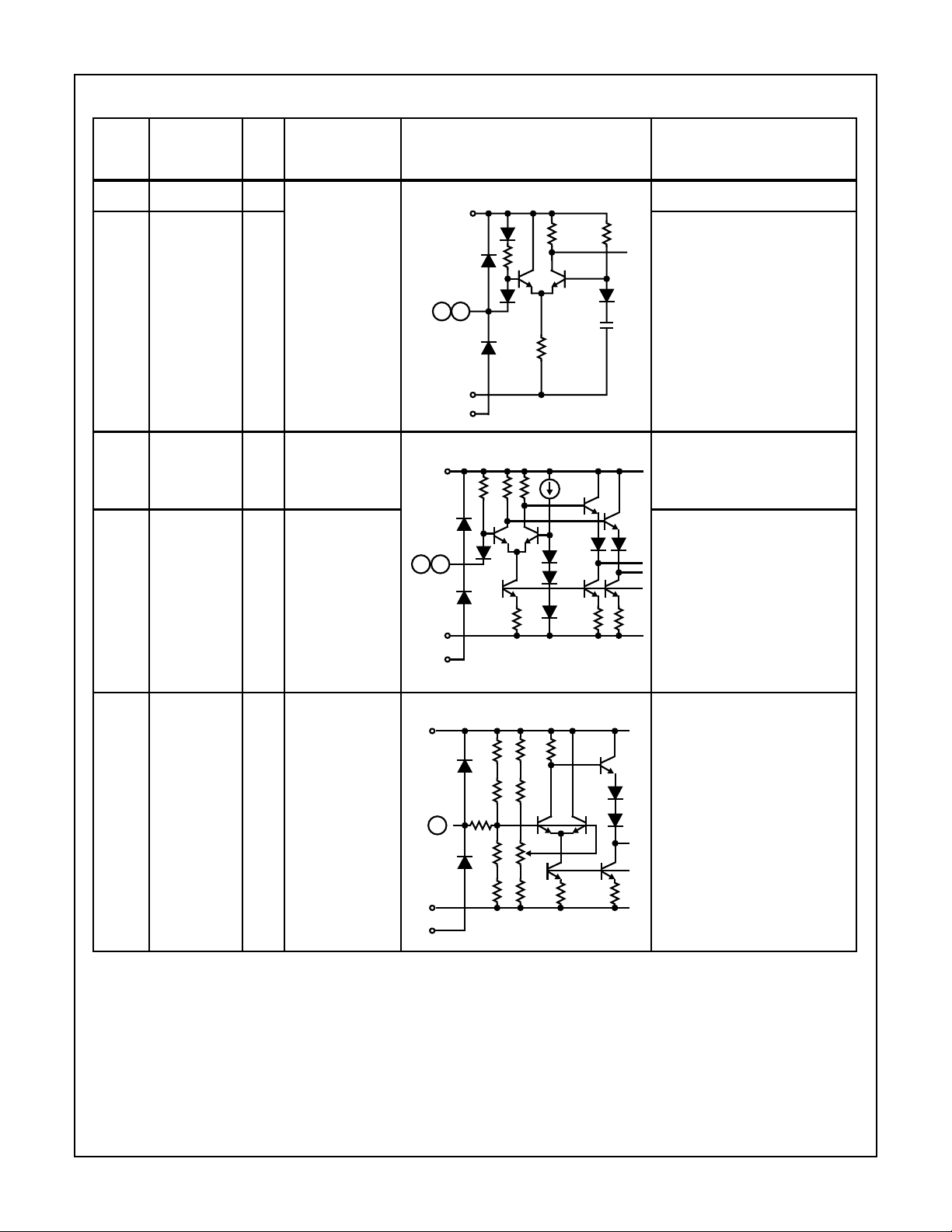

Pin Descriptions (Continued)

PIN

NO. SYMBOL I/O

HI3086

TYPICAL

VOLTAGE

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

27 CLK/T I TTL Clock Input.

10 RESETN/T I Reset Input. When left open, this

D

VCC1

R/2

input goes to high level. When the

input is set to low level, the built-in

CLK frequency divider circuit can

be reset.

2710

DGND1

DV

EE3

42 INV I TTL Data Output Polarity Inversion Input.

D

VCC1

1.5V

R

When left open, this input goes to

high level. (See Table 1; I/O

Correspondence Table).

44 PS I TTL Power Saving Input. When the input

is set to low level, the power saving

44

42

mode is set. In this time the all TTL

ouputs go into the high impedance

state. Normally, set to high level or

left open.

DGND1

D

VEE3

41 SELECT V

or GND Data Output Mode Selection. (See

CC

D

VCC1

41

DGND1

D

VEE3

Table 2, Operating Mode Table).

4-1409

Pin Descriptions (Continued)

PIN

NO. SYMBOL I/O

HI3086

TYPICAL

VOLTAGE

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

22 V

21 V

16 V

15 V

RTS

RT

RB

RBS

O +4.0V (Typ) Reference Voltage Sense. Bypass

to AGND with a 0.1µF chip

22

IV

IV

RTS

RBS

+ R1 x I

-R2 x I

REF

REF

O +2.0V (Typ) Reference Voltage Sense. Bypass

R1

21

R

COMPARATOR 1

R

R

COMPARATOR 2

R

capacitor.

Top Reference Voltage. Bypass to

AGND with a 1µF tantal capacitor

and 0.1µF chip capacitor.

Bottom Reference Voltage. Bypass

to AGND with a 1µF tantal capacitor

and a 0.1µF chip capacitor.

to AGND with a 0.1µF chip

capacitor.

R

COMPARATOR 62

R

R

COMPARATOR 63

R

R2

16

15

19 V

IN

30 to 35 P1D0 to P1D5 O TTL Port 1 Side Data Output.

2 to 7 P2D0 to P2D5 O Port 2 Side Data Output.

43 CLKOUT O Clock Output. (See Table 2.

IVRT to V

RB

AV

CC

19

DV

EE3

DV

CC1

DGND1

COMPARATOR

AV

CC

AGND

100K

DV

CC2

2

TO

304335

TO

DGND2

DV

EE3

Analog Input.

V

REF

7

Operating Mode Table.)

4-1410

HI3086

Absolute Maximum Ratings (T

Supply Voltage . . . . . . . . . . . (AVCC, DV

(DGND3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7.0V

(DV

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -7.0V to 0.5V

EE3

(DGND3 - DV

Analog Input Voltage (VIN) . . . . . . . . . . . . . . . . .VRT - 2.7V to AV

Reference Input Voltage (VRT). . . . . . . . . . . . . . . . . . .2.7V to AV

(VRB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . VIN - 2.7V to AV

). . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7.0V

EE3

=25oC) Thermal Information

A

, DV

CC1

) -0.5V to 7.0V

CC2

Thermal Resistance (Typical, Note 1) θJA (oC/W)

MQFP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

CC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

CC

CC

(MQFP - Lead Tips Only)

(|VRT - VRB|). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2.5V

Digital Input Voltage

ECL (***/E (Note 2)) . . . . . . . . . . . . . . . . . . . . . . . .DV

EE3

to 0.5V

PECL (***/E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to DGND3

TTL (***/T, INV PS) . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to DV

Other (SELECT) . . . . . . . . . . . . . . . . . . . . . . . . . . -0.5V to DV

CC1

CC1

VID (|***/E - ***N/E| (Note 3)) . . . . . . . . . . . . . . . . . . . . . . . . .2.7V

Recommended Operating Conditions

WITH A SINGLE POWER SUPPLY MIN TYP MAX

Supply Voltage

DV

CC1

, DV

, AVCC . . . . . . . . . +4.75 +5.0 +5.25V

CC2

DGND1, DGND2, AGND . . . . . . . -0.05 0 +0.05V

DGND3 . . . . . . . . . . . . . . . . . . . . . +4.75 +5.0 +5.25V

DV

. . . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

EE3

Analog Input Voltage (VIN) . . . . . . . . V

RB

-V

Reference Input Voltage

VRT. . . . . . . . . . . . . . . . . . . . . . . . +2.9 - +4.1V

VRB. . . . . . . . . . . . . . . . . . . . . . . . 1.4 - +2.6V

|VRT - VRB|. . . . . . . . . . . . . . . . . . 1.5 - 2.1V

Digital Input Voltage

ECL (***/E) VIH. . . . . . . . . . . . . . . . DGND3 - 1.05 DGND3 - 0.5V

PECL (***/E) VIL DGND3 . . . . . . . DGND3 - 3.2 DGND3 - 1.4V

TTL (***/T, INV, PS) VIH . . . . . . . . 2.0V - -

TTL (***/T, INV) VIL. . . . . . . . . . . . - - 0.8V

Other (SELECT) VIH. . . . . . . . . . . - DV

CC1

Other (SELECT) VIL. . . . . . . . . . . - DGND1 -

VID (Note 3) (|***/E- ***N/E|). . . . . 0.4 0.8 -

Max Conversion Rate (fC, Straight Mode) . . . 100 - -

Units = MSPS

Max Conversion Rate (fC, DMUX Mode). . . . 140 - -

Units = MSPS

Ambient Temperature (TA) . . . . . . . . . . . . . . . . . . . . . -20oC to 75oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

2. ***/E and ***T indicate CLK/E and CLK/T, etc. for the pin name.

3. VID: Input Voltage Differential.

WITH DUAL POWER SUPPLIES MIN TYP MAX

Supply Voltage

DV

, DV

CC1

, AVCC . . . . . . . . . +4.75 +5.0 +5.25V

CC2

DGND1, DGND2, AGND. . . . . . . . -0.05 0 +0.05V

DGND3 . . . . . . . . . . . . . . . . . . . . . -0.05 0 +0.05V

DV

. . . . . . . . . . . . . . . . . . . . . . -5.5 -5.0 -4.75V

EE3

Analog Input Voltage (VIN) . . . . . . . . V

RT

RB

Reference Input Voltage

VRT . . . . . . . . . . . . . . . . . . . . . . . . +2.9 - +4.1V

VRB . . . . . . . . . . . . . . . . . . . . . . . . 1.4 - +2.6V

|VRT - VRB| . . . . . . . . . . . . . . . . . . 1.5 - 2.1V

Digital Input Voltage

ECL (***/E) VIH DGND3 . . . . . . . .DGND3 - 1.05 DGND3 - 0.5V

ECL (***/E) VIL DGND3. . . . . . . . . DGND3 - 3.2 DGND3 -1.4V

TTL (***/T, INV) VIH. . . . . . . . . . . . . . . . . 2.0V - -

TTL (***/T, INV) VIL . . . . . . . . . . . . . . . . . - - 0.8V

-

Other (SELECT) VIH . . . . . . . . . . . . . . . . - DV

Other (SELECT) VIL . . . . . . . . . . . . . . . . - DGND1 -

VID (Note 3) (|***/E- ***N/E|) . . . . . . . . . . 0.4 0.8 -

Max Conversion Rate (fC, Straight Mode). . . 100 - -

Units = MSPS

Max Conversion Rate (fC, DMUX Mode). . . . 140 - -

Units = MSPS

Ambient Temperature (TA). . . . . . . . . . . . . . . . . . . . . .-20oC to 75oC

-V

CC1

RT

-

Electrical Specifications DV

TA = 25oC, PECL Input

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

Resolution

DC CHARACTERISTICS

Integral Linearity Error

Differential Linearity Error

, AVCC, DGND3 = +5V, DGND1, 2, AGND, DV

CC1,2

IL

DL

VIN = 2V

E

E

= 5 MSPS - - ±0.2 LSB

P-P,fC

4-1411

= 0V, VRT = 4V, VRB = 2V,

EE3

- 6 - Bits

--±0.2 LSB

Loading...

Loading...