August 1997

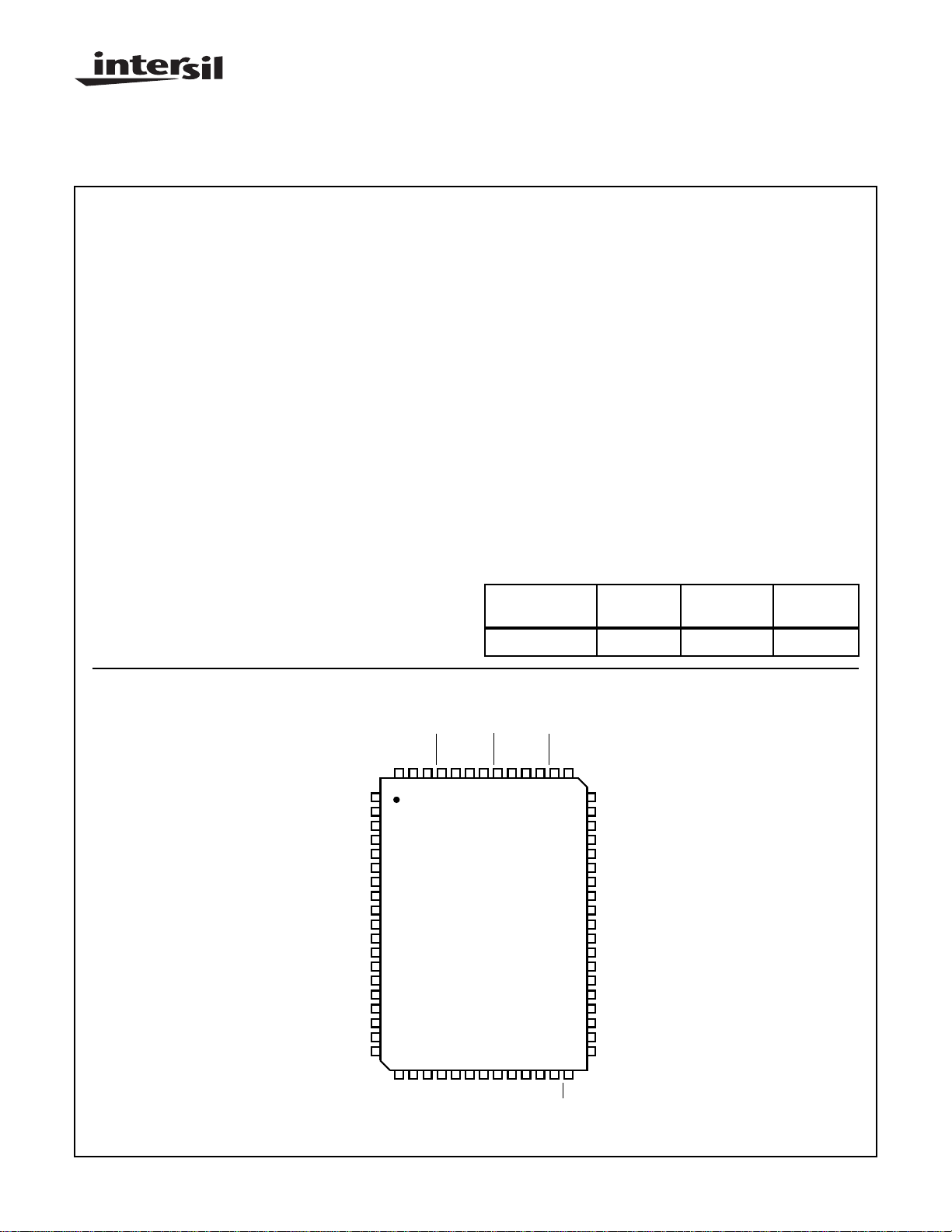

HI3050

Triple 10-Bit, 50 MSPS,

High Speed, 3-Channel D/A Converter

Features

• Resolution . . . . . . . . . . . . . . . . . . . . . . . . . .Triple 10-Bit

• Throughput Rate . . . . . . . . . . . . . . . . . . . . . . . . . 50MHz

• 3-Channel, RGB, I/O

• RS-343A/RS-170 Compatible Outputs

• Low Power Consumption (Typ) . . . . . . . . . . . . .500mW

• Differential Linearity Error . . . . . . . . . . . . . . . ±0.5 LSB

• Low Glitch Energy

• CMOS Compatible Inputs

• Direct Replacement for Sony CXD2308

Applications

• NTSC, PAL, SECAM Displays

• High Definition Television (HDTV)

• Presentation and Broadcast Video

• Image Processing

• Graphics Displays

Description

The HI3050 is a triple, 10-bit D/A converter, fabricated in a

silicon gate CMOS process, ideally suited for RGB video

applications.

The converter incorporates three 10-bit input data registers

with a common blanking capability, forcing all outputs to 0mA.

The HI3050 features low glitch, high impedance current outputs and single 5V supply operation. Low current inputs

accept standard TTL/CMOS levels. The architecture is a

current cell arrangement providing low differential andintegral

linearity errors.

The HI3050 requires a 2V external reference and a set

resistor to control the output current. The HI3050 also features

a chip enable/disable pin for reducing power consumption

(<5mW) when the part is not in use.

The HI3050 can generate RS-343A and RS-170 compatible

video signals into doubly terminated and singly terminated

75Ω loads.

Ordering Information

TEMP.

PART NUMBER

HI3050JCQ -20 to 75 64 Ld MQFP Q64.14x20-S

RANGE (oC) PACKAGE PKG. NO.

Pinout

R0 (LSB)

R1

R2

R3

R4

R5

R6

R7

R8

R9 (MSB)

G0 (LSB)

G1

G2

G3

G4

G5

G6

G7

G8

HI3050 (MQFP)

TOP VIEW

DVDDAVDDAVDDBOUT

6463 62 616059 58 575655 54 5352

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

2021 22 232425 26 272829 30 3132

G9 (MSB)

BOUT

AVDDAVDDGOUT

B1B2B3B4B5B6B8

B0 (LSB)

GOUT

AVDDAVDDROUT

B7

B9 (MSB)

ROUT

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

CE

BLANK

AGND

COMP B

V

OUT B

REF

COMP G

V

OUT G

REF

COMP R

V

OUT R

REF

V

REFB

V

REFG

V

REFR

FS ADJUST B

FS ADJUST G

FS ADJUST R

AGND

V

BIAS

DGND

BCLK

GCLK

RCLK

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

10-1

File Number 3936.2

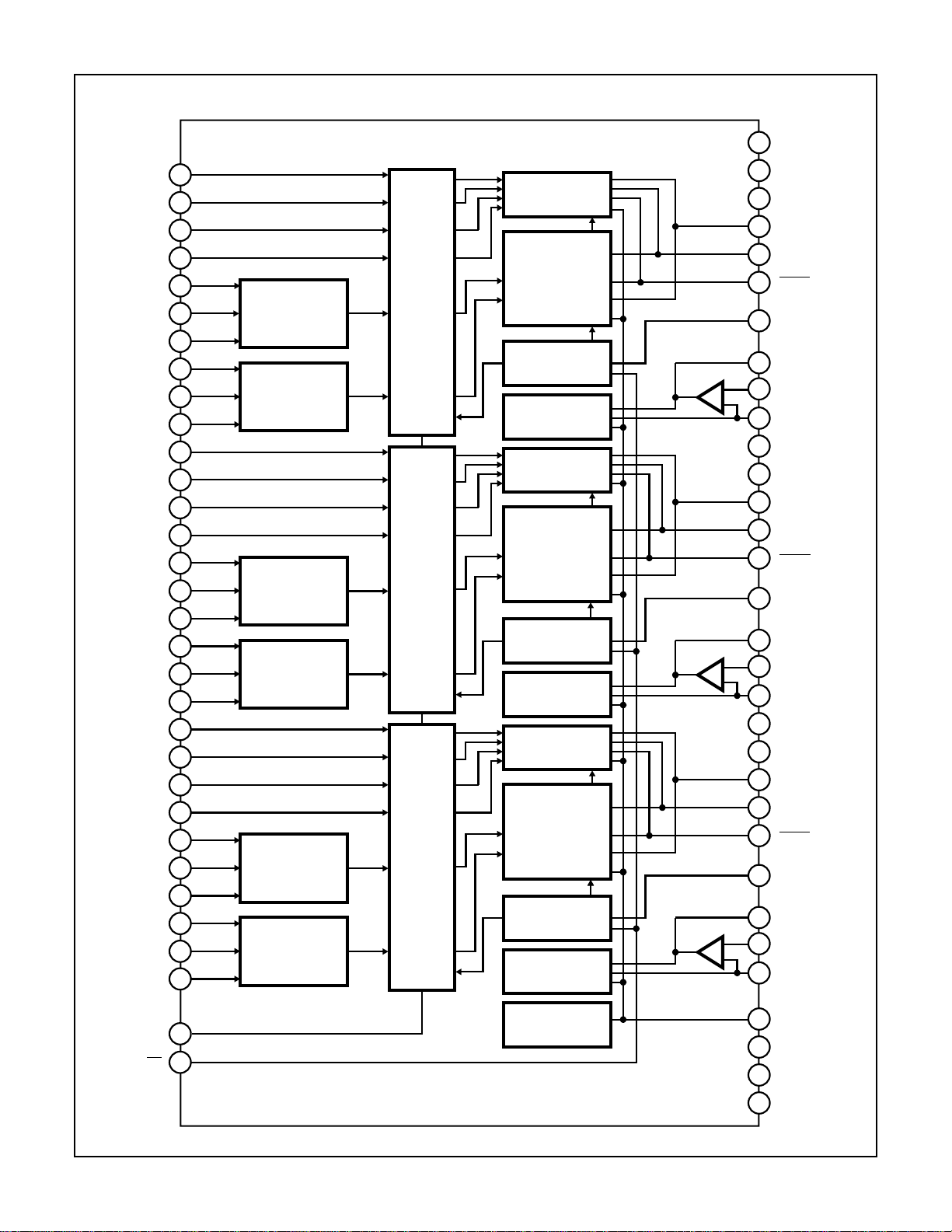

Functional Block Diagram

R0 (LSB)

G0 (LSB)

B0 (LSB)

R1

R2

R3

R4

R5

R6

R7

R8

R9

G1

G2

G3

G4

G5

G6

G7

G8

G9

B1

B2

B3

B4

B5

B6

B7

B8

B9

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

DECODER

DECODER

DECODER

DECODER

DECODER

DECODER

LATCHES

LATCHES

LATCHES

HI3050

4 LSBs

CURRENT

CELLS

6 MSBs

CURRENT

CELLS

CLOCK

GENERATOR

CURRENT CELLS

(FOR FULL SCALE)

4 LSBs

CURRENT

CELLS

6 MSBs

CURRENT

CELLS

CLOCK

GENERATOR

CURRENT CELLS

(FOR FULL SCALE)

4 LSBs

CURRENT

CELLS

6 MSBs

CURRENT

CELLS

CLOCK

GENERATOR

CURRENT CELLS

(FOR FULL SCALE)

DV

64

DD

AV

62

DD

AV

63

DD

COMP R

46

ROUT

52

53

ROUT

RCLK

33

45

42

-

+

39

58

59

48

56

57

34

47

43

-

+

40

54

55

50

60

61

35

49

44

-

+

41

OUT R

V

REF

V

REFR

FS ADJUST R

AV

DD

AV

DD

COMP G

GOUT

GOUT

GCLK

OUT G

V

REF

V

REFG

FS ADJUST G

AV

DD

AV

DD

COMP B

BOUT

BOUT

BCLK

OUT B

V

REF

V

REFB

FS ADJUST B

BLANK

CE

BIAS

31

32

VOLTAGE

GENERATOR

V

37

BIAS

AGND

38

AGND

51

DGND

36

10-2

HI3050

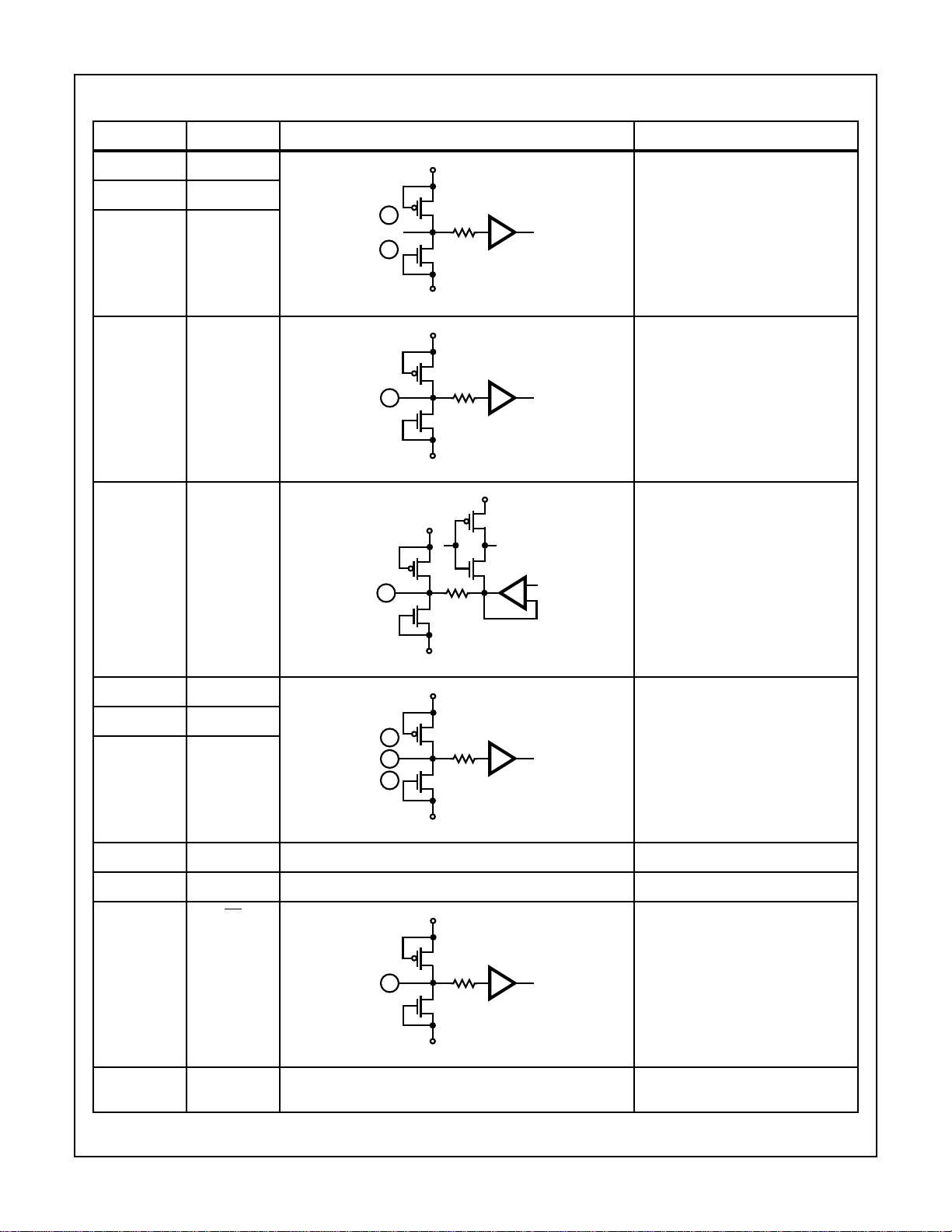

Pin Descriptions and Equivalent Circuits

PIN NO. SYMBOL EQUIVALENT CIRCUIT DESCRIPTION

1 - 10 R0 - R9 Digital Inputs.

DV

DD

11 - 20 G0 - G9

21 - 30 B0 - B9

31 BLANK Output Blanking Input.

TO

30

1

DGND

DV

DD

High: Outputs Set to 0mA.

Low: Normal Output Operation.

31

DGND

37 V

BIAS

DV

DD

DV

DD

37

+

-

Internal Bias Decoupling.

Connect a 0.1µF decoupling capacitor

to DGND.

DGND

33 RCLK Clock Inputs.

DV

DD

All input pins are TTL/CMOS compatible.

34 GCLK

35 BCLK

33

34

35

DGND

36 DGND Digital Ground.

38, 51 AGND Analog Ground.

32 CE Chip Enable pin.

DV

DD

High: Part Disabled

Low: Part Enabled

32

DGND

54, 55, 58, 59,

AV

DD

Analog Power Supply.

62, 63

10-3

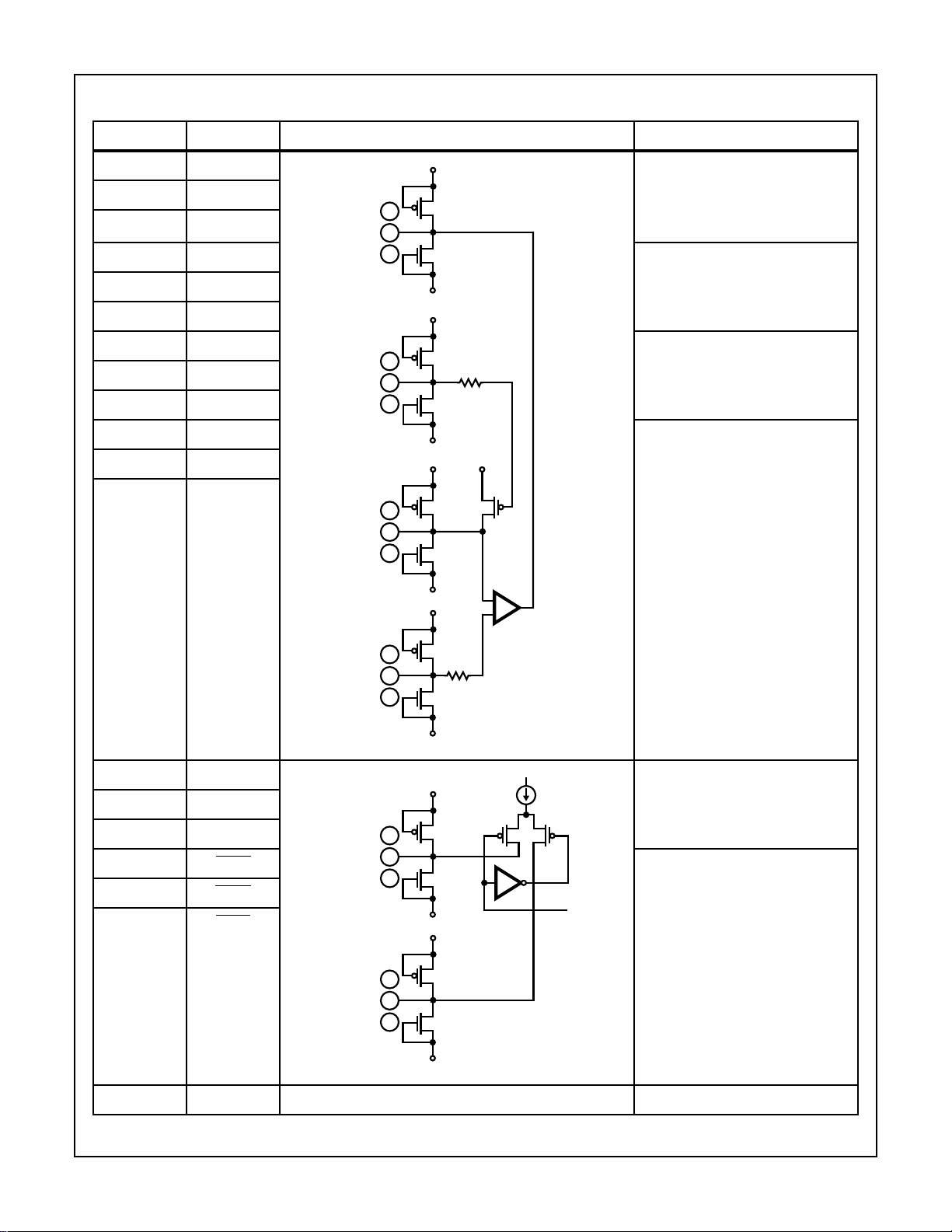

HI3050

Pin Descriptions and Equivalent Circuits

(Continued)

PIN NO. SYMBOL EQUIVALENT CIRCUIT DESCRIPTION

45 V

47 V

49 V

46 COMP R Reference Decoupling.

OUT R Reference Output.

REF

REF

REF

OUT G

OUT B

45

47

49

AV

DD

Typically connected to the Reference

Decoupling inputs (COMP R, COMP G,

COMP B). See Figures 11 and 12 for

various configurations.

Connect a decoupling capacitor (0.1µF)

48 COMP G

50 COMP B

AGND

AV

DD

to reduce noise on reference to AVDD.

39 FS ADJUST R Full Scale Adjust.

40 FS ADJUST G

41 FS ADJUST B

42 V

43 V

44 V

REFR

REFG

REFB

46

48

50

AGND

AV

DD

39

40

41

Typically connect a 1.2kΩ resistor, R

to AGND. R

is used to determine full

SET

scale output current.

Voltage Reference Input.

Typically set to 2V and determines full

scale output current.

I

Full Scale()

OUT

V

REF

---------------

R

SET

,

SET

16×=

AGND

AV

42

43

44

AGND

DD

+

-

52 ROUT Current Outputs.

AV

56 GOUT

60 BOUT

53 ROUT Inverted Current Outputs.

52

56

60

DD

57 GOUT

61 BOUT

53

57

61

AGND

AV

DD

64 DV

DD

AGND

Digital Power Supply.

10-4

Loading...

Loading...