Intersil Corporation HI-307, HI-303, HI-301 Datasheet

TM

HI-301 thru HI-307

Data Sheet March 2000

CMOS Analog Switches

The HI-301 thru HI-307 series of switches are monolithic

devices fabricated using CMOS technology and the Intersil

dielectric isolation process. These switches feature break

before-make switching, low and nearly constant ON

resistance over the full analog signal range, and low power

dissipation, (a few mW for the Hl-301 and HI-303, a few

hundred mW for the HI-307).

The HI-301 and HI-303 are TTL compatible and havealogic

“0” condition with an input less than 0.8V and a logic “1”

condition with an input greater than 4V. The HI-307 switches

are CMOS compatible and have a low state with an input

less than 3.5V and a high state with an input greater than

11V. (See pinouts for switchconditionswithalogic“1” input.)

Ordering Information

PART

NUMBER

HI9P0301-5 0 to 75 14 Ld SOIC M14.15

HI1-0303-2 -55 to 125 14 Ld CERDIP F14.3

HI1-0303-5 0 to 75 14 Ld CERDIP F14.3

HI9P0303-5 0 to 75 14 Ld SOIC M14.15

HI9P0303-9 -40 to 85 14 Ld SOIC M14.15

HI1-0307-5 0 to 75 14 Ld CERDIP F14.3

TEMP.

RANGE (oC) PACKAGE PKG. NO.

File Number 3125.4

Features

• Analog Signal Range (±15V Supplies) . . . . . . . . . . ±15V

o

• Low Leakage at 25

• Low Leakage at 125

• Low On Resistance at 25

C . . . . . . . . . . . . . . . . . . . . . . . 40pA

o

C . . . . . . . . . . . . . . . . . . . . . . . 1nA

o

C . . . . . . . . . . . . . . . . . . . 35Ω

• Break-Before-Make Delay . . . . . . . . . . . . . . . . . . . . 60ns

• Charge Injection . . . . . . . . . . . . . . . . . . . . . . . . . . . 30pC

• TTL, CMOS Compatible

• Symmetrical Switch Elements

• Low Operating Power (Typ for Hl-301 and HI-303) . . 1.0mW

Applications

• Sample and Hold (i.e., Low Leakage Switching)

• Op Amp Gain Switching (i.e., Low On Resistance)

• Portable, Battery Operated Circuits

• Low Level Switching Circuits

• Dual or Single Supply Systems

Functional Diagram

S

IN

N

P

Pinouts Switch States Shown For A Logic “1” Input

SPST HI-301

(SOIC)

TOP VIEW

1

NC

2

D

1

3

NC

4

S

1

5

NC

6

IN

7

GND

LOGIC SW1 SW2

0 OFF ON

1 ON OFF

14

V+

13

D

2

12

NC

11

S

2

10

NC

9

NC

8

V-

DUAL SPDT HI-303 (CERDIP, SOIC)

HI-307 (CERDIP)

TOP VIEW

NC

IN

GND

1

2

S

3

3

D

3

4

D

1

5

S

1

6

1

7

14

V+

13

S

4

12

D

4

11

D

2

10

S

2

9

IN

2

8

V-

LOGIC SW1, SW2 SW3, SW4

0 OFF ON

1 ON OFF

D

1

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

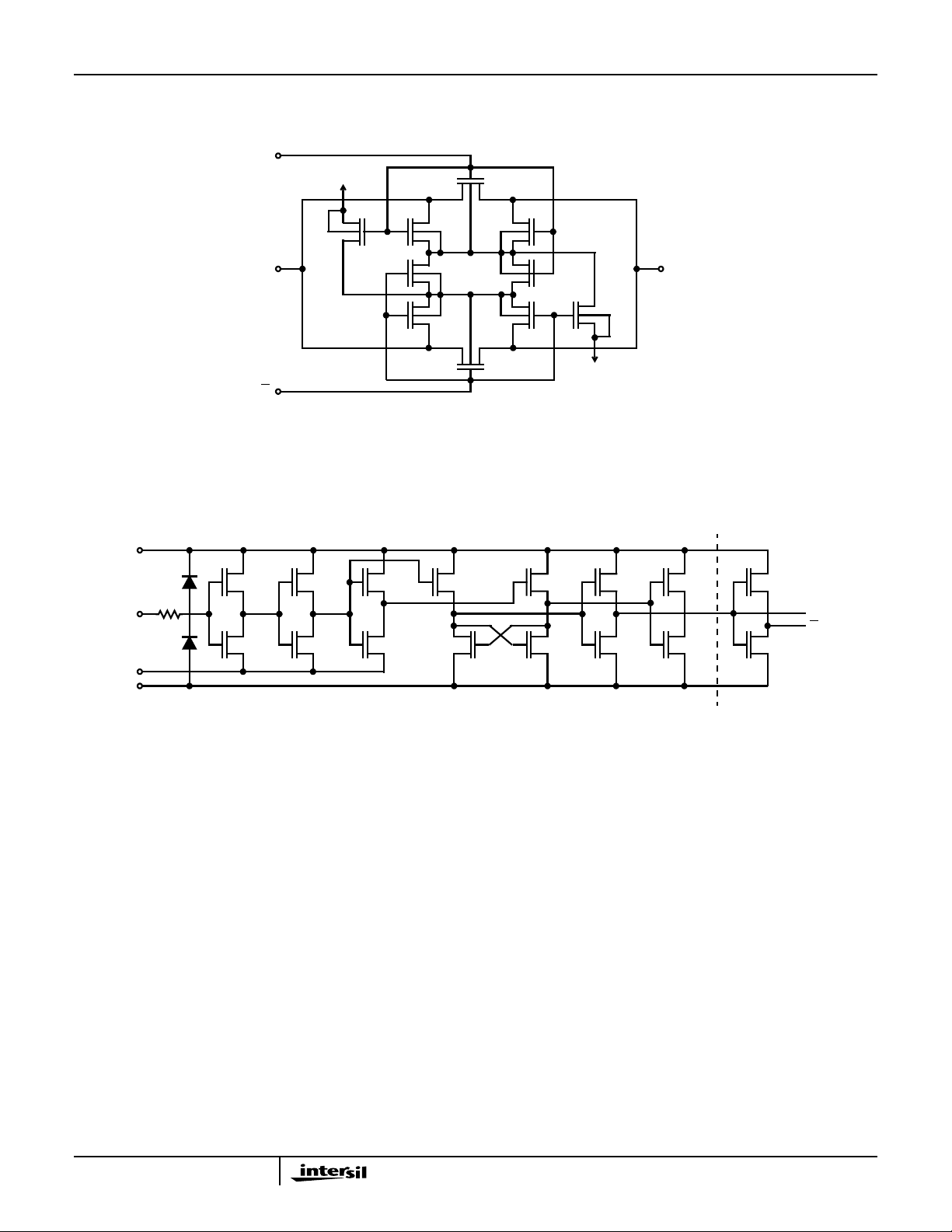

Schematic Diagrams

HI-301 thru HI-307

SWITCH CELL

A

V+

MN2BINMN3B

MP5B

MP4B

MP3B MP2B

MN1B

OUT

MN4B

MN6B

V+

LOGIC

GND

MP1B

A

V-

DIGITAL INPUT BUFFER AND LEVEL SHIFTER

D2A

200Ω

IN

D1A

V-

MP1A

MN1A

MP2A

MN2A

MP3A

MN3A

MN4A

MP4A

MP5A

MN5A

MP6A

MN6A

MP7A

MN7A

SWITCH CELL DRIVER

(ONE PER SWITCH CELL)

MP8A

A

A

MN8A

2

HI-301 thru HI-307

Absolute Maximum Ratings Thermal Information

Voltage Between Supplies (V+ to V-). . . . . . . . . . . . . . . .44V (±22V)

Digital Input Voltage. . . . . . . . . . . . . . . . . . . . . . (V+) +4V to (V-) -4V

Analog Input Voltage . . . . . . . . . . . . . . . . . . (V+) +1.5V to (V-) -1.5V

Typical Derating Factor . . . . . . . . . 1.5mA/MHz Increase in ICCOP

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Class 1

Operating Conditions

Temperature Range

HI-3XX-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

HI-3XX-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 75oC

HI-3XX-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

CERDIP Package. . . . . . . . . . . . . . . . . 95 40

SOIC Package . . . . . . . . . . . . . . . . . . . 120 N/A

Maximum Junction Temperature

Ceramic Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175oC

Plastic Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

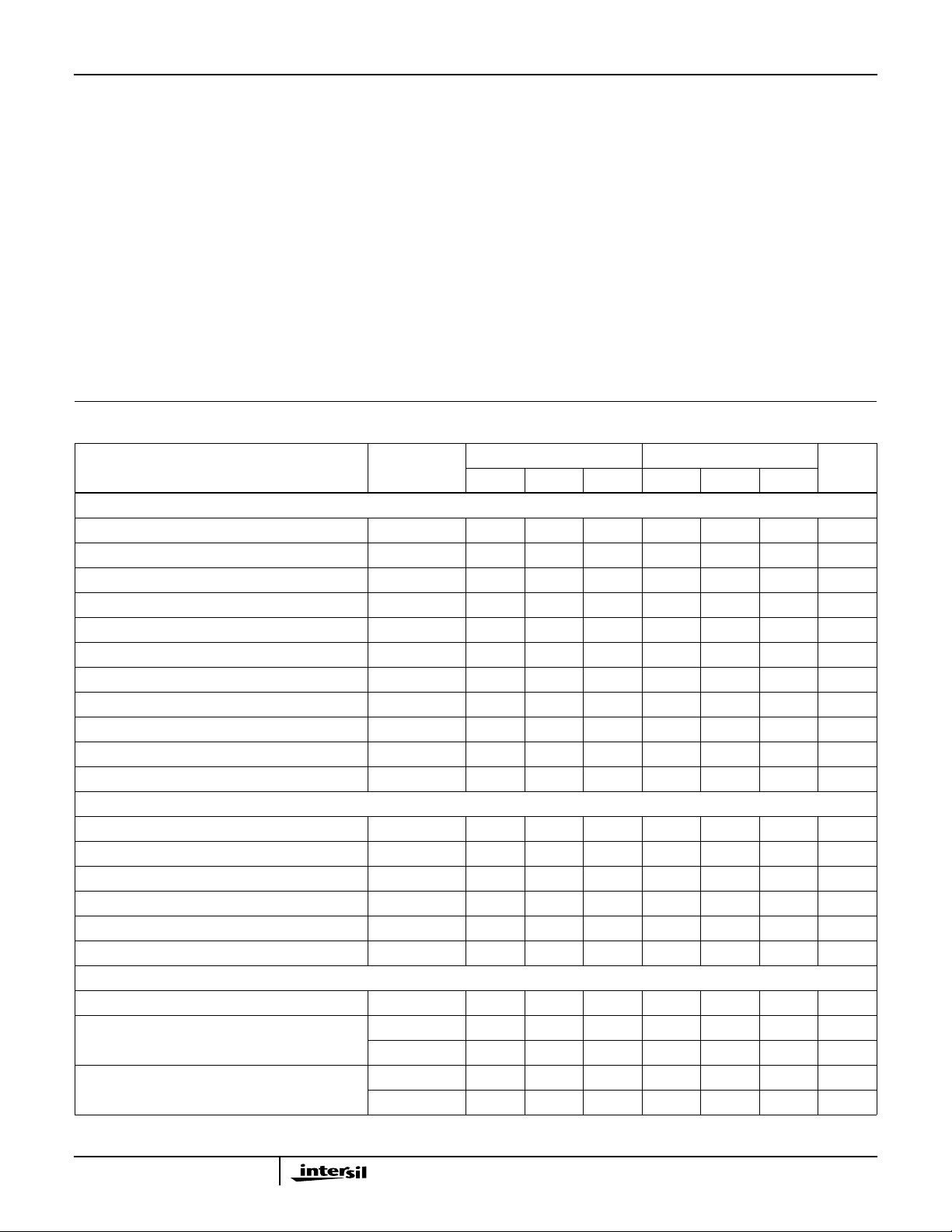

Electrical Specifications Supplies = +15V, -15V; V

HI-307: V

PARAMETER

- for Logic “1” = 11V, for Logic “0” = 3.5V, Unless Otherwise Specified

IN

= Logic Input. HI-301 and HI-303: VIN - for Logic “1” = 4V, for Logic “0” = 0.8V.

IN

TEMP

-2 -5, -9

(oC)

UNITSMIN TYP MAX MIN TYP MAX

DYNAMIC CHARACTERISTICS

Switch ON Time, tON (Note 13) 25 - 210 300 - 210 300 ns

Switch OFF Time, t

(Note 13) 25 - 160 250 - 160 250 ns

OFF

Switch ON Time, tON (Note 14) 25 - 160 250 - 160 250 ns

Switch OFF Time, t

Break-Before-Make Delay, t

(Note 14) 25 - 100 150 - 100 150 ns

OFF

OPEN

25 -60- -60-ns

Charge Injection Voltage, ∆V (Note 7) 25 - 3 - - 3 - mV

OFF Isolation (Note 6) 25 - 60 - - 60 - dB

Input Switch Capacitance, C

Output Switch Capacitance, C

Output Switch Capacitance, C

Digital Input Capacitance, C

IN

S(OFF)

D(OFF)

D(ON)

25 -16- -16-pF

25 -14- -14-pF

25 -35- -35-pF

25 - 5 - - 5 - pF

DIGITAL INPUT CHARACTERISTICS

Input Low Level, V

Input High Level, V

Input Low Level, V

Input High Level, V

Input Leakage Current (Low), I

Input Leakage Current (High), I

(Note 13) Full - - 0.8 - - 0.8 V

INL

(Note 13) Full 4 - - 4 - - V

INH

(Note 14) Full - - 3.5 - - 3.5 V

INL

(Note 14) Full 11 - - 11 - - V

INH

(Note 5) Full - - 1 - - 1 µA

INL

(Note 5) Full - - 1 - - 1 µA

INH

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range Full -15 - +15 -15 - +15 V

ON Resistance, rON (Note 2) 25 - 35 50 - 35 50 Ω

Full - 40 75 - 40 75 Ω

OFF Input Leakage Current, I

(Note 3) 25 - 0.04 1 - 0.04 5 nA

S(OFF)

Full - 1 100 - 0.2 100 nA

3

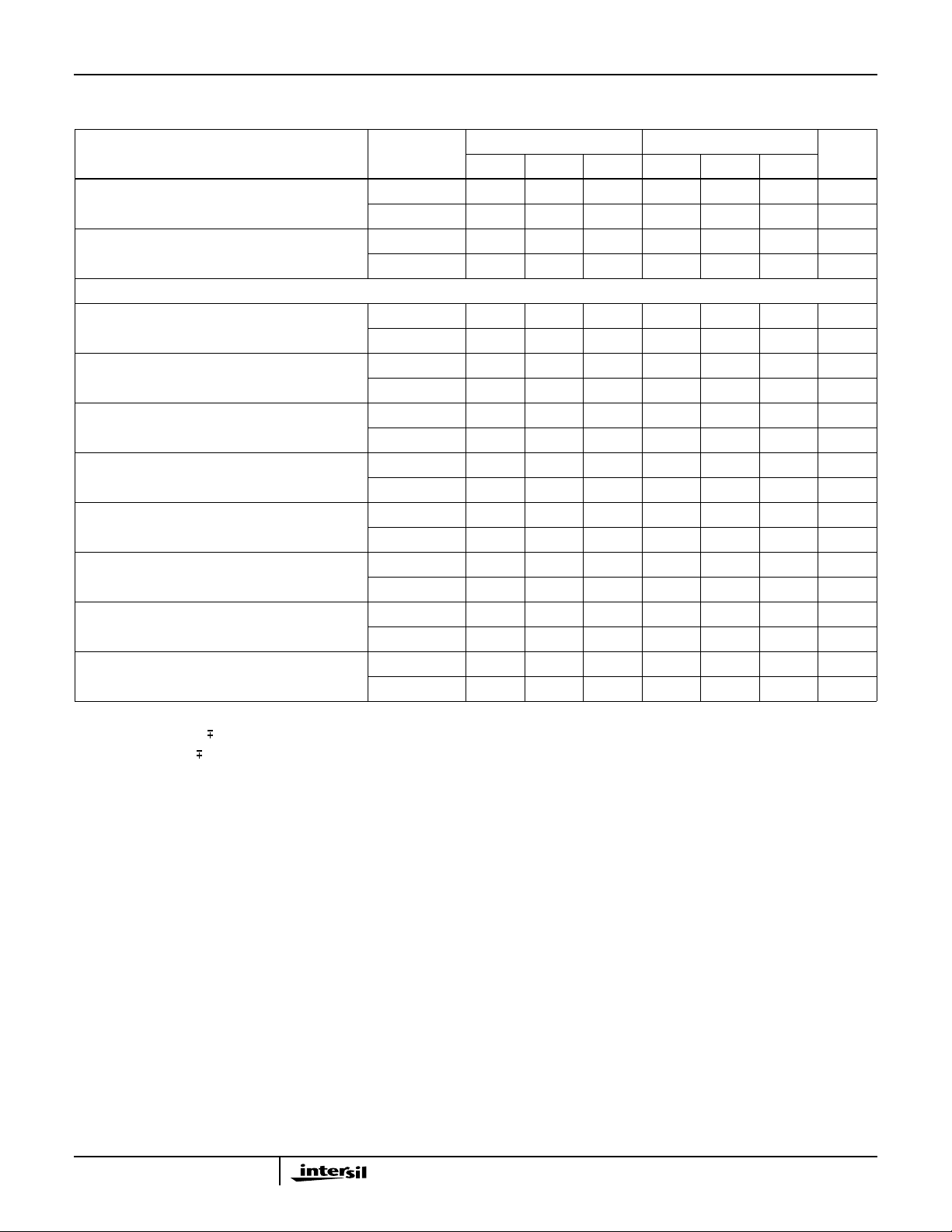

HI-301 thru HI-307

Electrical Specifications Supplies = +15V, -15V; V

HI-307: VIN - for Logic “1” = 11V, for Logic “0” = 3.5V, Unless Otherwise Specified (Continued)

PARAMETER

OFF Output Leakage Current, I

ON Leakage Current, I

POWER SUPPLY CHARACTERISTICS

Current, I+ (Notes 8, 13) 25 - 0.09 0.5 - 0.09 0.5 mA

Current, I- (Notes 8, 13) 25 - 0.01 10 - 0.01 100 µA

Current, I+ (Notes 9, 13) 25 - 0.01 10 - 0.01 100 µA

Current, I- (Notes 9, 13) 25 - 0.01 10 - 0.01 100 µA

Current, I+ (Notes 10, 14) 25 - 0.01 10 - 0.01 100 µA

Current, I- (Notes 10, 14) 25 - 0.01 10 - 0.01 100 µA

Current, I+ (Notes 11, 14) 25 - 0.01 10 - 0.01 100 µA

Current, I- (Notes 11, 14) 25 - 0.01 10 - 0.01 100 µA

NOTES:

2. VS = ±10V, I

3. VS = ±14V, VD = 14V.

4. VS = VD = ±14V.

5. The digital inputs are diode protected MOS gates and typical leakages of 1nA or less can be expected.

6. VS = 1V

7. VS=0V, CL=10nF, Logic Drive =5Vpulse (HI-301 - 303), 15Vpulse (HI-307). Switches are symmetrical;S and D may beinterchanged. Charge

Injection = Q = CL x ∆V.

8. VIN = 4V (one input, all other inputs = 0V).

9. VIN = 0.8V (all inputs).

10. VIN = 15V (all inputs).

11. VIN = 0V (all inputs).

12. To drive from DTL/TTL circuits, pullup resistors to +5V supply are recommended.

13. HI-301 thru HI-303 only.

14. HI-307 only.

OUT

, f = 500kHz, CL = 15pF, RL = 1K.

RMS

(Note 4) 25 - 0.03 1 - 0.03 5 nA

D(ON)

= 10mA. On resistance derived from the voltage measured across the switch under these conditions.

(Note 3) 25 - 0.04 1 - 0.04 5 nA

D(OFF)

= Logic Input. HI-301 and HI-303: VIN - for Logic “1” = 4V, for Logic “0” = 0.8V.

IN

TEMP

(oC)

Full - 1 100 - 0.2 100 nA

Full - 0.5 100 - 0.2 100 nA

Full - - 1 - - 1 mA

Full - - 100 - - - µA

Full - - 100 - - - µA

Full - - 100 - - - µA

Full - - 100 - - - µA

Full - - 100 - - - µA

Full - - 100 - - - µA

Full - - 100 - - - µA

-2 -5, -9

UNITSMIN TYP MAX MIN TYP MAX

4

Loading...

Loading...