Intersil Corporation HI2315 Datasheet

August 1997

HI2315

10-Bit, 80 MSPS D/A Converter

(Ultra-Low Glitch Version)

Features

• Throughput Rate . . . . . . . . . . . . . . . . . . . . . . . . . 80MHz

• Low Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150mW

• Single Power Supply . . . . . . . . . . . . . . . . . . . . . . . . .+5V

• Differential Linearity Error . . . . . . . . . . . . . . . ±0.5 LSB

• TTL/CMOS Compatible Inputs

• Built in Bandgap Voltage Reference

• Power Down and Blanking Control Pins

• Low Glitch

• Pin Compatible with Sony CXD2306

• Direct Replacement for Sony CXD2315Q

Applications

• Wireless Communications

• Direct Digital Frequency Synthesis

• Signal Reconstruction

• Test Equipment

• High Resolution Imaging and Graphics Systems

Description

The HI2315 is a 10-bit, 80MHz, high speed, low power CMOS

D/A converter. The converter incor porates a 10-bit input data

register with current outputs. The HI2315 includes a power

down feature that reduces power consumption and a blanking

control. The on-chip bandgap reference can be used to set the

output current range of the D/A.

Ordering Information

PART

NUMBER

HI2315JCQ -20 to 75 32 Ld MQFP Q32.7x7-S

TEMP.

RANGE (oC) PACKAGE PKG. NO.

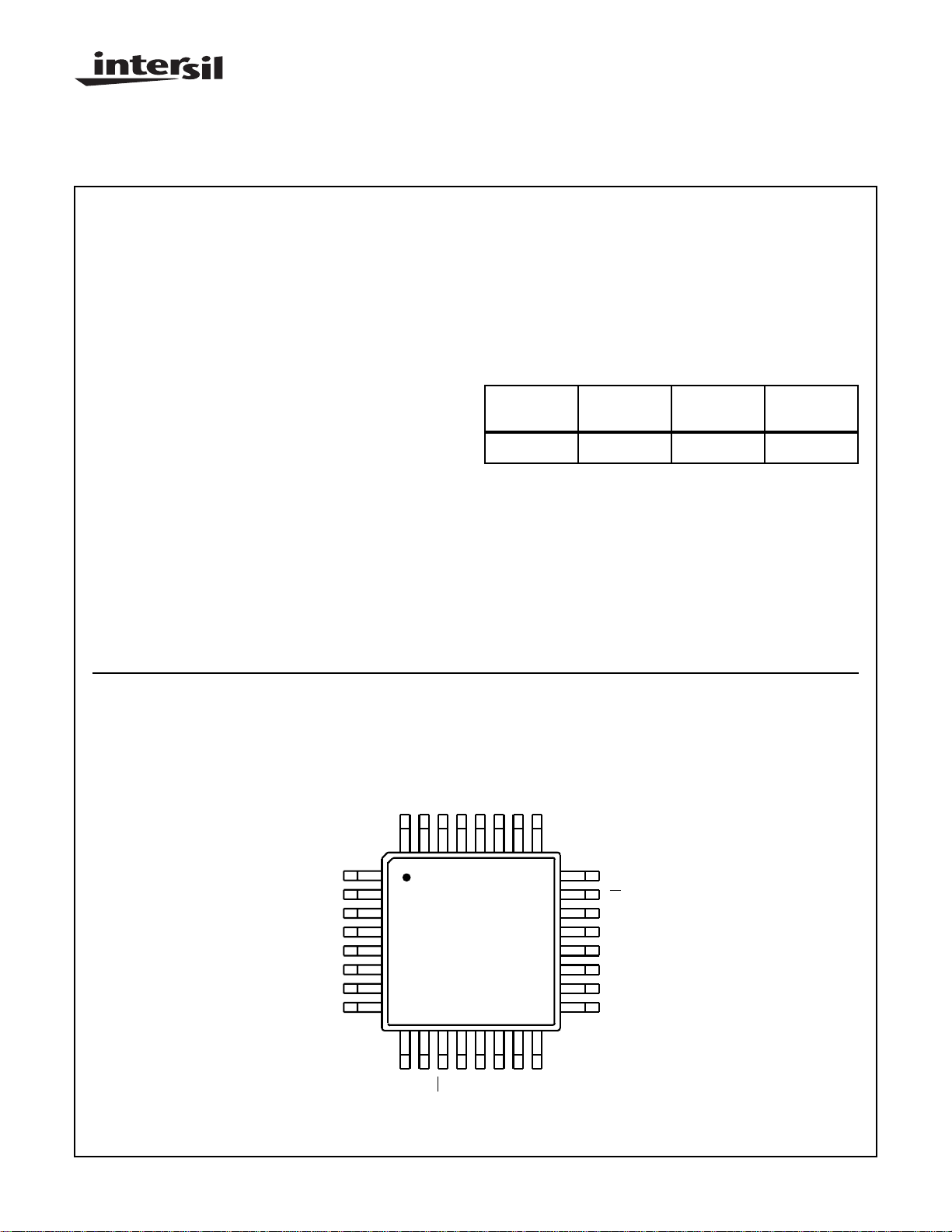

Pinout

D3

D4

D5

D6

D7

D8

D9 (MSB)

NC

HI2315

(MQFP)

TOP VIEW

SS

DD

NC

D0 (LSB)

D1

D2

32 31 30 29 28 27 26 25

1

2

3

4

5

6

7

8

9 10111213141516

CE

BLK

CLK

NC

DV

DV

DD

DV

VB

NC

DV

SS

AV

24

23

22

21

20

19

18

17

NC

SS

IO

IO

VG

AV

AV

V

S

I

REF

DD

DD

REF

REF

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

10-1

File Number 4119.1

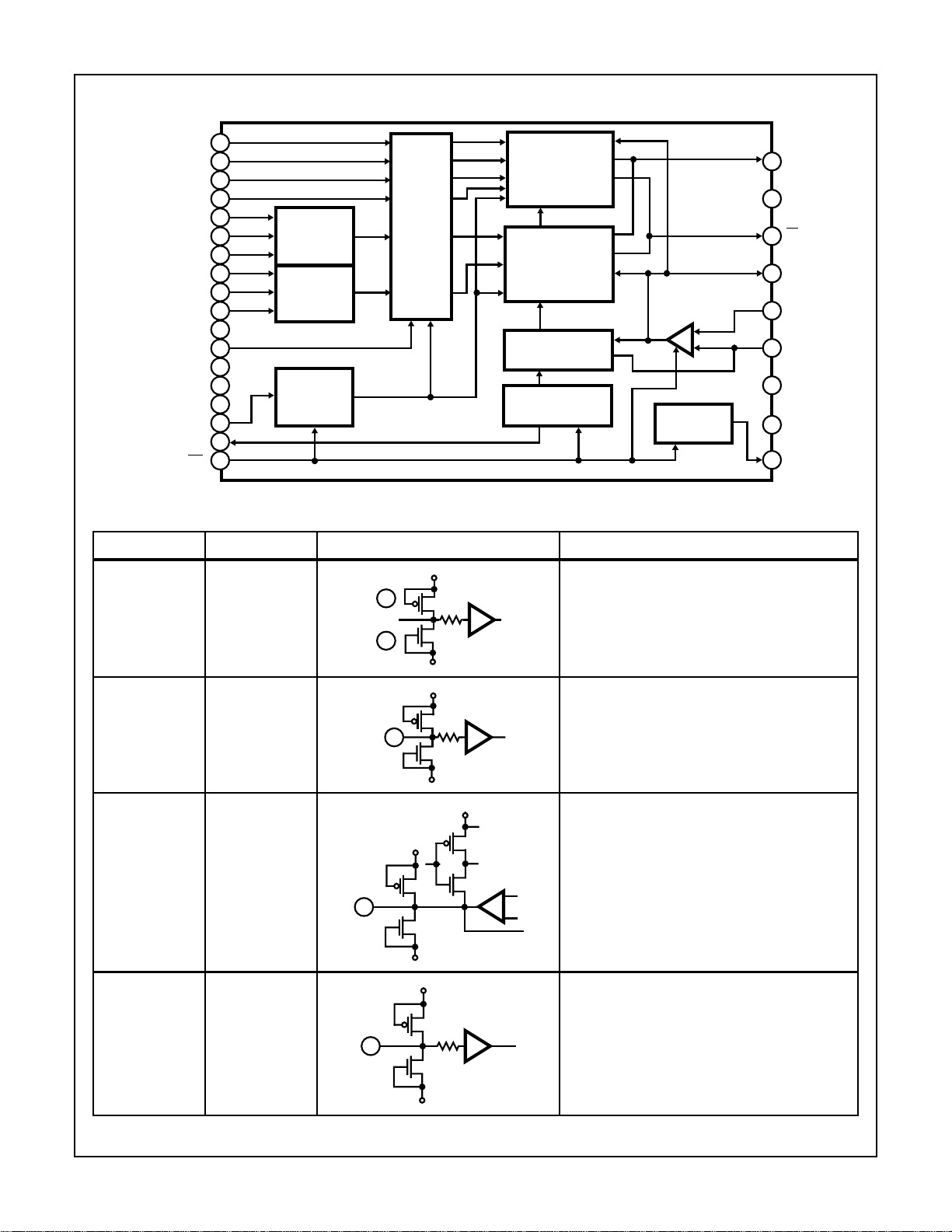

Functional Block Diagram

HI2315

DV

DV

DV

DV

D1

D2

D3

D4

D5

D6

D7

D8

D9

DD

BLK

DD

SS

SS

CLK

VB

CE

30

31

32

1

2

3

4

5

6

7

28

10

13

15

27

9

14

11

DECODER

DECODER

CLOCK

GENERATOR

LATCHES

4 LSBs

CURRENT

CELLS

6 MSBs

CURRENT

CELLS

CURRENT CELLS

(FOR FULL SCALE)

BIAS VOLTAGE

GENERATOR

BAND GAP

REFERENCE

(LSB) D0

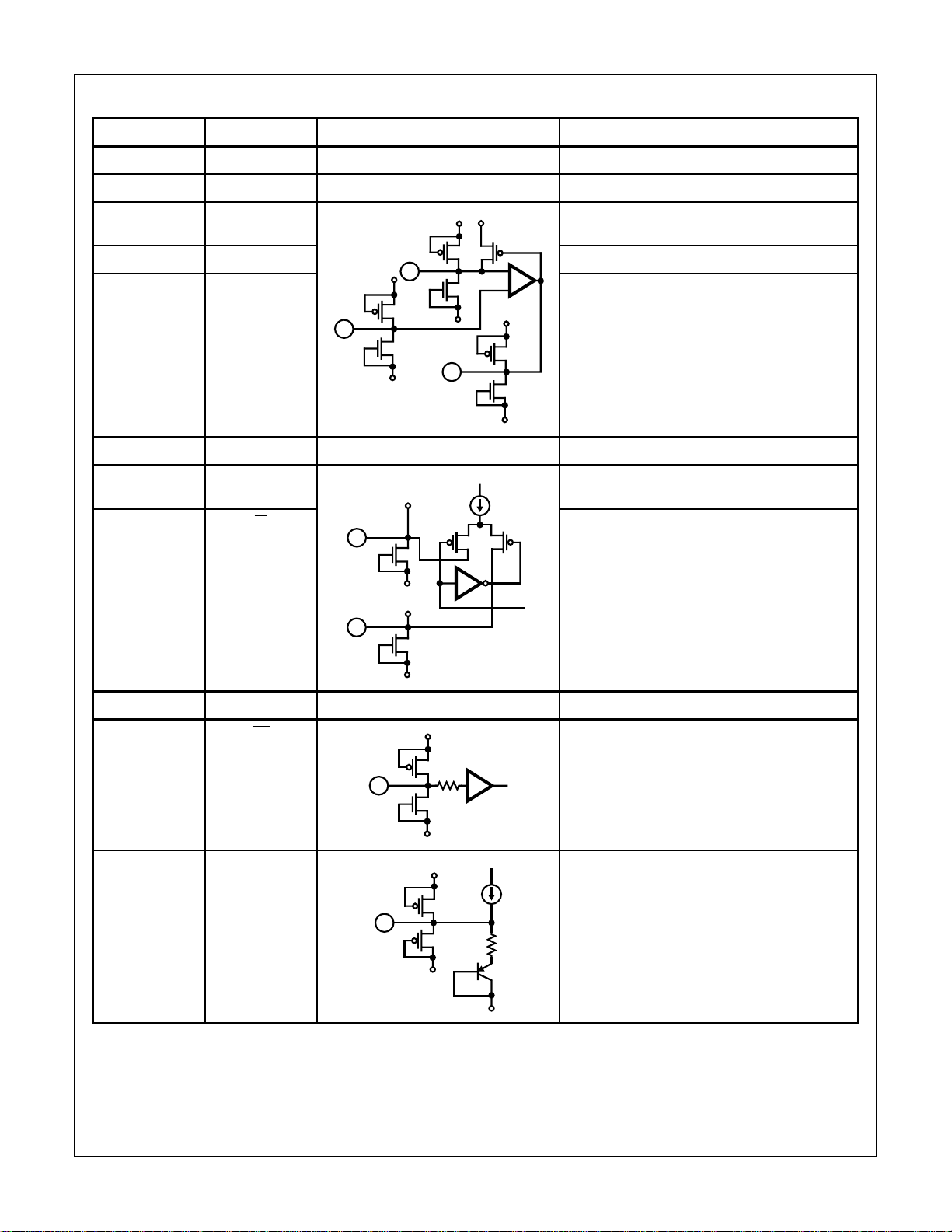

Pin Descriptions

PIN NO. SYMBOL EQUIVALENT CIRCUIT DESCRIPTION

30 to 32

1 to 7

D0 to D9 Digital Input.

30

TO

7

DV

DV

DD

SS

IO

24

AV

25

SS

IO

23

22

VG

19

V

REF

-

+

17

I

REF

21

AV

DD

20

AV

DD

18

S

REF

10 BLK Blanking pin. No signal (0V output) at high and

10

14 VB Connect a capacitor of approximately 0.1µF.

14

9 CLK Clock pin.

9

DV

DD

DV

DV

DV

SS

DV

DV

DD

SS

DD

SS

DV

DD

output state at low.

+

-

10-2

HI2315

Pin Descriptions

(Continued)

PIN NO. SYMBOL EQUIVALENT CIRCUIT DESCRIPTION

15, 27 DV

25 AV

17 I

19 V

22 VG Connect a capacitor of approximately 0.1µF.

20, 21 AV

REF

REF

SS

SS

DD

AV

DD

17

AV

DD

AV

19

AV

SS

SS

AV

DD

+

-

AV

22

AV

SS

Digital GND.

Analog GND.

Connect resistance “16R” which is 16 times output

resistance “R”.

Sets output full scale value.

DD

Analog VDD.

24 IO Current Output pin. Output can be retrieved by

AV

DD

connecting resistance. The standard is 200Ω.

23 IO Inverted Current Output pin. Connect to GND

24

normally.

AV

SS

AV

DD

23

AV

SS

13, 28 DV

11 CE Chip Enable pin. No signal (0V output) at high makes

18 S

DD

REF

DV

DD

11

DV

SS

AV

DD

Digital VDD.

power consumption minimum.

Independent Constant-Voltage Source Output pin

using band gap reference. Stable voltage

independent of the fluctuation for supply voltage can

18

AV

SS

be obtained by connecting to V

Circuit 2 for details.

. See Application

REF

10-3

Loading...

Loading...