Intersil Corporation HI-200, HI-201 Datasheet

HI-200, HI-201

Data Sheet October 1999

Dual/Quad SPST, CMOS Analog Switches

HI-200/HI-201 (dual/quad) are monolithic devices comprising

independently selectable SPST switches which f eature fast

switching speeds (HI-200 240ns, and HI-201 185ns)

combined with low power dissipation (15mW at 25

o

C). Each

switch provides low “ON” resistance operation for input signal

voltage up to the supply rails and for signal current up to

80mA. Rugged DI construction eliminates latch-up and

substrate SCR failure modes.

All devices provide break-before-make switching and are

TTL and CMOS compatible for maximum application

versatility. HI-200/HI-201 are ideal components for use in

high frequencyanalogswitching. Typicalapplicationsinclude

signal path switching, sample and hold circuit, digital filters,

and operational amplifier gain switching networks.

Ordering Information

PART

NUMBER

HI1-0200-5 0 to 75 14 Ld CERDIP F14.3

HI2-0200-5 0 to 75 10 Pin Metal Can T10.B

HI3-0200-5 0 to 75 14 Ld PDIP E14.3

HI1-0201-2 -55 to 125 16 Ld CERDIP F16.3

HI1-0201-4 -25 to 85 16 Ld CERDIP F16.3

HI1-0201-5 0 to 75 16 Ld CERDIP F16.3

TEMPERATURE

RANGE (oC) PACKAGE PKG. NO.

File Number 3121.4

Features

• Analog Voltage Range . . . . . . . . . . . . . . . . . . . . . . . ±15V

• Analog Current Range . . . . . . . . . . . . . . . . . . . . . . . 80mA

• Turn-On Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .240ns

•Low r

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55Ω

ON

• Low Power Dissipation . . . . . . . . . . . . . . . . . . . . . . .15mW

• TTL/CMOS Compatible

Applications

• High Frequency Analog Switching

• Sample and Hold Circuits

• Digital Filters

• Operational Amplifier Gain Switching Networks

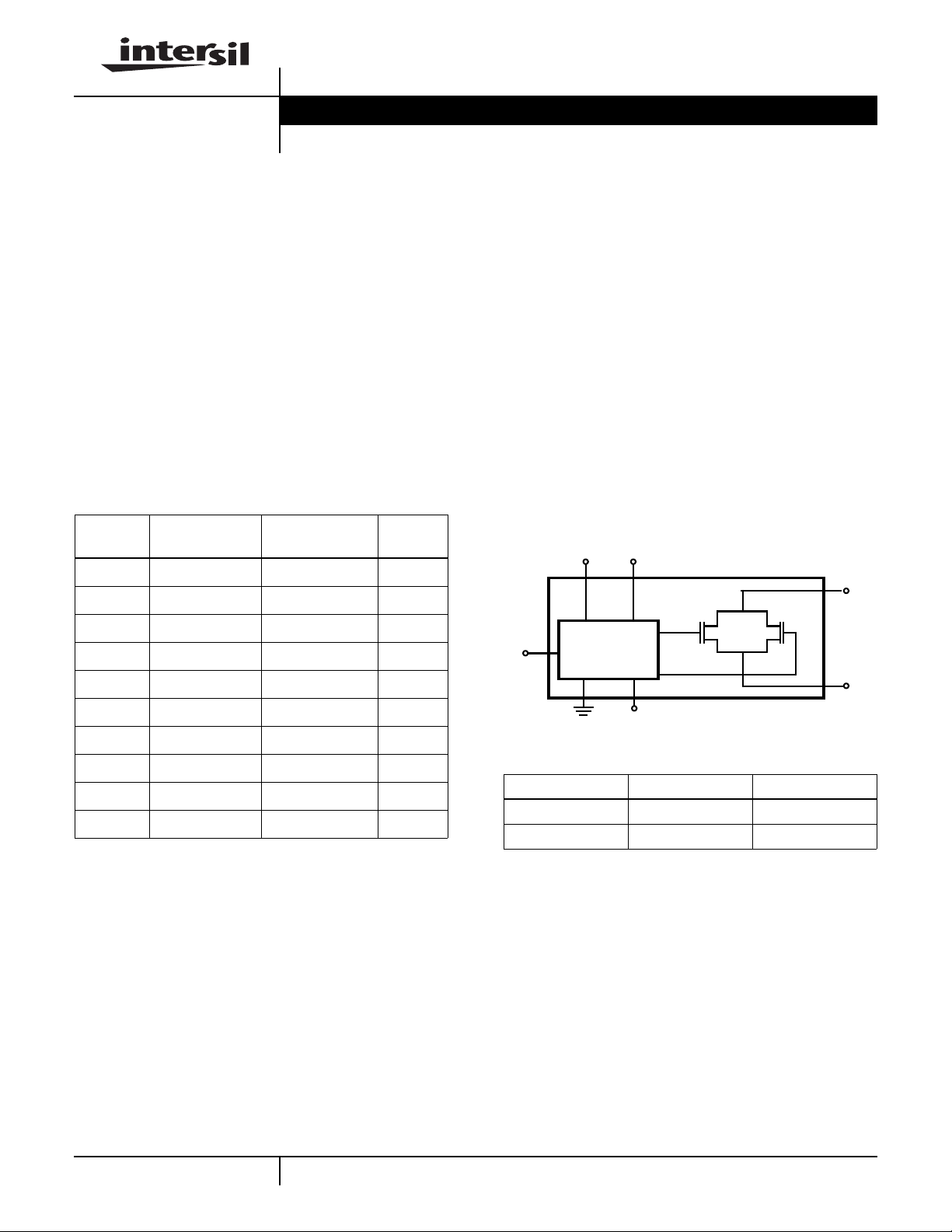

Functional Diagram

LOGIC

INPUT

V+ V

REFERENCE,

LEVEL SHIFTER,

AND DRIVER

V-

REF

GATE

SOURCE

SWITCH

CELL

INPUT

GATE

DRAIN

OUTPUT

HI3-0201-5 0 to 75 16 Ld PDIP E16.3

HI4P0201-5 0 to 75 20 Ld PLCC N20.35

HI9P0201-5 0 to 75 16 Ld SOIC M16.15

HI9P0201-9 -40 to 85 16 Ld SOIC M16.15

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

TRUTH TABLE

LOGIC HI-200 HI-201

0ONON

1 OFF OFF

1-888-INTERSIL or 407-727-9207

| Copyright © Intersil Corporation 1999

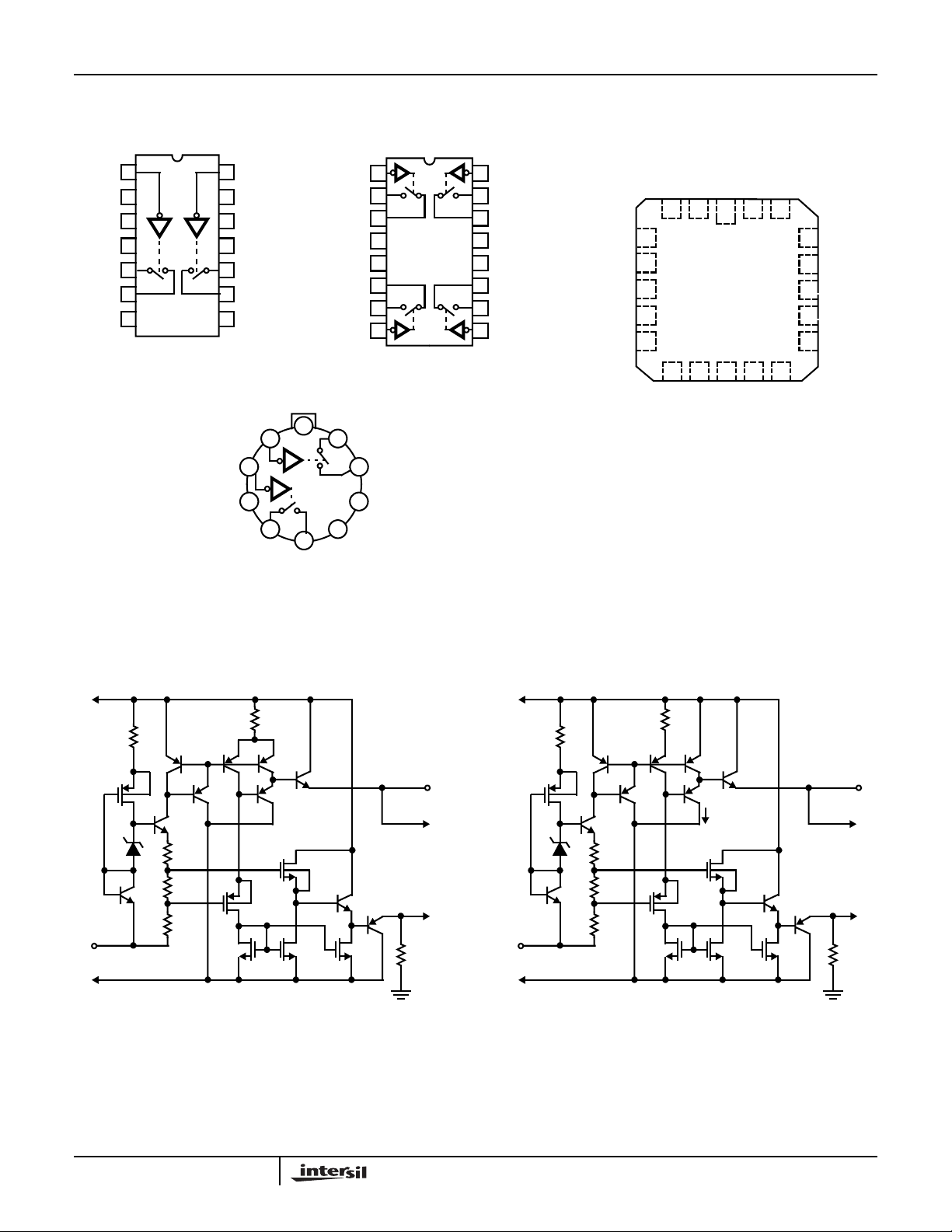

Pinouts (Switches Shown For Logic “1” Input)

HI-200 (CERDIP, PDIP)

TOP VIEW

A

NC

GND

NC

IN2

OUT2

1

2

2

3

4

5

6

7

V-

14

A

1

NC

13

12

V+

11

NC

10

IN1

9

OUT1

8

V

REF

OUT1

OUT4

HI-200, HI-201

HI-201 (CERDIP, PDIP, SOIC)

TOP VIEW

A

IN1

GND

IN4

A

1

1

2

3

4

V-

5

6

7

8

4

16

15

14

13

12

11

10

9

A

2

OUT2

IN2

V+

V

REF

IN3

OUT3

A

3

IN1

NC

GND

IN4

HI-201 (PLCC)

TOP VIEW

OUT1A1NC

3212019

4

V-

5

6

7

8

A2

OUT2

IN2

18

V+

17

NC

16

V

15

REF

IN3

14

A

A

2

GND

IN2

Schematic Diagrams

TTL/CMOS REFERENCE CIRCUIT V

HI-200

V+

R

2

GND

V-

5K

D

Q

P1

M

P13

Q

3

Q

N2

N1

R

3

24.2K

R

4

5.4K

R

5

7.9K

Q

P2

Q

P4

M

N15

HI-200 (METAL CAN)

TOP VIEW

V+

10

1

1

2

3

4

OUT2

6

R

300

Q

P3

Q

P5

M

N14

9

6

5

REF

Q

N4

M

N16

M

IN1

OUT1

8

7

V

V-

CELL

N17

REF

V

REF

TO P

V

R

7

100K

10 11 12 139

A4

OUT4

TTL/CMOS REFERENCE CIRCUIT V

NC

A3

REF

OUT3

CELL

HI-201

V+

6

R

R

2

5K

Q

P1

M

2

LL

GND

P13

Q

N1

D

3

R

3

24.2K

R

4

5.4K

Q

N2

R

5

7.9K

V-

600

Q

P2

Q

P3

Q

N4

Q

P4

M

N15

Q

P5

M

N14

M

P14

Q

N3

M

N16

M

N17

V

REF

TO P

2

V

LL

Q

P6

R

7

100K

GND

GND

2

Schematic Diagrams (Continued)

A’

HI-200, HI-201

SWITCH CELL

Q

N11

V+

Q

INPUT

A’

P1

Q

N1

V+

Q

P11

Q

N13

Q

N12

V-

Q

P12

DIGITAL INPUT BUFFER AND LEVEL SHIFTER

V+

Q

P3

Q

Q

P5

P4

OUTPUT

A’

200Ω

Q

Q

D

1

D

2

Q

TO V

TO V

P2

LL

REF

P6

Q

N6

P7

Q

N7

Q

P8

Q

N8

Q

P9

Q

N9

Q

P10

Q

N10

V-A

A’

Q

N2

Q

Q

N3

N4

Q

N5

V-

3

Loading...

Loading...