October 1998

Semiconductor

HI1866

See HI3086

NOT RECOMMENDED FOR NEW DESIGNS

6-Bit, 140 MSPS, Flash A/D Converter

Features

• Ultra-High Speed Operation with Maximum

Conversion Rate. . . . . . . . . . . . . . . . . . . . . . . 140 MSPS

[ /Title (HI1866)

• Low Input Capacitance . . . . . . . . . . . . . . . . . . . . . . . 7pF

/Subject (6-Bit, 140 MSPS, Flash A/D Converter)

• Wide Analog Input Bandwidth . . . . . . . . . . . . . 210MHz

/Author ()

• Low Power Consumption . . . . . . . . . . . . . . . . . .325mW

/Keywords (Harris Semiconductor, RGB, Video, Flat

• Low Error Rate

Panel, LCD)

• Excellent Temperature Characteristics

/Creator ()

• 1:2 Demultiplexed Output (TTL Level)

/DOCINFO pdfmark

• Direct Replacement for Sony CXA1866

[ /PageMode /UseOutlines

Applications

/DOCVIEW pdfmark

• LCD Panels

• Magnetic Recording (PRML)

• Communications (QPSK, QAM)

Pinout

HI1866

(MQFP)

TOP VIEW

Description

HI1866 is a 6-bit, high-speed, flash A/D converter capable of

digitizing analog signals at the maximum rate of 140 MSPS.

The digital input level is compatible with the ECL

100K/10KH/10K.

Ordering Information

PART

NUMBER

HI1866JCQ -20 to 75 48 Ld MQFP Q48.12x12-S

TEMP.

RANGE (oC) PACKAGE PKG. NO.

DGND3

P2D0 (LSB)

P2D1

P2D2

P2D3

P2D4

P2D5 (MSB)

DGND3

DV

CC2

NC

DCLK

NDCLK

CC2

DV

DV

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16

EE

NC

AV

CC1

DGND1

DGND2

RB

RBS

V

V

EE

DV

AGND

CC2

DV

NC

EE

DGND3

DV

IN

V

AGND

DGND2

DGND1

RT

RTS

V

V

DV

EE

AV

CC1

373839404142434445464748

2423222120191817

36

35

34

33

32

31

30

29

28

27

26

25

DV

NC

CC2

DGND3

P1D5 (MSB)

P1D4

P1D3

P1D2

P1D1

P1D0 (LSB)

DGND3

DV

CC2

INV

CCLK

NCCLK

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1997

4-1

File Number 4108.2

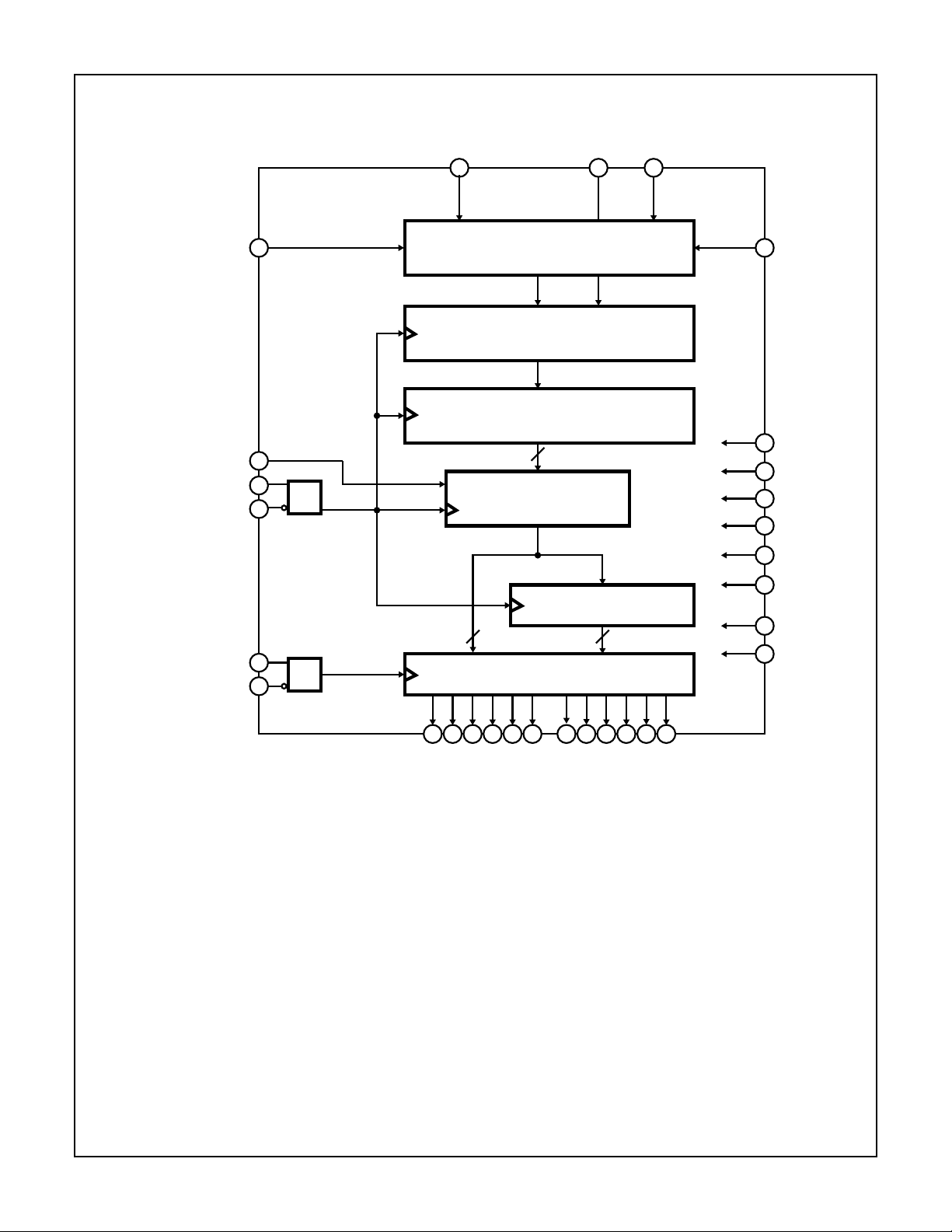

Functional Block Diagram

HI1866

V

RTS

INV

CCLK

NCCLK

DCLK

NDCLK

V

RBS

16 21 V

27

26

CD

25

11

CD

12

REFERENCE RESISTANCE CHAIN

COMPARATOR

6-BIT LATCH

CLATCH A

TTLOUT

6

V

IN

19 2215

CLATCH B

66

V

RTS

41

23

20

46

45

42

47

48

RT

D

VEE

A

VEE

AGND

DGND1

DGND2

DGND3

DV

CC1

DV

CC2

CD: CLOCK DRIVER

7 6 5 4 3 2 35 34 33 32 31 30

P2D4

P2D3

P2D2

P2D5 (MSB)

P2D1

P2D0 (LSB)

P1D4

P1D3

PD15 MSB)

P1D2

P1D1

P1D0 (LSB)

4-2

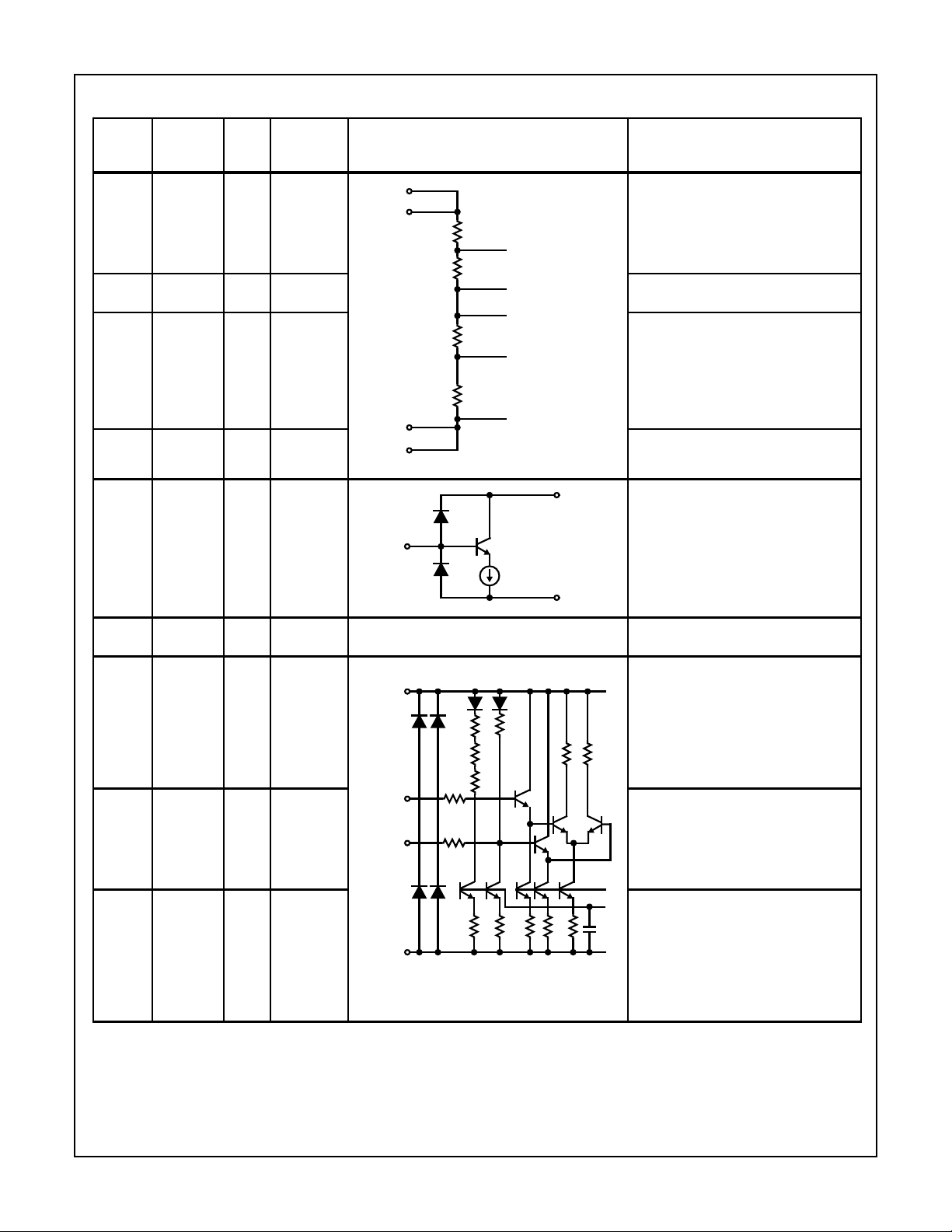

Pin Descriptions

PIN NO. SYMBOL I/O

21 V

22 V

16 V

15 V

RT

RTS

RB

RBS

HI1866

TYPICAL

VOLTAGE

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

I 0V Top reference voltage input (= 0). This is

O0V V

I -2V Bottom reference voltage input (= -2V).

O -2V VRB sense output. This is the voltage

V

V

V

RTS

RBS

V

RB

RT

COMPARATOR 1

COMPARATOR 2

COMPARATOR 31

COMPARATOR 32

COMPARATOR 63

the top reference voltage supplied to the

internal resistance chain. The external

input can be set in accordance with the

peak value on the plus side of the input

analog signal amplitude.

sense output. This is the voltage

RT

sense pin for VRT.

This is the bottom reference voltage

supplied to the internal resistance

chain. The external input can be set in

accordance with the peak value on the

minus side of the input analog signal

amplitude.

sense pin for VRB.

19 V

IN

IV

RTS

V

RBS

to

AGND

V

IN

A

VEE

Analog input. The input range is 2V

P-P

26 CCLK I ECL CCLK clock input. This is the conversion

clock, and is an ECL level input.

25 NCCLK I ECL CCLK inversion clock input. This is an

DGND1

ECL level input. When left open, this

input goes to the ECL threshold potential

(-1.3V). Only CCLK input can be used for

R

R

R

500

11 DCLK I ECL DCLK clock input. This is the 1:2 DMPX

CCLK

(DCLK)

NCCLK

(NDCLK)

R

500

operation with the NCCLK input left

open, but complementary input is

recommended to attain fast and stable

operation.

latch clock; input a clock of1/2 frequency

of CCLK. Data is output from DMPX port

1 and port 2 synchronously with the

rising edge of this signal. This is an ECL

level input.

12 NDCLK I ECL DCLK inversion clock input. This is an

RR

D

VEE

ECL level input. When left open, this

1.3V

input goes to the ECL threshold potential

(-1.3V). Only DCLK input can be used for

operation with the NDCLK input left

open, but complementary input is

recommended to attain fast and stable

operation.

.

4-3

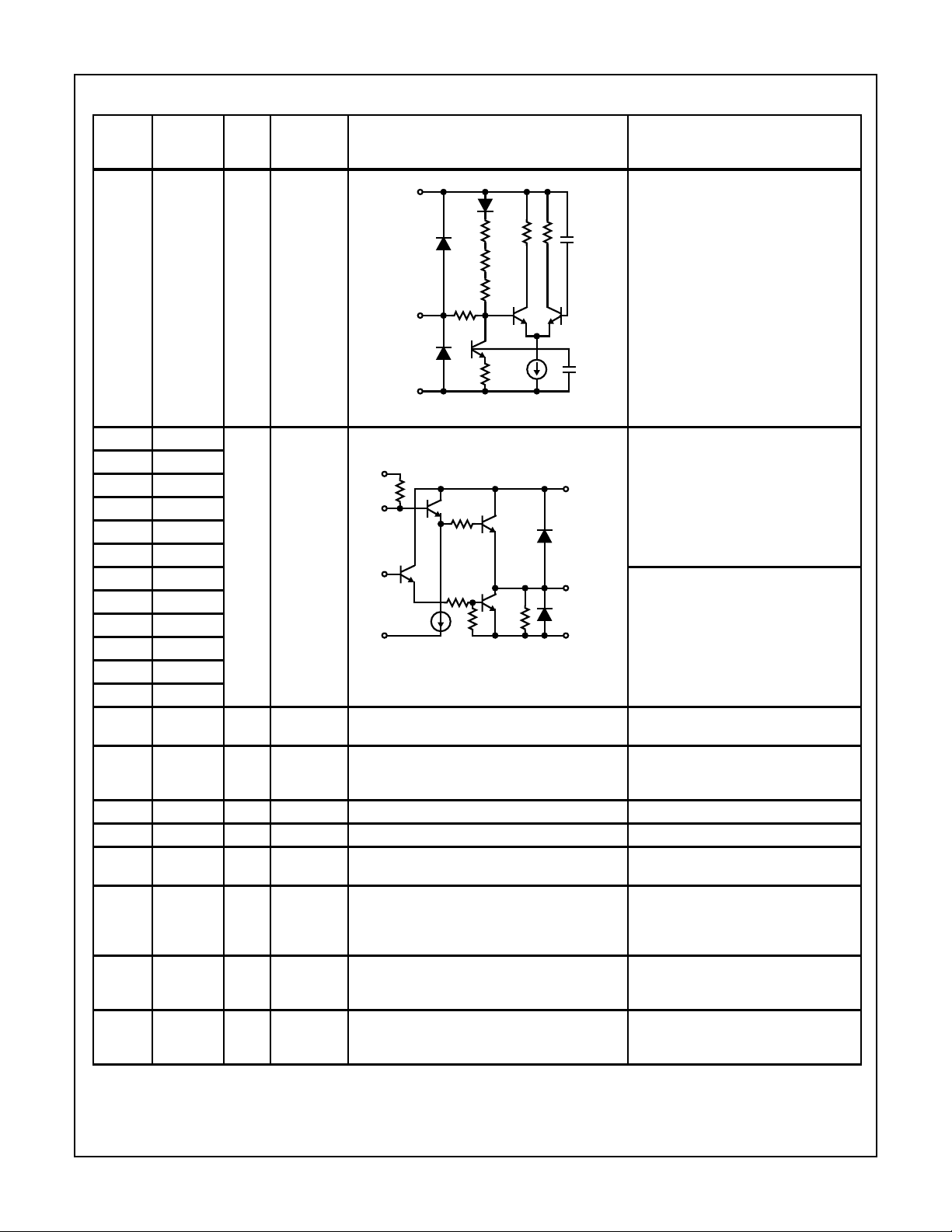

HI1866

Pin Descriptions

(Continued)

TYPICAL

VOLTAGE

PIN NO. SYMBOL I/O

27 INV I ECL Digital output polarity inversion input.

LEVEL EQUIVALENT CIRCUIT DESCRIPTION

DGND1

This is an ECL level input. This input

inverts the polarity of the digital outputs

R

R

1.3V

P1D0 to P1D5, and P2D0 to P2D5.

(Refer to the Output Code Table.) When

left open, this signal is maintained at the

low level.

R

500

INV

1.3V

D

R

VEE

30 P1D0 O TTL These pins are for the 6 bits of digital

31 P1D1

32 P1D2

DV

CC1

DV

CC2

output data for DMPX port 1. P2D5 is the

MSB, and P2D0 is the LSB. These are

TTL levels outputs.

33 P1D3

34 P1D4

35 P1D5

2 P2D0 These pins are for the 6 bits of digital

3 P2D1

100K

4 P2D2

5 P2D3

P1D0 TO D5

P2D0 TO D5

DGND3DGND2

output data for DMPX port 2. P2D5 is the

MSB, and P2D0 is the LSB. These are

TTL level outputs.

6 P2D4

7 P2D5

38, 47 DVCC1 - +5.0V +5V power supply for TTL level internal

circuit.

9, 28,

37, 43,

DVCC2 - +5.0V +5V power supply for TTL level output

buffers (P1D0 to P2D5).

48

39, 46 DGND1 - 0V Ground for DV

40, 45 DGND2 - 0V Ground for DV

1, 8, 29,

DGND3 - 0V Ground for DV

digital circuit.

EE

digital circuit.

CC1

digital circuit.

CC2

36, 42

17, 20 AGND - 0V Ground for A VEE analog circuit. Used as

the ground for the comparator input

buffers, latches, etc. Separated from

DGND.

41, 44 DV

EE

- -5.2V -5.2V power supply for digital circuit.

Connected internally with AVEE.

(Resistance is 4Ω to 6Ω.)

14, 23 AV

EE

- -5.2V -5.2V power supply for analog circuit.

Connected internally with DVEE.

(Resistance is 4Ω to 6Ω.)

4-4

Loading...

Loading...