Intersil Corporation HI1276 Datasheet

HI1276

August 1997

Features

• Differential Linearity Error . . . . . . . . . . . . . . . ±0.5 LSB

• Integral Linearity Error . . . . . . . . . . . . . . . . . . ±0.7 LSB

• Built-In Integral Linearity Compensation Circuit

• Ultra High Speed Operation with Maximum

Conversion Rate (Min). . . . . . . . . . . . . . . . . . 500 MSPS

• Low Input Capacitance (Typ) . . . . . . . . . . . . . . . . .20pF

• Wide Analog Input Bandwidth

(Min for Full Scale Input). . . . . . . . . . . . . . . . . . 300MHz

• Single Power Supply . . . . . . . . . . . . . . . . . . . . . . . -5.2V

• Low Power Consumption (Typ) . . . . . . . . . . . . . . .2.8W

• Low Error Rate

• Capable of Driving 50Ω Loads

• Direct Replacement for Sony CXA1276K

Applications

• Radar Systems

• Communication Systems

• Digital Oscilloscopes

• Direct RF Down-Conversion

8-Bit, 500 MSPS, Flash A/D Converter

Description

The HI1276 is an 8-bit, ultra-high-speed, flash Analog-toDigital converter IC capable of digitizing analog signals at a

maximum rate of 500 MSPS. The digital I/O lev els of this A/D

converter are compatible with ECL 100K/10KH/10K.

The HI1276 is available in the Industrial temperature range

and is supplied in a 68 lead ceramic LCC package.

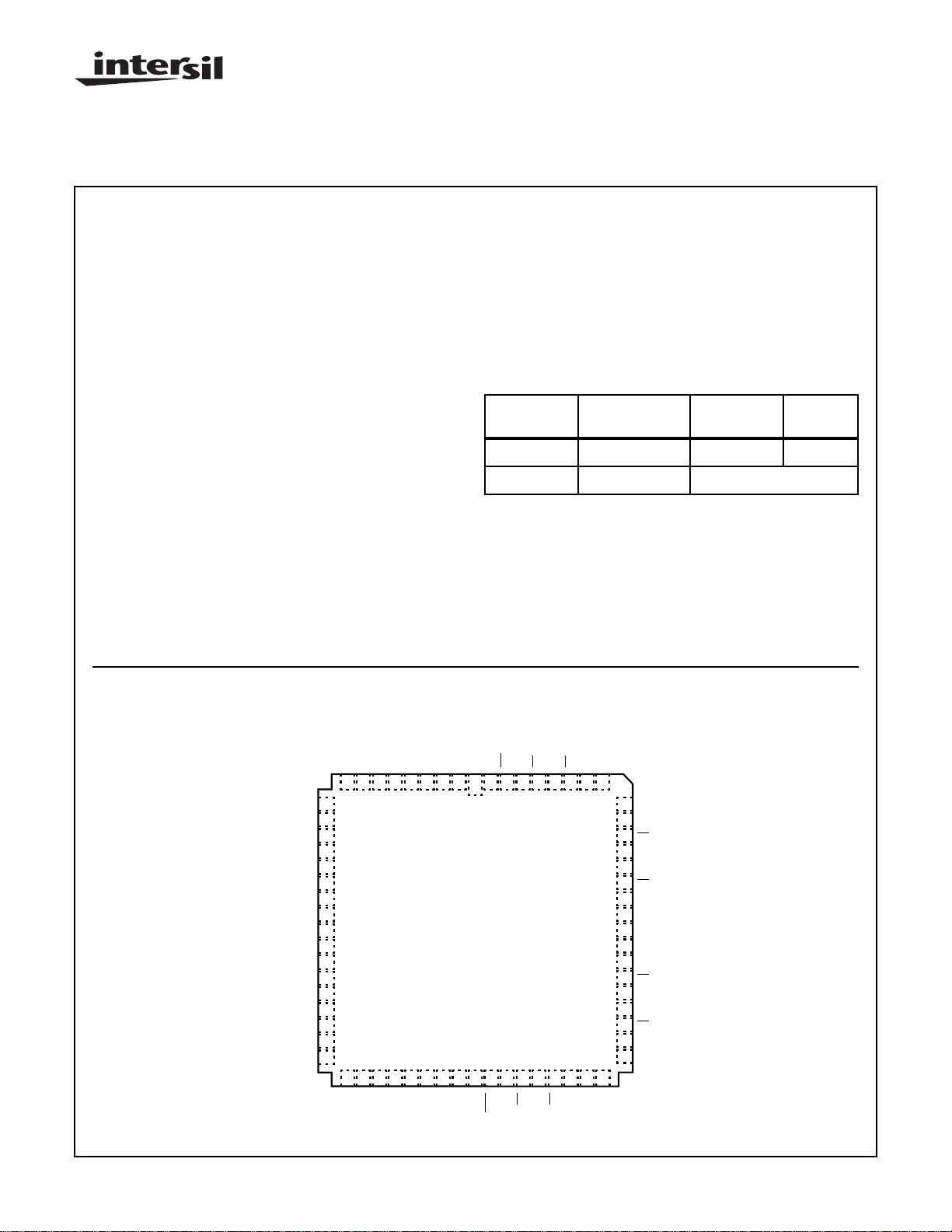

Ordering Information

PART

NUMBER

HI1276AIL -20 to 100 68 Ld CLCC J68.B

HI1276-EV 25 Evaluation Board

TEMP. RANGE

(oC) PACKAGE PKG. NO.

Pinout

NC

NC

AV

NC

AGND

V

IN1

V

IN1

AGND

V

RM

AGND

V

IN2

V

IN2

AGND

NC

NC

NC

NC

HI1276 (CLCC)

HEAT SINK UP, RECESSED CAVITY DOWN

EE

AGND

876543216867666564636261

9

10

11

12

EE

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

EE

AGND

RTSVRT

V

AVEEAV

RB

NC

RBS

V

AVEEAV

V

OR

LINV

AVEEAVEENC

EEAVEE

CLK

CLK

AV

OR

MINV

D0

D0

D7

D7

DVEED1

D1

D6

DGND1

60

DGND2

59

D2

58

D2

57

DV

EE

56

D3

55

D3

54

DGND2

53

DGND2

52

DGND1

51

DGND1

50

D4

49

D4

48

DV

EE

47

D5

46

D5

45

NC

44

DGND2

EE

D6

DV

DGND1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

4-1

File Number 3578.4

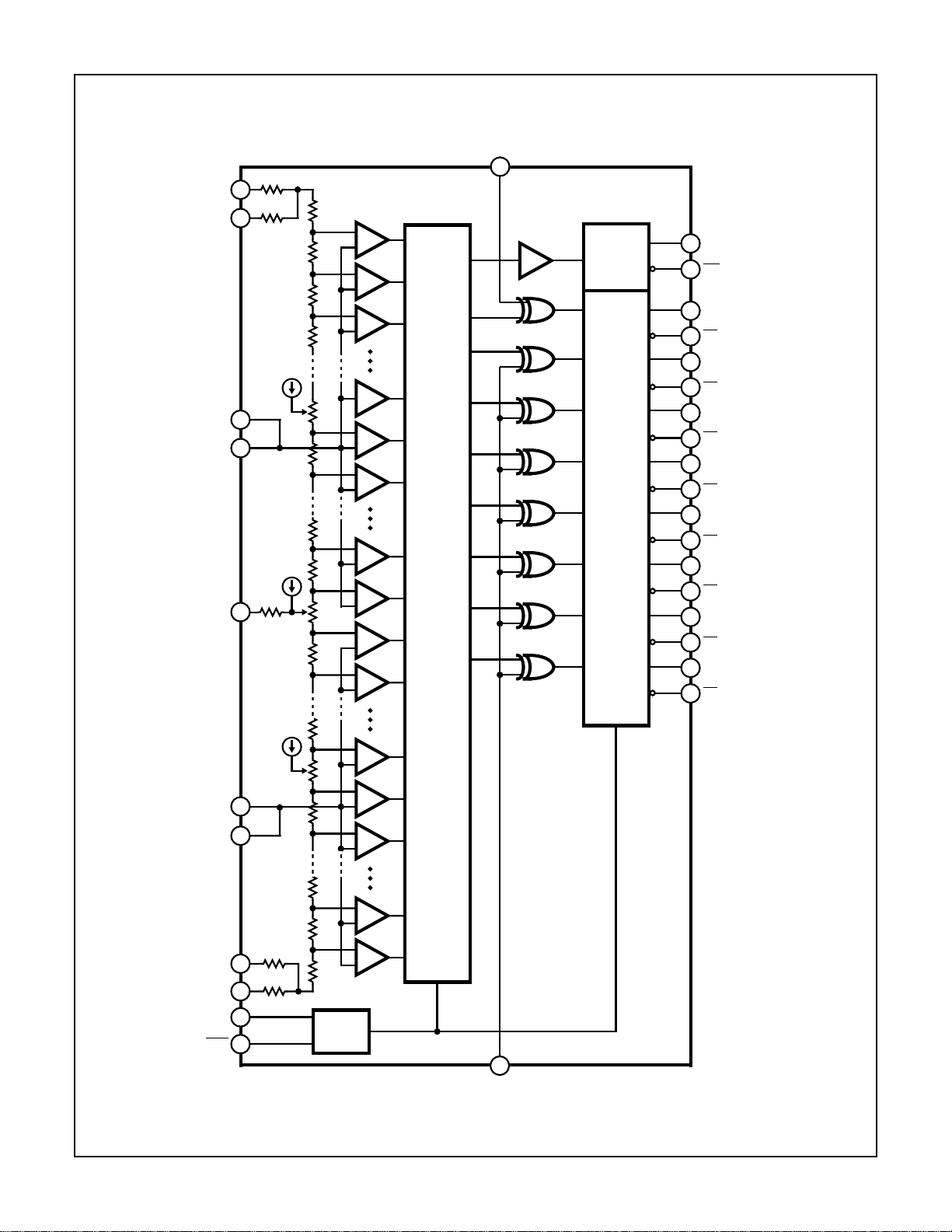

Functional Block Diagram

R1

6

V

RT

V

5

V

V

RTS

IN1

RM

R2

15

16

R3

18

R/2

R

R

R

R

R

R

R

R

R

COMPARATOR

0

1

2

63

64

65

126

127

ENCODE

128

129

LOGIC

HI1276

MINV

37

68

OR

67

OR

39

D7 (MSB)

D7

38

41

D6

40

D6

47

D5

D5

46

D4

50

49

56

55

59

58

64

63

66

65

D4

D3

D3

D2

D2

D1

D1

D0 (LSB)

D0

OUTPUT

V

V

CLK

CLK

IN2

RBS

V

RB

R

191

R

20

21

R4

31

30

R5

35

36

192

R

193

R

254

R

255

R/2

CLOCK

DRIVER

1

LINV

4-2

HI1276

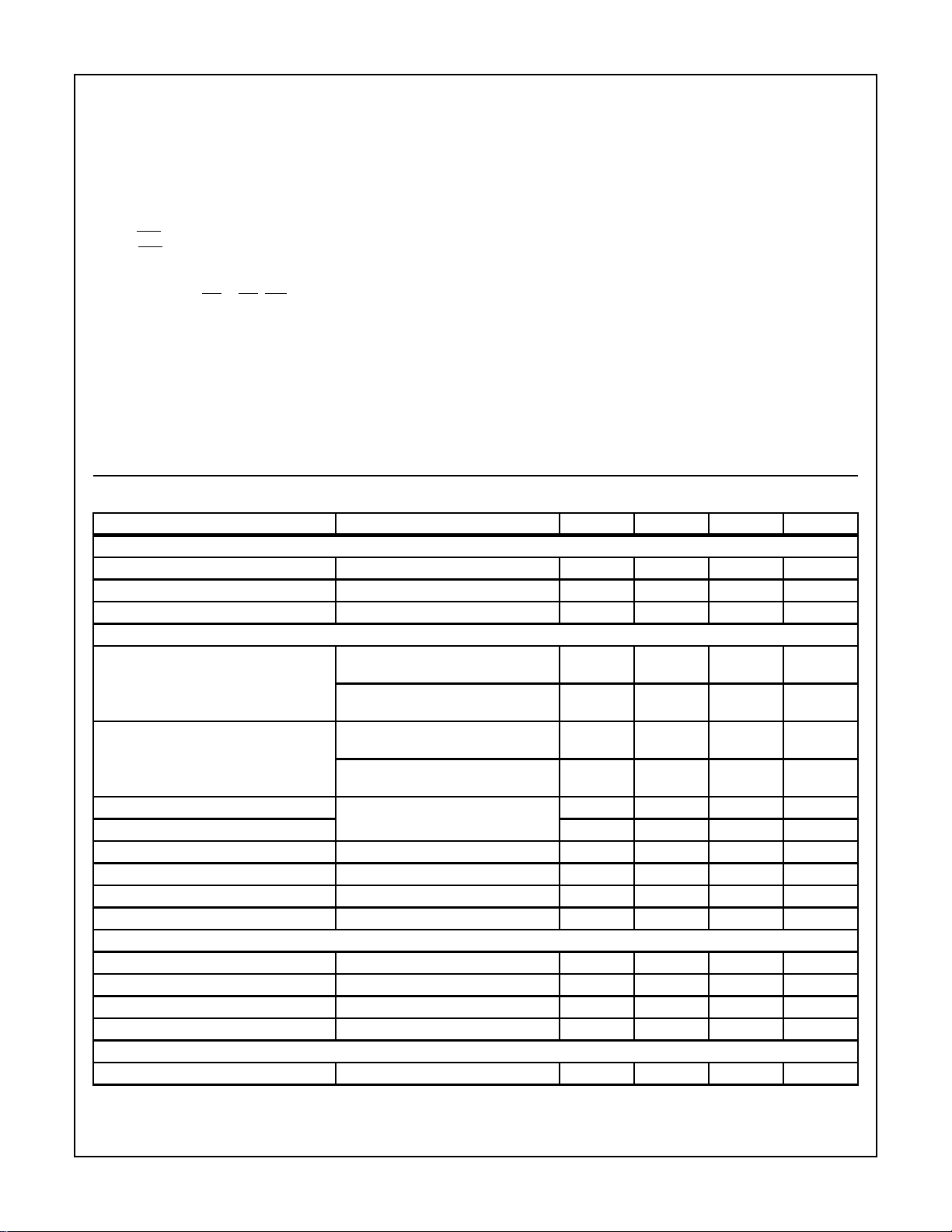

Absolute Maximum Ratings T

Supply Voltage (AVEE, DVEE) . . . . . . . . . . . . . . . . . . . -7V to +0.5V

Analog Input Voltage (VIN) . . . . . . . . . . . . . . . . . . . . . . -2.7 to +0.5V

Reference Input Voltage

VRT, VRB, VRM . . . . . . . . . . . . . . . . . . . . . . . . . . .AVEE to +0.5V

|VRT- VRB|. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2.5V

= 25oC Thermal Information

A

Thermal Resistance (Typical) θ

CLCC Package . . . . . . . . . . . . . . . . . . 18 4

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . . 175oC

Maximum Storage Temperature Range (T

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . 300oC

o

C/W θ

JA

) . . . .-65oC to 150oC

STG

JC

o

C/W

Digital Input Voltage

MINV, LINV . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -4V to +0.5V

CLK, CLK, . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .DVEE to +0.5V

|CLK-CLK | . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2.7V

VRM Pin Input Current (I

) . . . . . . . . . . . . . . . . . . -3mA to +3mA

VRM

Digital Output Current

(ID0 to ID7, IOR, ID0 to ID7, IOR) . . . . . . . . . . . . . -30mA to 0mA

Operating Conditions (Note 1)

Supply Voltage MIN TYP MAX

AVEE, DVEE . . . . . . . . . . . . . . . . . . . . . . . -5.5V -5.2V -4.95V

AVEE - DVEE. . . . . . . . . . . . . . . . . . . . . . .-0.05V 0V 0.05V

AGND - DGND . . . . . . . . . . . . . . . . . . . . .-0.05V 0V 0.05V

Temperature Range (Note 5)

TC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-20oC - 100oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Electrical Specifications T

= 25oC, AVEE = DVEE = -5.2V, VRT, V

A

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

SYSTEM PERFORMANCE

Resolution - 8 - Bits

Integral Linearity Error, INL f

Differential Linearity Error, DNL f

= 500 MSPS - ±0.3 ±0.7 LSB

C

= 500 MSPS - ±0.3 ±0.5 LSB

C

DYNAMIC CHARACTERISTICS

Signal to Noise and Distortion Ratio, SINAD Input = 1kHz, Full Scale

= 500 MSPS

f

RMS Signal

----------------------------------------------------------------- -=

RMS Noise Distortion+

C

Input = 100MHz, Full Scale

= 500 MSPS

f

C

Error Rate Input = 100MHz, Full Scale

Error > 16 LSB, f

C

Input = 125MHz, Full Scale

Error > 16 LSB, f

C

Differential Gain Error, DG NTSC 40 IRE Mod.

Differential Phase Error, DP - 0.5 - Degree

Ramp, f

= 500 MSPS

C

Overrange Recovery Time - 1.0 - ns

Maximum Conversion Rate, f

Aperture Jitter, t

Sampling Delay, t

AJ

DS

C

Input = 150MHz - 11 - ps

Input = 150MHz 0.2 0.8 1.5 ns

ANALOG INPUT

Analog Input Capacitance, C

Analog Input Resistance, R

Input Bias Current, I

IN

IN

IN

Full Scale Input Bandwidth V

VIN = 1V + 0.07V

RMS

VIN = -1V - - 850 µA

= 2V

IN

P-P

REFERENCE INPUTS

Reference Resistance, R

REF

Reference Input Voltage MIN TYP MAX

VRT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.1V -2 0.1V

VRB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -2.2V -2 -1.8V

Analog Input Voltage, VIN . . . . . . . . . . . . . . V

= 0V, VRB, V

RTS

= -2V (Note 1)

RBS

RB -

-46-dB

-37-dB

-10

-11

10

-9

= 400 MSPS

-10-810

-6

= 500 MSPS

- 1.0 - %

500 - - MSPS

-20-pF

30 70 - kΩ

300 - - MSPS

70 110 160 Ω

V

TPS

(Note 3)

TPS

(Note 3)

RT

4-3

HI1276

Electrical Specifications T

= 25oC, AVEE = DVEE = -5.2V, VRT, V

A

= 0V, VRB, V

RTS

= -2V (Note 1) (Continued)

RBS

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Residual Resistance R1 Note 2 0.1 0.5 2.0 Ω

R2 0.5 5.2 10 Ω

R3 0.5 1.6 5.0 Ω

R4 0.5 8.7 20 Ω

R5 0.1 0.5 2.0 Ω

DIGITAL INPUTS

Logic H Level, V

Logic L Level, V

Logic H Current, I

Logic L Current, I

IH

IL

IH

IL

Input Connected to -0.8V 0 - 70 µA

Input Connected to -1.6V -50 - 60 µA

-1.10 - - V

- - -1.55 V

Input Capacitance - 6 - pF

DIGITAL OUTPUTS

Logic H Level, V

Logic L Level, V

OH

OL

RL = 50Ω -1.03 - - V

RL = 50Ω - - -1.58 V

TIMING CHARACTERISTICS

Clock Duty Cycle 45 50 55 %

Output Rise Time, t

Output Fall Time, t

Output Delay, t

OD

r

f

RL = 50Ω, 20% to 80% 0.5 0.7 1.0 ns

RL = 50Ω, 80% to 20% 0.5 0.7 1.0 ns

1.5 1.9 2.3 ns

POWER SUPPLY CHARACTERISTICS

Supply Current, I

EE

Power Consumption, P

D

Note 4 - 2.8 3.6 W

-680 -520 - mA

NOTES:

1. Electrical Specifications guaranteed within stated operating conditions.

2. See Functional Block Diagram.

3. TPS: Times Per Sample.

PDI

4. .

5. T

EEAAVEEIEEDDVEE

is specified in still air and without heatsink. To extend temperature range, appropriate heat management techniques must be employed

A

•+•

V

RTVRB

-------------------------------------+=

R

2

–()

REF

(See Figure 2).

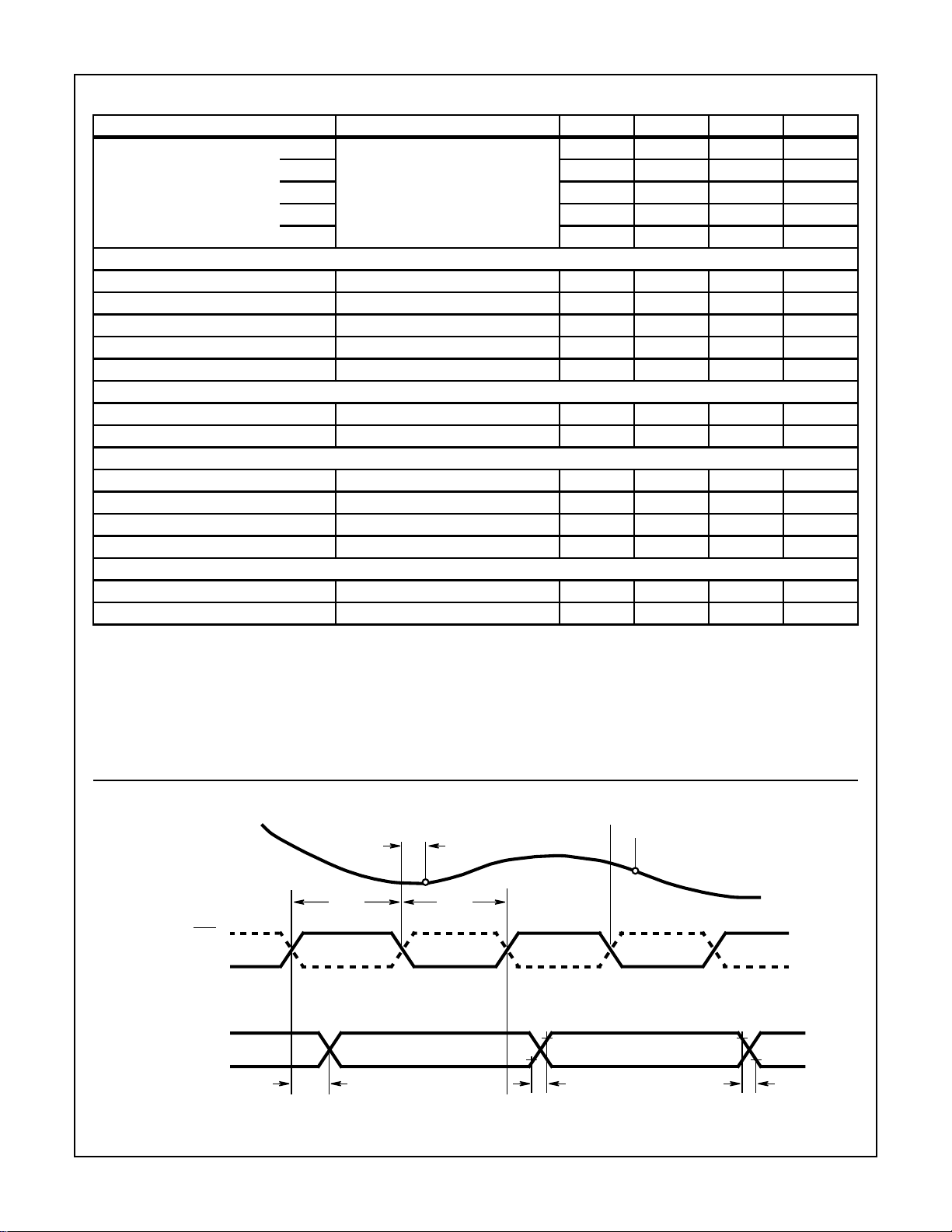

Timing Diagram

ANALOG IN

CLK

CLK

DIGITAL OUT

t

DS

N + 1

t

PW1

t

OD

t

PW0

20%

80%

t

r

N + 2

NN - 1

80%

N + 1

20%

t

f

FIGURE 1.

4-4

Loading...

Loading...