Intersil Corporation HI1176 Datasheet

October 1998

Semiconductor

HI1176

See HI1179

NOT RECOMMENDED FOR NEW DESIGNS

8-Bit, 20 MSPS, Flash A/D Converter

Features

• Resolution ±0.5 LSB (DNL) . . . . . . . . . . . . . . . . . . . 8-Bit

• Maximum Sampling Frequency . . . . . . . . . . . 20 MSPS

[ /Title (HI1176)

/Subject (8-Bit, 20 MSPS, Flash A/D Converter)

• Low Power Consumption at 20 MSPS (Typ)

(Reference Current Excluded) . . . . . . . . . . . . . . .60mW

/Author ()

/Keywords (Harris Semiconductor, Video, Image Scan-

• Built-In Sync Clamp Function

ner, PC Video capture, Set top box, Clamp, Internal Ref-

• Built-In Monostable Multivibrator for Clamp Pulse

erence)

Generation

/Creator ()

• Built-In Sync Pulse Polarity Selection Function

/DOCINFO pdfmark

• Clamp Pulse Direct Input Possible

Description

The HI1176 is an 8-bit, CMOS analog-to-digital converter for

video use that features a sync clamp function. The adoption

of a 2-step parallel method realizes low power consumption

and a maximum conversion speed of 20 MSPS. For higher

sampling rates, refer to the pin-for-pin compatible HI1179

data sheet, AnswerFAX document number 3666.

Applications

• Video Digitizing

• Image Scanners

• Low Cost High Speed Data Acquisition Systems

• Built-In Clamp ON/OFF Function

[ /PageMode /UseOutlines

• Built-In Reference Voltage Self Bias Circuit

/DOCVIEW pdfmark

• Input CMOS Compatible

• Multimedia

Ordering Information

• Three-State TTL Compatible Output

• Single +5V Power Supply

• Low Input Capacitance (Typ) . . . . . . . . . . . . . . . . 11pF

• Reference Impedance (Typ) . . . . . . . . . . . . . . . . . 300Ω

HI1176JCQ -40 to 85 32 Ld MQFP Q32.7x7-S

HI1176-EV 25 Evaluation Board

• Direct Replacement for the Sony CXD1176

PART

NUMBER

TEMP. RANGE

(oC) PACKAGE PKG. NO.

Pinout

(LSB) D0

D1

D2

D3

D4

D5

D6

(MSB) D7

HI1176

(MQFP)

TOP VIEW

NC

DVSSOE

CLE

DVSSCCP

32 31 30 29 28 27 26 25

1

2

3

4

5

6

7

8

9 10111213141516

DD

DD

NC

DV

DV

CLK

SEL

SYNC

REFVRBS

V

24

23

22

21

20

19

18

17

DD

PW

AV

V

AV

AV

V

AV

AV

V

V

RB

SS

SS

IN

DD

DD

RT

RTS

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1998

4-1

File Number 3582.5

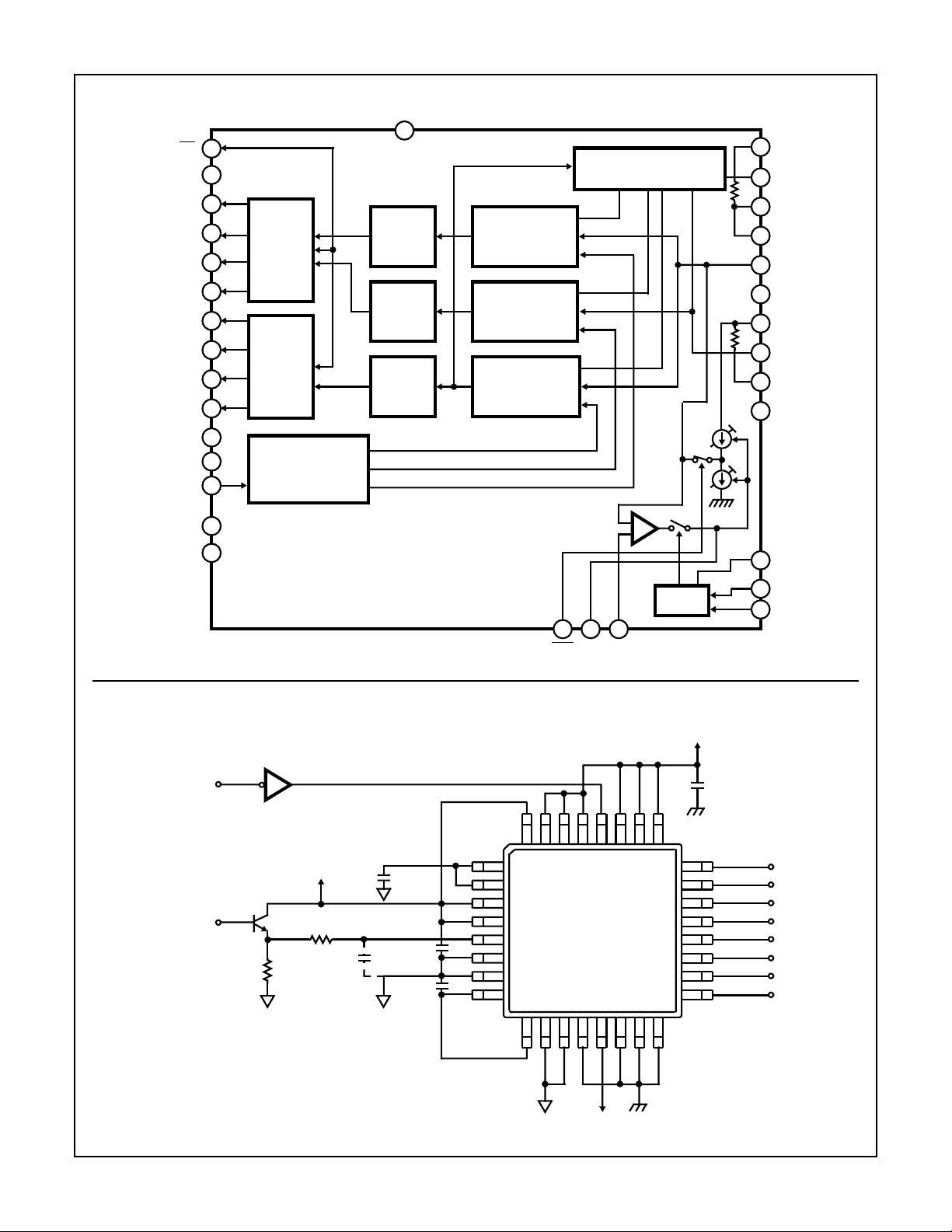

Functional Block Diagram

OE

30

DV

31

SS

D0 (LSB)

D7 (MSB)

DV

DV

CLK

D1

D2

D3

D4

D5

D6

DD

DD

1

2

3

4

5

6

7

8

10

11

12

LOWER

DAT A

LATCHES

UPPER

DAT A

LATCHES

CLOCK GENERATOR

28

DV

SS

LOWER

ENCODER

(4-BIT)

LOWER

ENCODER

(4-BIT)

UPPER

ENCODER

(4-BIT)

HI1176

LOWER SAMPLING

COMP ARAT OR

LOWER SAMPLING

COMP ARAT OR

UPPER SAMPLING

COMPARATOR

(4-BIT)

(4-BIT)

(4-BIT)

REFERENCE SUPPLY

25

V

RBS

24

V

RB

AV

23

SS

AV

22

SS

21

V

IN

20

AV

DD

AV

19

DD

V

18

RT

17

V

RTS

AV

16

DD

9

NC

32

NC

Typical Application Schematic

WHEN CLAMP IS NOT USED (SELF BIAS USED)

HCO4

CLOCK IN

+5V (ANALOG)

VIDEO IN

75Ω

10pF

0.01µF

0.1µF

0.01µF

-

+

262729

CLE CCP V

16 15 14 13 12 11 10 9

17

18

19

20

21

22

23

24

25 26 27 28 29 30 31 32

REF

M • M

8

7

6

5

4

3

2

1

15

14

13

+5V (DIGITAL)

0.1µF

PW

SYNC

SEL

D7

D6

D5

D4

D3

D2

D1

D0

GND (ANALOG) GND (DIGITAL)

+5V (DIGITAL)

4-2

HI1176

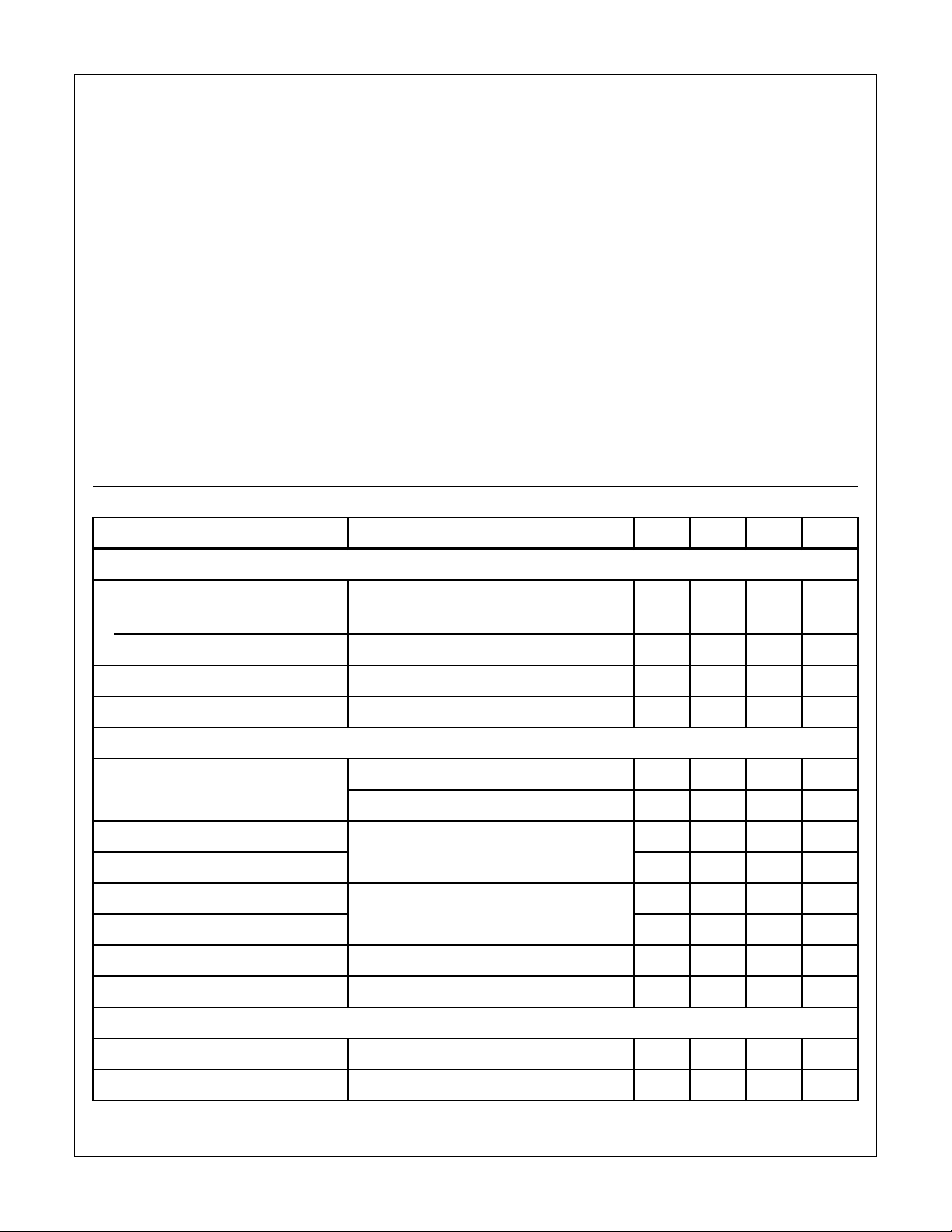

Absolute Maximum Ratings Thermal Information

Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7V

Reference Voltage, VRT, VRB . . . . . . . . . VDD + 0.5V to VSS- 0.5V

Analog Input Voltage, VIN. . . . . . . . . . . . . VDD + 0.5V to VSS- 0.5V

Digital Input Voltage, CLK. . . . . . . . . . . . . VDD + 0.5V to VSS- 0.5V

Digital Output Voltage, VOH, VOL. . . . . . . VDD + 0.5V to VSS- 0.5V

Operating Conditions (Note 1)

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

Supply Voltage

AVDD, AVSS, DVDD, DVSS . . . . . . . . . . . . . . . +4.75V to +5.25V

|DGND-AGND| . . . . . . . . . . . . . . . . . . . . . . . . . . . .0mV to 100mV

Reference Input Voltage

VRB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V and Above

VRT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2.8V and Below

Analog Input Voltage, VIN. . . . . . . . . VRB to VRT (1.8V

Clock Pulse Width

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25ns (Min)

PW1

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25ns (Min)

PW0

CAUTION: Stresses above those listed in “Absolute Maxim um Ratings” ma y cause permanent damage to the device . This is a stress only rating and oper ation of

the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

to AVDD)

P-P

Thermal Resistance (Typical, Note 1) θJA (oC/W)

MQFP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300oC

(Lead Tips Only)

Electrical Specifications f

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SYSTEM PERFORMANCE

Offset Voltage

E

OT

E

OB

Integral Non-Linearity, INL fC = 20 MSPS, VIN = 0.5V to 2.5V - ±0.5 ±1.3 LSB

Differential Non-Linearity, DNL fC = 20 MSPS, VIN = 0.5V to 2.5V - ±0.3 ±0.5 LSB

DYNAMIC CHARACTERISTICS

Signal to Noise Ratio, SINAD fS = 20MHz, fIN = 1MHz - 46 - dB

----------------------------------------------------------------------------------------------------------------

Signal-To-Noise + Distortion Ratio, SINAD

Maximum Conversion Speed, f

Minimum Conversion Speed - - 0.5 MSPS

Differential Gain Error, DG NTSC 40 IRE Mod Ramp, fC = 14.3 MSPS - 1.0 - %

Differential Phase Error, DP - 0.5 - Degree

RMS Signal

= 20 MSPS, VDD = +5V, VRB = 0.5V, VRT = 2.5V, TA = 25oC (Note 1)

C

fS = 20MHz, fIN = 3.58MHz - 46 - dB

C

VIN = 0.5V to 2.5V, fIN = 1kHz Ramp 20 35 - MSPS

-60 -40 -20 mV

+20 +40 +60 mV

Aperture Jitter, t

Sampling Delay, t

ANALOG INPUTS

Analog Input Bandwidth (-1dB), BW - 18 - MHz

Analog Input Capacitance, C

AJ

DS

IN

VIN = 1.5V + 0.07V

RMS

-30-ps

-4-ns

-11-pF

4-3

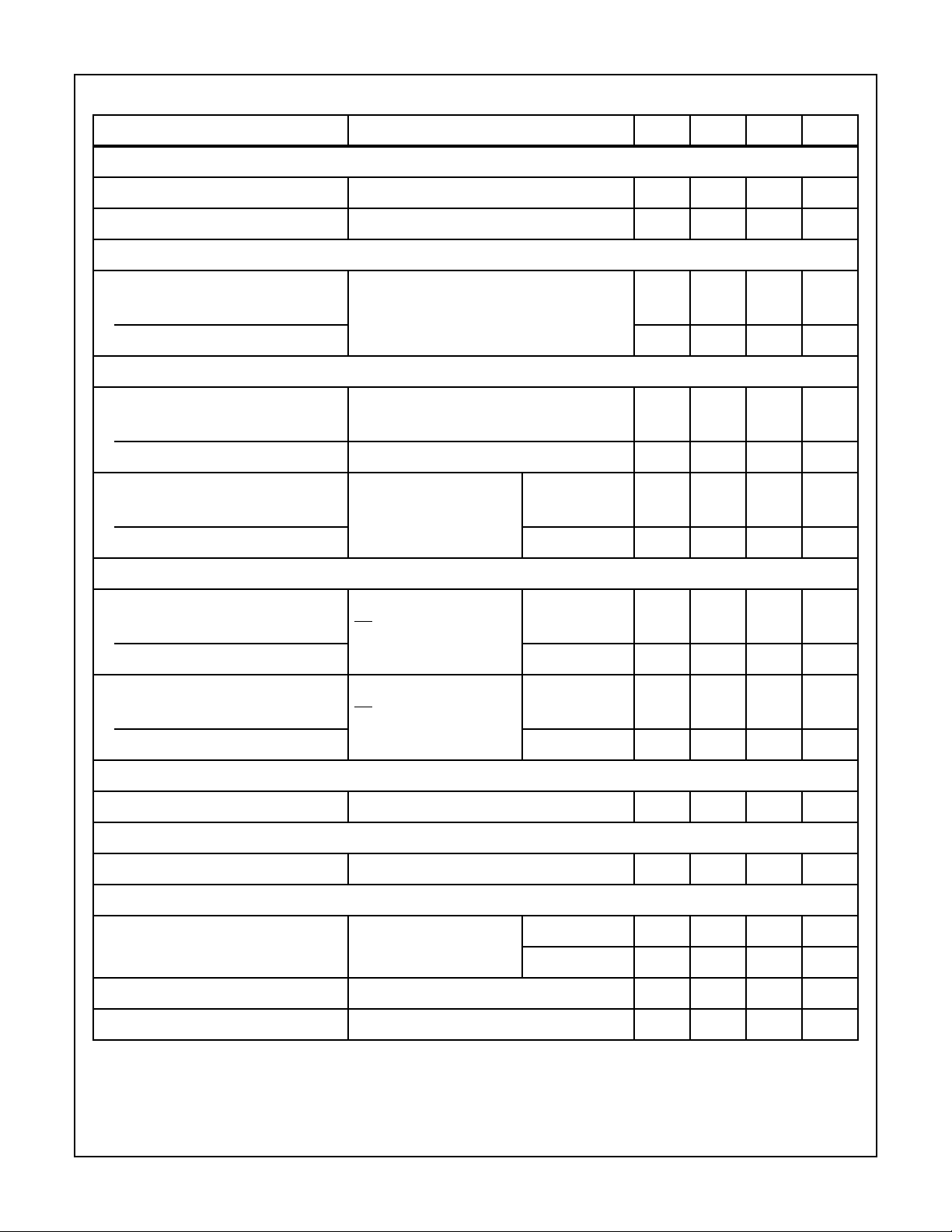

HI1176

Electrical Specifications f

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

REFERENCE INPUT

Reference Pin Current, I

Reference Resistance (VRT to VRB), R

INTERNAL VOLTAGE REFERENCES

Self Bias

V

RB

VRT - V

RB

DIGITAL INPUTS

Digital Input Voltage

V

IH

V

IL

Digital Input Current

I

IH

I

IL

REF

= 20 MSPS, VDD = +5V, VRB = 0.5V, VRT = 2.5V, TA = 25oC (Note 1) (Continued)

C

4.5 6.6 8.7 mA

REF

Short VRB and V

, Short VRT and V

RBS

RTS

230 300 450 Ω

0.48 0.52 0.56 V

1.96 2.08 2.22 V

4.0 - - V

- - 1.0 V

VDD = Max VIH = V

DD

--5µA

VIL = 0V - - 5 µA

DIGITAL OUTPUTS

Digital Output Current

I

OH

I

OL

Digital Output Current

I

OZH

I

OZL

TIMING CHARACTERISTICS

Output Data Delay, t

DL

POWER SUPPLY CHARACTERISTIC

Supply Current, I

DD

CLAMP CHARACTERISTICS

Clamp Offset Voltage, E

Clamp Pulse Width (Sync Pin Input), t

Clamp Pulse Delay, t

OC

CPW

CPD

OE = VSS, VDD = Min VOH = VDD -0.5V -1.1 - - mA

VOL = 0.4V 3.7 - - mA

OE = VDD, VDD = Max VOH = V

DD

--16µA

VOL = 0V - - 16 µA

-1830ns

fC = 20 MSPS, NTSC Ramp Wave Input - 12 18 mA

VIN = DC, PWS = 3µsV

= 0.5V 0 +20 +40 mV

REF

V

= 2.5V -50 -30 -10 mV

REF

C = 100pF, R = 130kΩ on Pin 15 1.75 2.75 3.75 µs

-25-ns

NOTE:

1. Electrical specifications guaranteed only under the stated operating conditions.

4-4

Loading...

Loading...