HI1175

August 1997

Features

• Resolution . . . . . . . . . . . . . . . . . . 8-Bit ±0.3 LSB (DNL)

• Maximum Sampling Frequency . . . . . . . . . . . 20 MSPS

• Low Power Consumption . . . .60mW (at 20 MSPS Typ)

(Reference Current Excluded)

• Built-In Sample and Hold Circuit

• Built-In Reference Voltage Self Bias Circuit

• Three-State TTL Compatible Output

• Single +5V Power Supply

• Low Input Capacitance . . . . . . . . . . . . . . . . . 11pF (Typ)

• Reference Impedance . . . . . . . . . . . . . . . . . . 300Ω (Typ)

• Evaluation Board Available (HI1175-EV)

• Low Cost

• Direct Replacement for the Sony CXD1175

Applications

• Video Digitizing • PC Video Capture

• Image Scanners • TV Set Top Boxes

• Multimedia • Personal Communication

Systems (PCS)

8-Bit, 20 MSPS, Flash A/D Converter

Description

The HI1175 is an 8-bit, analog-to-digital converter built in a

1.4µm CMOS process. The low power, low differential gain

and phase, high sampling rate, and single 5V supply make

the HI1175 ideal for video and imaging applications.

The adoption of a 2-step flash architecture achieves low

power consumption (60mW) at a maximum conversion

speed of 20 MSPS (Min), 35 MSPS typical with only a 2.5

clock cycle data latency. The HI1175 also features digital

output enable/disable and a built in voltage reference. The

HI1175 can be configured to use the internal reference or an

external reference if higher precision is required.

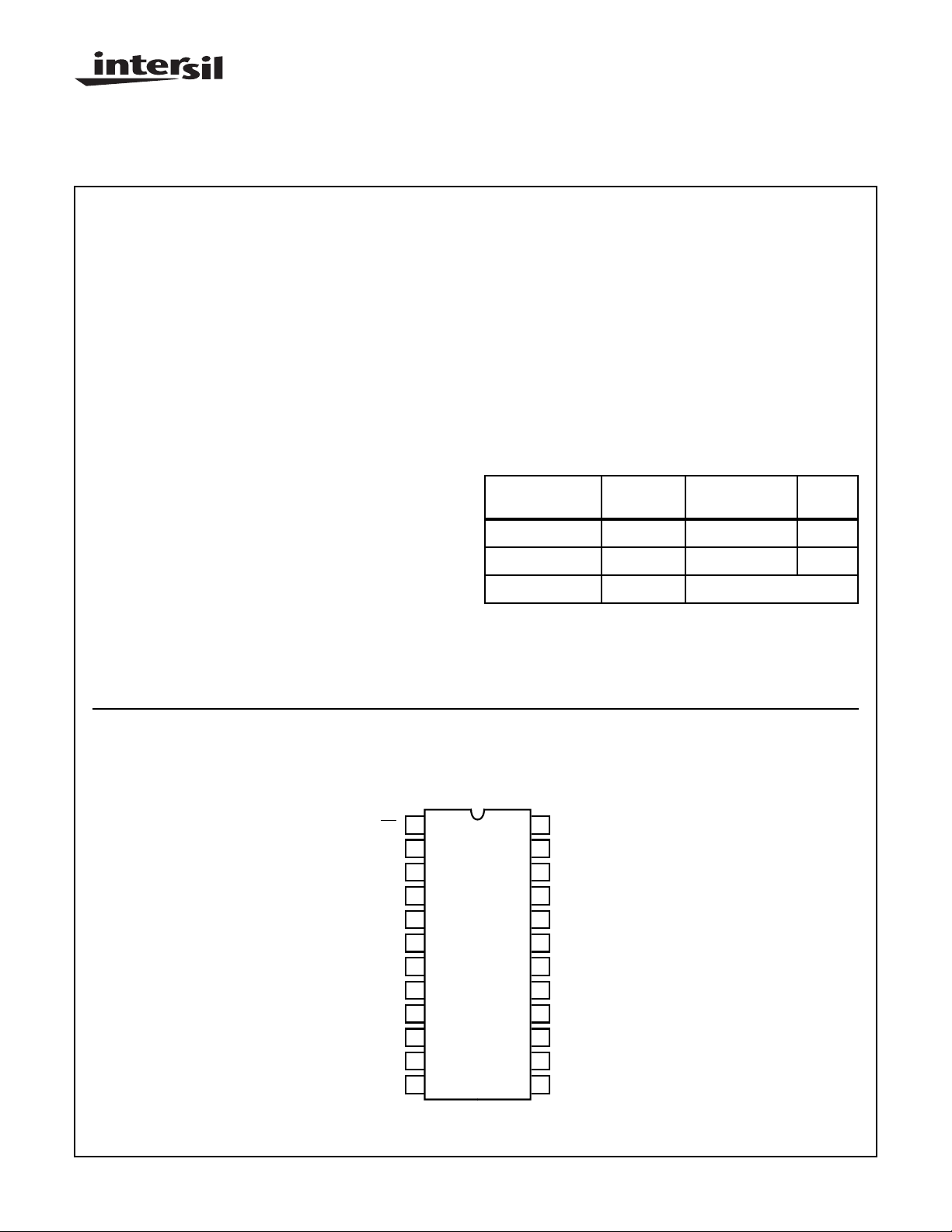

Ordering Information

TEMP.

PART NUMBER

HI1175JCP -40 to 85 24 Ld PDIP E24.4-S

HI1175JCB -40 to 85 24 Ld SOIC M24.2-S

HI1175-EV 25 Evaluation Board

RANGE (oC) PACKAGE

PKG.

NO.

Pinout

HI1175 (PDIP, SOIC)

TOP VIEW

1

OE

2

DV

SS

DV

D1

D2

D3

D4

D5

D6

DD

CLK

3

4

5

6

7

8

9

10

11

12

D0 (LSB)

D7 (MSB)

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

4-1069

24

DV

23

V

22

V

21

AV

20

AV

19

V

18

AV

17

V

16

V

15

AV

14

AV

13

DV

SS

RB

RBS

SS

SS

IN

DD

RT

RTS

DD

DD

DD

File Number 3577.6

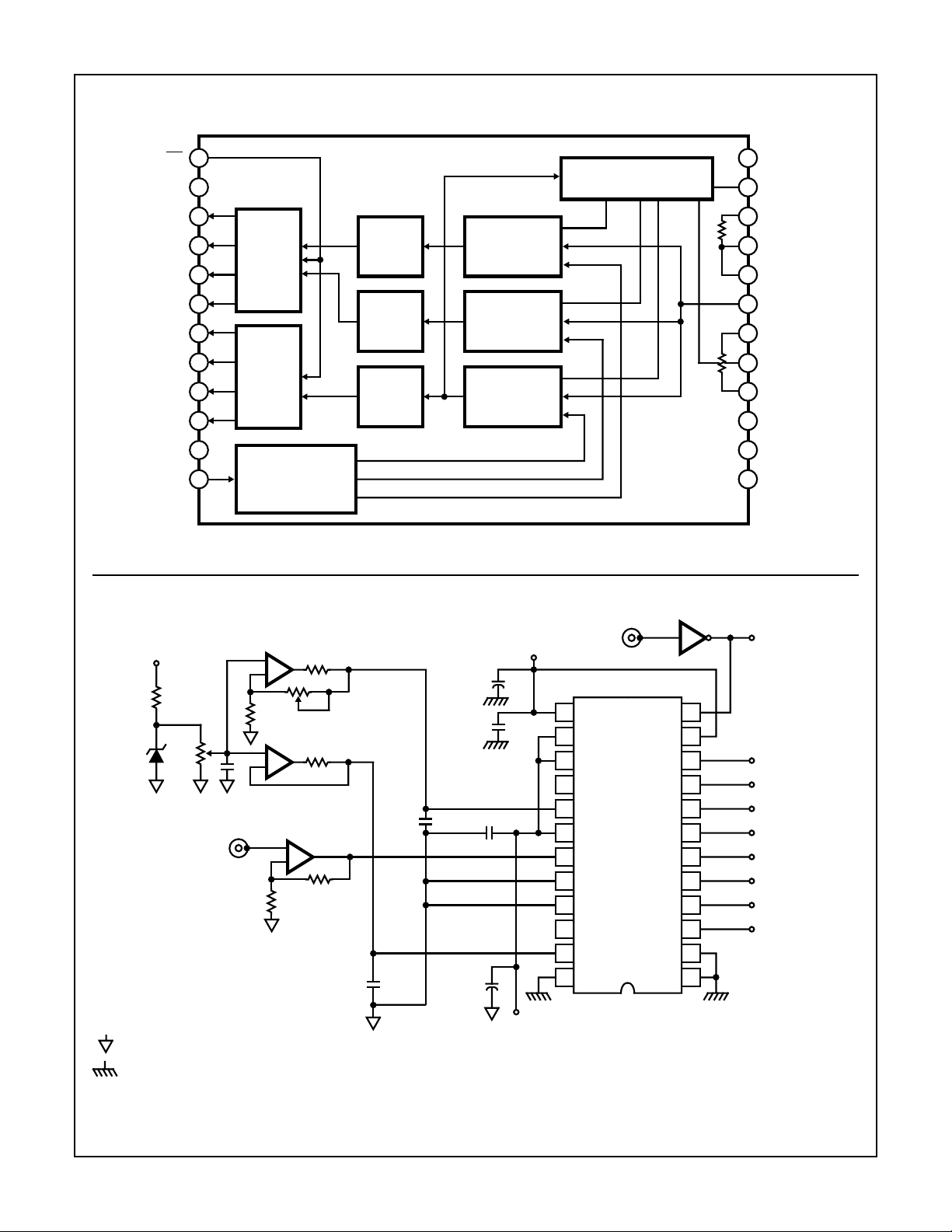

Functional Block Diagram

HI1175

1

OE

DV

2

SS

DV

CLK

D1

D2

D3

D4

D5

D6

DD

3

4

5

6

7

8

9

10

11

12

LOWER

DAT A

LATCHES

UPPER

DAT A

LATCHES

CLOCK GENERATOR

D0 (LSB)

D7 (MSB)

Typical Application Schematic

CA158A

R3

IN

R1

+

-

+

-

CA158A

R13

HA2544

+

-

R4

R5

R2

C11

0.1µF

R11

ICL8069

+5V

R12

V

LOWER

ENCODER

(4-BIT)

LOWER

ENCODER

(4-BIT)

UPPER

ENCODER

(4-BIT)

C12

0.1µF

LOWER

COMPARATORS

WITH S/H (4-BIT)

LOWER

COMPARATORS

WITH S/H (4-BIT)

UPPER

COMPARATORS

WITH S/H (4-BIT)

+

C9

4.7µF

C10

0.1µF

C8

†

+

C7

4.7µF

+5V

REFERENCE VOLTAGE

CLOCK IN

13

14

15

16

17

18

19

20

21

22

23

24

HI1175

HC04

12

11

10

9

8

7

6

5

4

3

2

1

24

DV

23

V

V

22

0.6V (Typ)

21

AV

20

AV

19

V

18

AV

V

17

V

16

2.6V (Typ)

15

AV

14

AV

DV

13

CLK

D7 (MSB)

D6

D5

D4

D3

D2

D1

D0 (LSB)

SS

RB

RBS

SS

SS

IN

DD

RT

RTS

DD

DD

DD

: Ceramic Chip Capacitor 0.1µF

†

+5V

: Analog GND

: Digital GND

NOTE: It is necessary that A VDD and DVDD pins be driven from the same supply . The gain of analog input signal can be changed by adjusting

the ratio of R2 to R1.

4-1070

HI1175

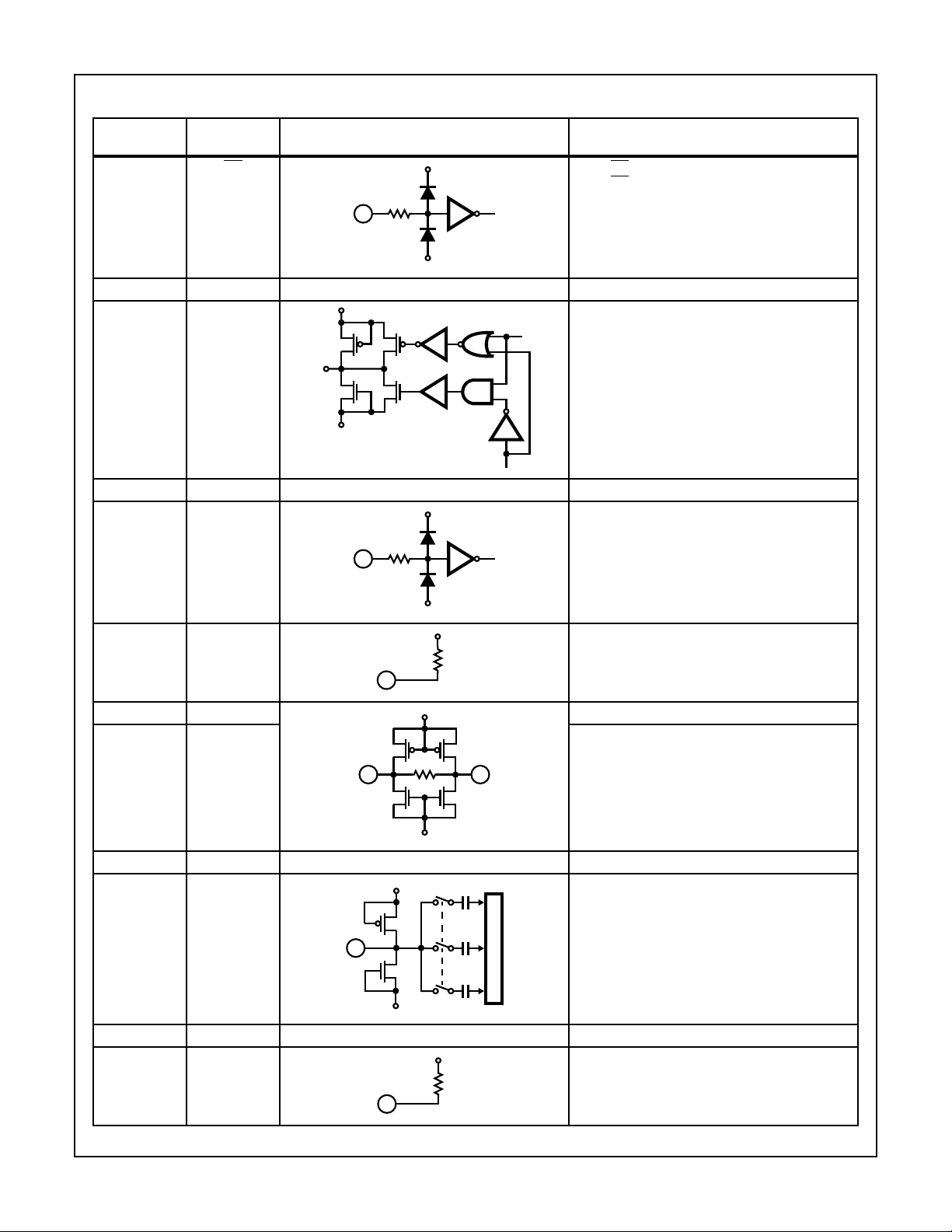

Pin Descriptions and Equivalent Circuits

PIN

NUMBER SYMBOL EQUIVALENT CIRCUIT DESCRIPTION

1 OE When OE = Low, Data is valid.

1

DV

DV

DD

SS

When OE = High, D0 to D7 pins high impedance.

2, 24 DV

SS

Digital GND.

3-10 D0 to D7 D0 (LSB) to D7 (MSB) Output.

D1

11, 13 DV

12 CLK Clock Input.

16 V

17 V

23 V

DD

RTS

RT

RB

DV

DD

12

DV

SS

AV

DD

16

AV

DD

Digital +5V.

Shorted with VRT generates, +2.6V.

Reference Voltage (Top).

Reference Voltage (Bottom).

14, 15, 18 AV

19 V

20, 21 AV

22 V

DD

IN

SS

RBS

17 23

AV

SS

AV

DD

19

AV

SS

AV

22

SS

4-1071

Analog +5V.

Analog Input.

Analog GND.

Shorted with VRB generates +0.6V.

HI1175

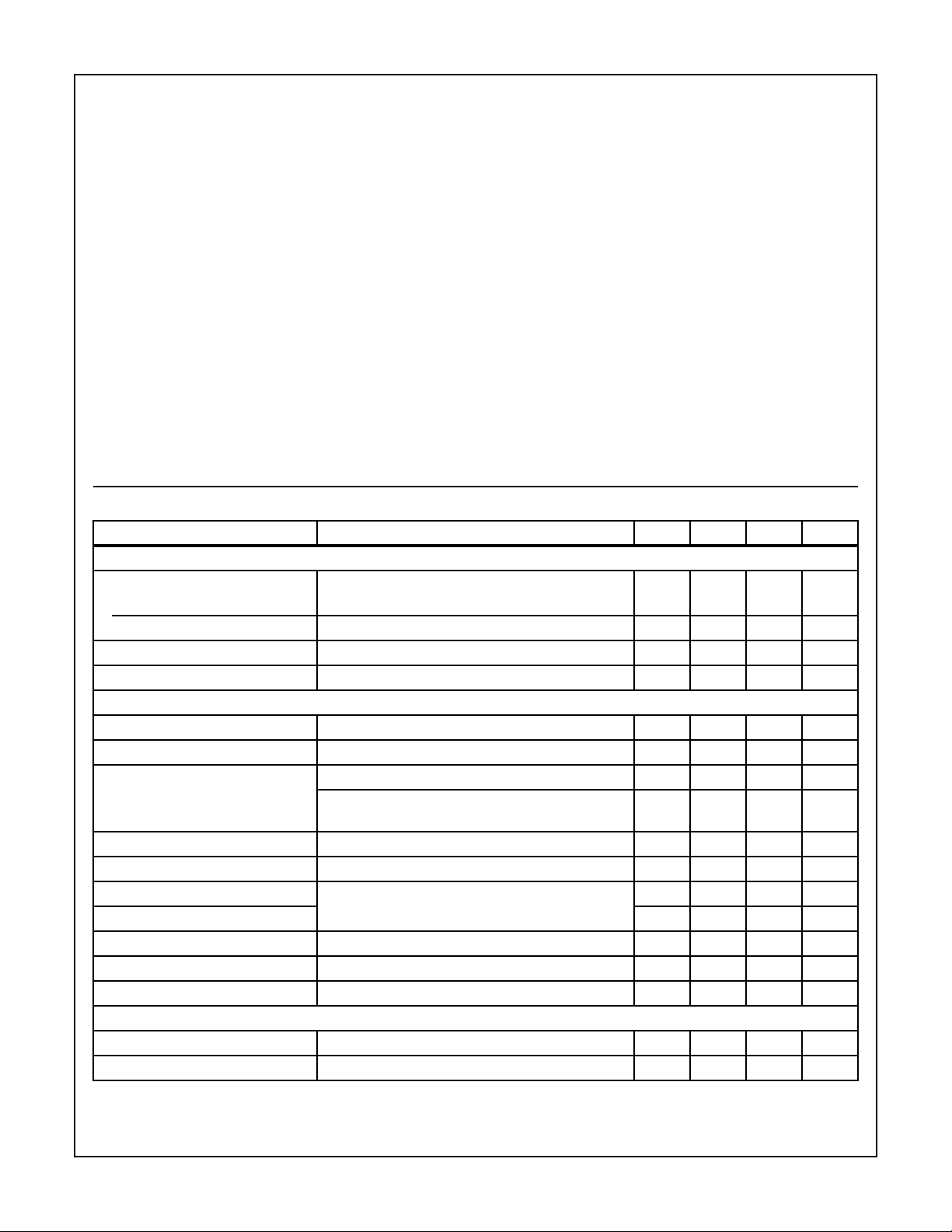

Absolute Maximum Ratings Thermal Information

Supply Voltage, VDD. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7V

Reference Voltage, VRT, VRB. . . . . . . . . . . . . . . . . . . . . VDD to V

Analog Input Voltage, VIN. . . . . . . . . . . . . . . . . . . . . . . . VDD to V

Digital Input Voltage, CLK. . . . . . . . . . . . . . . . . . . . . . . . VDD to V

Digital Output Voltage, VOH, VOL. . . . . . . . . . . . . . . . . . VDD to V

Operating Conditions (Note 1)

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

Supply Voltage

AVDD, AVSS, DVDD, DVSS . . . . . . . . . . . . . . . +4.75V to +5.25V

|DGND-AGND| . . . . . . . . . . . . . . . . . . . . . . . . . . . .0mV to 100mV

Reference Input Voltage

VRB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0V and Above

VRT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2.8V and Below

Analog Input Range, VIN . . . . . . . VRB to VRT (1.8V

Clock Pulse Width

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25ns (Min)

PW1

t

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25ns (Min)

PW0

CAUTION: Stresses above those listed in “Absolute Maxim um Ratings” ma y cause permanent damage to the device . This is a stress only rating and oper ation of

the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

P-P

to 2.8V

Thermal Resistance (Typical, Note 1) θJA (oC/W)

SS

PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

SS

SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

SS

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . 150oC

SS

Maximum Storage Temperature Range, T

. . . . .-65oC to 150oC

STG

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

)

P-P

Electrical Specifications f

= 20 MSPS, VDD = +5V, VRB = 0.5V, VRT = 2.5V, TA = 25oC (Note 1)

C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

SYSTEM PERFORMANCE

Offset Voltage

E

OT

E

OB

-60 -35 -10 mV

0 +15 +45 mV

Integral Non-Linearity, INL fC = 20 MSPS, VIN = 0.6V to 2.6V - ±0.5 ±1.3 LSB

Differential Non-Linearity, DNL fC = 20 MSPS, VIN = 0.6V to 2.6V - ±0.3 ±0.5 LSB

DYNAMIC CHARACTERISTICS

Effective Number of Bits, ENOB fIN = 1MHz - 7.6 - Bits

Spurious Free Dynamic Range fIN = 1MHz - 51 - dB

Signal to Noise Ratio, SINAD fC = 20MHz, fIN = 1MHz - 46 - dB

RMS Signal

----------------------------------------------------------------- -=

RMS Noise Distortion+

Maximum Conversion Speed, f

C

fC = 20MHz, fIN = 3.58MHz - 46 - dB

VIN = 0.6V to 2.6V, fIN = 1kHz Ramp 20 35 - MSPS

Minimum Conversion Speed - - 0.5 MSPS

Differential Gain Error, DG NTSC 40 IRE Mod Ramp, fC = 14.3 MSPS - 1.0 - %

Differential Phase Error, DP - 0.5 - Degree

Aperture Jitter, t

Sampling Delay, t

Data Latency, t

LAT

AJ

DS

-30-ps

-4-ns

- - 2.5 Cycles

ANALOG INPUTS

Analog Input Bandwidth (-1dB), BW - 18 - MHz

Analog Input Capacitance, C

IN

VIN = 1.5V + 0.07V

RMS

-11-pF

4-1072

Loading...

Loading...