Intersil Corporation HFA3783 Datasheet

TM

HFA3783

Data Sheet March 2000

I/Q Modulator/Demodulator and

Synthesizer

The HFA3783 is a highly integratedand

fully differential SiGe baseband

converter for half duplex wireless

applications. It features all the

necessary blocks for quadrature

modulation and demodulation of “I” and “Q” baseband

signals.

It has an integrated AGC receive IF amplifier with frequency

response to 600MHz. The AGC has 70dB of voltage gain

and better than 70dB of gain control range. The transmit

output also features gain control with 70dB of range.

The receive and transmit IF paths can share a common

differential matching network to reduce the filter component

count required for single IF half duplex transceivers.Apairof

2nd order antialiasing filters with an integrated DC offset

cancellation architecture is included in the receive chain for

baseband operation down to DC. In addition, an IF level

detector is included in the AGC chain for threshold

comparison. Up and down conversion are performed by

doubly balanced mixers for “I” and “Q” IF processing. These

converters are driven by a broadband quadrature LO

generator with frequency of operation phase locked by an

internal 3 wire interface synthesizer and PLL.

The device operates at low LO levels from an external VCO

with a PLL reference signal up to 50MHz. The HFA3783 is

housed in a thin 48 lead LQFP package well suited for

PCMCIA board applications.

File Number 4633.2

Features

• Integrates All IF Transmit and Receive Functions

• Broad Quadrature Frequency Range. . . . . .70 to 600MHz

• 600MHz AGC IF Strip with Level Detector. . . . . . . . .69dB

• DC Coupled Baseband Interfaces

• Integrates a Receiver DC Offset Calibration Loop

• Integrated 3 Wire Interface PLL For LO Applications

• Low LO Drive Level . . . . . . . . . . . . . . . . . . . . . . . -15dBm

• Fast Transmit-Receive Switching . . . . . . . . . . . . . . . .<1µs

• Power Management/Standby Mode

• Single Supply 2.7 to 3.3V Operation

Applications

• IEEE802.11 1 and 2Mbps Standard

• Systems Targeting IEEE 802.11 11Mbps Standard

• Wireless Local Area Networks

• PCMCIA Wireless Transceivers

• ISM Systems

• TDMA Packet Protocol Radios

Ordering Information

PART

NUMBER

HFA3783IN -40 to 85 48 Ld LQFP Q48.7x7A

HFA3783IN96 -40 to 85 Tape and Reel

TEMP. RANGE

(oC) PACKAGE PKG. NO.

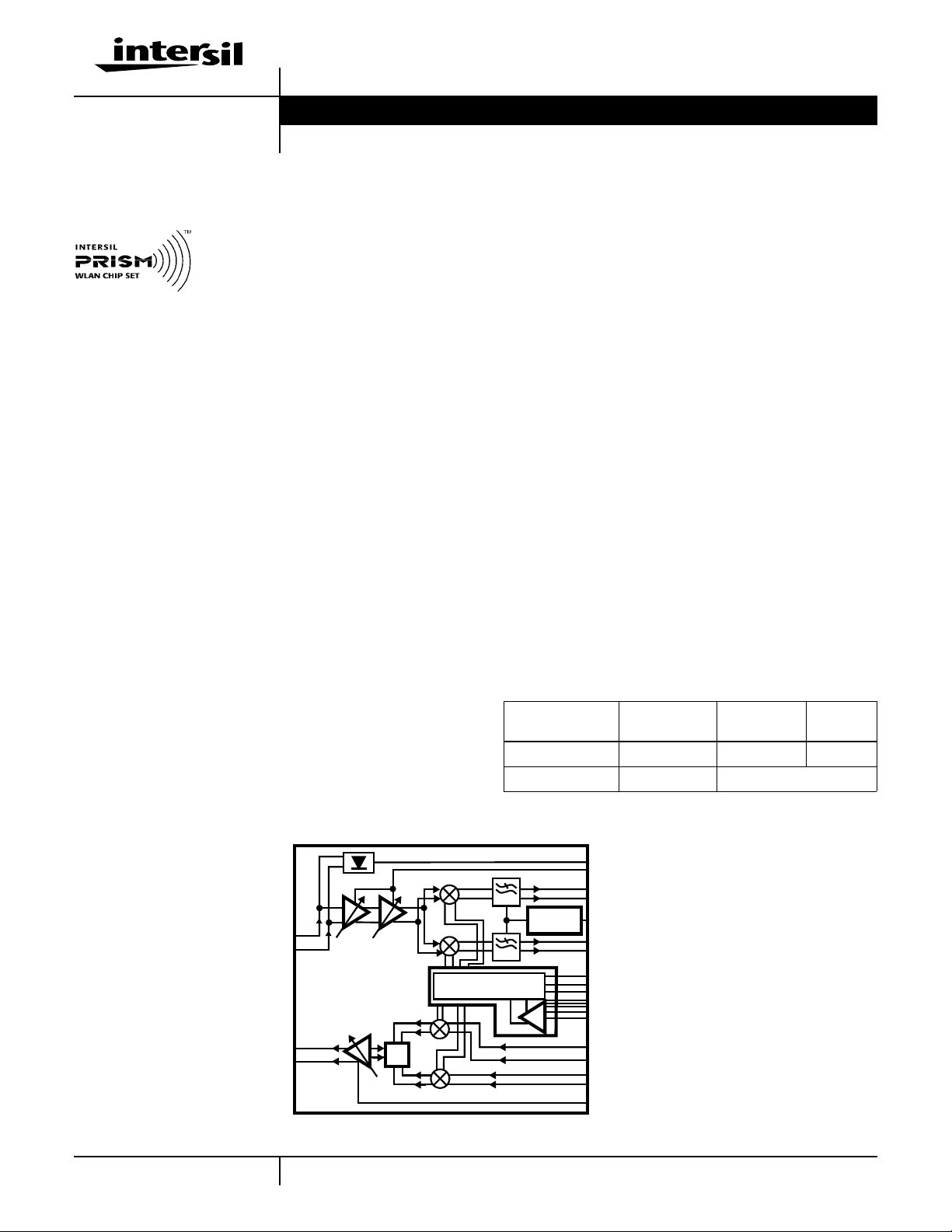

Simplified Block Diagram

IF_IN

IF_OUT

1

IF DETECTOR OUT

RECEIVE AGC

I

OFFSET

CAL

Q

0o/90oPLL MODULE

∑

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Corporation. | Copyright © Intersil Corporation 2000

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

PRISM is a registered trademark of Intersil Corporation. PRISM logo is a trademark of Intersil Corporation.

BASEBAND RXI

CAL ENABLE

BASEBAND RXQ

IF 2X LO / VCO IN

CHARGE PUMP OUT

3 WIRE INTERFACE

REF IN

BASEBAND TX I

BASEBAND TXQ

TRANSMIT IF AGC

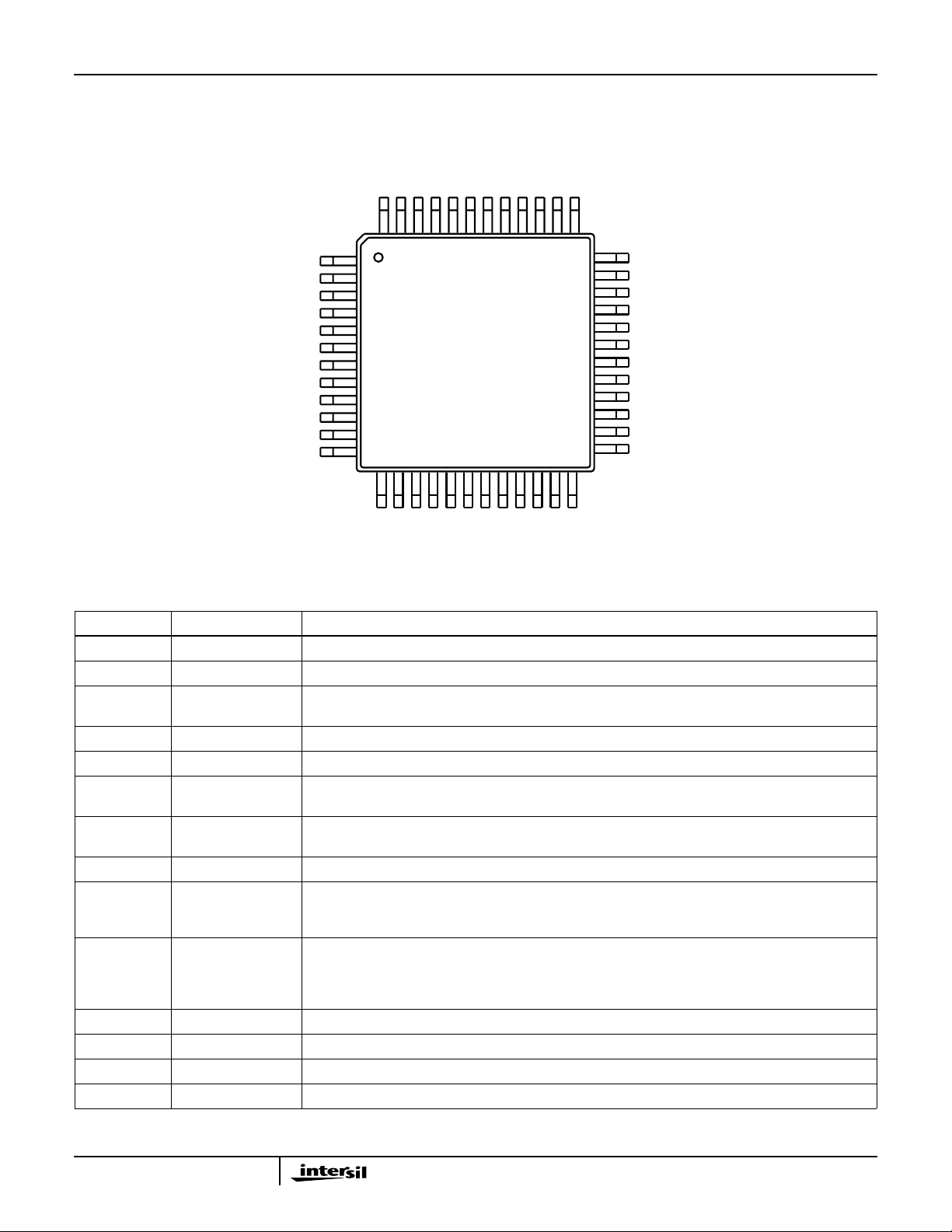

Pinout

HFA3783

CC

BB_V

DD

CP_D0

CP_V

GND

RXI+

373839404142434445464748

2423222120191817

GND

RXI-

36

35

34

33

32

31

30

29

28

27

26

25

LD

RXQ+

RXQTXI+

TXI-

1.2V_OUT

TXQ+

TXQGND

LO_V

CC

LO_IN+

LO_INGND

RX_V

CC

GND

IF_RX+

IR_RX-

GND

TX_VAGC

TX_V

CC

IF_TX+

IF_TX-

TX_V

CC

GND

GND

RX_VAGC

GND

1

2

3

4

5

6

7

8

9

10

11

12

13 14 15 16

REF_IN

REF_BYP

GND

GND

PE1

IF_DET

DD

GND

SYN_V

PE2

CLK

CAL_EN

GND

LE

DAT A

Pin Descriptions

PIN NUMBER NAME DESCRIPTION

1 RX_V

CC

3 IF_RX+ Receive AGC Differential Amplifier Non-Inverting IF Input. Requires a DC blocking capacitor.

4 IF_RX- Receive AGC Differential Amplifier Inverting IF Input. Requires a DC blocking capacitor. Pins 3 and 4 are

6 TX_VAGC Transmit AGC amplifier DC gain control input.

7 TX_V

CC

8 IF_TX+ Transmit AGC Differential Amplifier Positive Output. Open collector requiring DC bias from VCCthrough

9 IF_TX- Transmit AGC Differential Amplifier Negative Output. Open collector requiring DC bias from VCCthrough

10 TX_V

CC

13 REF_BYP PLL Reference Buffer Signal Negative Differential Input. Pin has active bias and can be used in

14 REF_IN PLLReferenceBufferSignal PositiveDifferential Input. Pin has active bias and can be used in conjunction

17 SYN_V

DD

18 CLK PLL Synthesizer Serial Interface Clock. CMOS input.

19 DATA PLL Synthesizer Serial Interface Data. CMOS input.

20 LE PLL Synthesizer Serial Interface Latch Enable Control. CMOS input.

Receive AGC Amplifier Power Supply. Requires high quality capacitor decoupling.

interchangeable and can be used single ended with the other being capacitively bypassed to ground.

Transmit AGC Amplifier Power Supply. Requires high quality capacitor decoupling.

an inductor.

an inductor.

Transmit AGC Amplifier Power Supply. Requires high quality capacitor decoupling.

conjunction with pin 14 either differential or single ended. CMOS inputs must be DC coupled. Small

sinusoidal inputs must be DC blocked with this pin bypassed to ground via a capacitor.

with pin 13 either differential or single ended. CMOS inputs must be DC coupled. Small sinusoidal inputs

must be DC blockedwith this pin used as an input for the reference signal. When used with single ended

CMOS inputs, pin 13 must be left floating. Pins 13 and 14 are interchangeable.

PLL Synthesizer Digital Power Supply. Requires high quality capacitor decoupling.

2

HFA3783

Pin Descriptions (Continued)

PIN NUMBER NAME DESCRIPTION

21 CP_V

22 CP_D0 PLL Charge Pump Current Output.

24 LD PLL Lock Detect Output. Requires low capacitive loading not to exceed 5pF.

26 LO_IN- Local Oscillator Differential Buffer Negative Input. Requires AC coupling. For single ended applications

27 LO_IN+ Local Oscillator Differential Buffer Positive Input. Requires AC coupling. For single ended applications its

28 LO_V

30 TXQ- Baseband Quadrature Differential Inputs for IF Transmission. DC coupled requiring 1.3V common mode

31 TXQ+

32 1.2V_OUT Highly Regulated Band Gap 1.2V Buffered Output. Used in conjunction with ADCs and DACsfor voltage

33 TXI- Baseband In Phase Differential Inputs for IF Transmission. DC coupled requiring 1.3V common mode

34 TXI+

35 RXQ- Baseband Quadrature Differential Outputs FromIF Demodulation. DC coupled output with 1.2V common

36 RXQ+

37 RXI- Baseband In Phase Differential Outputs From IF Demodulation. DC coupled output with 1.2V common

38 RXI+

40 BB_V

42 CAL_EN CMOS Input forActivation Of Internal DC Offset Adjust Circuit for the Receive Baseband Outputs. A rising

43 PE2 Power Enable Control Pins: Please refer to the POWER ENABLE TRUTH TABLE in the Electrical

44 PE1

45 IF_DET IF Detector Current Output. A current source of 175µA typical is generated at this pin when the IF AGC

47 RX_VAGC Receive AGC amplifier DC gain control input.

2, 5, 11, 12, 15,

16, 23, 25, 29,

39, 41, 46, 48

DD

CC

CC

GND Grounds. Connect to a solid ground plane.

PLL Charge Pump Power Supply. Independent supply for the charge pump, not to exceed3.6V.Requires

high quality capacitor decoupling.

its complementary input, Pin 27, must be bypassed to ground via a capacitor.

complementary input, Pin 26, must be bypassed to ground via a capacitor. Pins 26 and 27 are

interchangeable.

NOTE: High second harmonic content LO waveforms may degrade I/Q phase accuracy.

Local Oscillator Buffer Amplifier Power Supply. Requires high quality capacitor decoupling.

bias voltages.

/temperature tracking. Requires high quality 0.1µF capacitor decoupling to ground.

bias voltages.

mode DC outputs. AC coupling pins 35, 36, 37 and 38 requires programmable register activation for DC

hold during TX to RX switching.

mode DC outputs.

Baseband Receive LPF Output and Offset Control Power Supply. Requires high quality capacitor

decoupling.

edge activates the calibration cycle, which completes within a programmable time and holds the

calibration while this pin is held high. In applications where the synthesizer is not used, this pin needs to

be grounded.

Specifications section.

receive differential or single ended signal at pins 3 and 4 is between 100 and 200mVPP.

3

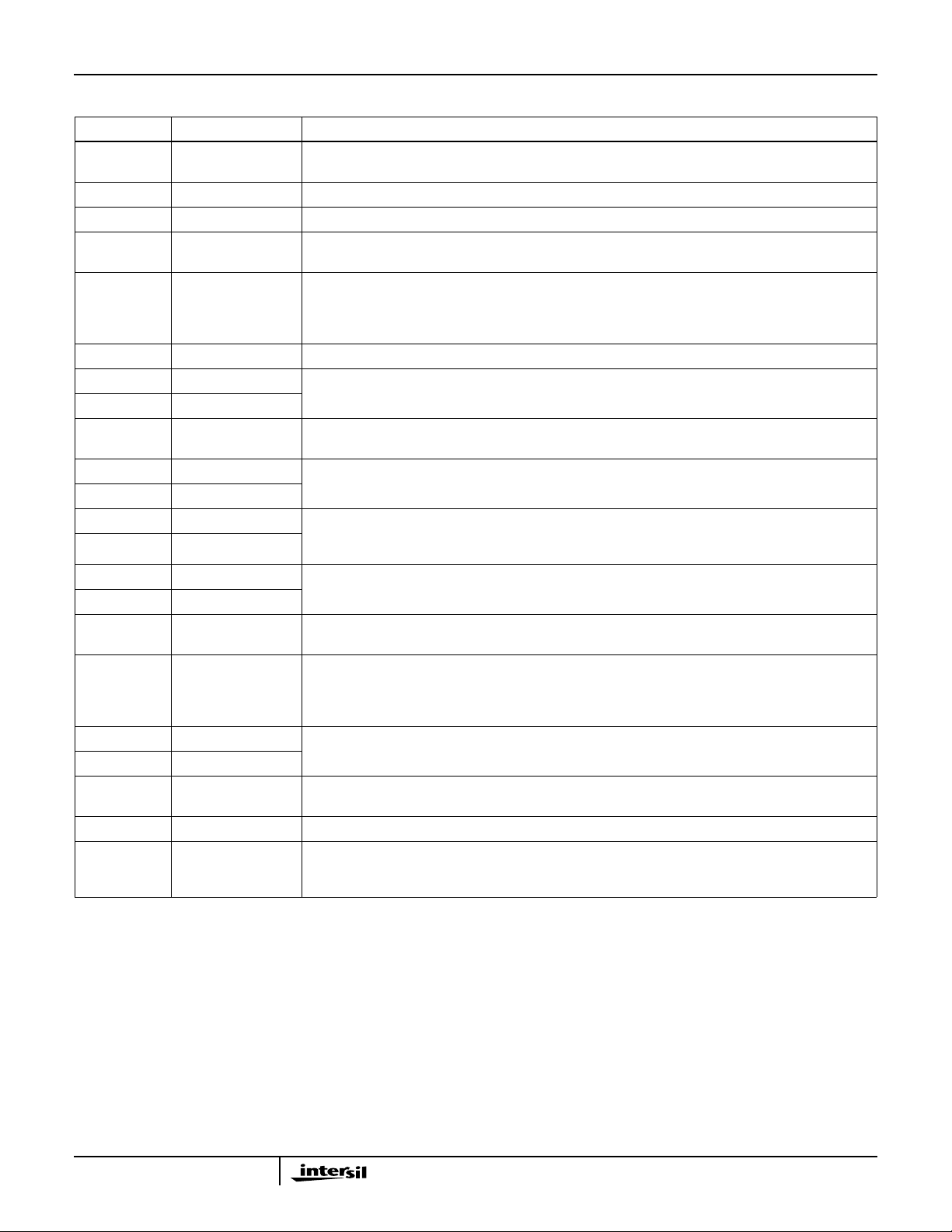

Application Circuit

HFA3783

SAW

SAWTEK

855653L1

V

CC

C

S

C

S

L

P

1000p

10µ

100p

2K

100p

L

P

1000p

0.01

1000p

0.01

100p

1000p

48

1

2

3

4

5

6

7

8

9

10

11

12

13

49.9

TX_VAGC

619

RX_VAGC

976

IF_DET

FROM MAC (CAL+ EN CTRL)

RX”I”

RX”Q”

0.01

2.87K

68p

47

46

44 43 42 41

45

LO

Σ

SYNTH

14

15

16

17

0.1

0/90

18

19

20

37383940

212223 24

0.1

36

35

34

33

32

31

30

29

28

27

26

25

0.022

56p

100p

100p

3.92K

0.22

2K

56

0.1

0.1

VT

3900pF

RF

VCO

PANASONIC

ENFV25F80

68p

536

536

124

TX”I”

124

124

TX”Q”

124

IDAC

7 BITS

IDAC

7 BITS

1-BIT

DET

ADC

6 BITS

ADC

6 BITS

DAC

6 BITS

1.2V REF IN

DAC

6 BITS

HFA3861

(SINUSOIDAL)

4

REF FREQ

FROM MAC (PLL CTRL)

VCO_V

10µ0.1

CC

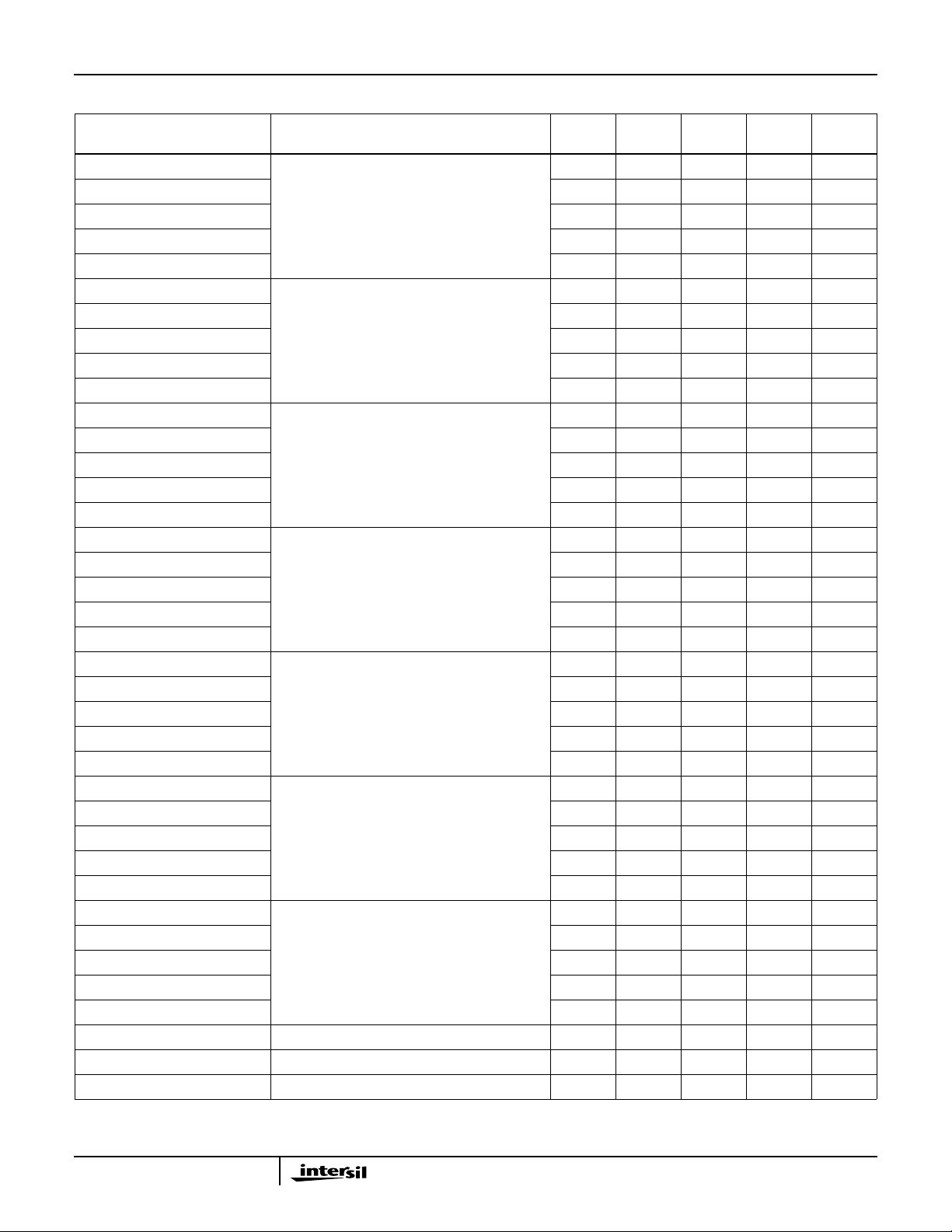

Test Diagram

FREQUENCY RESPONSE TEST SET UP

SWEEP

GEN.

50

V

CC

200p

50

ANALYZER

1000p

1000p

50

50

2

3

4

5

6

7

8

9

V

CC

10µ

IF_DET

RX_VAGC

.01

2.87K

PE1

PE2

HFA3783

CALIBRATION

RXI

CAL_EN

5KΩ INPUT

CALIBRATION

RXQ

.01

TX_VAGC

1000p

IF IN/OUT

TC4-1W

MATCH COMPONENTS FOR

TEST FIXTURE (374MHz)

AND TRANSFORMER

8p

8p

1000p

27n

100p

27n

100p

2K

.01

270p

1000p

1000p

100p

47

48

1

2

3

4

5

6

7

8

9

10

11

12

13

14

50

REF_IN

(SINUSOIDAL)

46

15

.1

270p

44 43 42 41

45

SYNTH

16

17

5KΩ INPUT

37383940

36

35

34

1.2V REF.

33

32

LO

∑

0/90

18

19

20

212223 24

VCC/2

LE

CLK

DAT A

31

30

29

28

27

26

25

.1

CP

.1

56p

100p

100p

BUFFER

.1

50

LO_IN (2X FREQ)

(LOW INPUT CAPACITANCE)

CALIBRATION

TXQ

1.2V_OUT

COMMON MODE VOLTAGE

CALIBRATION

TXI

COMMON MODE VOLTAGE

5

HFA3783

Absolute Maximum Ratings Thermal Information

Voltage on Any Other Pin. . . . . . . . . . . . . . . . . . . -0.3 to VCC+0.3V

VCC to VCC Decouple or Gnd to Gnd . . . . . . . . . . . . . -0.3 to +0.3V

Any Pin to Gnd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4.0V

Operating Conditions

Operating Temperature Range . . . . . . . . . . . . . . . . . . -40 to +85oC

Supply Voltage Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.7-3.3V

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJAis measured with the component mounted on an evaluation PC board in free air.

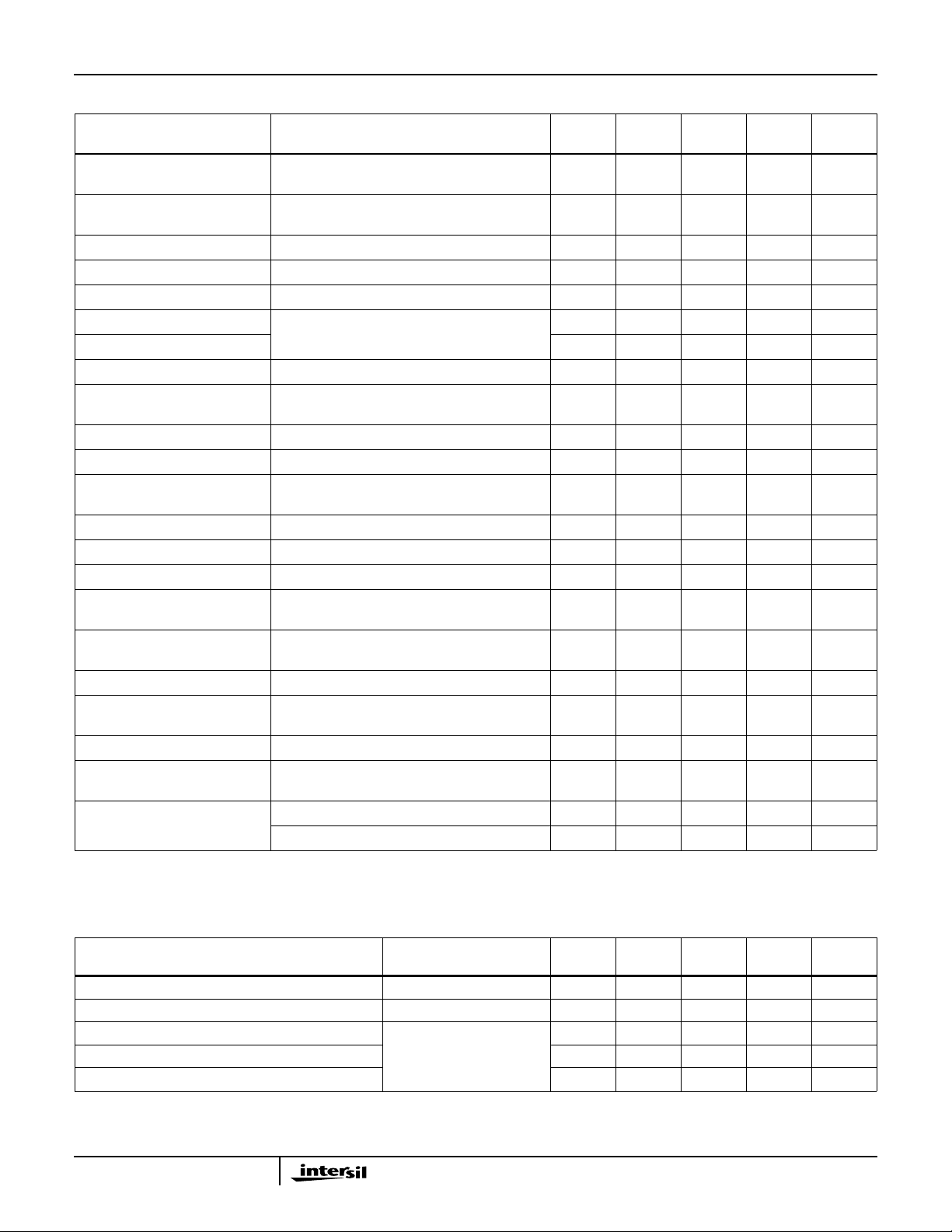

DC Electrical Specifications

PARAMETER

Supply Voltage Full 2.7 - 3.3 V

Receive Total Supply Current 25 - 36 40 mA

Transmit Total Supply Current 25 - 32 40 mA

Voltage Reference Output at ±1mA, 0.1µF Load Full 1.14 1.2 1.26 V

NOTE: TX/RX Power Down Supply Current (PLL Serial Interf. Active) (Note 2) Full - - 100 µA

TX/RX/Power Down Speed (Note 3) Full - - 10 µs

RX/TX, TX/RX Switching Speed (Note 3) Full - - 1 µs

CMOS Low Level Input Voltage Full -0.3 - 0.3*V

CMOS High Level Input Voltage (VDD = 3.6V) Full 0.7*V

CMOS Threshold Voltage Full - 0.5*V

CMOS High or Low Level Input Current Full -3.0 - +3.0 µA

NOTE:

2. Standby current is measured after a long elapsed time (20 seconds).

3. TX/RX/TX switching speed and power Down/Up speed are dependent on external components.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

LQFP Package. . . . . . . . . . . . . . . . . . . 70 N/A

Maximum Junction Temperature (Plastic Package) . . . . . . . . . . 150

Maximum Storage Temperature Range. . . . . . . . . . . . . . .-65 to 150

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . . .300

Moisture Sensitivity Level (Intersil Tech. Brief TB363). . . . . .168 Hrs

TEMP.

(oC) MIN TYP MAX UNITS

V

DD

DD

- 3.6 V

DD

-V

Receive Cascaded AC Electrical Specification IF = 375MHz, LO = 748MHz, V

PARAMETER TEST CONDITIONS

IF Frequency Range Test Diagram Full 70 - 600 MHz

2XLO Frequency Range Test Diagram Full 140 - 1200 MHz

Maximum Power Gain VAGC = 0V 25 56 61 dB

Voltage Gain Nominal High Gain. Differential 250Ω in, 5kΩ

Power Gain Full - 56 - dB

Cascaded Noise Figure Full - - 8 dB

Output IP3 Full +2.2 - - dBm

Output P1dB Full -14.1 - - dBm

output differential load.

AGC Control voltage set to 69dB of voltage gain

= 2.7V, Unless Otherwise Specified

CC

TEMP.

(oC) MIN TYP MAX UNITS

Full - 69 - dB

6

HFA3783

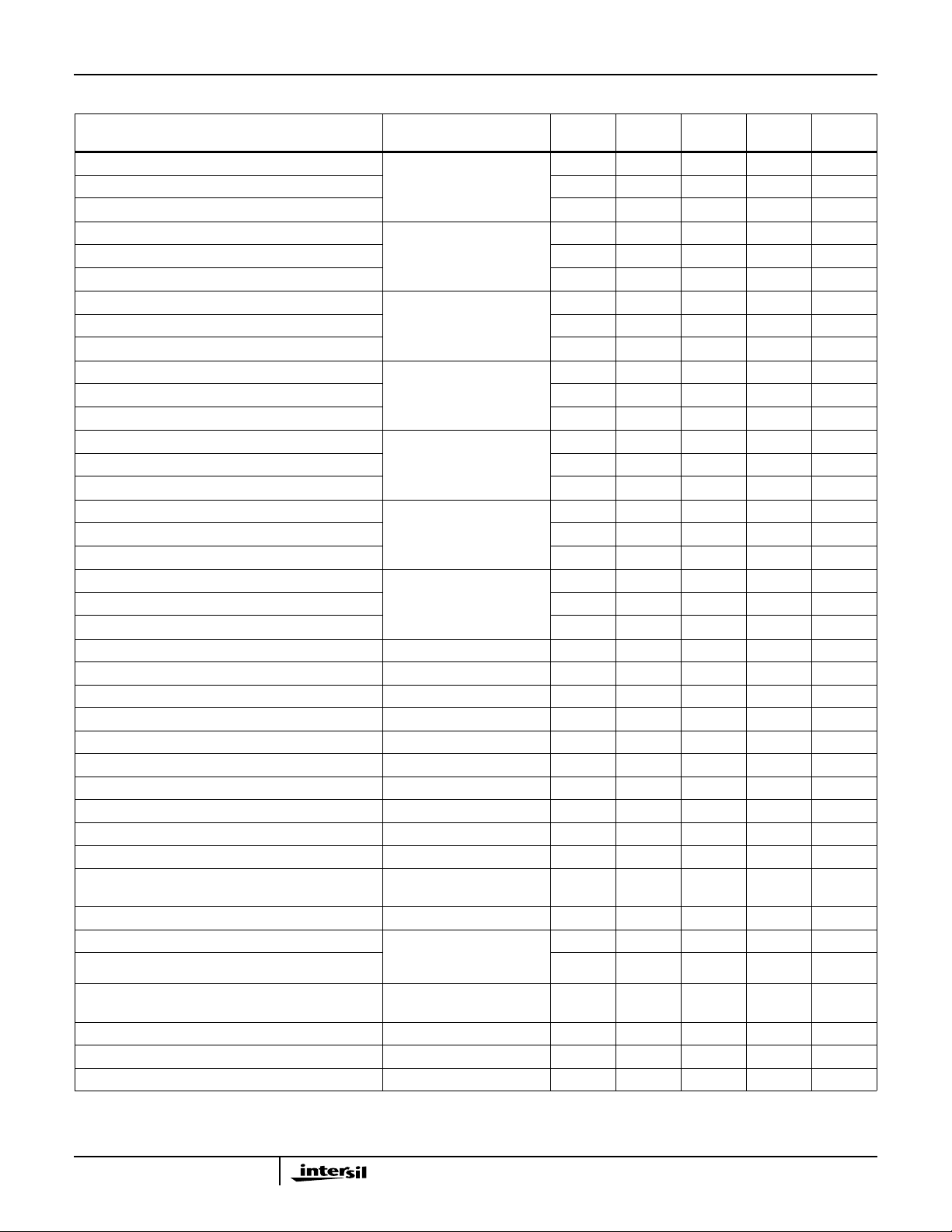

Receive Cascaded AC Electrical Specification IF = 375MHz, LO = 748MHz, V

PARAMETER TEST CONDITIONS

Voltage Gain AGC Control Voltage set to 10dB attenuation.

Power Gain Full - 46 - dB

Cascaded Noise Figure Full - - 11 dB

Output IP3 Full +1.5 - - dBm

Output P1dB Full -14.3 - - dBm

Voltage Gain AGC Control Voltage set to 20dB attenuation.

Power Gain Full - 36 - dB

Cascaded Noise Figure Full - 14.1 - dB

Output IP3 Full +1.0 - - dBm

Output P1dB Full -14.4 - - dBm

Voltage Gain AGC Control Voltage set to 30dB attenuation.

Power Gain Full - 26 - dB

Cascaded Noise Figure Full - 19.9 - dB

Output IP3 Full +0.3 - - dBm

Output P1dB Full -14.6 - - dBm

Voltage Gain AGC Control Voltage set to 40dB attenuation.

Power Gain Full - 16 - dB

Cascaded Noise Figure Full - 27 - dB

Output IP3 Full -1.4 .74 2.8 dBm

Output P1dB Full -15.0 - - dBm

Voltage Gain AGC Control Voltage set to 50dB attenuation.

Power Gain Full - 6 - dB

Cascaded Noise Figure Full - 35.1 - dB

Output IP3 0-85 -2.0 - - dBm

Output P1dB 0-85 -15.5 - - dBm

Voltage Gain AGC Control Voltage set to 60dB attenuation.

Power Gain Full - -4 - dB

Cascaded Noise Figure Full - 43.9 - dB

Output IP3 0-85 -3.3 - - dBm

Output P1dB 0-85 -16.1 - - dBm

Voltage Gain AGC Control Voltage set to 72dB attenuation.

Power Gain Full - -16 - dB

Cascaded Noise Figure Full - 60.0 - dB

Output IP3 0-85 -6.7 - - dBm

Output P1dB 0-85 -18.2 - - dBm

Minimum Power Gain VAGC = 2.25V 25 - - -17 dB

AGC Gain Control Voltage Full 0.2 - 2.25 V

AGC Gain Control Sensitivity Over Supply Range Full - 61.6 - dB/V

Differential 250Ω input, differential 5kΩ output

load.

Differential 250Ω input, differential 5kΩ output

load.

Differential 250Ω input, differential 5kΩ output

load.

Differential 250Ω input, differential 5kΩ output

load.

Differential 250Ω input, differential 5kΩ output

load.

Differential 250Ω input, differential 5kΩ output

load.

Differential 250Ω input, differential 5kΩ output

load.

= 2.7V, Unless Otherwise Specified (Continued)

CC

TEMP.

(oC) MIN TYP MAX UNITS

Full - 59 - dB

Full - 49 - dB

Full - 39 - dB

Full - 29 - dB

Full - 19 - dB

Full - 9 - dB

Full - -3 - dB

7

HFA3783

Receive Cascaded AC Electrical Specification IF = 375MHz, LO = 748MHz, V

PARAMETER TEST CONDITIONS

AGC Gain Control Input

Impedance

Gain Switching Speed to ±1dB

Settling

Insertion Phase vs AGC Full AGC Range 25 -2 ±0.3 +2 deg/dB

IF Detector Response Time 10pF, 2.9K External Load Full - 0.15 0.25 µs

IF Detector Input Voltage 0.5V, 175µA Into 2.87K Out Full 100 150 200 mV

LO Internal Input Resistance Single End. 748MHz 25 950 - 1.1K Ω

LO Internal Input Capacitance 25 - 0.96 - pF

LO Drive Level External 50Ω Match Network (single resistor) Full -15 -10 0 dBm

Upper Baseband 3dB Bandwidth

(2nd Order)

Lower Baseband 3dB Bandwidth DC Coupled Load Full DC - - I and Q 3dB BW Matching Full -2 - +2 %

Cascaded Receive I or Q

Baseband THD

Cascaded Receive I/Q Crosstalk 25 - - -40 dB

I/Q Amplitude Balance 100kHz CW Full -1 - +1 dB

I/Q Phase Balance 100kHz CW Full -2 - +2 deg

Cascaded I or Q Baseband

Differential Offset Voltage

Cascaded I or Q Common Mode

Voltage at Baseband

Offset Calibration Time Ref = 44MHz, Offset Counter C = 25 Full - 25 - µs

Offset Counter Divide Ratio

(C Counter)

CAL_EN Minimum Pulse Width High to Low to High Transition Time Full 0 - - nS

Baseband Output Resistance

Loading

Baseband Output Capacitance

Loading

NOTE:

4. A positive frequency offset from the carrier produces I leading Q by 90 degrees.

Full AGC Scale Full - 0.4 1 µs

1MHz, 1VPP Diff. for First 50dB of Attenuation

Range

AfterCalibration Cycle. Measured witha setting of

26dB of power gain

Input Ref Clock is Divided by C*2 for SAR Offset

Correction

Differential. 1/2 value for ground reference loads Full - 5 - kΩ

Single End, Each Full - - 10 pF

Differential Full - - 10 pF

= 2.7V, Unless Otherwise Specified (Continued)

CC

TEMP.

(oC) MIN TYP MAX UNITS

Full 20 23 - kΩ

Full 6.7 7.4 8.5 MHz

25 - - 1 %

Full - - 10 mV

Full 1.08 1.17 1.32 V

Full 1 - 127 -

PP

T ransmit Cascaded AC Electrical Specifications LO = 748MHz, V

PARAMETER TEST CONDITIONS

IF Frequency Range Test Diagram Full 70 - 600 MHz

2 X LO Frequency Range Test Diagram Full 140 - 1200 MHz

Output Power at 250Ω Differential Load AGC Voltage Set to -10dBm

Output Noise Floor Full - -141 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Output Power for 0.35V

Sine I and Q

Inputs

= 2.7V, VCM = 1.24V Unless Otherwise Specified

CC

TEMP.

(oC) MIN TYP MAX UNITS

Full - -10 - dBm

PP

8

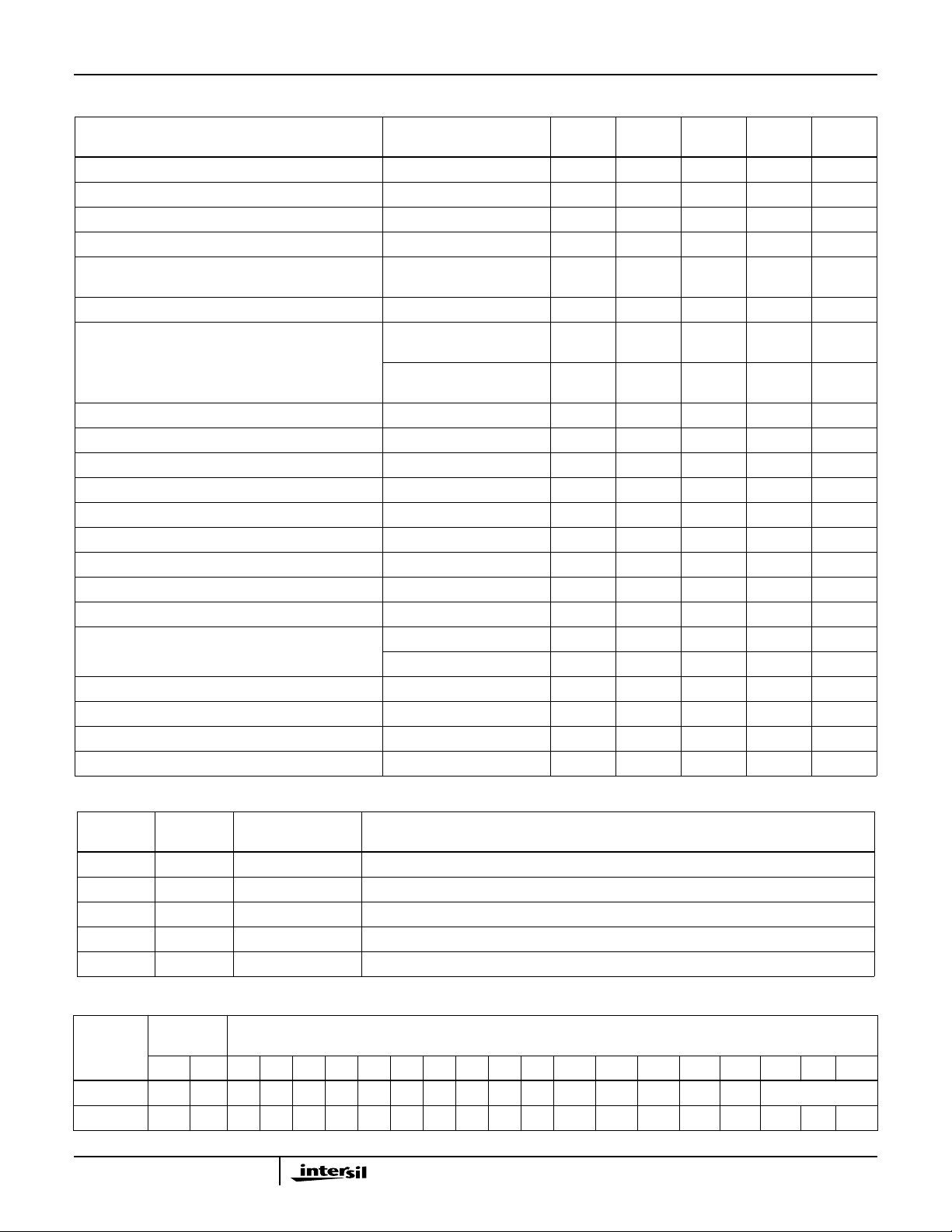

HFA3783

T ransmit Cascaded AC Electrical Specifications LO = 748MHz, V

= 2.7V, VCM = 1.24V Unless Otherwise Specified (Continued)

CC

TEMP.

PARAMETER TEST CONDITIONS

Output Power at 250Ω Differential Load AGC Voltage Set to 10dB

Output Noise Floor Full - -149 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Attenuation.

0.35VPP Sine I and Q

Inputs

Output Power at 250Ω Differential Load AGC Voltage Set to 20dB

Output Noise Floor Full - -157 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Attenuation.

0.35V

Sine I and Q

PP

Inputs

Output Power at 250Ω Differential Load AGC Voltage Set to 30dB

Output Noise Floor Full - -161 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Attenuation.

0.35V

Sine I and Q

PP

Inputs

Output Power at 250Ω Differential Load AGC Voltage Set to 40dB

Output Noise Floor Full - -162 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Attenuation.

0.35V

Sine I and Q

PP

Inputs

Output Power at 250Ω Differential Load AGC Voltage Set to 50dB

Output Noise Floor Full - -163 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Attenuation.

0.35V

Sine I and Q

PP

Inputs

Output Power at 250Ω Differential Load AGC Voltage Set to 60dB

Output Noise Floor Full - -164 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Attenuation.

0.35V

Sine I and Q

PP

Inputs

Output Power at 250Ω Differential Load AGC Voltage Set to 70dB

Output Noise Floor Full - -164 - dBm/Hz

P1dB/Output Power Ratio Full 10 - - dB

Attenuation.

0.35V

Sine I and Q

PP

Inputs

(oC) MIN TYP MAX UNITS

Full - -20 - dBm

Full - -30 - dBm

Full - -40 - dBm

Full - -50 - dBm

Full - -60 - dBm

Full - -70 - dBm

Full - -80 - dBm

AGC Gain Control Voltage Full 0.1 - 2.25 V

AGC Gain Control Sensitivity Supply Range 25 - 35.4 - dB/V

AGC Control Input Impedance Full 20 21 - kΩ

Gain Switching Speed to ±1% Settling Full Scale 25 - 0.8 4 µs

Insertion Phase vs AGC 50dB Range from Max Full - - 4.0 deg

I/Q Baseband Bandwidth Application Circuit Full 0 13 - MHz

Cascaded Baseband to IF TX THD 1MHz, 0.5V

PP

25 - - 0.5 %

Amplitude Balance DC Inputs 25 -0.5 - +0.5 dB

Phase Balance DC Inputs 25 -2 - +2 deg

Carrier Suppression Full AGC Range 25 - -43 -30 dBc

SSB Sideband Suppression (Note 5) 100kHz Inputs, Full AGC

25 - -43 -32 dBc

Range

Optimum IF Output Differential Impedance Shared with RX 25 - 250 - Ω

LO Internal Input Resistance Single End

LO Internal Input Capacitance 25 - 0.96 - pF

Across F. Range

Same as RX Section

LO Drive Level External 50Ω Match

25 950 - 1.1K Ω

Full -15 -10 0 dBm

Network (single resistor)

Baseband Differential Input Impedance Full 100 150 - kΩ

Optimum Baseband Differential Input Voltage Shaped Pulses Full - 0.5 - V

PP

Common Mode Baseband Input Voltage Range All TX Inputs Full 1.2 1.30 1.40 V

NOTE:

5. I leading Q produces a+jw CCW rotation and a positive frequency offset from the carrier.

9

HFA3783

Phase Lock Loop Electrical Specifications

TEMP.

PARAMETER TEST CONDITIONS

Operating 2X LO Frequency Test Diagram Full 140 - 1200 MHz

Reference Oscillator Frequency Test Diagram Full - - 50 MHz

Selectable Prescaler Ratios (2 Settings) Full 16/17 N/A 32/33 Swallow Counter Divide Ratio (A Counter) Full 0 - 127 Programmable Counter Divide Ratio

(B Counter)

Reference Counter Divide Ratio (R Counter) Full 3 - 32767 Reference Oscillator Sensitivity Single or Differential Sine

Inputs

CMOS Single or

Complementary

Reference Oscillator Duty Cycle CMOS Inputs Full 40 - 60 %

Charge Pump Sink/Source Current/Tolerance 250µA Selection +/- 25% Full 0.18 0.25 0.32 mA

Charge Pump Sink/Source Current/Tolerance 500µA Selection +/- 25% Full 0.375 0.5 0.625 mA

Charge Pump Sink/Source Current/Tolerance 750µA Selection +/- 25% Full 0.56 0.75 0.94 mA

Charge Pump Sink/Source Current/Tolerance 1mA Selection +/- 25% Full 0.75 1.0 1.25 mA

Charge Pump Sink/Source Mismatch Full - - 15 %

Charge Pump Output Compliance Full 0.5 - CPVDD-0.5 V

Charge Pump High Z leakage High Z state Full -10 ±0.1 10 µA

Charge Pump Supply Voltage Full 2.7 - 3.6 V

Serial Interface Clock Width High Level Full 20 - - ns

Low level Full 20 - - ns

Serial Interface Data/Clk Set-Up Time Full 20 - - ns

Serial Interface Data/Clk Hold Time Full 10 - - ns

Serial Interface Clk/LE Set-Up Time Full 20 - - ns

Serial Interface LE Pulse Width Full 20 - - ns

(oC) MIN TYP MAX UNITS

Full 3 - 2047 -

Full 0.5 - - V

Full - CMOS - -

PP

POWER ENABLE TRUTH TABLE

PLL_PE

PE1 PE2

0 0 1 Power Down State, PLL Registers in Save Mode, Inactive PLL, Active Serial Interface

1 1 1 Receive State, Active PLL

1 0 1 Transmit State, Active PLL

0 1 1 Inactive Transmit and Receive States, Active PLL, Active Serial Interface

X X 0 Inactive PLL, Disabled PLL Registers, Active Serial Interface

(SERIAL BUS) STATUS

PLL Synthesizer and DC Offset Clock Programming Table

REGISTER

SERIAL

BITS

R Counter 0 0 R(0) R(1) R(2) R(3) R(4) R(5) R(6) R(7) R(8) R(9) R(10) R(11) R(12) R(13) R(14) X (Don’t Care)

A/B Counter 0 1 A(0) A(1) A(2) A(3) A(4) A(5) A(6) B(0) B(1) B(2) B(3) B(4) B(5) B(6) B(7) B(8) B(9) B(10)

DEFINITION

LSB 1 2 345678910111213 14 1516171819MSB

10

HFA3783

PLL Synthesizer and DC Offset Clock Programming Table (Continued)

REGISTER

SERIAL

BITS

Operational

Mode

Offset

Calibration

NOTES:

6. The Serial data is clocked on the Rising Edge of the serial clock, MSB first. The serial Interface is active when LE is LOW. The serial Data is

latched into defined registers on the rising edge of LE.

7. The M register or Operational Mode needs to be loaded first. Registers R, A/B and Offset Calibration follow M loading in any sequence.

Reference Frequency Counter/Divider

R(0-14) Least significant bit R(0) to most significant bit R(14) of the divide by R counter. The Reference signal frequency is divided down

LO Frequency Counters/Dividers

A(0-6) Least significant bit A(0) to most significant bit A(6) of a 7-bit Swallow counter and LSB B(0) to MSB B(10) of the 11 bits divider.

B(0-10)

DEFINITION

LSB 1 2 345678910111213 14 1516171819MSB

1 0 M(0) 0 M(2) M(3) M(4) M(5) M(6) M(7) M(8) 0 0 0 0 M(13) M(14) M(15) X X

1 1 C(0) C(1) C(2) C(3) C(4) C(5) C(6) 0 0 0 0 C(11) X (Don’t Care)

BIT DESCRIPTION

by this counter and is compared with a divided LO by a phase detector.

BIT DESCRIPTION

The LO frequency is divided down by [P*B+A], where P is the prescaler divider set by bit M(2). This divided signal frequency is

compared by a phase detector with the divided Reference signal.

Operational Modes

BIT DESCRIPTION

M(0) (PLL_PE), Phase Lock Loop Power Enable. 1 = Enable, 0 = Power Down. Serial port always on.

M(2) Prescaler Select. 0 = 16/17, 1 = 32/33

M(3)

M(4)

M(5)

M(6)

M(7)

M(8)

M(13)

M(14)

M(15)

Charge Pump Current Setting. M(4) M(3) OUTPUT SINK/SOURCE

0 0 0.25mA

0 1 0.50mA

1 0 0.75mA

1 1 1.00mA

Charge Pump Sign. M(6) M(5)

0 0 Source Current if LO/ [P*B+A] < Ref/R

0 1 Source Current if LO/ [P*B+A] > Ref/R

LD Pin Multiplex Operation. M(13) M(8) M(7) OUTPUT AT PIN LD

0 0 X Lock Detect Operation

0 1 X Short to GND

1 0 X Serial Register Read Back

1 1 0 Ref. Divided by R Waveform

1 1 1 LO Divided by [P*B+A]

Charge Pump Operation/Test. M(15) M(14) OPERATION/TEST

0 0 Normal Operation

0 1 Charge Pump Constant Current Source

1 0 Charge Pump Constant Current Sink

1 1 High Impedance State

Waveform

11

Loading...

Loading...