HD-4702

March 1997

Features

• HD-4702 Provides 13 Commonly Used Bit Rates

• Uses a 2.4576MHz Crystal/Input for Standard

Frequency Output (16 Times Bit Rate)

• Low Power Dissipation

• Conforms to EIA RS-404

• One HD-4702 Controls up to Eight Transmission

Channels

• Initialization Circuit Facilitates Diagnostic Fault

Isolation

• On-Chip Input Pull-Up Circuit

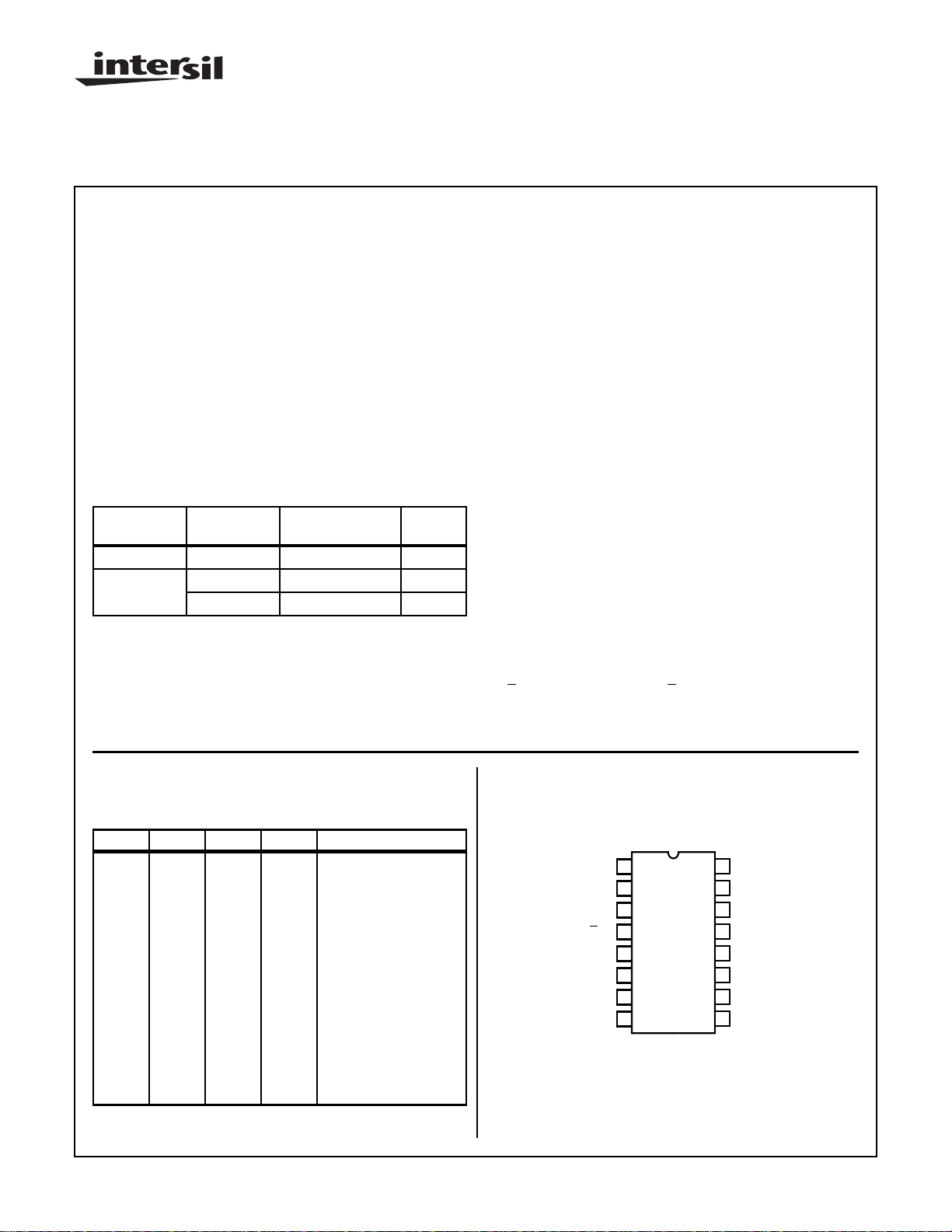

Ordering Information

TEMP.

PACKAGE

PDIP -40 to +85 HD3-4702-9 E16.3

CERDIP -40 to +85 HD1-4702-9 F16.3

SMD# -55 to +125 5962-9051801MEA F16.3

RANGE (oC) PART NUMBER PKG. NO.

CMOS Programmable Bit Rate Generator

Description

The HD-4702 Bit Rate Generator provides the necessary clock

signals for digital data transmission systems, such as a UART. It

generates 13 commonly used bit rates using an on-chip crystal

oscillator or an external input. For conventional operation generating 16 output clock pulses per bit period, the input clock frequency must be 2.4576MHz (i.e. 9600 Baud x 16 x 16, since

there is an internal ÷ 16 prescaler). A lower input frequency will

result in a proportionally lower output frequency.

The HD-4702 can provide multi-channel operation with a minimum of external logic by having the clock frequency CO and the

÷ 8 prescaler outputs Q0, Q1, Q2 available externally. All signals

have a 50% duty cycle except 1800 Baud, which has less than

0.39% distortion.

The four rate select inputs (S0-S3) select which bit rate is at the

output (Z). See Truth Table for Rate Select Inputs for select code

and output bit rate. Two of the 16 select codes for the HD-4702 do

not select an internally generated frequency, but select an input

into which the user can feed either a different frequency, or a static

level (High or Low) to gener ate “ZERO BAUD”.

The bit rates most commonly used in modern data terminals

(110, 150, 300, 1200, 2400 Baud) require that no more than one

input be grounded for the HD-4702, which is easily achieved with

a single 5-position switch.

The HD-4702 has an initialization circuit which generates a master reset for the scan counter. This signal is derived from a digital

differentiator that senses the first high level on the CP input after

ECP input goes low. When ECP is high, selecting the crystal

the

input, CP must be low. A high level on CP would apply a continuous reset. See Clock Modes and Initialization below .

Truth Table Pinout

TRUTH TABLE FOR RATE SELECT INPUTS

(Using 2.4576MHz Crystal)

S3 S2 S1 S0 OUTPUT RATE (Z)

L

L

L

L

L

L

L

L

H

H

H

H

H

H

H

H

NOTE: 19200 Baud by connecting Q2 to IM.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

L

L

L

L

H

H

H

H

L

L

L

L

H

H

H

H

L

L

H

H

L

L

H

H

L

L

H

H

L

L

H

H

L

MUX Input (IM)

H

MUX Input (IM)

L

50 Baud

H

75 Baud

L

134.5 Baud

H

200 Baud

L

600 Baud

H

2400 Baud

L

9600 Baud

H

4800 Baud

L

1800 Baud

H

1200 Baud

L

2400 Baud

H

300 Baud

L

150 Baud

H

110 Baud

| Copyright © Intersil Corporation 1999

5-1

HD-4702 (CERDIP, PDIP)

TOP VIEW

1

Q0

2

Q1

3

Q2

4

E

CP

5

CP

6

O

X

I

7

X

8

GND

16

V

CC

15

I

M

14

S0

13

S1

12

S2

S3

11

10

Z

9

CO

File Number 2954.1

HD-4702

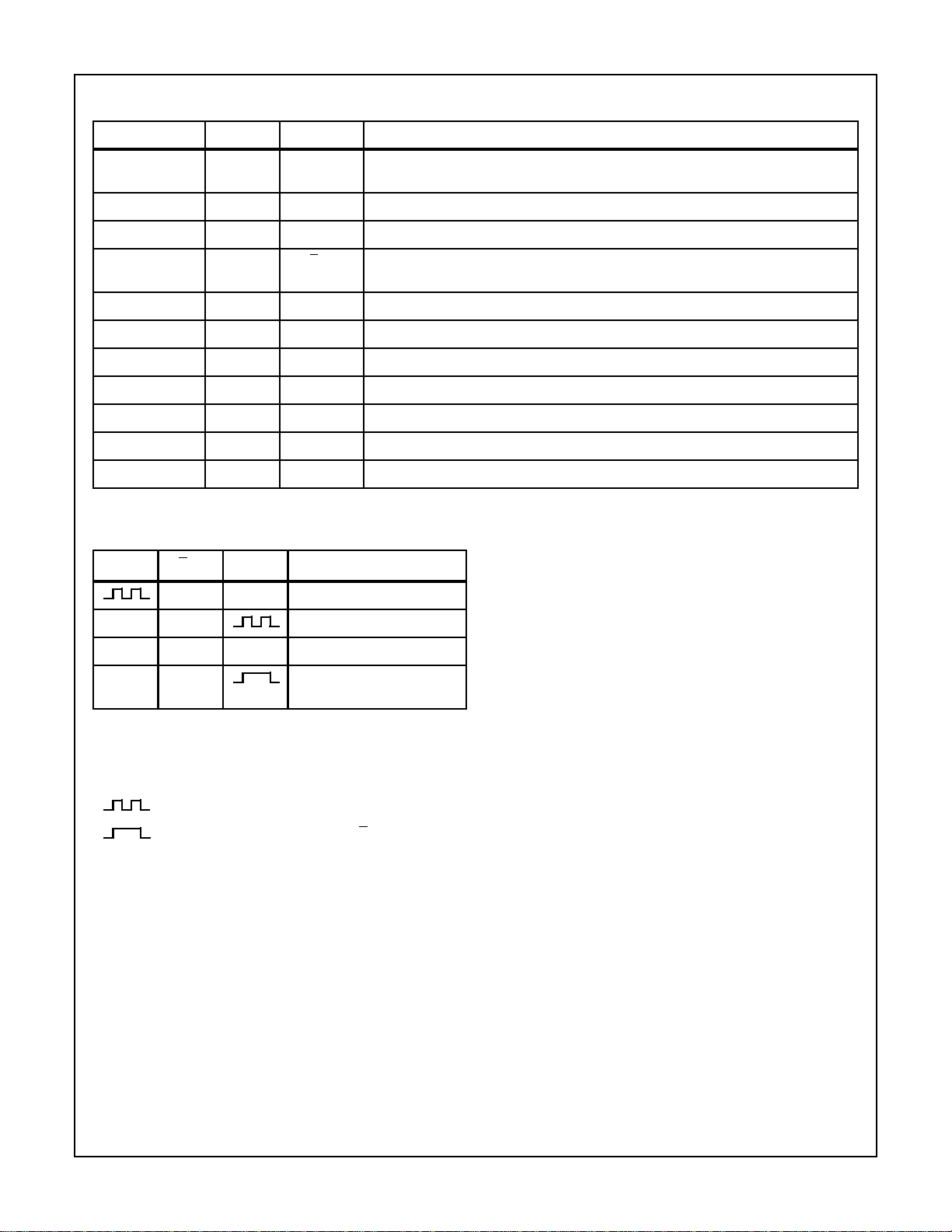

Pin Description

PIN NUMBER TYPE SYMBOL DESCRIPTION

16 V

8 GND GROUND

5 I CP EXTERNAL CLOCK INPUT

4IE

7II

6OO

15 I I

11, 12, 13, 14 I S0 - S3 BAUD RATE SELECT INPUTS

9 O CO CLOCK OUTPUT

1, 2, 3 O Q0 - Q

10 O Z BIT RATE OUTPUT

CLOCK MODES AND INITIALIZATION

IX E

X L Clocked from CP

CP

H L Clocked from I

CP OPERATION

CC

CP

X

X

M

VCC: Is the +5V power supply pin. A 0.1µF capacitor between pins 16 and 8 is

recommended for decoupling.

EXTERNAL CLOCK ENABLE: A low signal on this input allows the baud rate to be

generated from the CP input.

CRYSTAL INPUT

CRYSTAL DRIVE OUTPUT

MULTIPLEXED INPUT

SCAN COUNTER OUTPUTS

2

X

X H H Continuous Reset

X L Reset During 1st CP = High

Time

H = HIGH Level

L = LOW Level

X = Don’t Care

= Clock Pulse

= 1st HIGH Level Clock Pulse after ECP goes LOW

NOTE: Actual output frequency is 16 times the indicated Output

Rate, assuming a clock frequency of 2.4576MHz.

5-2

Block Diagram

5-3

MULTIPLEXER

14 13 12 11

15

I

S0 S1 S2 S3

M

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

50

75

134.5

200

600

2400

9600

4800

1800

1200

2400

300

150

110

DQ

FF

CP

MR

10

Z

HD-4702

CIRCUIT

OSCILLATOR

CIRCUIT

DQ

FF

CP Q

MR

MR

CO

9

SCAN

COUNTER

CP 8

÷

MR

Q0Q1Q

1 2 3

COUNTER NETWORK

CP

MR

9600

4800

2400

1200

600

300

150

75

CP 4÷Q

CP 18÷Q

CP 6÷Q

CP 16/3÷Q

2

CP 22÷Q

MR

MR

MR

MR

MR

(NOTE)

I

7

X

O

6

X

E

CP

4

5

CP

INITIALIZATION

=

PIN 16V

DD

V

PIN 8

=

SS

=

PIN NUMBER

NOTE: See Figure 4 in Design Information for Crystal Specifications.

Loading...

Loading...