Intersil Corporation HD-15531-883 Datasheet

HD-15531/883

March 1997

Features

• This Circuit is Processed in Accordance to MIL-STD883 and is Fully Conformant Under the Provisions of

Paragraph 1.2.1.

• Support of MIL-STD-1553

• Data Rate (15531B) . . . . . . . . . . . . . . . 2.5 Megabit/Sec

• Data Rate (15531). . . . . . . . . . . . . . . . 1.25 Megabit/Sec

• Variable Frame Length to 32-Bits

• Sync Identification and Lock-In

• Separate Manchester II Encode, Decode

• Low Operating Power . . . . . . . . . . . . . . . . .50mW at 5V

CMOS Manchester Encoder-Decoder

Description

The Intersil HD-15531/883 is a high performance CMOS

device intended to service the requirements of MIL-STD1553 and similar Manchester II encoded, time division multiplexed serial data protocols. This LSI chip is divided into two

sections, an Encoder and a Decoder. These sections operate independently of each other, except for the master reset

and word length functions. This circuit provides many of the

requirements of MIL-STD-1553. The Encoder produces the

sync pulse and the parity bit as well as the encoding of the

data bits. The Decoder recognizes the sync pulse and identifies it as well as decoding the data bits and checking parity.

The HD-15531/883 also surpasses the requirements of MILSTD-1553 by allowing the word length to be programmable

(from 2 to 28 data bits). A frame consists of three bits for

sync followed b y the data word (2 to 28 data bits) followed by

one bit of parity, thus, the frame length will vary from 6 to 32

bit periods. This chip also allows selection of either even or

odd parity for the Encoder and Decoder separately.

This integrated circuit is fully guaranteed to support the

1MHz data rate of MIL-STD-1553 over both temperature and

voltage. For high speed applications the 15531B will support

a 2.5 Megabit/sec data rate.

The HD-15531/883 can also be used in many party line digital data communications applications, such as a local area

network or an environmental control system driven from a

single twisted pair or fiber optic cable throughout a building.

Ordering Information

PACKAGE TEMPERATURE RANGE 1.25MBIT/SEC 2.5MBIT/SEC PKG. NO.

CERDIP -55oC to +125oC HD1-15531/883 HD1-15531B/883 F40.6

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

5-170

File Number 2962.1

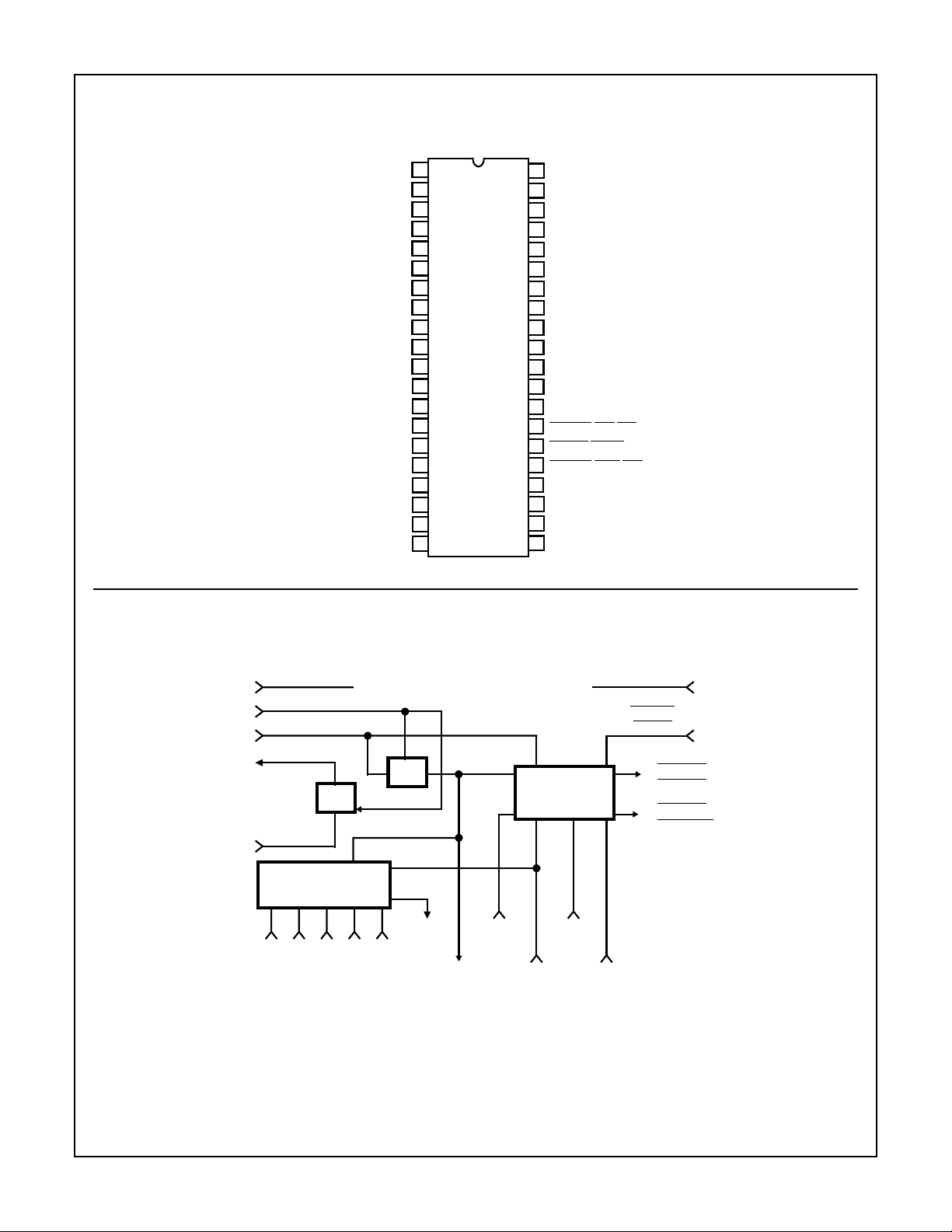

Pinout

VCC

VALID WORD

TAKE DATA’

TAKE DATA

SERIAL DATA OUT

SYNCHR DATA

SYNCHR DATA SEL

SYNCHR CLK

DECODER CLK

SYNCHR CLK SEL

BIPOLAR ZERO IN

BIPOLAR ONE IN

UNIPOLAR DATA IN

DECODER SHIFT CLK

TRANSITION SEL

NC

COMMAND SYNC

DECODER PARITY SEL

DECODER RESET

COUNT C0

HD-15531/883

HD-15531/883 (CERDIP)

TOP VIEW

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

COUNT C1

COUNT C4

DATA SYNC

ENCODER CLK

COUNT C3

NC

ENCODER SHIFT CLK

SEND CLK IN

SEND DATA

ENCODER PARITY SEL

SYNC SEL

ENCODER ENABLE

SERIAL DATA IN

BIPOLAR ONE OUT

OUTPUT INHIBIT

BIPOLAR ZERO OUT

÷ 6 OUT

COUNT 2

MASTER RESET

GND

Block Diagrams

GND

21

MASTER RESET

22

SEND CLK IN

33

6 OUT

24

ENCODER

37

CLK

BIT

COUNTER

20 40 23 36 39

C0C1C2C3C

÷ 6

ENCODER

V

CC

1

OUTPUT

INHIBIT

ENCODER

PARITY

SELECT

27

25

÷ 2

CHARACTER

FORMER

34 28 29 31

32

SEND

DAT A

4

ENCODER

SHIFT

CLK

SERIAL

DATA IN

ENCODER

ENABLE

30

SYNC

SELECT

26

BIPOLAR

ONE OUT

BIPOLAR

ZERO OUT

5-171

HD-15531/883

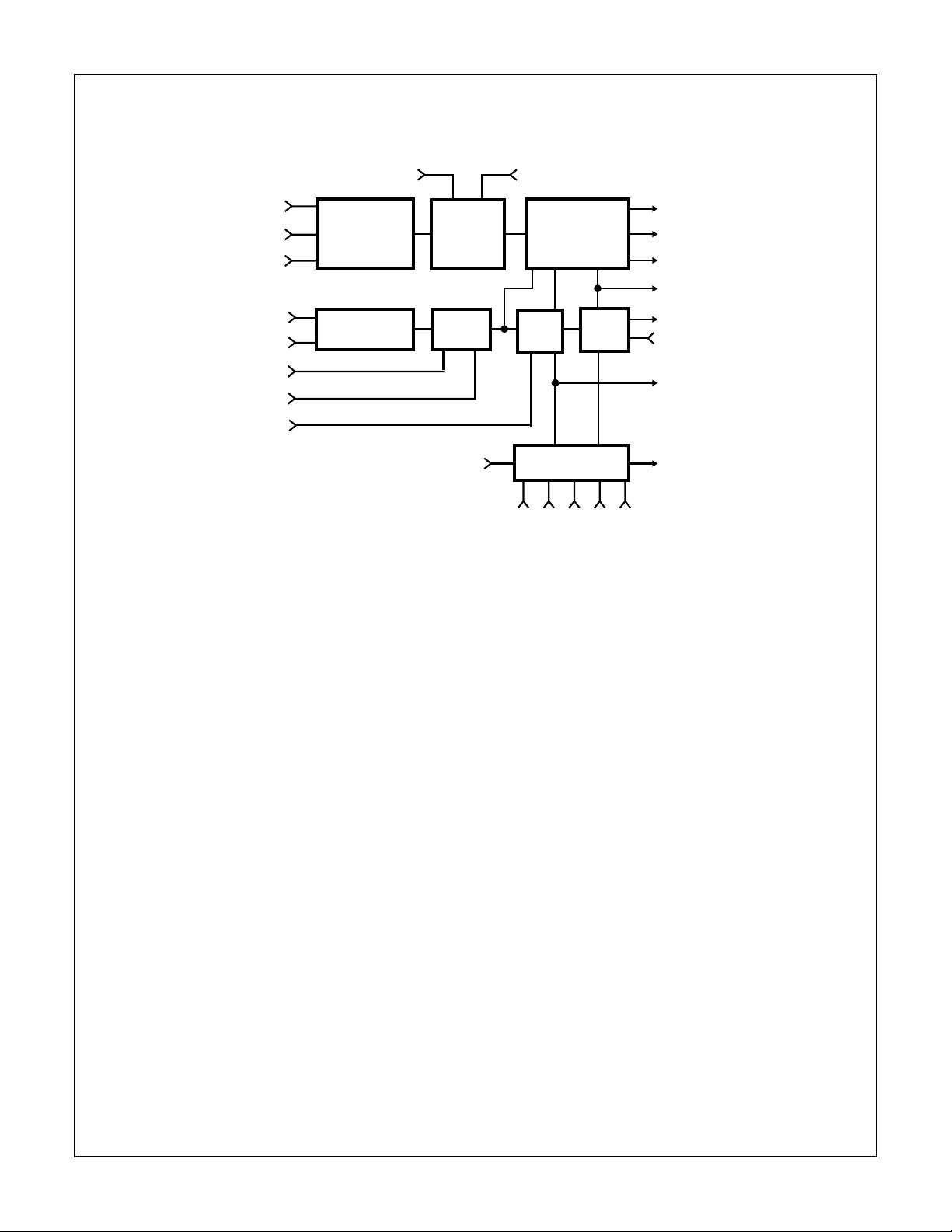

Block Diagrams

CLK SELECT

SYNCHRONOUS

SYNCHRONOUS

CLK SELECT

(Continued)

UNIPOLAR

DATA IN

BIPOLAR

ONE IN

BIPOLAR

ZERO IN

DECODER

CLK

DECODER

CLK

MASTER

RESET

SYNCHRONOUS

DATA SELECT

13

12

TRANSITION

FINDER

11

9

SYNCHRONIZER

15

8

10

22

DECODER

7 8

DAT A

SELECT

GATE

CLOCK

SELECT

DAT A

DECODER

RESET

SYNCHRONOUS

DAT A

CHARACTER

IDENTIFIER

BIT

RATE

CLK

19

20 40 23 36 39

C0 C1 C2 C3 C4

BIT

COUNTER

PARITY

CHECK

4

17

38

5

2

16

14

3

TAKE DATA

COMMAND

DATA SYNC

SERIAL

DATA OUT

VALID WORD

PARITY

SELECT

DECODER

SHIFT CLK

TAKE DATA

5-172

Loading...

Loading...