Intersil Corporation HCTS646MS Datasheet

August 1995

HCTS646MS

Radiation Hardened

Octal Bus Transceiver/Register, Three-State

Features

• 3 Micron Radiation Hardened CMOS SOS

• Total Dose 200K RAD (Si)

• SEP Effective LET No Upsets: >100 MEV-cm

• Single Event Upset (SEU) Immunity < 2 x 10

2

/mg

-9

Errors/

Bit-Day (Typ)

• Dose Rate Survivability: >1 x 10

• Dose Rate Upset >10

10

RAD (Si)/s 20ns Pulse

• Cosmic Ray Upset Rate 2 x 10

12

RAD (Si)/s

-9

Errors/Bit Day

• Latch-Up Free Under Any Conditions

• Fanout (Over Temperature Range)

- Bus Driver Outputs - 15 LSTTL Loads

• Military Temperature Range: -55

o

C to +125oC

• Significant Power Reduction Compared to LSTTL ICs

• DC Operating Voltage Range: 4.5V to 5.5V

• LSTTL Input Compatibility

- VIL = 0.8V Max

- VIH = VCC/2

• Input Current Levels Ii ≤ 5µA at VOL, VOH

Description

The Intersil HCTS646MS is a Radiation Hardened ThreeState Octal Bus Tranceiver/Register with Non-Inverting

outputs. This device is a bus transceiver with D-type flip-flops

which act as internal storage registers. Data on the A bus or

the B bus can be clocked into the registers on a High-to-Low

transition of either CAB ro CBA clock inputs. Output enable

(

OE) and Direction (DIR) inputs control the transceiver functions. Data present at the high impedance output can be

stored in either register or both but only one of the two buses

can be enabled as outputs at any one time. The select controls (SAB and SBA) can multiplex stored and transparent

(real time) data. The direction control determines which data

bus will receive data when the

impedance mode (

OE high), A data can be stored in one register and B data in the other register. Data at the A or B terminals can be clocked into the storage flip-flops at any time.

The HCTS646MS utilizes advanced CMOS/SOS technology

to achieve high-speed operation. This device is a member of

radiation hardened, high-speed, CMOS/SOS Logic Family.

The HCTS646MS is supplied in a 24 lead Ceramic flatpack

(K suffix) or a SBDIP Package (D suffix).

OE pin is LOW. In the high

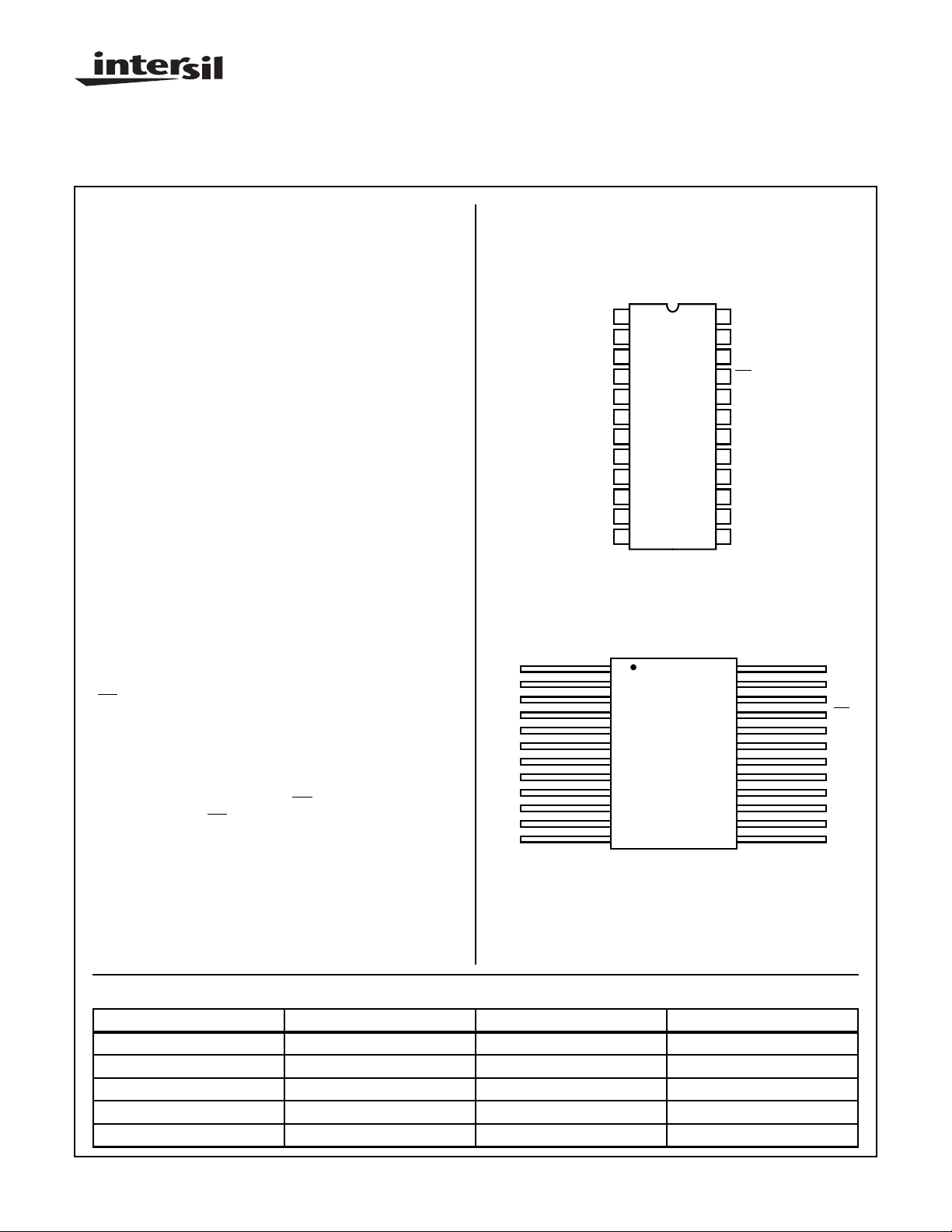

Pinouts

CAB

SAB

DIR

A0

A1

A2

A3

A4

A5

A6

A7

GND

24 LEAD CERAMIC DUAL-IN-LINE

METAL SEAL PACKAGE (SBDIP)

MIL-STD-1835 CDIP2-T24

TOP VIEW

1

CAB

2

SAB

3

DIR

A0

4

5

A1

6

A2

7

A3

8

A4

9

A5

10

A6

11

A7

12

GND

24 LEAD CERAMIC METAL SEAL

FLATPACK PACKAGE (FLATPACK)

MIL-STD-1835 CDFP4-F24

TOP VIEW

1

2

3

4

5

6

7

8

9

10

11

12

24

VCC

CBA

23

SBA

22

21

OE

B0

20

19

B1

B2

18

17

B3

B4

16

15

B5

B6

14

B7

13

24

23

22

21

20

19

18

17

16

15

14

13

VCC

CBA

SBA

OE

B0

B1

B2

B3

B4

B5

B6

B7

Ordering Information

PART NUMBER TEMPERATURE RANGE SCREENING LEVEL PACKAGE

HCTS646DMSR -55oC to +125oC Intersil Class S Equivalent 24 Lead SBDIP

HCTS646KMSR -55oC to +125oC Intersil Class S Equivalent 24 Lead Ceramic Flatpack

HCTS646D/Sample +25oC Sample 24 Lead SBDIP

HCTS646K/Sample +25oC Sample 24 Lead Ceramic Flatpack

HCTS646HMSR +25oC Die Die

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

706

Spec Number

File Number 3074.1

518628

Functional Diagram

HCTS646MS

CL

FF

Q

O

4

PAD

A0

22

PAD

SBA

2

PAD

SAB

23

PAD

CBA

1

PAD

CAB

P

N

CL

FF

Q

O

P

N

TO CHANNELS

1 THROUGH 7

20

PAD

B0

21

PAD

OE

3

PAD

DIR

3

PAD

DIR

12

PAD

VSS

CHANNEL

0

1

2

3

4

5

6

7

PINS

4 - 20

5 - 19

6 - 18

7 - 17

8 - 16

9 - 15

10 - 14

11 - 13

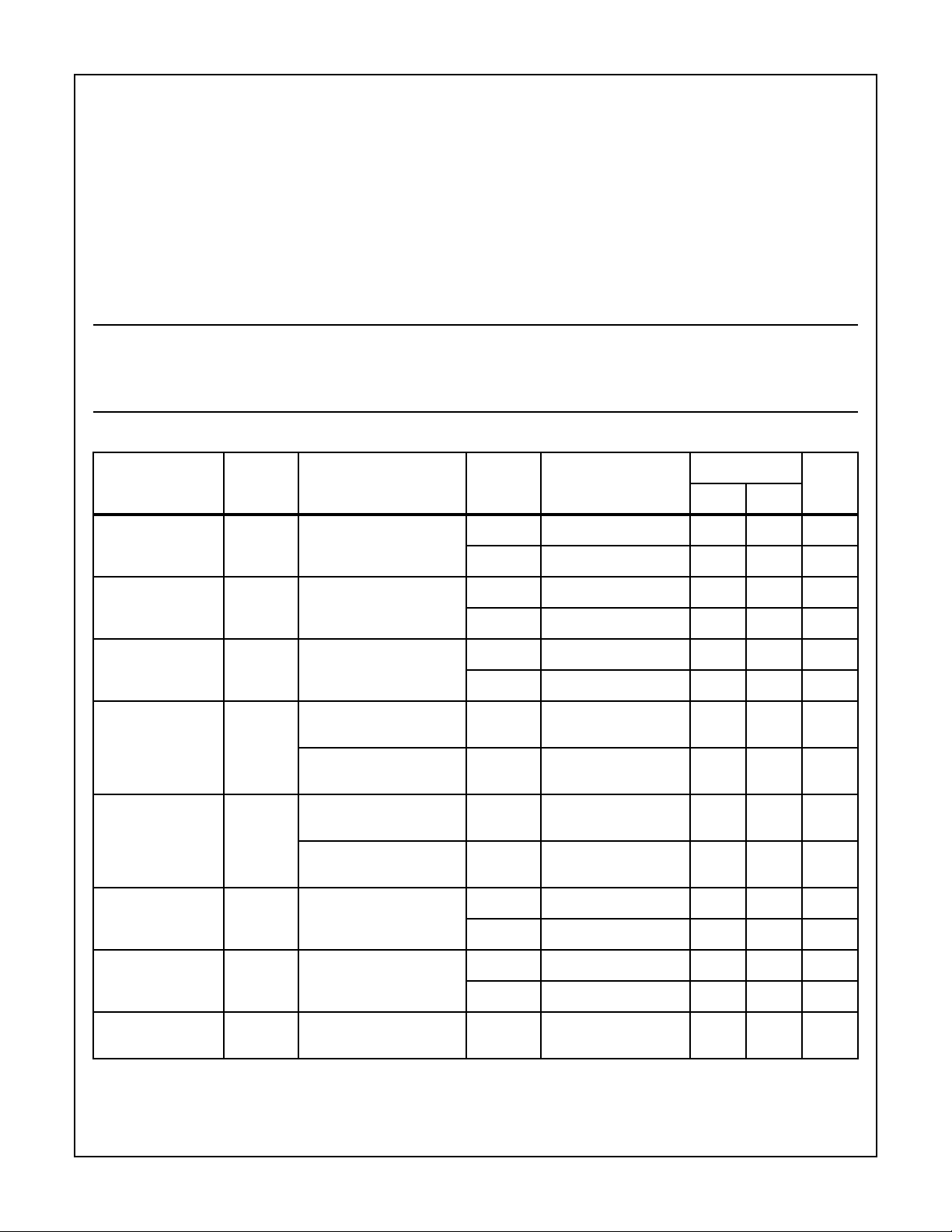

TRUTH TABLE

INPUTS DATA I/O*

OPERATION OR FUNCTIONOE DIR CAB CBA SAB SBA A0 THRU A7 B0 THRU B7

X X X X X Input Not

Specified

X X X X X Input Not

Not Specified

Store A, B Unspecified

Input

Input Store B, A Unspecified

Specified

H X X X Input Input Store A and B Data

H X H or L H or L X X Input Input Isolation, Hold Storage

L L X X X L Output Input Real-Time B Data to A Bus

L L X H or L X H Output Input StoredB Data to A Bus

L H X X L X Input Output Real-Time A Data to B Bus

L H H or L X H X Input Output Stored A Data to B Bus

707

Spec Number 518628

Specifications HCTS646MS

Absolute Maximum Ratings Reliability Information

Supply Voltage (VCC). . . . . . . . . . . . . . . . . . . . . . . . .-0.5V to +7.0V

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VCC +0.5V

DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . . . .±10mA

DC Drain Current, Any One Output. . . . . . . . . . . . . . . . . . . . . . .±25mA

(All Voltage Reference to the VSS Terminal)

Storage Temperature Range (TSTG). . . . . . . . . . . -65oC to +150oC

Lead Temperature (Soldering 10sec). . . . . . . . . . . . . . . . . . +265oC

Junction Temperature (TJ) . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

ESD Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Class 1

CAUTION: As with all semiconductors, stress listed under “Absolute Maximum Ratings” may be applied to devices (one at a time) without resulting in permanent

damage. This is a stress rating only. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. The conditions listed

under “Electrical Performance Characteristics” are the only conditions recommended for satisfactory device operation.

Operating Conditions

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +4.5V to +5.5V

Input Rise and Fall Times at 4.5V VCC (TR, TF). . . . . . .500ns Max

Operating Temperature Range (TA) . . . . . . . . . . . . -55oC to +125oC

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

Thermal Resistance θ

SBDIP Package. . . . . . . . . . . . . . . . . . . . 65oC/W 25oC/W

Ceramic Flatpack Package . . . . . . . . . . . 89oC/W 24oC/W

Maximum Package Power Dissipation at +125oC Ambient

SBDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.77W

Ceramic Flatpack Package . . . . . . . . . . . . . . . . . . . . . . . . . 0.56W

If device power exceeds package dissipation capability, provide heat

sinking or derate linearly at the following rate:

SBDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15.4mW/oC

Ceramic Flatpack Package . . . . . . . . . . . . . . . . . . . . . 11.2mW/oC

Input Low Voltage (VIL). . . . . . . . . . . . . . . . . . . . . . . . . 0.0V to 0.8V

Input High Voltage (VIH). . . . . . . . . . . . . . . . . . . . . . .VCC/2 to VCC

JA

θ

JC

(NOTE 1)

PARAMETER SYMBOL

Quiescent Current ICC VCC = 5.5V,

Output Current

(Sink)

Output Current

(Source)

Output Voltage Low VOL VCC = 4.5V, VIH = 2.25V,

Output Voltage High VOH VCC = 4.5V, VIH = 2.25V,

Input Leakage

Current

IOL VCC = 4.5V, VIH = 4.5V,

IOH VCC = 4.5V, VIH = 4.5V,

IIN VCC = 5.5V, VIN = VCC or

CONDITIONS

VIN = VCC or GND

VOUT = 0.4V, VIL = 0V

VOUT = VCC - 0.4V,

VIL = 0V

IOL = 50µA, VIL = 0.8V

VCC = 5.5V, VIH = 2.75V,

IOL = 50µA, VIL = 0.8V

IOH = -50µA, VIL = 0.8V

VCC = 5.5V, VIH = 2.75V,

IOH = -50µA, VIL = 0.8V

GND

GROUP

A SUB-

GROUPS TEMPERATURE

1 +25oC-40µA

2, 3 +125oC, -55oC - 750 µA

1 +25oC 7.2 - mA

2, 3 +125oC, -55oC 6.0 - mA

1 +25oC -7.2 - mA

2, 3 +125oC, -55oC -6.0 - mA

1, 2, 3 +25oC, +125oC, -55oC - 0.1 V

1, 2, 3 +25oC, +125oC, -55oC - 0.1 V

1, 2, 3 +25oC, +125oC, -55oC VCC

1, 2, 3 +25oC, +125oC, -55oC VCC

1 +25oC-±0.5 µA

2, 3 +125oC, -55oC-±5.0 µA

LIMITS

-V

-0.1

-V

-0.1

UNITSMIN MAX

Three-State Output

Leakage Current

Noise Immunity

Functional Test

NOTES:

1. All voltages referenced to device GND.

2. For functional tests, VO ≥ 4.0V is recognized as a logic “1”, and VO ≤ 0.5V is recognized as a logic “0”.

IOZ Applied Voltage = 0V or

VCC, VCC = 5.5V

FN VCC = 4.5V, VIH = 2.25V,

VIL = 0.8V (Note 2)

1 +25oC-±1 µA

2, 3 +125oC, -55oC-±50 µA

7, 8A, 8B +25oC, +125oC, -55oC---

708

Spec Number 518628

Specifications HCTS646MS

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

GROUP

(NOTES 1, 2)

PARAMETER SYMBOL

A Data to B Bus

(Store)

B Data to A Bus

(Store)

A Data to B Bus TPLH,

B Data to A Bus TPLH,

Select to Data TPLH,

DIR to Output TPLZ,

Enable to Output TPLZ,

DIR to Output TPZL,

Enable to Output TPZL,

NOTES:

1. All voltages referenced to device GND.

2. AC measurements assume RL = 500Ω, CL = 50pF, Input TR = TF = 3ns, VIL = GND, VIH = 3V.

TPLH,

TPHL

TPLH,

TPHL

TPHL

TPHL

TPHL

TPHZ

TPHZ

TPZH

TPZH

CONDITIONS

VCC = 4.5V 9 +25oC 2 31 ns

VCC = 4.5V 9 +25oC 2 32 ns

VCC = 4.5V 9 +25oC 2 24 ns

VCC = 4.5V 9 +25oC 2 24 ns

VCC = 4.5V 9 +25oC 2 30 ns

VCC = 4.5V 9 +25oC 2 28 ns

VCC = 4.5V 9 +25oC 2 28 ns

VCC = 4.5V 9 +25oC 2 28 ns

VCC = 4.5V 9 +25oC 2 30 ns

A SUB-

GROUPS TEMPERATURE

10, 11 +125oC, -55oC 2 36 ns

10, 11 +125oC, -55oC 2 37 ns

10, 11 +125oC, -55oC 2 27 ns

10, 11 +125oC, -55oC 2 27 ns

10, 11 +125oC, -55oC 2 34 ns

10, 11 +125oC, -55oC 2 31 ns

10, 11 +125oC, -55oC 2 31 ns

10, 11 +125oC, -55oC 2 34 ns

10, 11 +125oC, -55oC 2 36 ns

LIMITS

UNITSMIN MAX

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

LIMITS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

Capacitance Power

Dissipation

Input Capacitance CIN VCC = 5.0V, f = 1MHz 1 +25oC - 10 pF

Output Transition

Time

Max Operating

Frequency

Setup Time Data to

Clock

Hold Time Data to

Clock

Pulse Width Clocks TW VCC = 4.5V 1 +25oC25-ns

NOTE:

1. The parameters listed in Table 3 are controlled via design or process parameters. Min and Max Limits are guaranteed but not directly

tested. These parameters are characterized upon initial design release and upon design changes which affect these characteristics.

CPD VCC = 5.0V, f = 1MHz 1 +25oC - 54 pF

1 +125oC, -55oC - 123 pF

1 +125oC - 10 pF

TTHL,

TTLH

FMAX VCC = 4.5V 1 +25oC - 25 MHz

TSU VCC = 4.5V 1 +25oC12-ns

TH VCC = 4.5V 1 +25oC5-ns

VCC = 4.5V 1 +25oC - 12 ns

1 +125oC, -55oC - 18 ns

1 +125oC, -55oC - 17 MHz

1 +125oC, -55oC18-ns

1 +125oC, -55oC5-ns

1 +125oC, -55oC38-ns

UNITSMIN MAX

709

Spec Number 518628

Loading...

Loading...