HCTS373T

Data Sheet July 1999 File Number

Radiation Hardened Octal Transparent

Latch, Three-State

Intersil’sSatellite Applications FlowTM(SAF) devices are fully

tested and guaranteed to 100kRAD total dose. These QML

Class T devices are processed to a standard flow intended

to meet the cost and shorter lead-time needs of large

volume satellite manufacturers, while maintaining a high

level of reliability.

The Intersil HCTS373T is a Radiation Hardened Octal

Transparent Three-State Latch with an active-low output

enable. The outputs are transparent to the inputs when the

Latch Enable (

goes LOW, the data is latched. The Output Enable (

LE) is HIGH. When the Latch Enable (LE)

OE)

controls the three-state outputs. When the Output Enable

(

OE) is HIGH, the outputs are in the high impedance state.

The latch operation is independent of the state of the Output

Enable.

Specifications

Specifications for Rad Hard QML devices are controlled by

the Defense Supply Center in Columbus (DSCC). The SMD

numbers listed below must be used when ordering.

Detailed Electrical Specifications for the HCTS373T are

contained in SMD 5962-95747. A “hot-link” is provided from

our website for downloading.

www.intersil.com/spacedefense/ne wsafc lasst.asp

Intersil’s Quality Management Plan (QM Plan), listing all

Class T screening operations, is also available on our

website.

www.intersil.com/quality/manuals.asp

Ordering Information

TEMP.

ORDERING

NUMBER

PART

NUMBER

RANGE

(oC)

4628.1

Features

• QML Class T, Per MIL-PRF-38535

• Radiation Performance

5

- Gamma Dose (γ) 1 x 10

RAD(Si)

- Latch-Up Free Under Any Conditions

- SEP Effective LET No Upsets: >100 MEV-cm

- Single Event Upset (SEU) Immunity < 2 x 10

2

/mg

-9

Errors/Bit-Day (Typ)

• 3 Micron Radiation Hardened CMOS SOS

• Fanout (Over Temperature Range)

- Bus Driver Outputs - 15 LSTTL Loads

• Significant Power Reduction Compared to LSTTL ICs

• DC Operating Voltage Range: 4.5V to 5.5V

• LSTTL Input Compatibility

-V

= 0.8V Max

IL

-V

= V

IH

• Input Current Levels Ii ≤ 5mA at V

CC/2

Min

OL

, V

OH

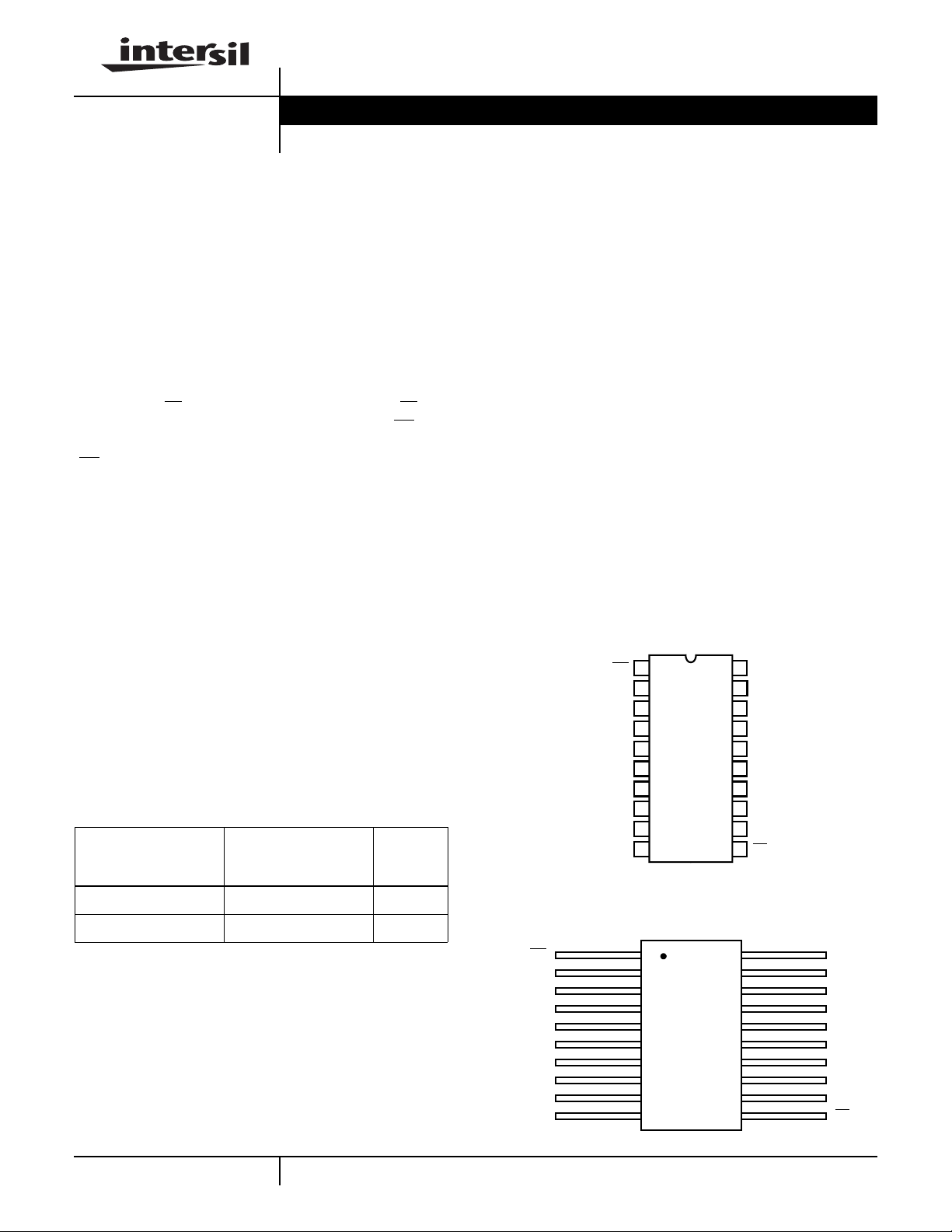

Pinouts

HCTS373T (SBDIP), CDIP2-T20

TOP VIEW

OE

Q0

D0

D1

Q1

Q2

D2

D3

Q3

GND

1

2

3

4

5

6

7

8

9

10

V

20

CC

Q7

19

D7

18

D6

17

Q6

16

Q5

15

D5

14

D4

13

12

Q4

11

LE

5962R9574701TRC HCTS373DTR -55 to 125

5962R9574701TXC HCTS373KTR -55 to 125

NOTE:

Minimumorderquantity for -T is 150 units through

distribution, or 450 units direct.

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

HCTS373T (FLATPACK), CDFP4-F20

TOP VIEW

OE

Q0

D0

D1

Q1

Q2

D2

D3

Q3

GND

www.intersil.com or 407-727-9207

Satellite Applications Flow™ (SAF) is a trademark of Intersil Corporation.

120

2

3

4

5

6

7

8

9

10

19

18

17

16

15

14

13

12

11

| Copyright © Intersil Corporation 1999

V

Q7

D7

D6

Q6

Q5

D5

D4

Q4

LE

CC

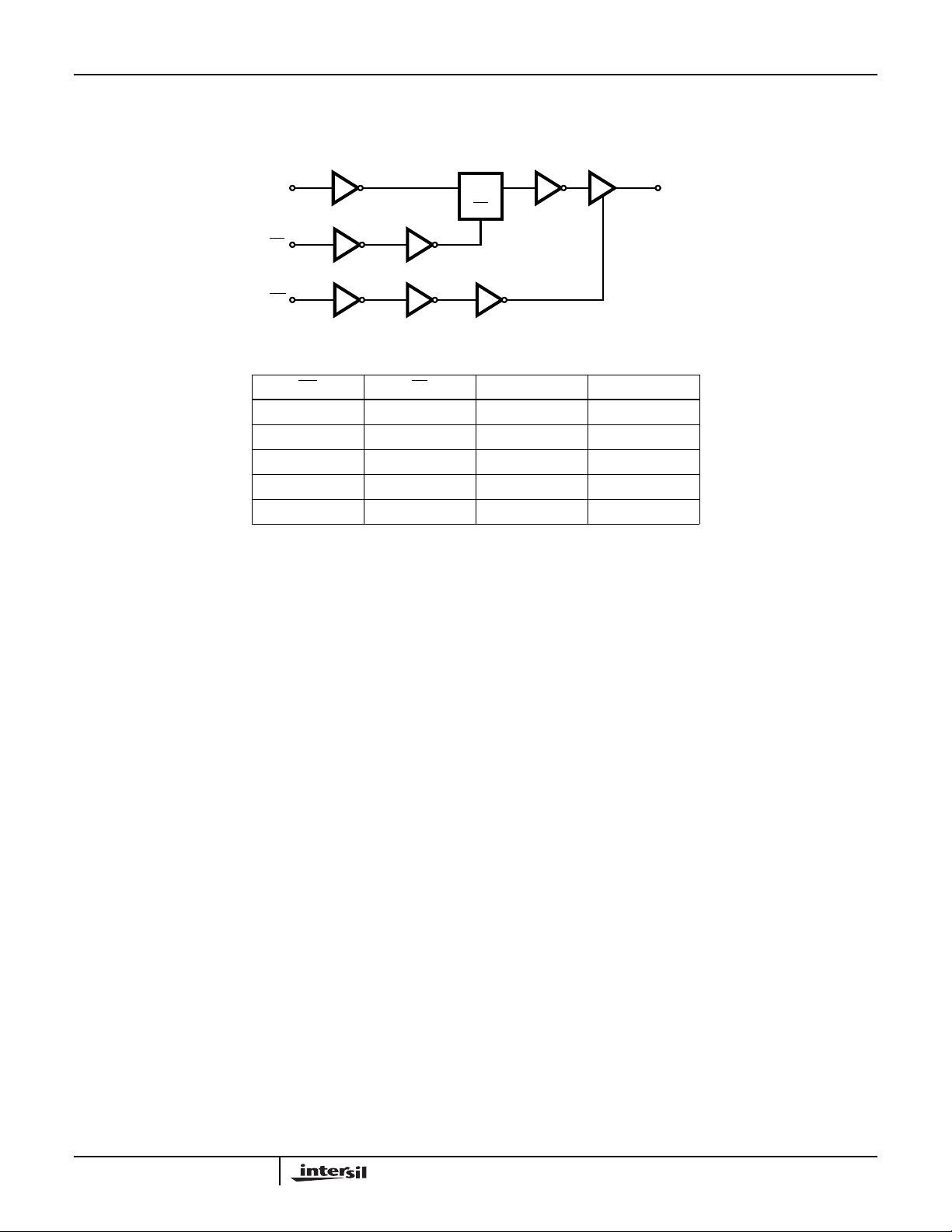

Functional Diagram

HCTS373T

1 OF 8

(3, 4, 7, 8, 13,

14, 17, 18)

D

COMMON CONTROLS

LE

(11)

OE

(1)

OE LE D Q

LHHH

LHLL

LLIL

LLhH

HXXZ

H = High Level, L = Low Level.

X = Immaterial, Z = High Impedance.

I = Low voltage level prior to the high-to-low latch enable transition.

h = High voltage level prior to the high-to-low latch enable transition.

LATCH

DQ

LE

TRUTH TABLE

OE

Q

(2, 5, 6, 9, 12,

15, 16, 19)

2

Loading...

Loading...