HC5513

Data Sheet October 1998 File Number 3963.10

TR909 DLC/FLC SLIC with

Low Power Standby

The HC5513 is a subscriber line interface circuit which is

interchangeable with Ericsson’s PBL3764 for distributed

central office applications. Enhancements include immunity

to circuit latch-up during hot plug and absence of false

signaling in the presence of longitudinal currents.

The HC5513 is fabricated in a High Voltage Dielectrically

Isolated (DI) Bipolar Process that eliminates leakage

currents and device latch-up problems normally associated

with Junction Isolated (JI) ICs. The elimination of the

leakage currents results in improved circuit performance for

wide temperature extremes. The latch free benefit of the DI

xxprocess guarantees operation under adverse transient

conditions. This process feature makes the HC5513 ideally

suited for use in harsh outdoor environments.

Ordering Information

PART

NUMBER

HC5513BIM -40 to 85 28 Ld PLCC N28.45

HC5513BIP -40 to 85 22 Ld PDIP E22.4

TEMP.RANGE

(oC) PACKAGE PKG. NO.

Features

• DI Monolithic High Voltage Process

• Programmable Current Feed (20mA to 60mA)

• Programmable Loop Current Detector Threshold and Battery Feed Characteristics

• Ground Key and Ring Trip Detection

• Compatible with Ericsson’s PBL3764

• Thermal Shutdown

• On-Hook Transmission

• Wide Battery Voltage Range (-24V to -58V)

• Low Standby Power

• Meets TR-NWT-000057 Transmission Requirements

o

• -40

C to 85oC Ambient Temperature Range

Applications

• Digital Loop Carrier Systems . . . . . . . . . . . . . .• Pair Gain

• Fiber-In-The-Loop ONUs . . . . . . . . . . . . . . . . . . . • POTS

• Wireless Local Loop. . . . . . . . . . . . . . . . . . . . . . . .• PABX

• Hybrid Fiber Coax

• Related Literature

- AN9537, Operation of the HC5513/26 Evaluation Board

Block Diagram

RINGRLY

DT

DR

TIP

RING

HPT

HPR

V

BAT

V

CC

V

EE

AGND

BGND

RING RELAY

RING TRIP

DETECTOR

INTERFACE

BIAS

DRIVER

2-WIRE

LOOP CURRENT

DETECTOR

GROUND KEY

DETECTOR

4-WIRE

INTERFACE

VF SIGNAL

PATH

DIGITAL

MULTIPLEXER

V

TX

RSN

E0

E1

C1

C2

DET

R

D

R

DC

RSG

54

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

HC5513

Absolute Maximum Ratings Thermal Information

Operating Temperature Range . . . . . . . . . . . . . . . . -40oC to 110oC

Power Supply (-40oC ≤ TA≤ 85oC)

Supply Voltage VCC to GND . . . . . . . . . . . . . . . . . . . . 0.5V to 7V

Supply Voltage VEE to GND. . . . . . . . . . . . . . . . . . . . .-7V to 0.5V

Supply Voltage V

to GND. . . . . . . . . . . . . . . . . . . -70V to 0.5V

BAT

Ground

Voltage between AGND and BGND. . . . . . . . . . . . . -0.3V to 0.3V

Relay Driver

Ring Relay Supply Voltage . . . . . . . . . . . . . . . . . 0V to V

BAT

75V

Ring Relay Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50mA

Ring Trip Comparator

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

BAT

to 0V

Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -5mA to 5mA

Digital Inputs, Outputs (C1, C2, E0, E1, DET)

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0V to V

Output Voltage (DET Not Active) . . . . . . . . . . . . . . . . . .0V to V

CC

CC

Thermal Resistance (Typical, Note 1) θ

22 Lead PDIP Package . . . . . . . . . . . . . . . . . . . . . . . 53

28 Lead PLCC Package. . . . . . . . . . . . . . . . . . . . . . . 53

Continuous Dissipation at 70oC

22 Lead PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5W

28 Lead PLCC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5W

Package Power Dissipation at 70oC, t < 100ms, t

REP

> 1s

22 Lead PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4W

28 Lead PLCC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4W

Derate above . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70oC

Plastic DIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . 18.8mW/oC

PLCC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18.8mW/oC

Maximum Junction Temperature Range . . . . . . . . . -40oC to 150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . .300oC

(PLCC - Lead Tips Only)

Output Current (DET). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5mA

Tipx and Ringx Terminals (-40oC ≤ TA ≤ 85oC)

Tipx or Ringx Voltage , Contin uous (Ref erenced to GND) .V

Tipx or Ringx, Pulse < 10ms, T

Tipx or Ringx, Pulse < 10µs, T

Tipx or Ringx, Pulse < 250ns, T

> 10s . . . . . .V

REP

> 10s . . . . V

REP

> 10s. . . . V

REP

BAT

BAT

BAT

-20V to 5V

BAT

-40V to 10V

-70V to 15V

to 2V

Die Characteristics

Gate Count . . . . . . . . . . . . . . . . . . . . . . .543 Transistors, 51 Diodes

Tipx or Ringx Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70mA

ESD Rating

Human Body Model (Per MIL-STD-883 Method 3015.7). . . .500V

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationofthe

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

JA

o

C/W

Typical Operating Conditions

These represent the conditions under which the part was developed and are suggested as guidelines.

PARAMETER CONDITIONS MIN TYP MAX UNITS

= R

DC2

R

T

600kΩ

R

RX

300kΩ

o

C

PEAK

R

Case Temperature -40 - 100

VCC with Respect to AGND -40oC to 85oC 4.75 - 5.25 V

VEE with Respect to AGND -40oC to 85oC -5.25 - -4.75 V

V

with Respect to BGND -40oC to 85oC -58 - -24 V

BAT

Electrical Specifications T

= -40oC to 85oC, VCC = 5V ±5%, VEE= -5V ±5%, V

A

= -28V, AGND = BGND = 0V, R

BAT

DC1

41.2kΩ, RD = 39kΩ, RSG = ∞, RF1 = RF2 = 0Ω, CHP = 10nF, CDC = 1.5µF, ZL = 600Ω, Unless Otherwise

Specified. All pin number references in the figures refer to the 28 lead PLCC package.

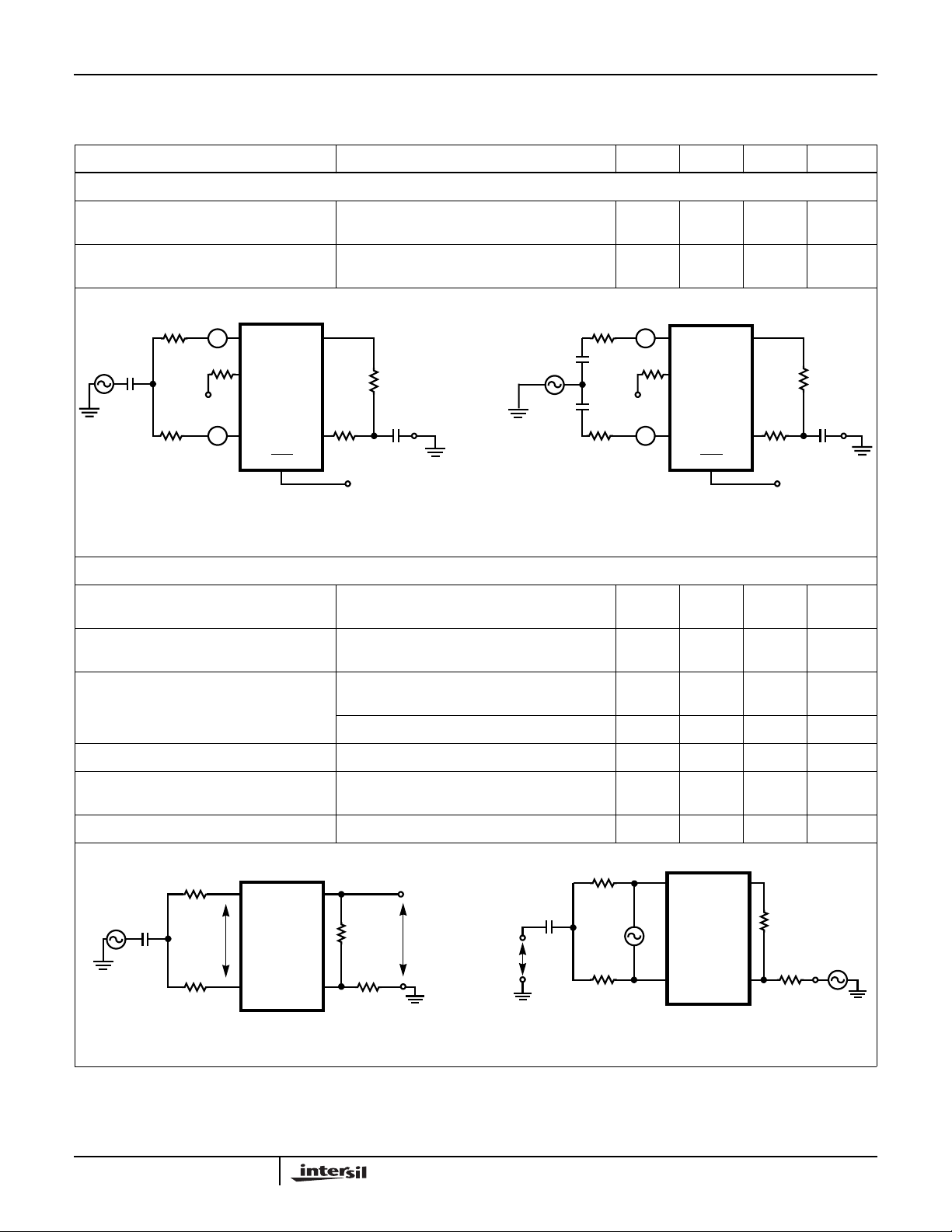

PARAMETER CONDITIONS MIN TYP MAX UNITS

Overload Level 1% THD, ZL = 600Ω, (Note 2, Figure 1) 3.1 - - V

Longitudinal Impedance (Tip/Ring) 0 < f < 100Hz (Note 3, Figure 2) - 20 35 Ω/Wire

600Ω

I

DCMET

23mA

A

300Ω

300Ω

T

A

R

LZT = VT/A

1V

V

TIP

27

R

L

V

TRO

RING28RSN

TX

19

R

T

600kΩ

E

R

RX

16

300kΩ

RX

RMS

0 < f < 100Hz

E

L

2.16µF

C

TIP

27

V

T

V

R

RING28RSN

T

V

TX

19

16

LZR = VR/A

=

FIGURE 1. OVERLOAD LEVEL (TWO-WIRE PORT) FIGURE 2. LONGITUDINAL IMPEDANCE

55

HC5513

Electrical Specifications T

= -40oC to 85oC, VCC = 5V ±5%, VEE= -5V ±5%, V

A

41.2kΩ, RD = 39kΩ, RSG = ∞, RF1 = RF2 = 0Ω, CHP = 10nF, CDC = 1.5µF, ZL = 600Ω, Unless Otherwise

Specified. All pin number references in the figures refer to the 28 lead PLCC package. (Continued)

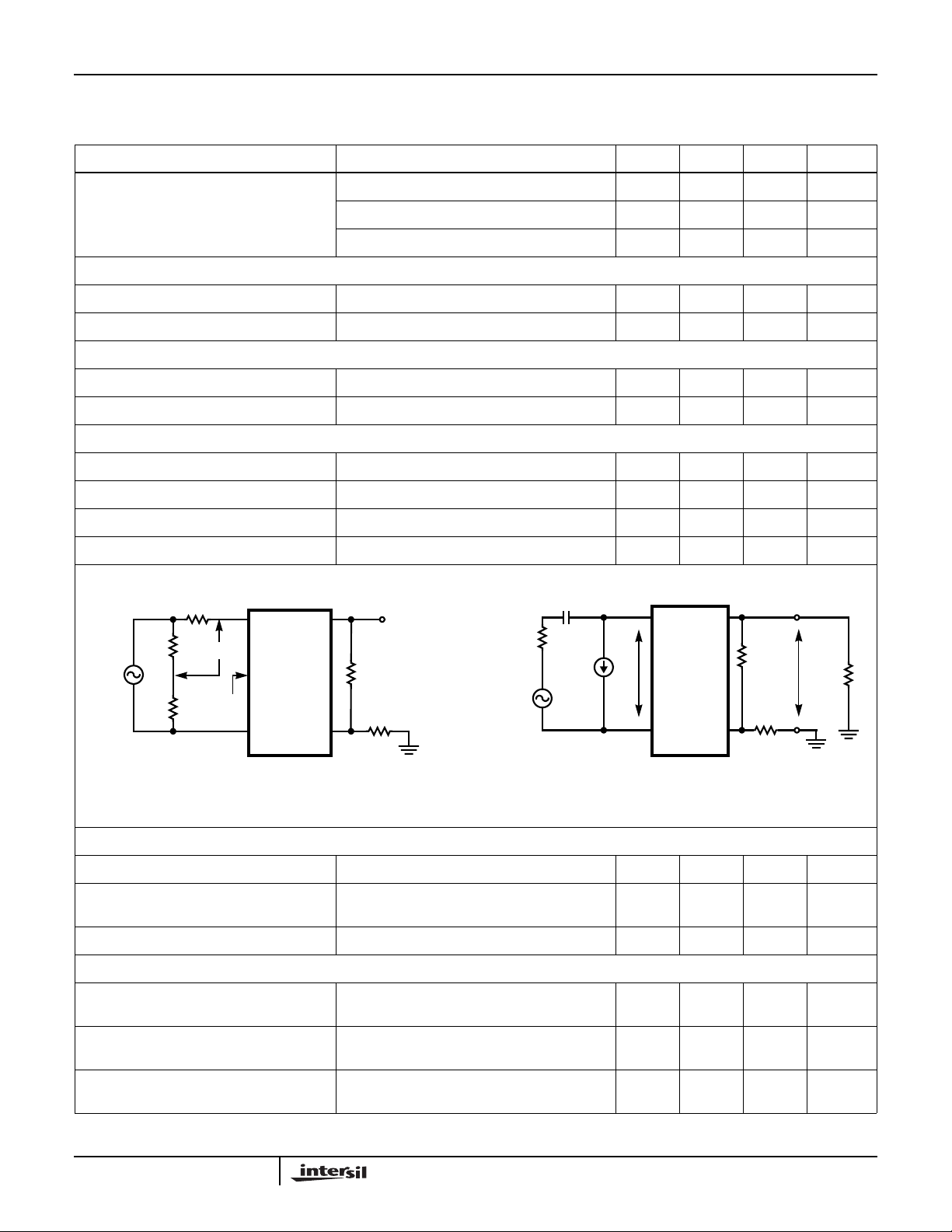

PARAMETER CONDITIONS MIN TYP MAX UNITS

LONGITUDINAL CURRENT LIMIT (TIP/RING)

Off-Hook (Active) No False Detections, (Loop Current),

LB > 45dB (Note 4, Figure 3A)

On-Hook (Standby), RL = ∞ No False Detections (Loop Current)

(Note 5, Figure 3B)

368Ω

E

C

L

2.16µF

368Ω

A

39kΩ

-5V

A

TIP

27

R

D

RING28R

DET

RSN

DC

16

14

R

DC2

41.2kΩ

R

DC1

41.2kΩ

C

DC

1.5µF

FIGURE 3A. OFF-HOOK FIGURE 3B. ON-HOOK

FIGURE 3. LONGITUDINAL CURRENT LIMIT

= -28V, AGND = BGND = 0V, R

BAT

- - 20 mA

DC1

= R

DC2

=

PEAK

/Wire

--5mA

PEAK

/Wire

368Ω

E

L

C2.16µF

C2.16µF

368Ω

A

39kΩ

-5V

A

TIP

27

R

D

RING

28

DET

RSN

R

DC

16

14

R

DC2

41.2kΩ

R

DC1

41.2kΩ

C

DC

1.5µF

OFF-HOOK LONGITUDINAL BALANCE

Longitudinal to Metallic IEEE 455 - 1985, RLR, RLT = 368Ω,

55 70 - dB

0.2kHz < f < 4.0kHz (Note 6, Figure 4)

Longitudinal to Metallic RLR, RLT = 300Ω, 0.2kHz < f < 4.0kHz (Note 6,

55 70 - dB

Figure 4)

Metallic to Longitudinal FCC Part 68, Para 68.310

50 55 - dB

0.2kHz < f < 1.0kHz

1.0kHz < f < 4.0kHz (Note 7) 50 55 - dB

Longitudinal to 4-Wire 0.2kHz < f < 4.0kHz (Note 8, Figure 4) 55 70 - dB

Metallic to Longitudinal RLR, RLT = 300Ω, 0.2kHz < f < 4.0kHz (Note 9,

50 55 - dB

Figure 5)

4-Wire to Longitudinal 0.2kHz < f < 4.0kHz (Note 10, Figure 5) 50 55 - dB

R

LT

300Ω

R

LR

300Ω

E

TR

TIP

27

RING28RSN

V

TX

19

16

R

T

600kΩ

R

RX

300kΩ

E

RX

E

L

C

2.16µF

R

LT

R

LR

TIP

27

V

TR

RING

28

V

RSN

TX

19

16

R

T

600kΩ

R

RX

300kΩ

2.16µF

V

TX

C

V

L

FIGURE 4. LONGITUDINAL TO METALLICAND

LONGITUDINAL TO 4-WIRE BALANCE

56

FIGURE 5. METALLIC TO LONGITUDINAL AND 4-WIRE TO

LONGITUDINAL BALANCE

HC5513

Electrical Specifications T

= -40oC to 85oC, VCC = 5V ±5%, VEE= -5V ±5%, V

A

= -28V, AGND = BGND = 0V, R

BAT

DC1

= R

DC2

=

41.2kΩ, RD = 39kΩ, RSG = ∞, RF1 = RF2 = 0Ω, CHP = 10nF, CDC = 1.5µF, ZL = 600Ω, Unless Otherwise

Specified. All pin number references in the figures refer to the 28 lead PLCC package. (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

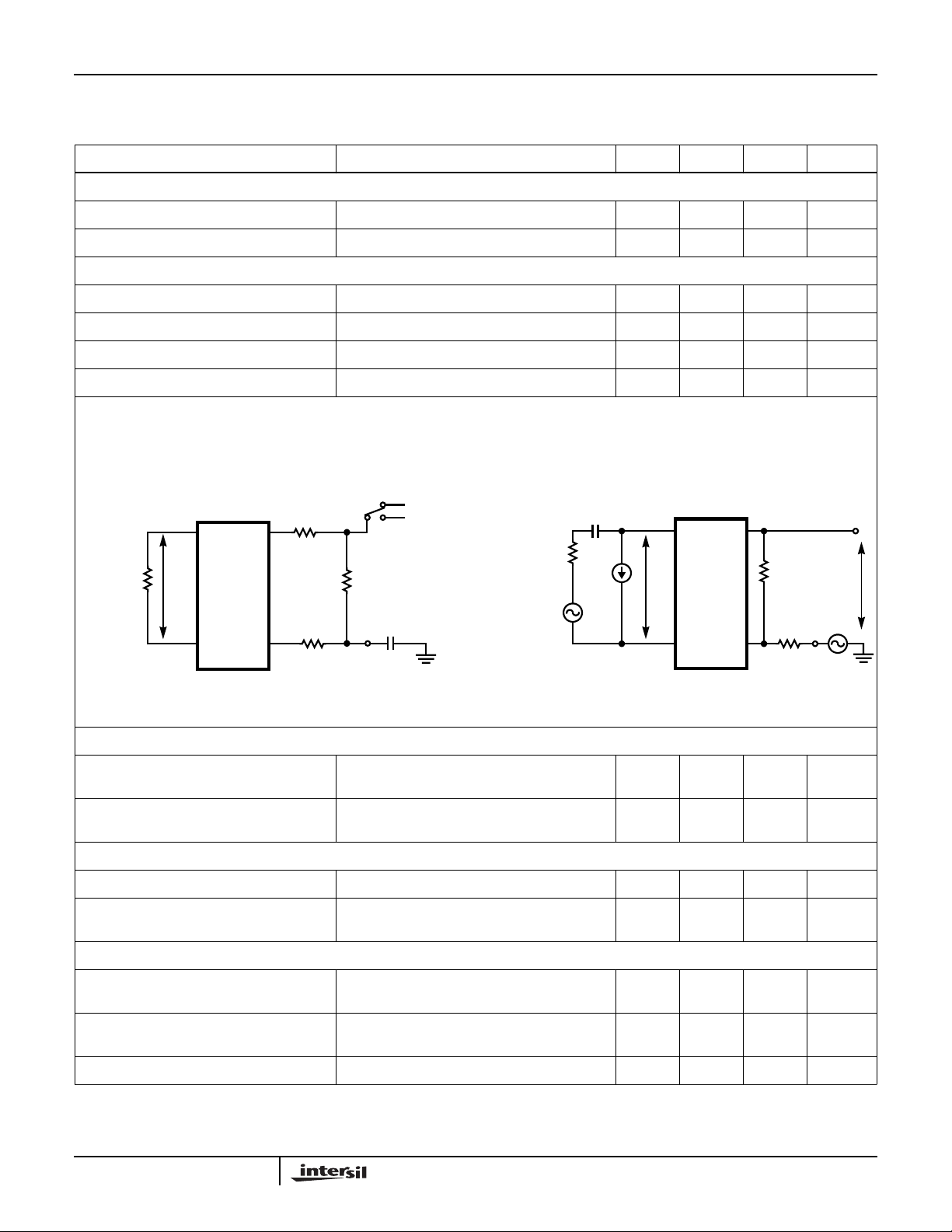

2-Wire Return Loss

0.2kHz to 0.5kHz (Note 11, Figure 6) 25 - - dB

CHP = 20nF

0.5kHz to 1.0kHz (Note 11, Figure 6) 27 - - dB

1.0kHz to 3.4kHz (Note 11, Figure 6) 23 - - dB

TIP IDLE VOLTAGE

Active, IL = 0 --4- V

Standby, IL = 0 -<0- V

RING IDLE VOLTAGE

Active, IL = 0 - -24 - V

Standby, IL = 0 - >-28 - V

4-WIRE TRANSMIT PORT (VTX)

Overload Level (ZL > 20kΩ, 1% THD) (Note 12, Figure 7) 3.1 - - V

PEAK

Output Offset Voltage EG = 0, ZL= ∞, (Note 13, Figure 7) -60 - 60 mV

Output Impedance (Guaranteed by Design) 0.2kHz < f < 03.4kHz - 5 20 Ω

2- to 4-Wire (Metallic to VTX) Voltage Gain 0.3kHz < f < 03.4kHz (Note 14, Figure 7) 0.98 1.0 1.02 V/V

Z

D

TIP

R

V

S

R

R

LR

V

M

Z

IN

27

RING28RSN

V

TX

19

R

T

600kΩ

R

RX

16

300kΩ

R

600Ω

E

2.16µF

L

C

I

DCMET

23mA

G

V

TR

TIP27V

RING28RSN

TX

19

16

R

T

600kΩ

R

RX

300kΩ

V

V

TXO

TX

FIGURE 6. TWO-WIRE RETURN LOSS FIGURE 7. OVERLOAD LEVEL (4-WIRE TRANSMIT PORT),

OUTPUT OFFSET VOLTAGE, 2-WIRE TO 4-WIRE

VOLTAGE GAIN AND HARMONIC DISTORTION

4-WIRE RECEIVE PORT (RSN)

DC Voltage I

RX Sum Node Impedance (Guaranteed by

= 0mA - 0 - V

RSN

0.3kHz < f < 3.4kHz - - 20 Ω

Design)

Current Gain-RSN to Metallic 0.3kHz < f < 3.4kHz (Note 15, Figure 8) 980 1000 1020 Ratio

FREQUENCY RESPONSE (OFF-HOOK)

2-Wire to 4-Wire 0dBm at 1.0kHz, ERX= 0V

-0.2 - 0.2 dB

0.3kHz < f < 3.4kHz (Note 16, Figure 9)

4-Wire to 2-Wire 0dBm at 1.0kHz, EG= 0V

-0.2 - 0.2 dB

0.3kHz < f < 3.4kHz (Note 17, Figure 9)

Z

L

4-Wire to 4-Wire 0dBm at 1.0kHz, EG= 0V

0.3kHz < f < 3.4kHz (Note 18, Figure 9)

57

-0.2 - 0.2 dB

HC5513

Electrical Specifications T

= -40oC to 85oC, VCC = 5V ±5%, VEE= -5V ±5%, V

A

= -28V, AGND = BGND = 0V, R

BAT

DC1

= R

DC2

41.2kΩ, RD = 39kΩ, RSG = ∞, RF1 = RF2 = 0Ω, CHP = 10nF, CDC = 1.5µF, ZL = 600Ω, Unless Otherwise

Specified. All pin number references in the figures refer to the 28 lead PLCC package. (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

INSERTION LOSS

2-Wire to 4-Wire 0dBm, 1kHz (Note 19, Figure 9) -0.2 - 0.2 dB

4-Wire to 2-Wire 0dBm, 1kHz (Note 20, Figure 9) -0.2 - 0.2 dB

GAIN TRACKING (Ref = -10dBm, at 1.0kHz)

2-Wire to 4-Wire -40dBm to +3dBm (Note 21, Figure 9) -0.1 - 0.1 dB

2-Wire to 4-Wire -55dBm to -40dBm (Note 21, Figure 9) - ±0.03 - dB

4-Wire to 2-Wire -40dBm to +3dBm (Note 22, Figure 9) -0.1 - 0.1 dB

4-Wire to 2-Wire -55dBm to -40dBm (Note 22, Figure 9) - ±0.03 - dB

GRX = ((V

Where: V

and V

600Ω

- V

TR1

TR1

TR2

R

L

)(300k))/(-3)(600)

TR2

is the Tip to Ring Voltage with V

is the Tip to Ring Voltage with V

TIP

RSN

27

V

TR

RING28R

16

DC

14

R

RX

300kΩ

R

DC2

41.2kΩ

RSN

RSN

= 0V

= -3V

R

DC1

41.2kΩ

1.5µF

V

= 0V

RSN

= -3V

V

RSN

600Ω

C

DC

E

1/ωC << R

C

V

TR

TIP27V

RING28RSN

R

L

I

DCMET

G

L

TX

19

R

T

600kΩ

RX

E

R

16

300kΩ

RX

=

V

TX

FIGURE 8. CURRENT GAIN-RSN TO METALLIC FIGURE 9. FREQUENCY RESPONSE, INSERTIONLOSS,

GAIN TRACKING AND HARMONIC DISTORTION

NOISE

Idle Channel Noise at 2-Wire C-Message Weighting (Note 23,

- 12 - dBrnC

Figure 10)

Idle Channel Noise at 4-Wire C-Message Weighting (Note 24,

- 12 - dBrnC

Figure 10)

HARMONIC DISTORTION

2-Wire to 4-Wire 0dBm, 1kHz (Note 25, Figure 7) - -65 -54 dB

4-Wire to 2-Wire 0dBm, 0.3kHz to 3.4kHz (Note 26,

- -65 -54 dB

Figure 9)

BATTERY FEED CHARACTERISTICS

Constant Loop Current Tolerance

R

DCX

= 41.2kΩ

Loop Current Tolerance (Standby) IL= (V

IL= 2500/(R

DC1

+ R

DC2

-40oC to 85oC (Note 27)

-3)/(RL +1800),

BAT

),

0.9I

0.8I

L

L

I

L

I

L

1.1I

1.2I

L

L

mA

mA

-40oC to 85oC (Note 28)

Open Circuit Voltage (V

TIP

- V

) -40oC to 85oC, (Active) 14 - 20 V

RING

58

HC5513

Electrical Specifications T

= -40oC to 85oC, VCC = 5V ±5%, VEE= -5V ±5%, V

A

= -28V, AGND = BGND = 0V, R

BAT

DC1

= R

DC2

41.2kΩ, RD = 39kΩ, RSG = ∞, RF1 = RF2 = 0Ω, CHP = 10nF, CDC = 1.5µF, ZL = 600Ω, Unless Otherwise

Specified. All pin number references in the figures refer to the 28 lead PLCC package. (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

LOOP CURRENT DETECTOR

On-Hook to Off-Hook RD = 39kΩ,-40oC to 85oC 372/RD465/RD558/R

Off-Hook to On-Hook RD = 39kΩ,-40oC to 85oC 325/RD405/RD485/R

Loop Current Hysteresis RD = 39kΩ,-40oC to 85oC 25/R

60/R

D

D

95/R

D

D

D

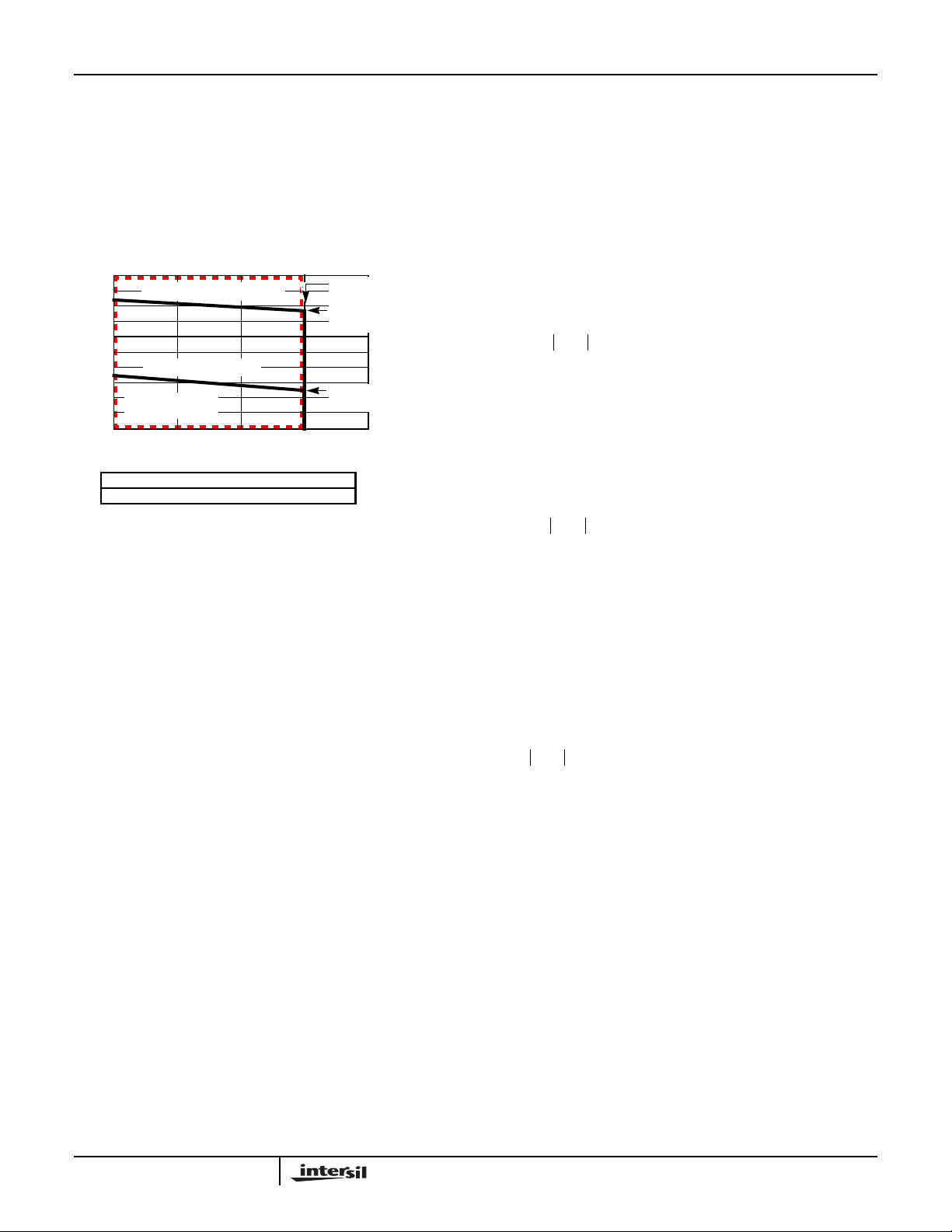

GROUND KEY DETECTOR

Tip/Ring Current Difference - Trigger (Note 29, Figure 11) 8 12 17 mA

Tip/Ring Current Difference - Reset (Note 29, Figure 11) 3 7 12 mA

Hysteresis (Note 29, Figure 11) 0 5 9 mA

R

600Ω

TIP27V

L

V

TR V

RING28RSN

TX

19

16

R

T

600kΩ

R

RX

300kΩ

TIP

27

TX

RING

28

DET

RSN

R

16

DC

14

R

DC2

41.2kΩ

E1 = C1 = 0, C2 = 1

R

DC1

41.2kΩ

C

DC

1.5µF

=

mA

mA

mA

FIGURE 10. IDLE CHANNEL NOISE FIGURE 11. GROUND KEY DETECT

RING TRIP DETECTOR (DT, DR)

Offset Voltage Source Res = 0 -20 - 20 mV

Input Bias Current Source Res = 0 -500 - 500 nA

Input Common-Mode Range Source Res = 0 V

+1 - 0 V

BAT

Input Resistance Source Res = 0, Balanced 3 - - MΩ

RING RELAY DRIVER

V

at 25mA IOL = 25mA - 1.0 1.5 V

SAT

Off-State Leakage Current VOH = 12V - - 10 µA

DIGITAL INPUTS (E0, E1, C1, C2)

Input Low Voltage, V

Input High Voltage, V

IL

IH

0 - 0.8 V

2-VCCV

Input Low Current, IIL: C1, C2 VIL = 0.4V -200 - - µA

Input Low Current, IIL: E0, E1 VIL = 0.4V -100 - - µA

Input High Current VIH = 2.4V - - 40 µA

DETECTOR OUTPUT (DET)

Output Low Voltage, V

Output High Voltage, V

OL

OH

IOL = 2mA - - 0.45 V

IOH = 100µA 2.7 - - V

59

HC5513

Electrical Specifications T

= -40oC to 85oC, VCC = 5V ±5%, VEE= -5V ±5%, V

A

= -28V, AGND = BGND = 0V, R

BAT

DC1

= R

DC2

41.2kΩ, RD = 39kΩ, RSG = ∞, RF1 = RF2 = 0Ω, CHP = 10nF, CDC = 1.5µF, ZL = 600Ω, Unless Otherwise

Specified. All pin number references in the figures refer to the 28 lead PLCC package. (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

Internal Pull-Up Resistor 10 15 20 kΩ

POWER DISSIPATION

Open Circuit State C1 = C2 = 0 - - 23 mW

On-Hook, Standby C1 = C2 = 1 - - 30 mW

On-Hook, Active C1 = 0, C2 = 1, RL= High Impedance - - 150 mW

Off-Hook, Active RL = 0Ω - - 1.1 W

RL = 300Ω - - 0.75 W

RL = 600Ω - - 0.5 W

TEMPERATURE GUARD

Thermal Shutdown 150 - 180

SUPPLY CURRENTS (V

BAT

= -28V)

ICC, On-Hook Open Circuit State (C1, 2 = 0, 0) - - 1.5 mA

Standby State (C1, 2 = 1, 1) - - 1.7 mA

Active State (C1, 2 = 0,1) - - 5.5 mA

=

o

C

IEE, On-Hook Open Circuit State (C1, 2 = 0, 0) - - 0.8 mA

Standby State (C1, 2 = 1, 1) - - 0.8 mA

Active State (C1, 2 = 0, 1) - - 2.2 mA

I

, On-Hook Open Circuit State (C1, 2 = 0, 0) - - 0.4 mA

BAT

Standby State (C1, 2 = 1, 1) - - 0.6 mA

Active State (C1, 2 = 0, 1) - - 3.9 mA

PSRR

VCC to 2 or 4-Wire Port (Note 30, Figure 12) - 40 - dB

VEE to 2 or 4-Wire Port (Note 30, Figure 12) - 40 - dB

V

to 2 or 4-Wire Port (Note 30, Figure 12) - 40 - dB

BAT

-48V SUPPLY

5V SUPPLY

-5V SUPPLY

R

L

600Ω

TIP27V

100mV

TX

19

, 50Hz TO 4kHz

RMS

R

T

600kΩ

PSRR = 20 log (V

V

TX

TX/VIN

)

60

R

RING28RSN

16

RX

300kΩ

FIGURE 12. POWER SUPPLY REJECTION RATIO

HC5513

V

TX

-5V

I

RSN

RSN

R

DC

-

+

R

1

-

+

-2.5V

R

SG

I

I

RING

TIP

TIP

RING

HC5513

+

-

I

TIP

I

RING

-

+

LOOP CURRENT

CIRCUIT

SATURATION GUARD

CIRCUIT

A

A

1

I

1

-5V

2

I

2

FIGURE 13. DC LOOP CURRENT

Circuit Operation and Design Information

-5V

R

RX

R

DC1

C

R

DC2

R

SG

DC

The HC5513 is a current feed voltage senseSubscriber Line

InterfaceCircuit (SLIC). This means that for short loop

applications the SLICprovides a programedconstant current to

the tip and ring terminals while sensing the tip to ring voltage.

The following discussion separates the SLIC’soperation into

its DC and AC path, then follows up with additional circuit

and design information.

Constant Loop Current (DC) Path

SLIC in the Active Mode

The DC path establishes a constant loop current that flows

out of tip and into the ring terminal. The loop current is

programmed by resistors R

the R

the voltage across R

pin (Figure 13). The RDC voltage is determined by

DC

in the saturation guard circuit. Under

1

constant current feed conditions, the voltage drop across R

sets the RDC voltage to -2.5V. This occurs when current

flows through R

establishes a current (I

+R

). This current is then multiplied by 1000, in the loop

DC2

into the current source I2. The RDCvoltage

1

RSN

current circuit, to become the tip and ring loop currents.

For the purpose of the following discussion, the saturation

guard voltage is defined as the maximum tip to ring voltage

at which the SLIC can provide a constant current for a given

battery and overhead voltage.

For loop resistances that result in a tip to ring voltage less than

the saturation guard voltage the loop current is defined as:

2.5V

------------------------------------- -

I

L

R

where: I

R

and R

DC1

+

DC1RDC2

= Constant loop current.

L

1000×=

= Loop current programming resistors.

DC2

, R

DC1

and the voltage on

DC2

) that is equal to V

RDC

/(R

DC1

(EQ. 1)

Capacitor C

signals from the battery feed control loop. The value of C

between R

DC

DC1

and R

removes the VF

DC2

DC

is determined by Equation 2:

1

C

DC

×=

T

---------------

R

DC1

---------------+

R

1

DC2

(EQ. 2)

where T = 30ms.

NOTE: The minimum CDC value is obtained if R

DC1

= R

DC2

.

Figure 14 illustrates the relationship between the tip to ring

voltageand the loop resistance. Fora 0Ω loopresistance both

tip and ring are at V

/2. As the loop resistance increases,

BAT

so does the voltage differential between tip and ring. When

this differential voltage becomes equal to the saturation guard

voltage, the operation of the SLIC’s loop feed changes from a

constant current feed to a resistive f eed. The loop current in

1

the resistive feed region is no longer constant but varies as a

function of the loop resistance.

V

= -48V, IL = 23mA, RSG = 21.4kΩ

0

-10

-20

-30

-40

TIP TO RING VOLTAGE (V)

-50

0 1.2K

SATURATION

GUARD VOLTAGE

CONSTANT CURRENT

FEED REGION

SATURATION

GUARD VOLTAGE

BAT

RESISTIVE FEED

LOOP RESISTANCE (Ω)

FIGURE 14. VTR vs R

REGION

L

V

TIP

V

RING

∞

61

HC5513

Figure 15 shows the relationship between the saturation

guard voltage, the loopcurrent and the loop resistance. Notice

from Figure 15 that for a loop resistance <1.2kΩ (R

21.4k

Ω) the SLIC is operating in the constant current feed

SG

=

region and for resistances >1.2kΩ the SLIC is operating in the

resistive feed region. Operation in the resistive feed region

allows long loop and off-hook transmission by keeping the tip

and ring voltages off the rails. Operation in this region is

transparent to the customer.

50

40

30

20

10

TIP TO RING VOLTAGE (V)

R

L

R

L

V

BAT

V

BAT

RESISTIVE FEED

REGION

0

0

100kΩ

= -48V, RSG = 21.4kΩ

= -24V, RSG = ∞

10 20

LOOP CURRENT (mA)

4kΩ

1.5kΩ

FIGURE 15. VTR vs IL AND R

2kΩ

700Ω <400Ω

CONSTANT CURRENT

FEED REGION

SATURATION GUARD

VOLTAGE, V

SATURATION GUARD

VOLTAGE, V

30

<1.2kΩ

R

RSG

R

RSG

L

= 38V

TR

= 13V

TR

= 21.4kΩ100kΩ

= ∞Ω

The Saturation Guard circuit (Figure 13) monitors the tip to

ring voltage via the transconductance amplifier A

. A

1

1

generates a current that is proportional to the tip to ring

voltage difference. I

is internally set to sink all of A1’s current

1

until the tip to ring voltage exceeds12.5V. When the tip to ring

voltage exceeds 12.5V (with no R

more current than I

can sink. When this happens A

1

resistor) A1 supplies

SG

2

amplifies its input current by a factor of 12 and the current

through R

current from A

across R

becomes the difference between I2and the output

1

. As the current from A2increases, the voltage

2

decreases and the output voltage on R

1

DC

decreases. This results in a corresponding decrease in the

loop current. The R

pin provides the ability to increase the

SG

saturation guard reference voltage be yond 12.5V. Equation 3

gives the relationship between the R

resistor value and the

SG

programmable saturation guard ref erence voltage:

V

SGREF

12.5

510•

------------------+=

R

SG

(EQ. 3)

5

where:

V

R

= Saturation Guard reference voltage.

SGREF

= Saturation Guard programming resistor.

SG

When the Saturation guard reference voltage is exceeded,

the tip to ring voltage is calculated using Equation 4:

V

TRRL

16.66 5 105• RSG⁄+

----------------------------------------------------------------------

×=

R

LRDC1RDC2

+()600⁄+

(EQ. 4)

where:

= Voltage differential between tip and ring.

V

TR

= Loop resistance.

R

L

For on-hook transmission R

5

•

510

16.66

V

TR

The value of R

------------------+=

R

SG

should be calculated to allow maximum

SG

= ∞, Equation 4 reduces to:

L

(EQ. 5)

loop length operation. This requires that the saturationguard

reference voltage be set as high as possible without clipping

the incoming or outgoing VF signal. A voltage margin of -4V

on tip and -4V on ring, for a total of -8V margin, is

recommended as a general guideline. The value of R

SG

is

calculated using Equation 6:

5

510

--------------------------------------------------------------------------------------------------------------------------------------------------=

R

SG

V

–()1

BATVMARGIN

•

R

+()

DC1RDC2

------------------------------------------ -+

600R

L

16.66V–×

(EQ. 6)

where:

= Battery voltage.

V

BAT

V

MARGIN

overload level of 3.1V

For on-hook transmission, R

R

SG

= Recommended valueof -8Vto allowa maximum

.

PEAK

= ∞, Equation 6 reduces to:

L

5

510

----------------------------------------------------------------------------=

V

BATVMARGIN

•

16.66V––

(EQ. 7)

SLIC in the Standby Mode

Overallsystem poweris saved byconfiguring the SLIC in the

standby state when not in use. In the standby state the tip

and ring amplifiers are disabled and internal resistors are

connected between tip to ground and ring to V

BAT

. This

connection enables a loop current to flow when the phone

goes off-hook. The loop current detector then detects this

current and the SLIC is configured in the active mode for

voice transmission. The loop current in standby state is

calculated as follows:

V

------------------------------- -

≈

I

L

R

BAT

L

3V–

1800Ω+

(EQ. 8)

where:

I

= Loop current in the standby state.

L

= Loop resistance.

R

L

= Battery voltage.

V

BAT

(AC) Transmission Path

SLIC in the Active Mode

Figure 16 shows a simplified AC transmission model. Circuit

analysis yields the following design equations:

V

TRVTXIM2RF

V

V

TX

RX

---------- -

-----------+

Z

Z

T

RX

V

TREGIMZL

•+=

I

M

------------ -=

1000

•–=

(EQ. 9)

(EQ. 10)

(EQ. 11)

62

HC5513

where:

V

= Is the AC metallic voltage between tip and ring,

TR

including the voltage drop across the fuse resistors R

= Is the AC metallic voltage. Either at the ground

V

TX

.

F

referenced 4-wire side or the SLIC tip and ring terminals.

I

= Is the AC metallic current.

M

R

= Is a fuse resistor.

F

= Is used to set the SLIC’s 2-wire impedance.

Z

T

V

= Is the analog ground referenced receive signal.

RX

Z

= Is used to set the 4-wire to 2-wire gain.

RX

= Is the AC open circuit voltage.

E

G

Z

= Is the line impedance.

L

(AC) 2-Wire Impedance

The AC 2-wire impedance (ZTR) is the impedance looking

into the SLIC, including the fuse resistors, and is calculated

as follows:

Let V

V

ZTR is defined as:

Z

Substituting in Equation 9 for V

Z

Substituting in Equation 12 for V

Z

Therefore

ZT1000 ZTR2RF–()•=

Equation 16 can now be used to match the SLIC’s

impedance to any known line impedance (Z

= 0. Then from Equation 10

RX

I

M

------------ -

TXZT

TR

TR

TR

•=

1000

V

TR

-----------=

I

M

V

2RFIM•

TX

---------- -

-----------------------+=

I

M

Z

T

------------ - 2R

+=

1000

+

V

TR

-

I

M

F

Z

L

Z

TR

+

E

G

-

TIP

RING

(EQ. 12)

(EQ. 13)

TR

(EQ. 14)

TX

(EQ. 15)

(EQ. 16)

).

TR

I

M

R

F

+

+

V

TX

-

I

M

R

F

-

1

HC5513

A = 250

A = 250

Example:

Calculate ZT to make ZTR = 600Ω in series with 2.16µF.

R

= 20Ω:

F

ZT1000 600

Z

= 560kΩ in series with 2.16nF.

T

•=

(AC) 2-Wire to 4-Wire Gain

The 2-wire to 4-wire gain is equal to VTX/ VTR.

From Equations 9 and 10 with V

V

A

24–

TX

-----------

V

TR

------------------------------------------==

Z

T

(AC) 4-Wire to 2-Wire Gain

The 4-wire to 2-wire gain is equal to VTR/VRX.

From Equations 9, 10 and 11 with EG = 0:

For applications where the 2-wire impedance (ZTR,

42–

V

-----------

V

A

TR

RX

Z

-----------–

Z

Equation 15) is chosen to equal the line impedance (Z

expression for A

A

42–

4-2

Z

1

T

-- -

-----------–

•=

2

Z

RX

(AC) 4-Wire to 4-Wire Gain

The 4-wire to 4-wire gain is equal to VTX/VRX.

From Equations 9, 10 and 11 with EG = 0:

44–

V

-----------

V

RX

A

TX

Z

-----------–

Z

A = 4

1

----------------------------------------- 220•–+

jω 2.16• 10

•

ZT1000⁄

1000⁄ 2RF+

T

--------------------------------------------

•==

Z

T

RX

------------ - 2RFZ

++

1000

simplifies to:

ZL2RF+

T

--------------------------------------------

•==

Z

T

RX

------------ - 2RFZ

++

1000

Z

L

V

RSN

6–

RX

TX

I

M

1000

= 0:

L

L

Z

(EQ. 17)

(EQ. 18)

(EQ. 19)

(EQ. 20)

+

V

TX

T

-

Z

RX

+

V

RX

-

), the

L

63

FIGURE 16. SIMPLIFIED AC TRANSMISSION CIRCUIT

HC5513

Transhybrid Circuit

The purpose of the transhybrid circuit is to remove the

receive signal (V

) from the transmit signal (VTX), thereby

RX

preventing an echo on the transmit side. This is

accomplished by using an external op amp (usually part of

the CODEC) and by the inversion of the signal from the

4-wire receive port (RSN) to the 4-wire transmit port (V

TX

).

Figure 17 shows the transhybrid circuit. The input signal will

be subtracted from the output signal if I

equals I2. Node

1

analysis yields the following equation:

V

V

TX

RX

-----------

-----------+ 0=

R

Z

TX

B

The value of Z

Z

B

Where V

R–

TX

RX/VTX

•=

is then:

B

V

RX

-----------

V

TX

equals 1/ A

4-4

.

(EQ. 21)

(EQ. 22)

Therefore:

Z

T

------------ - 2RFZ

ZBR

TX

•

Z

RX

-----------

Z

T

++

1000

--------------------------------------------

•=

ZL2RF+

L

(EQ. 23)

Example:

Given: RTX = 20kΩ, ZRX = 280kΩ, ZT = 562kΩ (standard

value), R

= 20Ω and ZL= 600Ω,

F

The value of ZB = 18.7kΩ.

R

FB

I

2

R

TX

I

1

Z

T

Z

RX

Z

B

-

+

+

V

TX

-

+

V

RX

-

HC5513

V

TX

RSN

CODEC/

FILTER

FIGURE 17. TRANSHYBRID CIRCUIT

Supervisory Functions

The loop current, ground key and the ring trip detector

outputs are multiplexed to a single logic output pin called

DET. See Table 1 to determine the active detector for a given

logic input. For further discussion of the logic circuitry see

section titled “Digital Logic Inputs”.

Before proceeding with an explanation of the loop current

detector, ground k ey detector and later the longitudinal

impedance, it is important to understand the difference

between a “metallic” and “longitudinal” loop currents. Figure

18 illustrates 3 different types of loop current encountered.

Case 1 illustrates the metallic loop current. The definition of

a metallic loop current is when equal currents flow out of tip

and into ring. Loop current is a metallic current.

Cases 2 and 3 illustrate the longitudinal loop current. The

definition of a longitudinal loop current is a common mode

current, that flows either out of or into tip and ring

simultaneously. Longitudinal currents in the on-hook state

result in equal currents flowing through the sense resistors

R

and R2 (Figure 18). And longitudinal currents in the off-

1

hook state result in unequal currents flowing through the

sense resistors R

and R2. Notice that for case 2,

1

longitudinal currents flowing awayfrom the SLIC, the current

through R

current; whereas the current through R

is the metallic loop current plus the longitudinal

1

is the metallic loop

2

current minus the longitudinal current. Longitudinal currents

are generated when the phone line is influenced by

magnetic fields (e.g., power lines).

Loop Current Detector

Figure 18 shows a simplified schematic of the loop current

and ground key detectors. The loop current detector works

by sensing the metallic current flowing through resistors R

and R2. This results in a current (IRD) out of the

transconductance amplifier (gm

of gm

and the metallic loop current. IRD then flows out the

1

R

pin and through resistor RD to VEE. The value of IRD is

D

equal to:

I

I

RD

The I

–

TIPIRING

----------------------------------- -

600

current results in a voltage drop across RD that is

RD

I

L

--------- -==

300

compared to an internal 1.25V reference voltage. When the

voltage drop across R

exceeds 1.25V, and the logic is

D

configured for loop current detection, the

The hysteresis resistor RH adds an additional voltage

effectively across R

, causing the on-hook to off-hook

D

threshold to be slightly higher than the off-hook to on-hook

threshold.

Taking into account the hysteresis voltage, the typical value

of R

for the on-hook to off-hook condition is:

D

R

--------------------------------------------------------------------------=

D

I

ON HOOK to OFF– HOOK–

465

Taking into account the hysteresis voltage, the typical value

for the off-hook to on-hook condition is:

of R

D

R

--------------------------------------------------------------------------=

D

I

OFF HOOK to ON– HOOK–

375

) that is equal to the product

1

(EQ. 24)

DET pin goes low.

(EQ. 25)

(EQ. 26)

1

64

HC5513

+

-

CASE 1 CASE 2 CASE 3

I

METALLIC

I

METALLIC

←

→

I

LONGITUDINAL

←

I

LONGITUDINAL

←

I

LONGITUDINAL

→

I

LONGITUDINAL

→

TIP

RING

R

1

R

2

HC5513

-

+

FIGURE 18. LOOP CURRENT AND GROUND KEY DETECTORS

A filter capacitor (CD) in parallel with RD will improve the

accuracy of the trip point in a noisy environment. The value

of this capacitor is calculated using the following Equation:

T

C

------- -=

D

R

D

(EQ. 27)

Where: T = 0.5ms.

Ground Key Detector

A simplified schematic of the ground key detector is sho wn in

Figure 18. Ground key, is the process in which the ring terminal

is shorted to ground for the purpose of signaling an Operator or

seizing a phone line (between the Central Office and a Private

Branch Exchange). The Ground Ke y detector is activated when

unequal current flow through resistors R1 and R2. This results

in a current (IGK) out of the transconductance amplifier (gm2)

that is equal to the product of gm2 and the differential (ITIP IRING) loop current. If IGK is less than the internal current

source(I1), then diodeD1 is onand the outputof the groundkey

comparator is low . If IGK is g reater than the internal current

source(I1), then diodeD2 is onand the outputof the groundkey

comparator is high. With the output of the ground ke y

comparator high, andthe logic configured for ground keydetect,

the DET pin goes low . The g round k ey detector has a built in

hysteresis of typically 5mA between its trigger and reset v alues .

Ring Trip Detector

Ring trip detection is accomplished with the internal ring trip

comparator and the external circuitry shown in Figure 19. The

process of ring trip isinitiated when thelogic input pinsare in the

followingstates: E0 = 0, E1 = 1/0, C1 = 1 and C2 = 0. This logic

condition connects the ring trip comparator to the

and causes the Ringrly pin to energize the ring relay. The ring

relay connects the tip and ring of the phone to the e xternal

circuitry in Figure 19. When the phone is on-hook the DT pin is

more positive than the DR pin and the

DET output is high. For

off-hook conditions DR is more positive than DT and

low . When

DET goes low , indicating that the phone has gone

DET output,

DET goes

gm

1

gm

2

R

H

+

-

GROUND

KEY

COMPARATOR

gm1(I

METALLIC

CURRENT

COMPARATOR

gm2(I

I

GK

D

1

DIGITAL MULTIPLEXER

LOOP

- I

TIP

)

RING

D

2

I

1

R

D

R

H

+

-

+

)

V

1.25V

REF

I

RD

R

D

-

V

EE

-5V

DET

off-hook, the SLIC is commanded by the logic inputs to go into

the active state. In the activ e state , tip and ring are once again

connected to the phone and normal operation ensues.

Figure 19 illustrates battery backed unbalanced ring injected

ringing. For tip injected ringing just reverse the leads to the

phone. The ringing source could also be balanced.

NOTE: The DET output will toggle at 20Hz because the DT input is

not completely filtered by CRT. Software can examine the duty cycle

and determine if the DET pin is low for more that half the time, if so

the off-hook condition is indicated.

TIP

RING

R

3

C

RT

R4R

E

RG

R

1

2

V

BAT

RINGRLY

DT

DR

COMPARATOR

-

+

RING TRIP

HC5513

R

RT

RING

RELAY

FIGURE 19. RING TRIP CIRCUIT FOR BA TTERY BACKED RINGING

Longitudinal Impedance

The feedback loop described in Figure 20(A, B) realizes the

desired longitudinal impedances from tip to ground and from

ring to ground. Nominal longitudinal impedance is resistive

and in the order of 22Ω.

In the presence of longitudinal currents this circuit

attenuates the voltages that would otherwise appear at the

tip and ring terminals, to levelswell within the common mode

range of the SLIC. In fact, longitudinal currents may exceed

the programmed DC loop current without disturbing the

SLIC’s VF transmission capabilities.

C

D

DET

65

HC5513

The function of this circuit is to maintain the tip and ring

voltages symmetrically around V

/2, in the presence of

BAT

longitudinal currents. The differential transconductance

amplifiers G

the required current to maintain V

and GRaccomplish this by sourcing or sinking

T

C

at V

BAT

/2.

When a longitudinal current is injected onto the tip and ring

inputs, the voltage at V

/2. When VCchanges by the amount ∆VC, this change

V

BAT

moves from it’s equilibrium value

C

appears between the input terminals of the differential

transconductance amplifiers G

and GR. The output of G

T

T

and GR are the differential currents ∆I1 and ∆I2, which in

turn feed the differential inputs of current sources I

and I

T

R

respectively. IT and IR have current gains of 250 single

ended and 500 differentially, thus leading to a change in I

T

and IR that is equal to 500(∆I) and 500(∆I2).

The circuit shown in Figure 20(B) illustrates the tip side of

the longitudinal network. The advantages of a differential

input current source are: improved noise since the noise due

to current source 2I

is now correlated, power savings due

O

to differential current gain and minimized offset error at the

Operational Amplifier inputs via the two 5kΩ resistors.

Digital Logic Inputs

Table 1 is the logic truth table for the TTL compatible logic

input pins. The HC5513 has two enable inputs pins (E0, E1)

and two control inputs pins (C1, C2).

The enable pin E0 is used to enable or disable the

output pin. The

DET pin is enabled if E0 is at a logic level 0

and disabled if E0 is at a logic level 1.

The enable pin E1 gates the ground key detector to the

output with a logic level 0, and gates the loop or ring trip

detector to the

DET output with a logic level 1.

A combination of the control pins C1 and C2 is used to

select 1 of the 4 possible operating states. A description of

each operating state and the control logic follow:

DET

DET

Open Circuit State (C1 = 0, C2 = 0)

In this state the SLIC is effectively off. All detectors and both

the tip and ring line drive amplifiers are powered down,

presenting a high impedance to the line. Powerdissipation is

at a minimum.

Active State (C1 = 0, C2 = 1)

The tip output is capable of sourcing loop current and for

open circuit conditions is about -4V from ground. The ring

output is capable of sinking loop current and for open circuit

conditions is about V

+ 4V. VF signal transmission is

BAT

normal. The loop current and ground key detectors are both

active, E0 and E1 determine which detector is gated to the

DET output.

Ringing State (C1 = 1, C2 = 0)

The ring relay driver and the ring trip detector are activated.

Both the tip and ring line drive amplifiers are powered down.

Both tip and ring are disconnected from the line via the

external ring relay.

Standby State (C1 = 1, C2 = 1)

Both the tip and ring line drive amplifiers are powered down.

Internal resistors are connected between tip to ground and ring

to V

to allow loop current detect in an off-hook condition.

BAT

The loop current and ground key detectors are both active , E0

and E1 determine which detector is gated to the

DET output.

AC Transmission Circuit Stability

To ensure stability of the AC transmission feedbackloop two

compensation capacitors C

Figure 21 (Application Circuit) illustrates their use.

Recommended value is 2200pF.

and CRC are required.

TC

I

LONG

I

LONG

I

LONG

TIP

+

∆V

T

-

R

LARGE

+

V

C

-

R

+

R

-

LARGE

RING

HC5513

FIGURE 20. LONGITUDINAL IMPEDANCE NETWORK

I

LONG

∆V

FIGURE 20A. FIGURE 20B.

I

T

∆I

∆I

∆I

1

2

1

G

T

V

/2

BAT

G

R

∆I

2

I

R

TIP

V

RING

R

LARGE

C

R

LARGE

66

TIP CURRENT SOURCE

WITH DIFFERENTIAL INPUTS

20Ω

5kΩ

5kΩ

∆I

1

2I

0

TIP DIFFERENTIAL

TRANSCONDUCTANCE

AMPLIFIER

-

+

∆I

1

V

BAT

/2

G

T

HC5513

AC-DC Separation Capacitor, C

HP

The high pass filter capacitor connected between pins HPT

and HPR provides the separation between circuits sensing

tip to ring DC conditions and circuits processing AC signals.

A 10nf C

will position the low end frequency response

HP

3dB break point at 48Hz. Where:

f

3dB

Where R

---------------------------------------------------- -=

1

2 π• RHP• CHP•()

= 330kΩ.

HP

(EQ. 28)

Thermal Shutdown Protection

The HC5513’s thermal shutdown protection is invoked if a

fault condition on the tip or ring causes the temperature of

the die to exceed 160

o

C. If this happens, the SLIC goes into

a high impedance state and will remain there until the

temperature of the die cools down by about 20

o

C. The SLIC

will return back to its normal operating mode, providing the

fault condition has been removed.

Surge Voltage Protection

The HC5513 must be protected against surge voltages and

power crosses. Refer to “Maximum Ratings” TIPX and

RINGX terminals for maximum allowable transient tip and

ring voltages. The protection circuit shown in Figure 21

utilizes diodes together with a clamping device to protect tip

and ring against high voltage transients.

Positive transients on tip or ring are clamped to within a

couple of volts above ground via diodes D

and D2. Under

1

normal operating conditions D

and D2 are reverse biased

1

and out of the circuit.

Negative transients on tip and ring are clamped to within a

couple of volts below ground via diodes D

and D4 with the

3

help of a Surgector. The Surgector is required to block

conduction through diodes D

and D4 under normal

3

operating conditions and allows negative surges to be

returned to system ground.

The fuse resistors (R

) serve a dual purpose of being

F

nondestructive power dissipaters during surge and fuses

when the line in exposed to a power cross.

Power-Up Sequence

The HC5513 has no required power-up sequence. This is a

result of the Dielectrically Isolated (DI) process used in the

fabrication of the part. By using the DI process, care is no

longer required to insure that the substrate be kept at the

most negative potential as with junction isolated ICs.

Printed Circuit Board Layout

Care in the printed circuit board layout is essential for proper

operation. All connections to the RSN pin should be made

as close to the device pin as possible, to limit the

interference that might be injected into the RSN terminal. It

is good practice to surround the RSN pin with a ground

plane.

The analog and digital grounds should be tied together at

the device.

SLIC Operating States

TABLE 1. LOGIC TRUTH TABLE

E0 E1 C1 C2 SLIC OPERATING STATE ACTIVE DETECTOR

0000Open Circuit No Active Detector Logic Level High

0001Active Ground Key Detector Ground Key Status

0010Ringing No Active Detector Logic Level High

0011Standby Ground Key Detector Ground Key Status

0100Open Circuit No Active Detector Logic Level High

0101Active Loop Current Detector Loop Current Status

0110Ringing Ring Trip Detector Ring Trip Status

0111Standby Loop Current Detector Loop Current Status

1000Open Circuit No Active Detector

1001Active Ground Key Detector

1010Ringing No Active Detector

1011Standby Ground Key Detector

1100Open Circuit No Active Detector

1101Active Loop Current Detector

1110Ringing Ring Trip Detector

1111Standby Loop Current Detector

DET OUTPUT

Logic Level High

67

HC5513

Notes

2. Overload Level(Two-Wireport) - The overload le vel is speci-

fied at the 2-wire port (V

receive port (ERX). I

ERX until 1% THD is measured at V

3. Longitudinal Impedance - The longitudinal impedance is

computed using the following equations, where TIP and RING

voltages are referenced to ground. LZT,LZR,VT,VR,ARand

AT are defined in Figure 2.

(TIP) LZT = VT/A

T

(RING) LZR = VR/A

Where: EL = 1V

RMS

4. Longitudinal Current Limit(Off-HookActive) - Off-Hook

(Active, C1=1,C2= 0) longitudinal current limit is determined

by increasing the amplitude of EL(Figure 3A) until the 2-wire

longitudinal balance drops below 45dB. DET pin remains low

(no false detection).

5. Longitudinal CurrentLimit(On-Hook Standby) - On-Hook

(Active, C1=1,C2= 1) longitudinal current limit is determined by

increasing the amplitude of EL(Figure 3B) until the 2-wire longitudinal balance drops below 45dB. DET pin remains high (no

false detection).

6. Longitudinal to MetallicBalance - The longitudinal to metallic balance is computed using the following equation:

BLME = 20 • log (EL/VTR), where: ELand VTRare defined in

Figure 4.

7. Metallic to Longitudinal FCC Part68,Para68.310 - The

metallic to longitudinal balance is defined in this spec.

8. Longitudinal to Four-WireBalance - The longitudinal to 4-wire

balance is computed using the following equation:

BLFE = 20 • log (EL/VTX),: ELand VTXare defined in Figure 4.

9. Metallic to LongitudinalBalance - The metallic to longitudinal

balance is computed using the following equation:

BMLE = 20 • log (ETR/VL), ERX = 0

Where: ETR,VLand ERX are defined in Figure 5.

10. Four-Wire toLongitudinalBalance - The 4-wire to longitudinal

balance is computed using the following equation:

BFLE = 20 • log (ERX/VL), ETR = source is removed.

Where: ERX,VLand ETR are defined in Figure 5.

11. Two-WireReturn Loss - The 2-wire return loss is computed

using the following equation:

r = -20 • log (2VM/VS)

Where: ZD= The desired impedance; e.g., the characteristic

impedance of the line, nominally 600Ω. (Reference Figure 6).

12. Overload Level(4-Wireport) - The overload level is specified

at the 4-wire transmit port (V

the 2-wire port, I

DCMET

7). Increase the amplitude of EGuntil 1% THD is measured at

V

. Note that the gain from the 2-wire port to the 4-wire port

TXO

is equal to 1.

13. Output OffsetVoltage - The output offset voltage is specified

with the following conditions: EG=0,I

and is measured at VTX.EG,I

in Figure 7. Note: I

resistor between tip and ring.

) with the signal source at the 4-wire

TR0

=30µA, increase the amplitude of

DCMET

R

. Reference Figure 1.

TRO

(0Hz to 100Hz).

) with the signal source (EG)at

TXO

= 23mA, ZL= 20kΩ (Reference Figure

= 23mA, ZL= ∞

DCMET

DCMET,VTX

is established with a series 600Ω

DCMET

and ZLare defined

14. Two-Wireto Four-Wire(Metallic toVTX) Voltage Gain - The

2-wire to 4-wire (metallic to VTX) voltage gain is computed

using the following equation.

G

=(VTX/VTR), EG= 0dBm0, VTX,VTR, and EGare

2-4

defined in Figure 7.

15. Current Gain RSN to Metallic - The current gain RSN to

Metallic is computed using the following equation:

K=IM[(R

V

and V

RDC

DC1+RDC2

RSN

)/(V

RDC-VRSN

are defined in Figure 8.

)] K, IM,R

DC1,RDC2

16. Two-Wireto Four-Wire Frequency Response - The 2-wire to

4-wire frequency response is measured with respect to

EG= 0dBm at 1.0kHz, ERX=0V,I

= 23mA. The frequency

DCMET

response is computed using the following equation:

F

=20• log (VTX/VTR), vary frequency from 300Hz to

2-4

3.4kHz and compare to 1kHz reading.

VTX, VTR, and EG are defined in Figure 9.

17. Four-Wire to Two-WireFrequency Response - The 4-wire to

2-wire frequency response is measured with respect to

ERX= 0dBm at 1.0kHz, EG=0V,I

= 23mA. The frequency

DCMET

response is computed using the following equation:

F

=20• log (VTR/ERX), vary frequency from 300Hz to

4-2

3.4kHz and compare to 1kHz reading.

VTR and ERX are defined in Figure 9.

18. Four-Wire to Four-WireFrequencyResponse - The 4-wire to

4-wire frequency response is measured with respect to

ERX= 0dBm at 1.0kHz, EG=0V,I

= 23mA. The frequency

DCMET

response is computed using the following equation:

F

=20• log (VTX/ERX), vary frequency from 300Hz to

4-4

3.4kHz and compare to 1kHz reading.

VTXand ERX are defined in Figure 9.

19. Two-Wireto Four-Wire Insertion Loss - The 2-wire to 4-wire

insertion loss is measured with respect to EG= 0dBm at 1.0kHz

input signal, ERX=0,I

= 23mA and is computed using

DCMET

the following equation:

L

= 20 • log (VTX/VTR)

2-4

where: VTX,VTR, and EGare defined in Figure 9. (Note: The

fuse resistors, RF, impact the insertion loss. The specified

insertion loss is for RF = 0).

20. Four-Wire to Two-WireInsertion Loss - The 4-wire to 2-wire

insertion loss is measured based upon ERX= 0dBm, 1.0kHz

input signal, EG=0,I

= 23mA and is computed using

DCMET

the following equation:

L

= 20 • log (VTR/ERX)

4-2

Where: VTR and ERX are defined in Figure 9.

21. Two-Wireto Four-Wire Gain Tracking - The 2-wire to 4-wire

gain tracking is referenced to measurements taken for

EG= -10dBm, 1.0kHz signal, ERX=0,I

DCMET

= 23mA and is

computed using the following equation.

G

=20• log (VTX/VTR) vary amplitude -40dBm to +3dBm, or

2-4

-55dBm to -40dBm and compare to -10dBm reading.

VTX and VTR are defined in Figure 9.

22. Four-Wire to Two-WireGain Tracking - The 4-wire to 2-wire

gain tracking is referenced to measurements taken for

ERX= -10dBm, 1.0kHz signal, EG=0,I

DCMET

= 23mA and is

computed using the following equation:

G

=20• log (VTR/ERX) vary amplitude -40dBm to +3dBm,

4-2

or -55dBm to -40dBm and compare to -10dBm reading.

VTRand ERXare defined in Figure 9. The level is specified at the

4-wire receive port and referenced to a 600Ω impedance lev el.

,

68

HC5513

23. Two-WireIdle Channel Noise - The 2-wire idle channel noise

at VTRis specified with the 2-wire port terminated in 600Ω (RL)

and with the 4-wire receive port grounded (Reference Figure 10).

24. Four-Wire IdleChannelNoise - The 4-wire idle channel noise

at VTXis specified with the 2-wire port terminated in 600Ω (RL).

The noise specification is with respect to a 600Ω impedance

level at VTX. The 4-wire receive port is grounded (Reference

Figure 10).

25. Harmonic Distortion (2-Wire to 4-Wire) - The harmonic distortion is measured with the following conditions. EG= 0dBm at

1kHz, I

= 23mA. Measurement taken at VTX. (Reference

DCMET

Figure 7).

26. Harmonic Distortion (4-Wire to 2-Wire) - The harmonic distortion is measured with the followingconditions. ERX= 0dBm0.

Vary frequency between 300Hz and 3.4kHz, I

DCMET

= 23mA.

Measurement taken at VTR. (Reference Figure 9).

27. Constant LoopCurrent - The constant loop current is calculated using the following equation:

IL = 2500 / (R

DC1

+ R

DC2

)

28. Standby StateLoopCurrent - The standby state loop current

is calculated using the following equation:

IL = [|V

| - 3] / [RL +1800], TA = 25oC

BAT

29. GroundKeyDetector - (TRIGGER) Increase the input current

to 8mA and verify that DET goes low.

(RESET) Decrease the input current from 17mA to 3mA and

verify that DET goes high.

(Hysteresis) Compare difference between trigger and reset.

30. PowerSupply Rejection Ratio - Inject a 100mV

(50Hz to 4kHz) on V

BAT,VCC

and VEEsupplies. PSRR is com-

RMS

puted using the following equation:

PSRR = 20 • log (VTX/VIN). VTXand VINare defined in Figure 12.

Pin Descriptions

PLCC PDIP SYMBOL DESCRIPTION

1 RING

SENSE

2 7 BGND Battery Ground - To be connectedto zero potential. All loop currentand longitudinal current flow from thisground.

48 VCC5V power supply.

5 9 RINGRLY Ring relay driver output.

610 V

BAT

711 RSGSaturation guard programming resistor pin.

8 12 E1 TTL compatible logic input. The logic state of E1 in conjunction with the logic state of C1 determines which detec-

9 13 E0 TTL compatible logic input. Enables the DET output when set to logic level zero and disables DET output when

11 14 DET Detector output. TTL compatible logic output. A zero logic level indicates that the selected detector was triggered

12 15 C2 TTL compatible logic input. The logic states of C1 and C2 determine the operating states (Open Circuit, Active,

13 16 C1 TTL compatible logic input. The logic states of C1 and C2 determine the operating states (Open Circuit, Active,

14 17 R

DC

15 18 AGND Analog ground.

16 19 RSN Receive Summing Node. The AC and DC current flowing into this pin establishes the metallic loop current that

18 20 V

19 21 V

EE

TX

20 22 HPR RING side of AC/DC separation capacitor CHP.CHPis required to properly separate the ring AC current from the

21 1 HPT TIP side of AC/DC separation capacitor CHP.CHPis required to properly separate the tip AC current from the DC

Internally connected to output of RING power amplifier.

Internally separate from AGND but it is recommended that it is connected to the same potential as AGND.

Battery supply voltage, -24V to -56V.

tor is gated to the DET output.

set to a logic level one.

(see Truth Table for selection of Ground Key detector, Loop Current detector or the Ring Trip detector). The DET

output is an open collector with an internal pull-up of approximately 15kΩ to VCC.

Ringing or Standby) of the SLIC.

Ringing or Standby) of the SLIC.

DC feed current programming resistor pin. Constant current feed is programmed by resistors R

DC1

and R

connected in series from this pin to the receive summing node (RSN). The resistor junction point is decoupled to

AGND to isolate the AC signal components.

flows between tip and ring. The magnitude of the metallic loop current is 1000 times greater than the current into

the RSN pin. The constant current programming resistors and the networks for program receive gain and 2-wire

impedance all connect to this pin.

-5V power supply.

Transmitaudio output. This output is equivalent to the TIP toRINGmetallicvoltage.The network for programming

the 2-wire input impedance connects between this pin and RSN.

DC loop current. The other end of CHPis connected to HPT.

loop current. The other end of CHPis connected to HPR.

signal

DC2

69

HC5513

Pin Descriptions

(Continued)

PLCC PDIP SYMBOL DESCRIPTION

22 2 RD Loopcurrent programming resistor. Resistor RDsets the trigger level for the loop current detect circuit. A filter ca-

pacitor CD is also connected between this pin and VEE.

23 3 DT Input to ring trip comparator. Ring trip detection is accomplished by connecting an external network to a

comparator in the SLIC with inputs DT and DR.

25 4 DR Input to ring trip comparator. Ring trip detection is accomplished by connecting an external network to a

comparator in the SLIC with inputs DT and DR.

26 TIP

SENSE

Internally connected to output of tip power amplifier.

27 5 TIPX Output of tip power amplifier.

28 6 RINGX Output of ring power amplifier.

3, 10

N/C No internal connection.

17, 24

Pinouts

RINGRLY

V

BAT

R

SG

E1

E0

N/C

DET

HC5513

(PLCC)

TOP VIEW

SENSE

VCCN/C

5

6

7

8

9

10

11

BGND

RING

1234

RINGX

TIPX

262728

SENSE

TIP

DR

25

N/C

24

DT

23

RD

22

HPT

21

HPR

20

V

19

TX

HPT

RD

DT

DR

TIPX

RINGX

BGND

V

CC

RINGRLY

V

BAT

R

SG

1

2

3

4

5

6

7

8

9

10

11

HC5513

(PDIP)

TOP VIEW

22

21

20

19

18

17

16

15

14

13

12

HPR

V

TX

V

EE

RSN

AGND

R

DC

C1

C2

DET

E0

E1

12 13 14 15 16 17 18

C1

DC

R

AGND

RSN

N/C

C2

70

EE

V

Application Circuit

HC5513

(V

BAT

R

RT

PTC

PTC

RINGING

+ 90V

TIP

RING

RMS

)

C

R

3

R

4

R

F1

D

3

D

4

R

F2

+5V RELAY

OR

12V

U1 SLIC (Subscriber LineInterface Circuit)

HC5513

U2 Combination CODEC/Filter e.g.

CD22354A or Programmable CODEC/

Filter, e.g. SLAC

CDC1.5µF, 20%, 10V

CHP10nF, 20%, 100V (Note 2)

CRT0.39µF, 20%, 100V

CTC, CRC2200pF, 20%, 100V

Relay Relay, 2C Contacts, 5V or 12V Coil

D1 - D5IN4007 Diode

Surgector SGT27S10

PTC Polyswitch TR600-150

D6Diode, 1N4454

RT

NOTE 31

Surgector

21 HPT

22 RD

23 DT

25 DR

27 TIPX

2 BGND

4 V

CC

28 RINGX

6 V

BAT

5 RINGRLY

7 R

SG

CHP (NOTE 32)

U

1

HPR 20

19

V

TX

18

V

EE

RSN 16

AGND 15

R

14

DC

C1 13

C2 12

DET 11

E

O

E

1

R

FB

U

R

TX

-5V

R

DC2

9

8

R

R

B

T

R

RX

R

DC1

C

DC

2

-

+

CODEC/FILTER

R

1

R

D

R

2

V

BAT

AK

G

D

5

D

6

-5V

D

1

C

TC

C

D

2

RC

V

BAT

R

SG

-5V

RF1, RF2Line Resistor, 20Ω, 1% Match, 2 W

Carbon column resistor or thick film on

ceramic

R1, R3200kΩ, 5%, 1/4W

R2910kΩ, 5%, 1/4W

R41.2MΩ, 5%, 1/4W

RB18.7kΩ,1%, 1/4W

RD39kΩ, 5%, 1/4W

R

DC1

, R

41.2kΩ, 5%, 1/4W

DC2

RFB20.0kΩ, 1%, 1/4W

RRX280kΩ, 1%, 1/4W

RT562kΩ, 1%, 1/4W

RTX20kΩ, 1%, 1/4W

RRT150Ω, 5%, 2W

RSGV

= -28V, RSG= ∞

BAT

V

= -48V, RSG= 21.4kΩ, 1/4W 5%

BAT

NOTES:

31. It is recommended that the anodes of D3 and D4 be shorted to ground through a battery referenced surgector (SGT27S10).

32. To meet the specified 25dB 2-wire return loss at 200Hz, CHP needs to be 20nF, 20%, 100V.

FIGURE 21. APPLICATION CIRCUIT

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only .Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However ,no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

71

Loading...

Loading...