®

www.BDTIC.com/Intersil

HA-5102, HA-5104

Data Sheet October 26, 2004

Dual and Quad, 8MHz, Low Noise

Operational Amplifiers

Low noise and high performance are key words describing

HA-5102 and HA-5104. These general purpose amplifiers

offer an array of dynamic specifications including a 3V/µs

slew rate and 8MHz bandwidth. Complementing these

outstanding parameters is a very low noise specification of

4.3nV/√Hz

at 1kHz.

Fabricated using the Intersil high frequency DI process,

these operational amplifiers also offer excellent input

specifications such as a 0.5mV offset voltage and 30nA

offset current. Complementing these specifications are

108dB open loop gain and 60dB channel separation.

Consuming a very modest amount of power (90mW/

package for duals and 150mW/package for quads),

HA-5102/04 also provide 15mA of output current.

This impressive combination of features make this series of

amplifiers ideally suited for designs ranging from audio

amplifiers and active filters to the most demanding signal

conditioning and instrumentation circuits.

These operational amplifiers are available in dual or quad

form with industry standard pinouts allowing for immediate

interchangeability with most other dual and quad operational

amplifiers.

HA-5102 Dual, Comp. HA-5104 Quad, Comp.

Refer to the /883 data sheet for military product.

Ordering Information

PART NUMBER

(oC) PACKAGE

HA7-5102-2 -55 to 125 8 Ld CERDIP F8.3A

HA1-5104-2 -55 to 125 14 Ld CERDIP F14.3

HA9P5104-9 -40 to 85 16 Ld SOIC M16.3

TEMP. RANGE

PKG.

DWG. #

FN2925.9

Features

• Low Noise . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4.3nV/√Hz

• Bandwidth . . . . . . . . . . . . . . . . . . . 8MHz (Compensated)

• Slew Rate. . . . . . . . . . . . . . . . . . . . 3V/µs (Compensated)

• Low Offset Voltage. . . . . . . . . . . . . . . . . . . . . . . . . 0.5mV

• Available in Duals or Quads

Applications

• High Q, Active Filters

• Audio Amplifiers

• Instrumentation Amplifiers

• Integrators

• Signal Generators

• For Further Design Ideas, See Application Note AN554

Pinouts

HA-5102 (CERDIP)

TOP VIEW

OUT1

1

2

-IN1

+IN1

-

+

3

4

V-

HA-5104 (CERDIP)

TOP VIEW

OUT1

1

-IN1

+IN1

V+

+IN2

-IN2

OUT2

1

2

-

+

3

4

5

+

-

6

2

7

8

V+

7

OUT2

6

-IN2

-

+

5

+IN2

14

OUT4

4

13

-IN4

-

+

12

+IN4

11

V-

10

+IN3

+

9

-IN3

3

8

OUT3

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

HA5104 (SOIC)

TOP VIEW

OUT1

1

-IN1

+IN1

V+

+IN2

-IN2

OUT2

NC

Copyright © Intersil Americas Inc. 2003, 2004. All Rights Reserved

14

2

-

+

3

4

5

+

-

6

23

7

8

OUT4

16

-IN4

15

-

+

+IN4

14

V-

13

+IN3

12

+

11

-IN3

10

OUT3

9

NC

HA-5102, HA-5104

www.BDTIC.com/Intersil

Absolute Maximum Ratings Thermal Information

Supply Voltage Between V+ and V- Terminals. . . . . . . . . . . . . . 40V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7V

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±V

Output Short Circuit Duration (Note 3). . . . . . . . . . . . . . . . Indefinite

SUPPLY

Operating Conditions

Temperature Range

HA-510X-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55

HA-5104-9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -40

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Maximum power dissipation, including output load, must be designed to maintain the maximum junction temperature below 175

packages, and below 150

2. θ

is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

JA

3. Any one amplifier may be shorted to ground indefinitely.

o

C for plastic packages.

o

C to 125oC

o

C to 85oC

Thermal Resistance (Typical, Note 2) θ

8 Lead CERDIP Package. . . . . . . . . . . 115 28

14 Lead CERDIP Package. . . . . . . . . . 75 20

SOIC Package . . . . . . . . . . . . . . . . . . . 100 N/A

Maximum Junction Temperature (Note 1 , Hermetic P ackage) . .175

Maximum Junction Temperature (Plastic Package) . . . . . . . .150

Maximum Storage Temperature Range. . . . . . . . . . -65

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300

(SOIC - Lead Tips Only)

(oC/W) θJC (oC/W)

JA

o

C to 150oC

o

C for hermetic

o

o

o

C

C

C

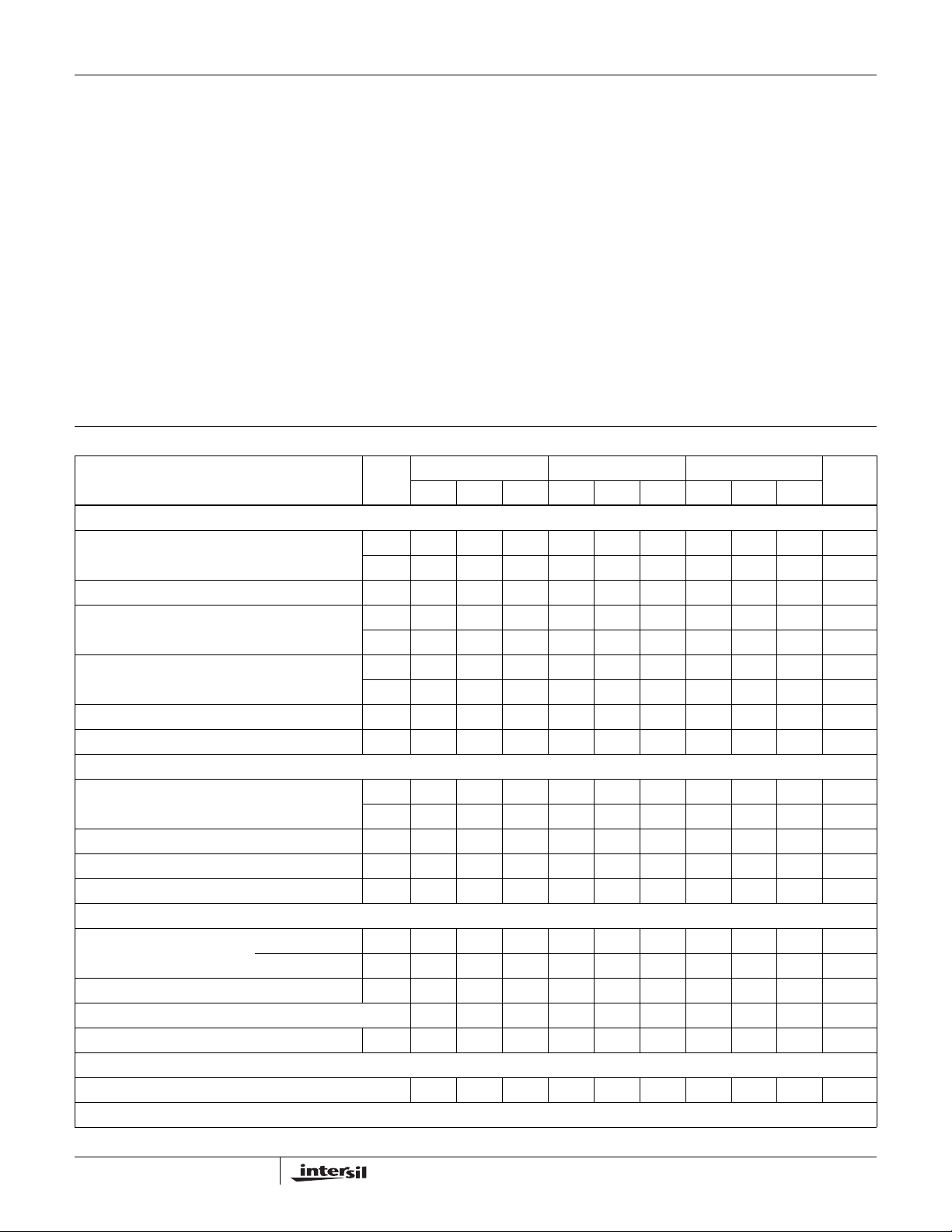

Electrical Specifications V

PARAMETER

INPUT CHARACTERISTICS

Offset Voltage 25 - 0.5 2.0 - 0.5 2.5 - 0.5 2.5 mV

Offset Voltage Average Drift Full - 3 - - 3 - - 3 - µV/

Bias Current 25 - 130 200 - 130 200 - 130 200 nA

Offset Current 25 - 30 75 - 30 75 - 30 75 nA

Input Resistance 25 - 500 - - 500 - - 500 - kΩ

Common Mode Range Full ±12 - - ±12 - - ±12 - - V

TRANSFER CHARACTERISTICS

Large Signal Voltage Gain,

= ±5V, RL = 2kΩ)

(V

OUT

Common Mode Rejection Ratio (V

Small Signal Bandwidth, (A

Channel Separation (Note 4) 25 - 60 - - 60 - - 60 - dB

OUTPUT CHARACTERISTICS

Output Voltage Swing (R

Output Current, (V

Full Power Bandwidth (Note 5) 25 16 47 - 16 47 - 16 47 - kHz

Output Resistance 25 - 110 - - 110 - - 110 - Ω

STABILITY

Minimum Stable Closed Loop Gain Full 1 - - 1 - - 1 - - V/V

TRANSIENT RESPONSE (Note 6)

= ±5V) Full ±10 ±15 - ±10 ±15 - ±7 ±15 - mA

OUT

CM

= 1) 25-8--8--8-MHz

V

L

(R

L

= ±15V, Unless Otherwise Specified

SUPPLY

TEMP.

o

(

C)

Full--2.5--3.0--3.0mV

Full - - 325 - - 325 - - 500 nA

Full - - 125 - - 125 - - 125 nA

25 100 250 - 100 250 - 80 250 - kV/V

Full 100 - - 100 - - 80 - - kV/V

= ±5.0V) Full 86 95 - 86 95 - 80 95 - dB

= 10kΩ)Full±12 ±13 - ±12 ±13 - ±12 ±13 - V

= 2kΩ)Full±10 ±12 - ±10 ±12 - ±10 ±12 - V

HA-5102-2 HA-5104-2 HA-5104-9

UNITSMIN TYP MAX MIN TYP MAX MIN TYP MAX

o

C

2

FN2925.9

HA-5102, HA-5104

www.BDTIC.com/Intersil

Electrical Specifications V

PARAMETER

Rise Time 25 - 108 200 - 108 200 - 108 200 ns

Overshoot 25 - 20 35 - 20 35 - 20 35 %

Slew Rate 25 1 3 - 1 3 - 1 3 - V/µs

Settling Time (Note 7) 25 - 4.5 - - 4.5 - - 4.5 - µs

NOISE CHARACTERISTICS (Note 8)

Input Noise Voltage f = 10Hz 25 - 9 25 - 9 25 - 9 25 nV/√Hz

f = 1kHz 25 - 4.3 6.0 - 4.3 6.0 - 4.3 6.0 nV/√Hz

Input Noise Current f = 10Hz 25 - 5.1 15 - 5.1 15 - 5.1 15 pA/√Hz

f = 1kHz 25 - 0.57 3 - 0.57 3 - 0.57 3 pA/√Hz

Broadband Noise Voltage f = DC to 30kHz 25 - 870 - - 870 - - 870 - nV

POWER SUPPLY CHARACTERISTICS

Supply Current (All Amps) 25 - 3.0 5.0 - 5.0 6.5 - 5.0 6.5 mA

Power Supply Rejection Ratio, (∆V

NOTES:

4. Channel separation value is referred to the input of the amplifier. Input test conditions are: f = 10kHz; V

5. Full power bandwidth is guaranteed by equation: .

6. Refer to Test Circuits section of the data sheet.

7. Settling time is measured to 0.1% of final value for a 10V input step, A

8. The limits for these parameters are guaranteed based on lab characterization, and reflect lot-to-lot variation.

S

= ±15V, Unless Otherwise Specified (Continued)

SUPPLY

TEMP.

o

(

C)

= ±5V) Full 86 100 - 86 100 - 80 100 - dB

Full power bandwidth

HA-5102-2 HA-5104-2 HA-5104-9

= -1.

V

Slew Rate

---------------------------- -=

2π V

PEAK

= 100mV

IN

PEAK

; RS = 1kΩ.

UNITSMIN TYP MAX MIN TYP MAX MIN TYP MAX

RMS

3

FN2925.9

Test Circuits and Waveforms

www.BDTIC.com/Intersil

2kΩ

HA-5102, HA-5104

IN

2kΩ

1kΩ

-

+

50pF

OUTPUT

Vertical = 5V/Div., Horizontal = 5µs/Div. (AV = -1)

FIGURE 1. LARGE SIGNAL RESPONSE CIRCUIT

INPUT

OUT

+5V

0V

-5V

+5V

0V

-5V

IN

+

-

2kΩ

OUTPUT

200mV

INPUT

0V

Vertical = 40mV/Div., Horizontal = 50ns/Div. (AV = +1)

FIGURE 2. SMALL SIGNAL RESPONSE CIRCUIT

50pF

5kΩ

500Ω (NOTE 9)

V

IN

200Ω (NOTE 9)

2kΩ

NOTES:

= -1.

9. A

V

10. Feedback and summing resistors should be 0.1% matched.

11. Clipping diodes are optional, HP5082-2810 recommended.

FIGURE 3. SETTLING TIME CIRCUIT

+15V

2N4416

5kΩ

+15V

+

TO

OSCILLOSCOPE

2kΩ

V

OUT

-

-15V

2kΩ

50pF

4

FN2925.9

Simplified Schematic

www.BDTIC.com/Intersil

V+

HA-5102, HA-5104

OUTPUT

V-

Typical Performance Curves

15

VS = ±15V, TA = 25oC

HIGH

10

TYPICAL

LOW

5

NOISE VOLTAGE (nV/√Hz)

0

10 100 1K

FREQUENCY (Hz)

FIGURE 4. INPUT NOISE VOLTAGE DENSITY

-INPUT+INPUT

10

VS = ±15V, TA = 25oC

5.0

1.0

0.5

NOISE CURRENT (pA/√Hz)

0.1

10 100 1K

FREQUENCY (Hz)

FIGURE 5. INPUT NOISE CURRENT DENSITY

5

FN2925.9

Typical Performance Curves (Continued)

www.BDTIC.com/Intersil

HA-5102, HA-5104

VS = ±15V, TA = 25oC, 50µV/Div., 1s/Div., AV = 1000V/V

INPUT OFFSET VOLTAGE (mV)

INPUT OFFSET CURRENT (nA)

2.0

1.5

1.0

0.5

-10

-12

-14

-16

-18

-20

-22

-24

-26

V

0

-60 20 1201008060400-20-40

4

2

VS = ±15V

0

-2

-4

-6

-8

-60 20 1201008060400-20-40

Input Noise = 0.232µV

FIGURE 6. 0.1Hz TO 10Hz NOISE

= ±15V

S

TEMPERATURE (

FIGURE 8. V

vs TEMPERATURE

IO

TEMPERATURE (

P-P

o

o

C)

C)

V

= ±15V, TA = 25oC, 500µV/Div., 1s/Div., AV = 1000V/V

S

2.0

1.5

1.0

0.5

OFFSET VOLTAGE (mV)

0

08 1816141210642

100

90

80

70

60

50

40

30

INPUT BIAS CURRENT (nA)

20

10

0

-60 20 1201008060400-20-40

Total Output Noise = 2.075µV

FIGURE 7. 0.1Hz TO 1MHz NOISE

TA = 25oC

SUPPLY VOLTAGE (±V)

FIGURE 9. V

VS = ±15V

TEMPERATURE (

IO

vs V

P-P

S

o

C)

FIGURE 10. IIO vs TEMPERATURE FIGURE 11. I

6

vs TEMPERATURE

BIAS

FN2925.9

Typical Performance Curves (Continued)

www.BDTIC.com/Intersil

HA-5102, HA-5104

5

4

3

2

1

TOTAL SUPPLY CURRENT (mA)

0

-60 20 1201008060400-20-40

VS = ±15V, I

= 0

OUT

TEMPERATURE (oC)

TOTAL SUPPLY CURRENT (mA)

5

4

3

2

1

0

08 1816141210642

TA = 25oC, I

= 0

OUT

SUPPLY VOLTAGE (±V)

FIGURE 12. ICC vs TEMPERATURE (HA-5104) FIGURE 13. ICC vs VS (HA-5102)

5

VS = ±15V, ∆VO = ±10V, RL = 2kΩ

V/V)

5

4

3

5.5

VO = ±10V, VS = ±15V

5.0

V/V)

5

4.0

125oC

25oC

2

1

OPEN LOOP VOLTAGE GAIN (10

0

-60 20 1201008060400-20-40

290

TA = 25oC, RL = 2kΩ

280

270

260

250

240

230

220

210

200

190

180

170

OPEN LOOP GAIN (kV/V)

160

150

140

130

08 1816141210642

FIGURE 14. A

SUPPLY VOLTAGE (±V)

3.0

OPEN LOOP VOLTAGE GAIN (10

2.0

TEMPERATURE (

vs TEMPERATURE FIGURE 15. A

VOL

o

C)

1K 10K8K6K4K2K

13

TA = 25oC, RL = 2kΩ

12

11

10

9

8

7

6

5

4

3

MAX OUTPUT SWING (±V)

2

1

0

08 1816141210642

-55oC

LOAD RESISTANCE (Ω)

vs LOAD RESISTANCE

VOL

SUPPLY VOLTAGE (±V)

FIGURE 16. A

VOL

vs V

S

7

FIGURE 17. V

OUT

vs V

S

FN2925.9

Typical Performance Curves (Continued)

www.BDTIC.com/Intersil

HA-5102, HA-5104

OUTPUT CURRENT (mA)

45

VS = ±15V, TA = 25oC

40

35

30

25

20

0200 45040035030025015010050

V

= +15V

OUT

TIME (SECONDS)

V

OUT

= -15V

0

-20

-40

-60

CMRR (dB)

-80

-100

1K 1M100K10K

FREQUENCY (Hz)

FIGURE 18. OUTPUT SHORT CIRCUIT CURRENT vs TIME FIGURE 19. CMRR vs FREQUENCY

POWER SUPPLY REJECTION (dB)

-100

-20

-40

-60

-80

0

+PSRR

-PSRR

1M100K10K1K

FREQUENCY (Hz)

6

VS = ±15V, RL = 2kΩ, CL = 50pF

0

-3

-6

-12

VOLTAGE GAIN (dB)

-18

-24

10K

125oC

GAIN

125oC

PHASE

FREQUENCY (Hz)

-55oC

PHASE

-55oC

GAIN

225

135

45

0

-45

PHASE SHIFT (DEGREES)

-135

-225

40M10M1M100K

FIGURE 20. PSRR vs FREQUENCY FIGURE 21. UNITY GAIN FREQUENCY RESPONSE

60

VS = ±15V, TA = 25oC, RL = 2kΩ

50

40

30

20

OVERSHOOT (%)

10

0

10 100 1K 10K

LOAD CAPACITANCE (pF)

VOLTAGE GAIN (dB)

120

100

VS = ±15V, TA = 25oC,

= 2kΩ, CL = 50pF

R

80

GAIN

60

40

20

0

PHASE

FREQUENCY (Hz)

L

0

45

90

135

PHASE SHIFT (DEGREES)

1M100K10K1K 10M 100M100

180

FIGURE 22. OPEN LOOP GAIN vs FREQUENCY FIGURE 23. SMALL SIGNAL OVERSHOOT vs C

8

LOAD

FN2925.9

Typical Performance Curves (Continued)

www.BDTIC.com/Intersil

HA-5102, HA-5104

1.1

RL = 2kΩ, CL = 50pF, VS = ±15V

1.0

0.9

0.8

0.7

SLEW RATE (NORMALIZED)

0.6

-60 20 1201008060400-20-40

TEMPERATURE (oC)

FIGURE 24. SLEW RATE vs TEMPERATURE

Die Characteristics

DIE DIMENSIONS:

98.4 mils x 67.3 mils x 19 mils

2500µm x 1710µm x 483µm

METALLIZATION:

Type: Al, 1% Cu

Thickness: 16kÅ ±2kÅ

1.1

RL = 2kΩ, CL = 50pF , VS = ±15V

1.0

0.9

0.8

0.7

RISE TIME (NORMALIZED)

0.6

-60 20 1201008060400-20-40

TEMPERATURE (

FIGURE 25. RISE TIME vs TEMPERATURE

o

C)

PASSIVATION:

Type: Nitride (Si

) over Silox (SiO2, 5% Phos.)

3N4

Silox Thickness: 12kÅ ±2kÅ

Nitride Thickness: 3.5kÅ ±1.5kÅ

SUBSTRATE POTENTIAL (POWERED UP):

Unbiased

TRANSISTOR COUNT:

93

Metallization Mask Layout

V- +IN1 -IN1 OUT1

+IN2 -IN2 OUT2 V+

PROCESS:

Bipolar Dielectric Isolation

HA-5102

9

FN2925.9

HA-5102, HA-5104

www.BDTIC.com/Intersil

Die Characteristics

DIE DIMENSIONS:

95 mils x 99 mils x 19 mils

2420µm x 2530µm x 483µm

METALLIZATION:

Type: Al, 1% Cu

Thickness: 16kÅ ±2kÅ

PASSIVATION:

Type: Nitri de (Si

Silox Thickness: 12k

Nitride Thickness: 3.5kÅ ±1.5kÅ

) over Silox (SiO2, 5% Phos.)

3N4

Å ±2kÅ

Metallization Mask Layout

-IN2

SUBSTRATE POTENTIAL (POWERED UP):

Unbiased

TRANSISTOR COUNT:

175

PROCESS:

Bipolar Dielectric Isolation

HA-5104

+IN2 V+ +IN1

-IN1

OUT2

OUT3

-IN3

OUT1

OUT4

-IN4

+IN4V-+IN3

10

FN2925.9

HA-5102, HA-5104

www.BDTIC.com/Intersil

Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

c1

LEAD FINISH

-A-

-B-

bbb C A - B

S

BASE

PLANE

SEATING

PLANE

S1

b2

b

ccc C A - BMD

D

A

A

e

S

S

NOTES:

1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded

area shown. The manufacturer’s identification shall not be used

as a pin one identification mark.

2. The maximum limits of lead dimensions b and c or M shall be

measured at the centroid of the finished lead surfaces, when

solder dip or tin plate lead finish is applied.

3. Dimensions b1 and c1 apply to lead base metal only. Dimension

M applies to lead plating and finish thickness.

4. Corner leads (1, N, N/2, and N/2+1) may be configured with a

partial lead paddle. For this configuration dimension b3 replaces

dimension b2.

5. This dimension allows for off-center lid, meniscus, and glass

overrun.

6. Dimension Q shall be measured from the seating plane to the

base plane.

7. Measure dimension S1 at all four corners.

8. N is the maximum number of terminal positions.

9. Dimensioning and tolerancing per ANSI Y14.5M - 1982.

10. Controlling dimension: INCH

-DBASE

E

D

S

S

Q

A

-CL

METAL

b1

M

(b)

SECTION A-A

α

(c)

M

eA

eA/2

aaa CA - B

M

c

D

S

S

F8.3A MIL-STD-1835 GDIP1-T8 (D-4, CONFIGURATION A)

8 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.200 - 5.08 -

b 0.014 0.026 0.36 0.66 2

b1 0.014 0.023 0.36 0.58 3

b2 0.045 0.065 1.14 1.65 b3 0.023 0.045 0.58 1.14 4

c 0.008 0.018 0.20 0.46 2

c1 0.008 0.015 0.20 0.38 3

D - 0.405 - 10.29 5

E 0.220 0.310 5.59 7.87 5

e 0.100 BSC 2.54 BSC -

eA 0.300 BSC 7.62 BSC -

eA/2 0.150 BSC 3.81 BSC -

L 0.125 0.200 3.18 5.08 -

Q 0.015 0.060 0.38 1.52 6

S1 0.005 - 0.13 - 7

o

α

90

105

o

90

o

105

aaa - 0.015 - 0.38 bbb - 0.030 - 0.76 ccc - 0.010 - 0.25 -

M - 0.0015 - 0.038 2, 3

N8 88

NOTESMIN MAX MIN MAX

o

Rev. 0 4/94

-

11

FN2925.9

HA-5102, HA-5104

www.BDTIC.com/Intersil

Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

LEAD FINISH

c1

-A-

-B-

bbb C A - B

S

BASE

PLANE

SEATING

PLANE

S1

b2

b

ccc C A - BMD

D

A

A

e

S

S

NOTES:

1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded

area shown. The manufacturer’s identification shall not be used

as a pin one identification mark.

2. The maximum limits of lead dimensions b and c or M shall be

measured at the centroid of the finished lead surfaces, when

solder dip or tin plate lead finish is applied.

3. Dimensions b1 and c1 apply to lead base metal only. Dimension

M applies to lead plating and finish thickness.

4. Corner leads (1, N, N/2, and N/2+1) may be configured with a

partial lead paddle. For this configuration dimension b3 replaces

dimension b2.

5. This dimension allows for off-center lid, meniscus, and glass

overrun.

6. Dimension Q shall be measured from the seating plane to the

base plane.

7. Measure dimension S1 at all four corners.

8. N is the maximum number of terminal positions.

9. Dimensioning and tolerancing per ANSI Y14.5M - 1982.

10. Controlling dimension: INCH.

-DBASE

E

D

S

S

Q

A

-CL

METAL

b1

M

(b)

SECTION A-A

α

(c)

M

eA

eA/2

aaa CA - B

M

c

D

S

S

F14.3 MIL-STD-1835 GDIP1-T14 (D-1, CONFIGURATION A)

14 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.200 - 5.08 -

b 0.014 0.026 0.36 0.66 2

b1 0.014 0.023 0.36 0.58 3

b2 0.045 0.065 1.14 1.65 b3 0.023 0.045 0.58 1.14 4

c 0.008 0.018 0.20 0.46 2

c1 0.008 0.015 0.20 0.38 3

D - 0.785 - 19.94 5

E 0.220 0.310 5.59 7.87 5

e 0.100 BSC 2.54 BSC -

eA 0.300 BSC 7.62 BSC -

eA/2 0.150 BSC 3.81 BSC -

L 0.125 0.200 3.18 5.08 -

Q 0.015 0.060 0.38 1.52 6

S1 0.005 - 0.13 - 7

o

α

90

105

o

90

o

105

aaa - 0.015 - 0.38 bbb - 0.030 - 0.76 -

ccc - 0.010 - 0.25 -

M - 0.0015 - 0.038 2, 3

N14 148

NOTESMIN MAX MIN MAX

o

Rev. 0 4/94

-

12

FN2925.9

HA-5102, HA-5104

www.BDTIC.com/Intersil

Small Outline Plastic Packages (SOIC)

N

INDEX

AREA

123

-AD

e

B

0.25(0.010) C AM BS

NOTES:

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead

flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater above

the seating plane, shall not exceed a maximum value of 0.61mm (0.024

inch)

10. Controlling dimension: MILLIMETER. Converted inch dimensions are

not necessarily exact.

E

-B-

SEATING PLANE

A

-C-

M

0.25(0.010) BM M

H

α

µ

A1

0.10(0.004)

L

h x 45

o

C

M16.3 (JEDEC MS-013-AA ISSUE C)

16 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.0926 0.1043 2.35 2.65 -

A1 0.0040 0.0118 0.10 0.30 -

B 0.013 0.0200 0.33 0.51 9

C 0.0091 0.0125 0.23 0.32 D 0.3977 0.4133 10.10 10.50 3

E 0.2914 0.2992 7.40 7.60 4

e 0.050 BSC 1.27 BSC H 0.394 0.419 10.00 10.65 h 0.010 0.029 0.25 0.75 5

L 0.016 0.050 0.40 1.27 6

N16 167

o

α

0

o

8

o

0

o

8

Rev. 0 12/93

NOTESMIN MAX MIN MAX

-

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

13

FN2925.9

Loading...

Loading...