Intersil Corporation HA-2406 Datasheet

HA-2406

Data Sheet April 1999

30MHz, Digitally Selectable Four Channel

Operational Amplifier

The HA-2406 is a monolithic device consisting of four op

amp input stages that can be individually connected to one

output stage by decoding two TTL lines into four channel

select signals. In addition to allowing each channel to be

addressed, an enable control disconnects all input stages

from the output stage when asserted low.

Each input-output combination of the HA-2406 is designed

to be a 20V/µs, 30MHz gain-bandwidth amplifier that is

stable at a gain of ten. By connecting one external 15pF

capacitor all amplifiers are compensated for unity gain

operation. The compensation lead may also be used to limit

the output swing to TTL levels through suitable clamping

diodes and divider networks (see Application Note AN514).

Dielectric isolation and short-circuit protected output stages

contribute to the quality and durability of the HA-2406. When

used as a simple amplifier, its dynamic performance is very

good and when its added versatility is considered, the

HA-2406 is unmatched in the analog world. It can replace a

number of individual components in analog signal

conditioning circuits for digital signal processing systems. Its

advantages include saving board space and reducing power

supply requirements.

During Disable Mode V

goes to V-. For high output

OUT

impedance during Disable, see HA2444.

For further design ideas, see Application Note AN514.

Pinout

HA-2406

(PDIP)

TOP VIEW)

+IN3

-IN3

+IN4

-IN4

-IN1

+IN1

+

1

3

3

2

-

3

+

4

4

-

-

5

1

6

+

DECODE

CONTROL

16

15

14

13

12

11

D0

D1

ENABLE

GND

COMP

V+

File Number 2892.4

Features

• TTL Compatible Inputs

• Single Capacitor Compensation

• Low Crosstalk. . . . . . . . . . . . . . . . . . . . . . . . . . . . . -110dB

• High Slew Rate. . . . . . . . . . . . . . . . . . . . . . . . . . . . 20V/µs

• Low Offset Current. . . . . . . . . . . . . . . . . . . . . . . . . . . 5nA

• Offset Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7mV

• High Gain-Bandwidth . . . . . . . . . . . . . . . . . . . . . . . 30MHz

• High Input Impedance . . . . . . . . . . . . . . . . . . . . . . .30MΩ

• Compensation Pin for Unity Gain Capability

Applications

• Digital Control Of

- Analog Signal Multiplexing

- Op Amp Gains

- Oscillator Frequencies

- Filter Characteristics

- Comparator Levels

Ordering Information

TEMPRANGE

PART NO.

HA3-2406-5 0 to 75 16 Ld PDIP E16.3

D1 D0 EN SELECTED CHANNEL

LLH 1

LHH 2

HLH 3

HHH 4

X X L None, V

(oC) PACKAGE PKG. NO.

TRUTH TABLE

goes to V-

OUT

-IN2

+IN2

7

-

2

8

+

OUTPUT AMP

1

10

OUTPUT

9

V-

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Copyright © Intersil Corporation 1999

HA-2406

Absolute Maximum Ratings T

Supply Voltage Between V+ and V- Terminals. . . . . . . . . . . . . . 45V

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . V

Output Current. . . . . . . . . . . Short Circuit Protected (ISC < ±33mA)

= 25oC Thermal Information

A

Thermal Resistance (Typical, Note 1) θJA (oC/W)

SUPPLY

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Maximum Junction Temperature (Plastic Package). . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Operating Conditions

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

Temperature Range

HA-2406-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0oC to 75oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

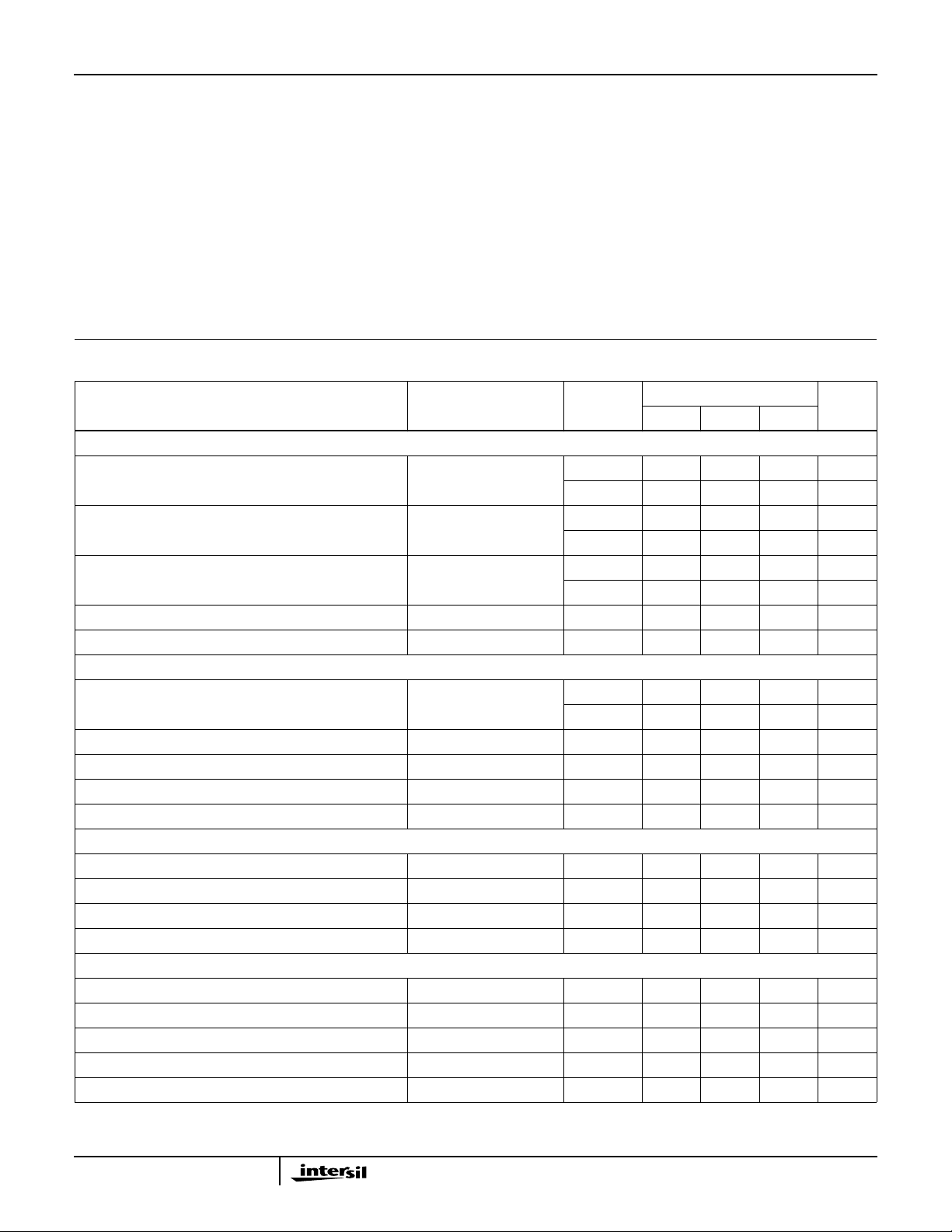

Electrical Specifications Test Conditions: V

= ±15.0V, Unless Otherwise Specified. Digital Inputs: VIL = +0.5V, VIH = +2.4V. Lim-

SUPPLY

its apply to each of the four channels, when addressed.

HA-2406-5

UNITSMIN TYP MAX

PARAMETER

TEST

CONDITIONS TEMP (oC)

INPUT CHARACTERISTICS

Offset Voltage 25 - 7 10 mV

Full - - 12 mV

Bias Current (Note 7) 25 - 50 250 nA

Full - - 500 nA

Offset Current (Note 7) 25 - 5 50 nA

Full - - 100 nA

Input Resistance (Note 7) 25 - 30 - MΩ

Common Mode Range Full ±9.0 - - V

TRANSFER CHARACTERISTICS

Large Signal Voltage Gain RL = 2kΩ

V

= 20V

OUT

P-P

25 40 150 - kV/V

Full 20 - - kV/V

Common Mode Rejection Ratio VCM = ±5V Full 74 80 - dB

Gain Bandwidth Product (Notes 2, 9) 25 15 30 - MHz

Gain Bandwidth Product (Notes 3, 9) 25 3 6 - MHz

Minimum Stable Gain C

= 0 10 - - V/V

COMP

OUTPUT CHARACTERISTICS

Output Voltage Swing RL = 2kΩ Full ±10.0 ±12.0 - V

Output Current V

Full Power Bandwidth (Notes 2, 8, 9) V

Full Power Bandwidth (Notes 3, 8) V

= ±10V 25 10 15 - mA

OUT

OUT

OUT

= 20V

= 20V

P-P

P-P

25 240 320 - kHz

25 64 95 - kHz

TRANSIENT RESPONSE (Note 10)

Rise Time (Note 3) V

Overshoot (Note 3) V

Slew Rate (Notes 2, 9) V

Slew Rate (Note 3) V

Settling Time (Notes 3, 4) V

OUT

OUT

OUT

OUT

OUT

= 200mV

= 200mV

= 10V

= 10V

= 10V

P-P

P-P

P-P

PEAK

PEAK

25 - 30 100 ns

25 - 25 40 %

25 15 20 - V/µs

25 4 6 - Vµs

25 - 2.0 3.5 µs

2

HA-2406

Electrical Specifications Test Conditions: V

= ±15.0V, Unless Otherwise Specified. Digital Inputs: VIL = +0.5V, VIH = +2.4V. Lim-

SUPPLY

its apply to each of the four channels, when addressed. (Continued)

HA-2406-5

UNITSMIN TYP MAX

PARAMETER

TEST

CONDITIONS TEMP (oC)

CHANNEL SELECT CHARACTERISTICS

Digital Input Current VIN = 0V Full - 1 1.5 mA

Digital Input Current VIN = +5.0V Full - 15 - nA

Output Delay (Notes 5, 9) 25 - 150 300 ns

Crosstalk (Note 6) 25 -74 -110 - dB

POWER SUPPLY CHARACTERISTICS

Supply Current 25 - 4.8 7.0 mA

Power Supply Rejection Ratio VS = ±10V to ±20V Full 74 90 - dB

NOTES:

2. AV = +10, C

3. AV = +1, C

= 0, RL = 2kΩ, CL = 50pF.

COMP

= 15pF, RL = 2kΩ, CL = 50pF.

COMP

4. To 0.1% of final value.

5. To 10% of final value; output then slews at normal rate to final value.

6. Unselected input to output; VIN = ±10V.

7. Unselected channels have approximately the same input parameters.

8. Full power Bandwidth based on slew rate measurement using: .

FPBW

9. Sample tested.

Slew Rate

---------------------------- -=

2πV

PEAK

10. See Figure 13 for test circuit.

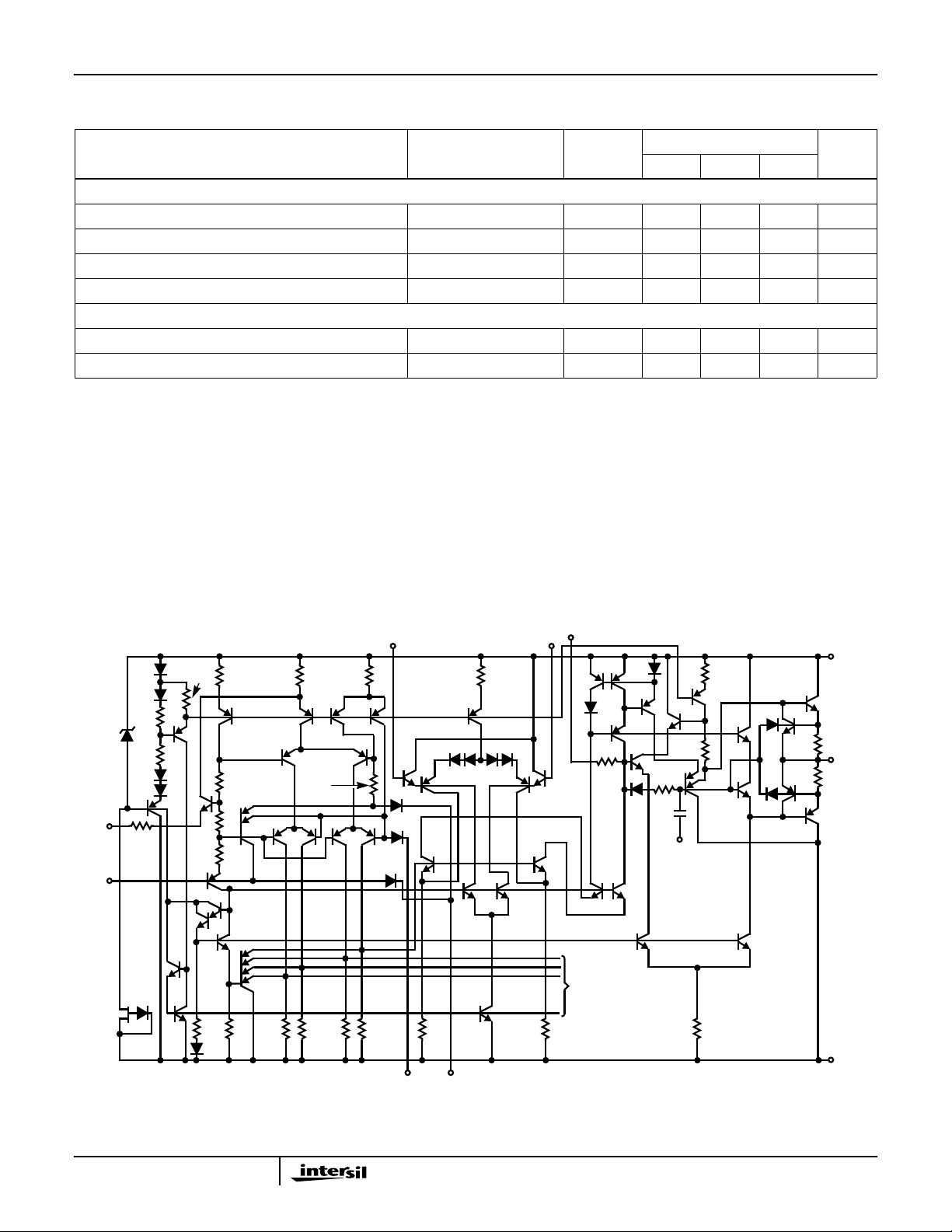

Schematic Diagram

R

Q

2

R

GND

Q

2

ENABLE

Q

R

1.8K

22.9K

R

35

1.6K

Q

1

3

3

Q

R

4

Q

6

Q

7

Q

8

14

Q

15

2.4K

4

Q

9

2.0K

1

1.6K

Q

5

R

5

8.0K

R

6

R

7

5.6K

Q

10

Q

11

Q

Q

12

R

8

4K

R

Q

16

1.5K

COMPIN-IN+

Q

Q

R

0.75K

Q

88

82

Q

81

Q

84

Q

80

Q

35

Q

Q

85

83

87

89

Q

86

R

1.2K

9.0pF

Q

90

30

C

1

V+

R

0.4K

R

33

4K

29

VB

R

12

1.6K

Q

VE

28

Q

27

Q

18

Q

19

VD

13

Q

17

R

10

10K

9

R

13

0.8K

Q

29

Q

30

Q

26

R

14

10K

Q

Q

21

20

Q

VC

VA

R

11

10K

R

15

10K

Q

32

Q

25

22

Q

24

Q

23

R

16

10K

R

18

2.0K

Q

31

Q

Q

102

35

Q

Q

34

103

Q

Q

33

Q

38

R

17

1.6K

36

Q

39

Q

40

Q

42

R

1.6K

D1D0

19

Q

Q

37

Q

41

TO ADDITIONAL

INPUT STAGES

79

Diagram Includes: One Input Stage, Decode Control, Bias Network, and Output Stage

+V

CC

R

34

1.6K

Q

98

Q

Q

99

Q

97

92

Q

Q

93

94

Q

91

Q

101

R

100

95

32

34

OUT

R

31

36.5

Q

96

-V

EE

Q

Q

3

Loading...

Loading...