查询EL8170供应商

®

EL8170, EL8173

Data Sheet January 3, 2006

Micropower, Single Supply, Rail-to-Rail

Input-Output Instrumentation Amplifiers

The EL8170 and EL8173 are micropower instrumentation

amplifiers optimized for operation at 2.9V to 5V single

supplies. Inputs and outputs can operate rail-to-rail. As with

all instrumentation amplifiers, a pair of inputs provide very

high common-mode rejection and are completely

independent from a pair of feedback terminals. The

feedback terminals allow zero input to be translated to any

output offset, including ground. A feedback divider controls

the overall gain of the amplifier.

The EL8170 is compensated for a gain of 100 or more, and

the EL8173 is compensated for a gain of 10 or more. The

EL8170 and EL8173 have bipolar input devices for best

offset and 1/f noise performance.

The amplifiers can be operated from one lithium cell or two

Ni-Cd batteries. The EL8170 and EL8173 input range

includes ground to slightly above positive rail. The output

stage swings to ground and positive supply - no pull-up or

pull-down resistors are needed.

Pinout

EL8170, EL8173

(8 LD SO)

TOP VIEW

ENABLE

IN-

IN+

1

2

+

3

+

8

FB+

-

-

7

Σ

VS+

OUT

6

FN7490.0

Features

• 78µA maximum supply current

• Maximum offset voltage

- 250µV (EL8170)

- 1000µV (EL8173)

• 500pA input bias current

• 2µV/°C offset voltage drift

• 396kHz -3dB bandwidth (G = 10)

• 192kHz -3dB bandwidth (G = 100)

• 0.5V/µs slew rate

• Single supply operation

- Input voltage range is rail-to-rail

- Output swings rail-to-rail

• Output sources and sinks ±29mA load current

• 0.2% gain error

• Pb-free plus anneal available (RoHS compliant)

Applications

• Battery- or solar-powered systems

• Strain gauges

• Current monitors

• Thermocouple amplifiers

VS-

4

1

5

FB-

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Copyright © Intersil Americas Inc. 2006. All Rights Reserved.

Ordering Information

EL8170, EL8173

PAR T

PART NUMBER

EL8170IS 8170IS - 8 Ld SO MDP0027 EL8173IS 8173IS - 8 Ld SO MDP0027

EL8170IS-T7 8170IS 7” 8 Ld SO MDP0027 EL8173IS-T7 8173IS 7” 8 Ld SO MDP0027

EL8170IS-T13 8170IS 13” 8 Ld SO MDP0027 EL8173IS-T13 8173IS 13” 8 Ld SO MDP0027

EL8170ISZ

(See Note)

EL8170ISZ-T7

(See Note)

EL8170ISZ-T13

(See Note)

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate

termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

MARKING

8170ISZ - 8 Ld SO

8170ISZ 7” 8 Ld SO

8170ISZ 13” 8 Ld SO

TAPE &

REEL PACKAGE

(Pb-free)

(Pb-free)

(Pb-free)

PKG.

DWG. # PART NUMBER

MDP0027 EL8173ISZ

(See Note)

MDP0027 EL8173ISZ-T7

(See Note)

MDP0027 EL8173ISZ-T13

(See Note)

PART

MARKING

8173ISZ - 8 Ld SO

8173ISZ 7” 8 Ld SO

8173ISZ 13” 8 Ld SO

TAPE &

REEL PACKAGE

(Pb-free)

(Pb-free)

(Pb-free)

PKG.

DWG. #

MDP0027

MDP0027

MDP0027

Pin Description

EL8170/EL8173 PIN NAME PIN FUNCTION

1ENABLE

2 IN- Inverting (IN-) and non-inverting (IN+) high impedance input terminals.

3IN+

4 VS- Negative supply terminal.

5 FB- High impedance feedback terminals. The feedback terminals have a very similar equivalent

8FB+

7 VS+ Positive supply terminal.

6 VOUT Output Voltage.

Active Low. When pulled up above 2V, the in-amp conserves 3µA disabled supply current and

the output is in a high impedance state. An internal pull down defines the ENABLE

left floating.

circuit as the input terminals. They also have an Input Bias Compensation/Cancelling Circuit.

The negative feedback (FB-) pin connects to an external resistive network to set the gain of

the in-amp. The positive feedback (FB+) can be used to shift the DC level of the output or as

an output offset.

low when

2

FN7490.0

January 3, 2006

EL8170, EL8173

Absolute Maximum Ratings (T

Supply Voltage, V

Differential Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5mA

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5V

V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . - 0.5V, VS+ + 0.5V

EN

ESD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3kV

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests

are at the specified temperature and are pulsed tests, therefore: T

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.5V

S

Electrical Specifications V

= 25°C)

A

Output Short-Circuit Duration . . . . . . . . . . . . . . . . . . . . . . .Indefinite

Ambient Operating Temperature . . . . . . . . . . . . . . . . -40°C to +85°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150°C

= TC = T

J

+ = +5V, VS- = GND, VCM = 1/2VS+, TA = 25°C, unless otherwise specified.

S

A

PARAMETER DESCRIPTION CONDITIONS MIN TYP MAX UNIT

V

OS

Input Offset Voltage EL8170 100 250 µV

EL8173 400 1000 µV

TCV

OS

Input Offset Voltage Temperature

Temperature = -40°C to 85°C 2 µV/°C

Coefficient

I

OS

I

B

Input Offset Current between IN+, and

IN- and between FB+ and FB-

Input Bias Current (IN+, IN-, FB+, and

0.5 2 nA

0.5 2 nA

FB- terminals)

e

N

Input Noise Voltage EL8170 f = 0.1Hz to 10Hz 2 µV

EL8173 10 µV

P-P

P-P

Input Noise Voltage Density fo = 1kHz 50 nV/√Hz

R

IN

Input Resistance EL8170 8 MΩ

EL8173 14 MΩ

V

IN

Input Voltage Range Guaranteed by CMRR test 0 5 V

CMRR Common Mode Rejection Ratio EL8170 VCM = 0V to +5V 80 108 dB

EL8173 80 104 dB

PSRR Power Supply Rejection Ratio EL8170 V

= 2.9V to 5V 80 104 dB

S

EL8173 70 90 dB

E

G

Gain Error EL8170 RL = 100kΩ to 2.5V -1.5 +0.3 +1.5 %

EL8173 -0.8 +0.2 +0.8 %

V

OUT

Maximum Voltage Swing Output low, 100kΩ to 2.5V 0 4 10 mV

Output low, 1kΩ to 2.5V 0.13 0.25 V

Output high, 100kΩ to 2.5V 4.990 4.996 V

Output high, 1kΩ to GND 4.75 4.88 V

SR Slew Rate R

= 1kΩ to GND 0.3 0.5 0.7 V/µs

L

3

FN7490.0

January 3, 2006

EL8170, EL8173

Electrical Specifications V

+ = +5V, VS- = GND, VCM = 1/2VS+, TA = 25°C, unless otherwise specified. (Continued)

S

PARAMETER DESCRIPTION CONDITIONS MIN TYP MAX UNIT

-3dB BW -3dB Bandwidth EL8170 Gain = 100V/V 192 kHz

Gain = 200 93 kHz

Gain = 500 30 kHz

Gain = 1000 13 kHz

EL8173 Gain = 10 396 kHz

Gain = 20 221 kHz

Gain = 50 69 kHz

Gain = 100 30 kHz

I

S,EN

I

S,DIS

V

ENH

V

ENL

V

S

I

O

Supply Current, Enabled 40 60 78 µA

Supply Current, Disabled EN = VS+1.52.95µA

Enable Pin for Shut-down 2 V

Enable Pin for Power-on 0.8 V

Minimum Supply Voltage 2.2 2.4 V

Output Current into 10Ω to VS/2 VS = 5V ±18 ±29 mA

V

= 2.9V ±4 ±7.5 mA

S

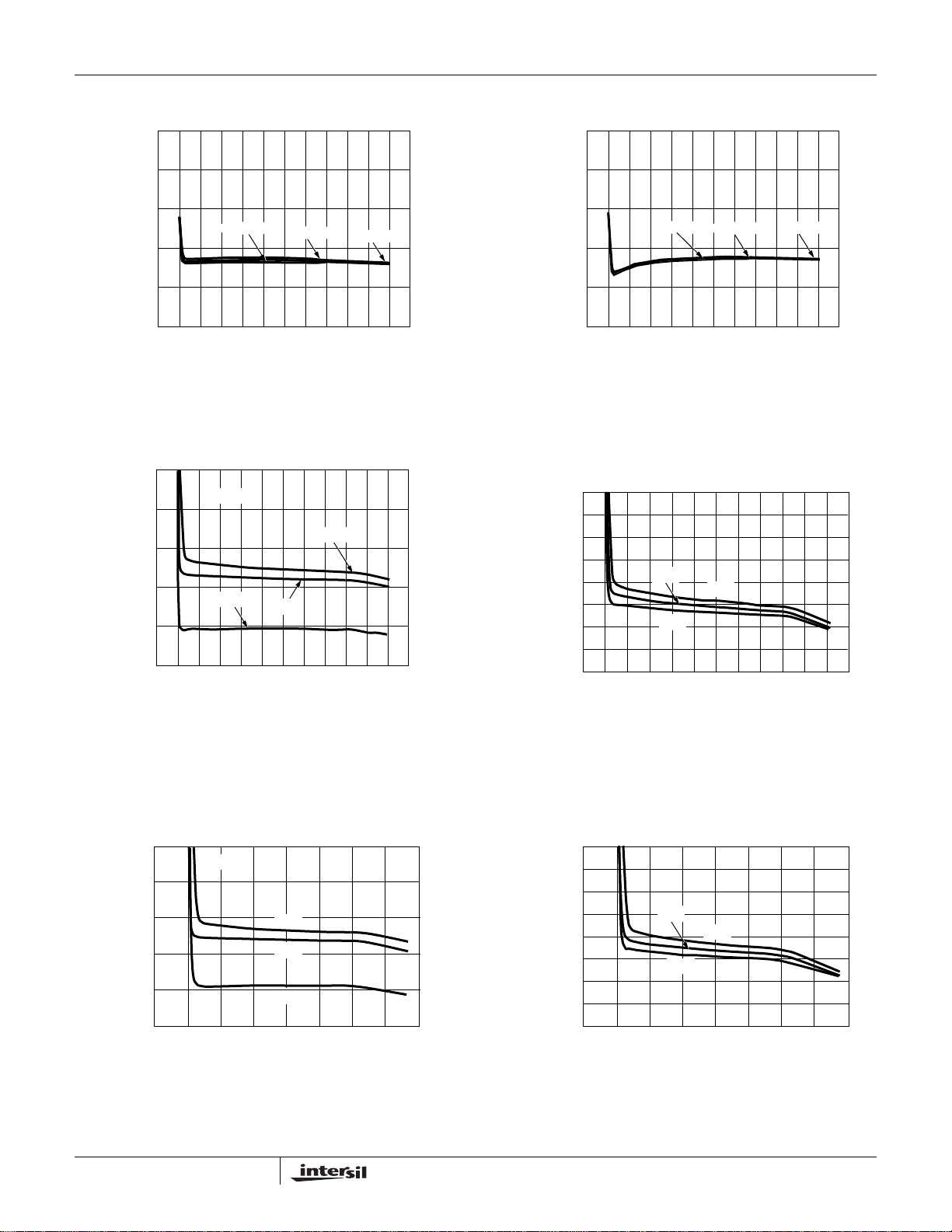

Typical Performance Curves

65

60

55

50

45

40

GAIN (dB)

35

30

25

20

1 10 100 1k 10k 100k 1M

FIGURE 1. EL8170 FREQUENCY RESPONSE vs CLOSED

G=1000

G=500

G=200

G=100

G=50

VS=5V

FREQUENCY (Hz)

LOOP GAIN

45

40

35

30

25

20

GAIN (dB)

15

10

5

0

1 10 100 1k 10k 100k 1M

G=100

G=50

G=20

G=10

G=5

VS=5V

FREQUENCY (Hz)

FIGURE 2. EL8173 FREQUENCY RESPONSE vs CLOSED

LOOP GAIN

4

FN7490.0

January 3, 2006

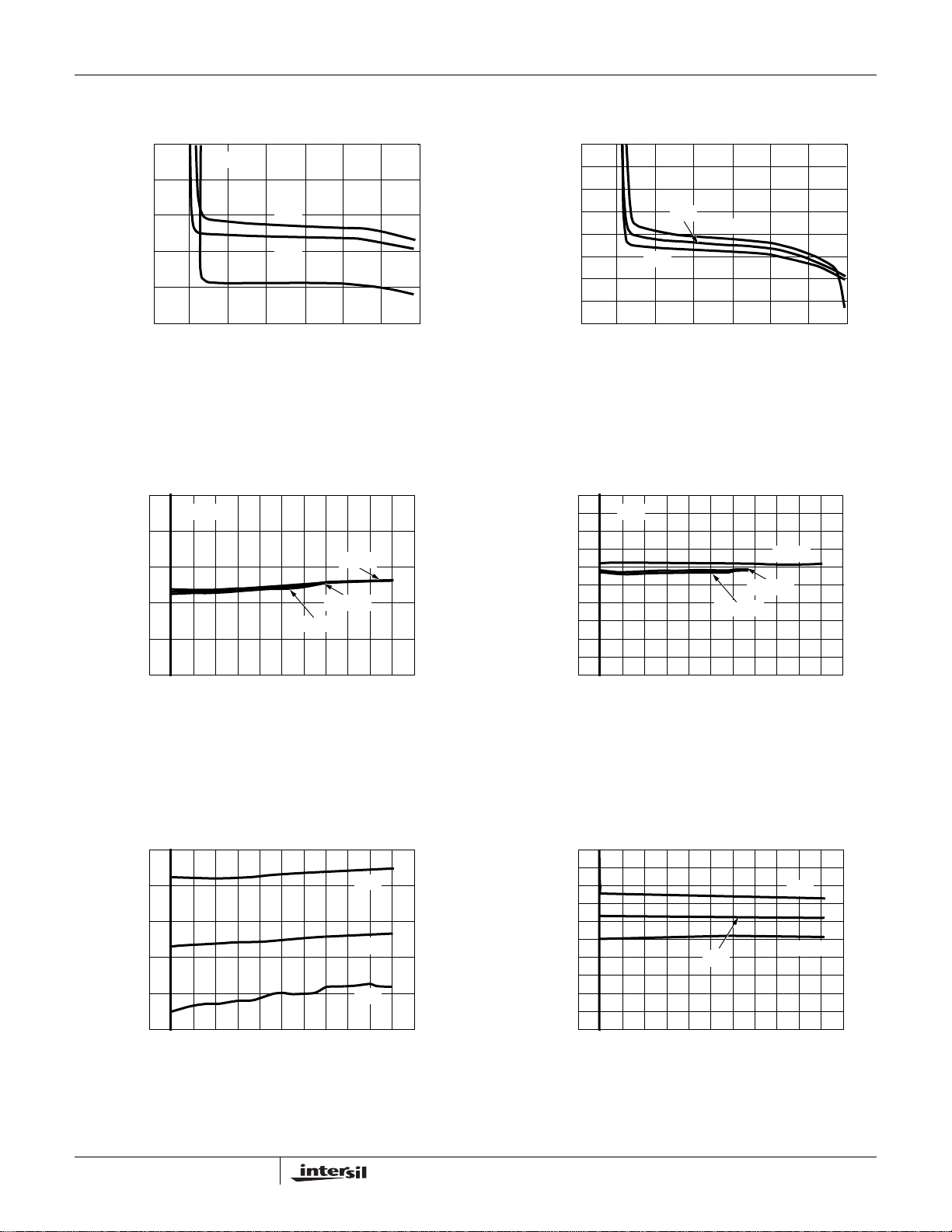

Typical Performance Curves (Continued)

EL8170, EL8173

45

40

35

30

25

20

GAIN (dB)

AV=100

15

=10kΩ

R

L

C

=10pF

L

10

5

0

100 10k1k 100k 1M

R

R

R

F/RG

F

G

=221kΩ

=99.02Ω

=2.23kΩ

FREQUENCY (Hz)

VS=3.3V

VS=5V

VS=2.9V

FIGURE 3. EL8170 FREQUENCY RESPONSE vs SUPPLY

VO LTAGE

50

45

40

35

GAIN (dB)

AV=100

=5V

V

S

=10kΩ

R

L

30

25

100 10k1k 100k

R

F/RG

=221kΩ

R

F

=2.23kΩ

R

G

=99.02Ω

CL=470pF

CL=220pF

FREQUENCY (Hz)

FIGURE 5. EL8170 FREQUENCY RESPONSE vs C

CL=820pF

CL=56pF

1M

LOAD

25

20

15

10

AV=10

=10kΩ

R

MAGNITUDE (dB)

L

C

=10pF

L

5

0

100 10k1k 100k

R

R

R

F/RG

F

G

=9.08Ω

=178kΩ

=19.6kΩ

FREQUENCY (Hz)

VS=5V

VS=3.3V

VS=2.9V

1M

FIGURE 4. EL8173 FREQUENCY RESPONSE vs SUPPLY

VOLTAGE

30

25

20

15

GAIN (dB)

AV=10

10

=5V

V

S

=10kΩ

R

L

=9.08Ω

R

F/RG

5

=178kΩ

R

F

=19.6kΩ

R

G

0

100 10k1k 100k

FREQUENCY (Hz)

CL=47pF

CL=27pF

FIGURE 6. EL8173 FREQUENCY RESPONSE vs C

CL=100pF

CL=2.7pF

1M

LOAD

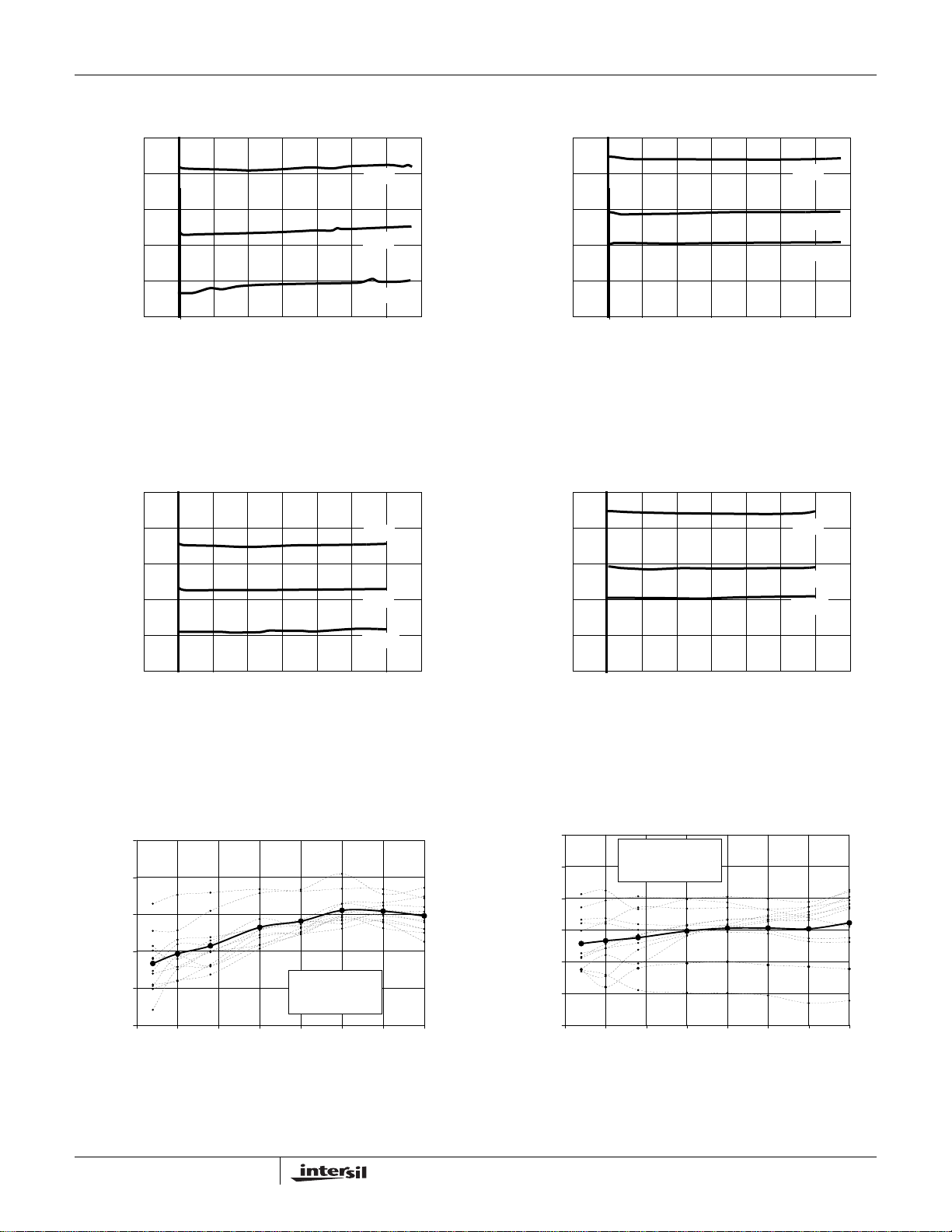

1500

1000

VS=3.3V

500

VS=2.9V

-0.5 0 0.5 1.0 1.5 2.0 2.5

COMMON-MODE INPUT VOLTAGE (V)

AVERAGE INPUT BIAS CURRENT (pA)

0

-500

VS=5.0V

3.0 3.5 4.0 4.5 5.0 5.5

FIGURE 7. EL8170 AVERAGE INPUT BIAS CURRENT vs

COMMON-MODE INPUT VOLTAGE @ 25°C

5

2000

1500

1000

500

AVERAGE INPUT BIAS CURRENT (pA)

0

-0.5 0 0.5 1.0 1.5 2.0 2.5

COMMON-MODE INPUT VOLTAGE (V)

VS=2.9V

VS=5.0V

VS=3.3V

3.0 3.5 4.0 4.5 5.0 5.5

FIGURE 8. EL8173 AVERAGE INPUT BIAS CURRENT vs

COMMON-MODE INPUT VOLTAGE @ 25°C

FN7490.0

January 3, 2006

Typical Performance Curves (Continued)

EL8170, EL8173

100

-100

INPUT OFFSET CURRENT (pA)

-300

-0.5 0 0.5 1.0 1.5 2.0 2.5

COMMON-MODE INPUT VOLTAGE (V)

VS=2.9V

VS=3.3V

3.0 3.5 4.0 4.5 5.0 5.5

VS=5.0V

FIGURE 9. EL8170 INPUT OFFSET CURRENT vs COMMON-

MODE INPUT VOLTAGE @ 25°C

1500

1000

500

0

-500

VS=5V

-45°C

85°C

25°C

100

-100

INPUT OFFSET CURRENT (pA)

-300

-0.5 0 0.5 1.0 1.5 2.0 2.5

COMMON-MODE INPUT VOLTAGE (V)

VS=2.9V

VS=3.3V

3.0 3.5 4.0 4.5 5.0 5.5

VS=5.0V

FIGURE 10. EL8173 INPUT OFFSET CURRENT vs COMMON-

MODE INPUT VOLTAGE @ 25°C

2000

1500

1000

500

25°C

85°C

-45°C

AVERAGE INPUT BIAS CURRENT (pA)

0

-0.5 0 0.5 1.0 1.5 2.0 2.5

COMMON-MODE INPUT VOLTAGE (V)

3.0 3.5 4.0 4.5 5.0 5.5

FIGURE 11. EL8170 AVERAGE INPUT BIAS CURRENT vs

COMMON-MODE INPUT VOLTAGE @ V

= 5V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

1500

1000

500

0

-500

-1000

AVERAGE INPUT BIAS CURRENT (pA)

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5

VS=3.3V

85°C

25°C

-45°C

COMMON-MODE INPUT VOLTAGE (V)

FIGURE 13. EL8170 AVERAGE INPUT BIAS CURRENT vs

COMMON MODE INPUT VOLTAGE @ V

= 3.3V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

0

AVERAGE INPUT BIAS CURRENT (pA)

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5

COMMON-MODE INPUT VOLTAGE (V)

4.0 4.5 5.0 5.5

FIGURE 12. EL8173 AVERAGE INPUT BIAS CURRENT vs

COMMON-MODE INPUT VOLTAGE @ V

S

= 5V,

TEMPERATURE = -45°C, 25°C, AND 85°C

2000

1500

25°C

1000

500

0

AVERAGE INPUT BIAS CURRENT (pA)

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5

COMMON-MODE INPUT VOLTAGE (V)

85°C

-45°C

FIGURE 14. EL8173 AVERAGE INPUT BIAS CURRENT vs

COMMON MODE INPUT VOLTAGE @ V

= 3.3V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

6

FN7490.0

January 3, 2006

Typical Performance Curves (Continued)

EL8170, EL8173

1500

1000

500

0

-500

-1000

AVERAGE INPUT BIAS CURRENT (pA)

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0

VS=2.9V

85°C

25°C

-45°C

COMMON-MODE INPUT VOLTAGE (V)

FIGURE 15. EL8170 AVERAGE INPUT BIAS CURRENTS vs

COMMON-MODE INPUT VOLTAGE @ V

= 2.9V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

250

25°C

200

150

100

50

INPUT OFFSET VOLTAGE (µV)

0

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

COMMON-MODE INPUT VOLTAGE (V)

VS=5V

VS=3.3V

VS=2.9V

2000

1500

25°C

1000

-45°C

500

0

AVERAGE INPUT BIAS CURRENT (pA)

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0

COMMON-MODE INPUT VOLTAGE (V)

85°C

FIGURE 16. EL8173 AVERAGE INPUT BIAS CURRENTS vs

COMMON-MODE INPUT VOLTAGE @ V

= 2.9V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

0

25°C

-200

-400

-600

-800

INPUT OFFSET VOLTAGE (µV)

-1000

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

COMMON-MODE INPUT VOLTAGE (V)

VS=2.9V

VS=5V

VS=3.3V

FIGURE 17. EL8170 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 5V, 3.3V AND

S

2.9V AND TEMPERATURE = 25°C

250

200

150

100

50

INPUT OFFSET VOLTAGE (µV)

0

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

COMMON-MODE INPUT VOLTAGE (V)

85°C

25°C

-45°C

FIGURE 19. EL8170 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 5.0V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

7

FIGURE 18. EL8173 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 5V, 3.3V, AND

S

2.9V AND TEMPERATURE = 25°C

0

-200

-400

-600

-800

INPUT OFFSET VOLTAGE (µV)

-1000

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

COMMON-MODE INPUT VOLTAGE (V)

25°C

85°C

-45°C

FIGURE 20. EL8173 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 5.0V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

FN7490.0

January 3, 2006

Typical Performance Curves (Continued)

EL8170, EL8173

250

200

150

100

50

INPUT OFFSET VOLTAGE (µV)

0

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0

COMMON-MODE INPUT VOLTAGE (V)

85°C

25°C

-45°C

3.5

FIGURE 21. EL8170 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 3.3V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

450

300

200

100

85°C

25°C

0

-200

-400

-600

-800

INPUT OFFSET VOLTAGE (µV)

-1000

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0

COMMON-MODE INPUT VOLTAGE (V)

85°C

25°C

-45°C

3.5

FIGURE 22. EL8173 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 3.3V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

0

-200

-400

-600

85°C

25°C

-45°C

0

INPUT OFFSET VOLTAGE (µV)

-100

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0

COMMON-MODE INPUT VOLTAGE (V)

-45°C

3.5

FIGURE 23. EL8170 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 2.9V,

S

TEMPERATURE = -45°C, 25°C, AND 85°C

500

250

0

-250

-500

INPUT OFFSET VOLTAGE (uV)

-750

-50 -25 0 25 50 75 100 125

TEMPERATURE (degrees C)

TEMPERATURE (°C)

12 samples

Vs=5V

Average = 2uV/C

FIGURE 25. EL8170 INPUT OFFSET VOLTAGE vs

TEMPERATURE @ V

= 5.0V

S

-800

INPUT OFFSET VOLTAGE (µV)

-1000

-0.5 0 0.5 1.0 1.5 2.0 2.5 3.0

COMMON-MODE INPUT VOLTAGE (V)

3.5

FIGURE 24. EL8173 INPUT OFFSET VOLTAGE vs COMMON-

MODE INPUT VOLTAGE @ V

= 3.3V,

S

TEMPERATURE = - 45°C, 25°C, AND 85°C

1500

1000

500

0

-500

-1000

INPUT OFFSET VOLTAGE (uV)

-1500

-50 -25 0 25 50 75 100 125

12 samples

Vs=5V

Average = 1.8uV/C

TEMPERATURE (degrees C)

TEMPERATURE (°C)

FIGURE 26. EL8173 INPUT OFFSET VOLTAGE vs

TEMPERATURE @ VS = 5.0V

8

FN7490.0

January 3, 2006

Typical Performance Curves (Continued)

EL8170, EL8173

500

250

0

-250

12 samples

-500

INPUT OFFSET VOLTAGE (uV)

-750

-50 -25 0 25 50 75 100 125

TEMPERATURE (degrees C)

TEMPERATURE (°C)

Vs=2.9V

Average = 2.2uV/C

FIGURE 27. EL8170 INPUT OFFSET VOLTAGE vs

TEMPERATURE @ V

120

110

100

90

80

70

CMRR (dB)

60

50

40

1 10 100 1k 10k 100k 1M

FREQUENCY (Hz)

= 2.9V

S

GAIN=1000

GAIN=100

1500

1000

500

0

-500

-1000

INPUT OFFSET VOLTAGE (uV)

-1500

-50 -25 0 25 50 75 100 125

12 samples

Vs=2.9V

Average = 1.38uV/C

TEMPERATURE (degrees C)

TEMPERATURE (°C)

FIGURE 28. EL8173 INPUT OFFSET VOLTAGE vs

TEMPERATURE @ VS = 2.9V

120

110

100

90

80

CMRR (dB)

70

60

50

40

1 10 100 1k 10k 100k 1M

FREQUENCY (Hz)

GAIN=10

GAIN=1000

GAIN=100

FIGURE 29. EL8170 CMRR vs FREQUENCY FIGURE 30. EL8173 CMRR vs FREQUENCY

120

110

100

90

80

PSRR (dB)

70

60

50

40

1 10 100 1k 10k 100k 1M

FREQUENCY (Hz)

PSRR+

PSRR-

100

90

80

70

60

50

PSRR (dB)

40

30

20

1 10 100 1k 10k 100k 1M

PSRR-

FREQUENCY (Hz)

FIGURE 31. EL8170 PSRR vs FREQUENCY FIGURE 32. EL8173 PSRR vs FREQUENCY

9

PSRR+

FN7490.0

January 3, 2006

Typical Performance Curves (Continued)

EL8170, EL8173

1µV/DIV

1s/DIV

FIGURE 33. EL8170 0.1Hz TO 10Hz INPUT VOLTAGE NOISE

(GAIN = 100)

70

60

50

40

30

20

SUPPLY CURRENT (µA)

10

0

23.52.5 4.5

5µV/DIV

FIGURE 34. EL8173 0.1Hz TO 10Hz INPUT VOLTAGE NOISE

435

SUPPLY VOLTAGE (V)

1s/DIV

(GAIN = 10)

5.5

FIGURE 35. EL8170 AND EL8173 SUPPLY CURRENT vs SUPPLY VOLTAGE

JEDEC JESD51-7 HIGH EFFECTIVE THERMAL

CONDUCTIVITY TEST BOARD

1.4

1.2

1

909mW

0.8

0.6

0.4

POWER DISSIPATION (W)

0.2

0

0 25 50 75 100 150

θ

S

O

J

A

8

=

1

1

0

°

C

/

W

AMBIENT TEMPERATURE (°C)

12585

FIGURE 36. PACKAGE POWER DISSIPATION vs AMBIENT

TEMPERATURE

10

JEDEC JESD51-3 LOW EFFECTIVE THERMAL

CONDUCTIVITY TEST BOARD

1

0.9

0.8

0.7

625mW

0.6

0.5

0.4

0.3

0.2

POWER DISSIPATION (W)

0.1

0

0 25 50 75 100 150

S

θ

O

J

A

8

=

1

6

0

°

C

/

W

AMBIENT TEMPERATURE (°C)

12585

FIGURE 37. PACKAGE POWER DISSIPATION vs AMBIENT

TEMPERATURE

FN7490.0

January 3, 2006

EL8170, EL8173

Description of Operation and Applications

Information

Product Description

The EL8170 and EL8173 are micropower instrumentation

amplifiers (in-amps) which deliver rail-to-rail input

amplification and rail-to-rail output swing on a single 2.9V to

5V supply. The EL8170 and EL8173 also deliver excellent

DC and AC specifications while consuming only 60µA typical

supply current. Because the EL8170 and EL8173 provide an

independent pair of feedback terminals to set the gain and to

adjust output level, these in-amps achieve high commonmode rejection ratio regardless of the tolerance of the gain

setting resistors. The EL8173 is internally compensated for a

minimum closed loop gain of 10 or greater, well suited for

moderate to high gains. For higher gains, the EL8170 is

internally compensated for a minimum gain of 100. An

ENABLE

2.9µA, while the instrumentation amplifier is disabled.

Input Protection

All input and feedback terminals of the EL8170 and EL8173

have internal ESD protection diodes to both positive and

negative supply rails, limiting the input voltage to within one

diode drop beyond the supply rails. The EL8170 has

additional back-to-back diodes across the input terminals

and also across the feedback terminals. If overdriving the

inputs is necessary, the external input current must never

exceed 5mA. On the other hand, the EL8173 has no clamps

to limit the differential voltage on the input terminals allowing

higher differential input voltages at lower gain applications. It

is recommended however, that the input terminals of the

EL8173 is not overdriven beyond 1V to avoid offset drift. An

external series resistor may be used as an external

protection to limit excessive external voltage and current

from damaging the inputs.

Input Stage and Input Voltage Range

The input terminals (IN+ and IN-) of the EL8170 and EL8173

are single differential pair bipolar PNP devices aided by an

Input Range Enhancement Circuit to increase the headroom

of operation of the common-mode input voltage. The

feedback terminals (FB+ and FB-) also have a similar

topology. As a result, the input common-mode voltage range

of both the EL8170 and EL8173 is rail-to-rail. These in-amps

are able to handle input voltages that are at or slightly

beyond the supply and ground making these in-amps well

suited for single 5V or 3.3V low voltage supply systems.

There is no need then to move the common-mode input of

the in-amps to achieve symmetrical input voltage.

Input Bias Cancellation/Compensation

Inside the EL8170 and EL8173 is an Input Bias

Cancellation/Compensation Circuit for both the input and

feedback terminals (IN+, IN-, FB+ and FB-), acheiving a low

input bias current all throughout the input common-mode

pin is used to reduce power consumption, typically

range and the operating temperature range. While the PNP

bipolar input stages are biased with an adequate amount of

biasing current for speed and increased noise performance,

the Input Bias Cancellation/Compensation Circuit sinks most

of the base current of the input transistor leaving a small

portion as input bias current, typically 500pA. In addition, the

Input Bias Cancellation/Compensation Circuit maintains a

smooth and flat behavior of input bias current over the

common mode range and over the operating temperature

range. The Input Bias Cancellation/Compensation Circuit

operates from input voltages of 10mV above the negative

supply to input voltages slightly above the positive supply.

See Average Input Bias Current vs Common-Mode Input

Voltage in the performance curves section.

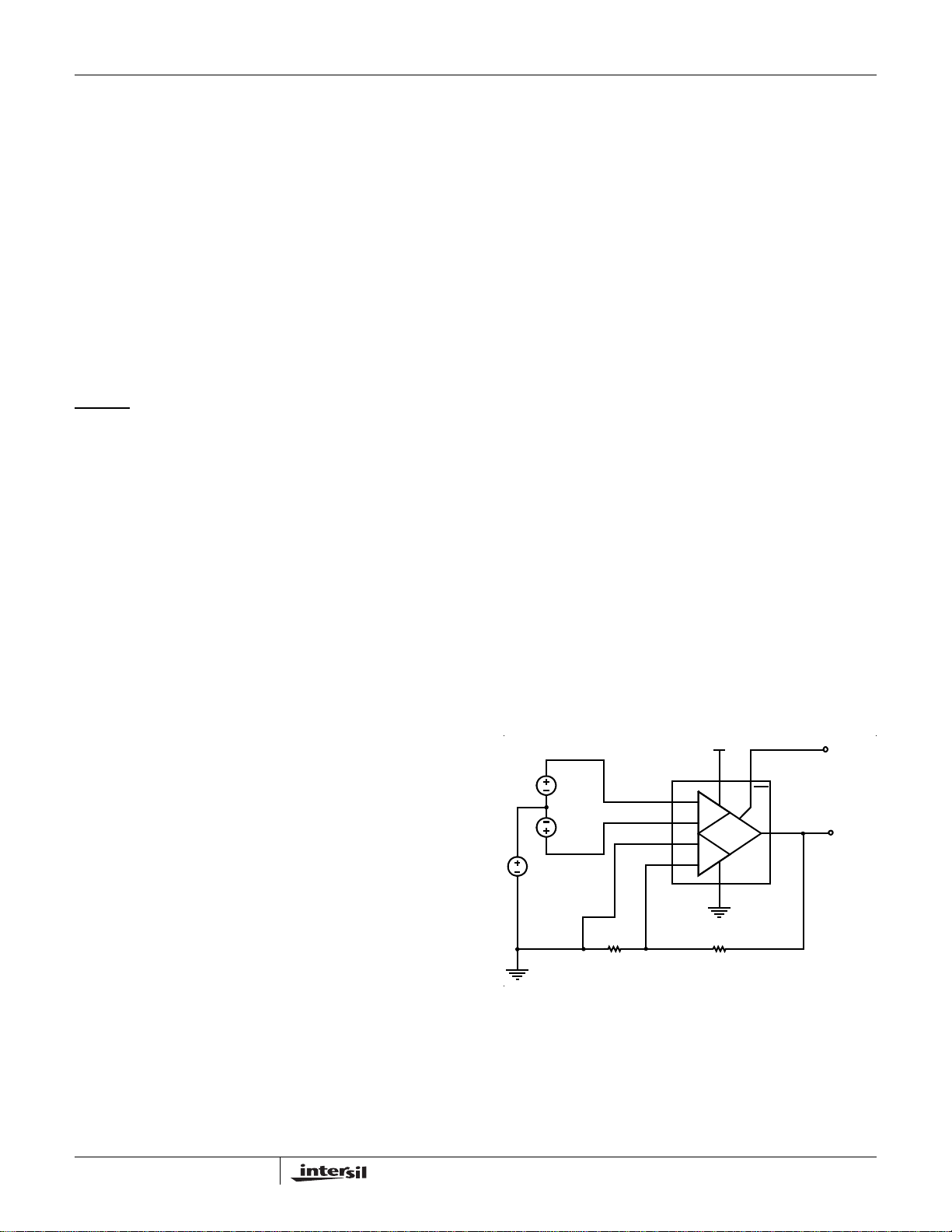

Output Stage and Output Voltage Range

A pair of complementary MOSFET devices drives the output

VOUT to within a few millivolts of the supply rails. At a

100kΩ load, the PMOS sources current and pulls the output

up to 4mV below the positive supply, while the NMOS sinks

current and pulls the output down to 4mV above the negative

supply, or ground in the case of a single supply operation.

The current sinking and sourcing capability of the EL8170

and EL8173 are internally limited to 29mA.

Gain Setting

VIN, the potential difference across IN+ and IN-, is replicated

(less the input offset voltage) across FB+ and FB-. The

obsession of the EL8170 and EL8173 in-amp is to maintain

the differential voltage across FB+ and FB- equal to IN+ and

IN-; (FB+ - FB-) = (IN+ - IN-). Consequently, the transfer

function can be derived. The gain of the EL8170 and EL8173

is set by two external resistors, the feedback resistor RF, and

the gain resistor RG.

2.9V to 5V

1

VIN/2

VIN/2

VCM

FIGURE 38. GAIN IS SET BY TWO EXTERNAL RESISTORS,

R

AND R

VOUT 1

F

R

F

--------+

R

G

G

VIN=

7

VS+

EL8170/3

VS-

4

RFRG

EN

6

IN+

3

+

IN-

2

-

FB+

8

+

5

FB-

-

In Figure 38, the FB+ pin and one end of resistor RG are

connected to GND. With this configuration, the above gain

EN_BAR

VOUT

11

FN7490.0

January 3, 2006

EL8170, EL8173

equation is only true for a positive swing in VIN; negative

input swings will be ignored and the output will be at ground.

Reference Connection

Unlike a three-opamp instrumentation amplifier, a finite

series resistance seen at the REF terminal does not degrade

the EL8170 and EL8173's high CMRR performance

eliminating the need for an additional external buffer

amplifier. Figure 39 uses the FB+ pin to provide a high

impedance REF terminal.

2.9V to 5V

1

7

VS+

EL8170/3

VS-

4

RFRG

EN

6

IN+

3

+

IN-

2

-

8

FB+

+

5

FB-

-

VCM

VIN/2

VIN/2

2.9V to 5V

R1

REF

R2

FIGURE 39. GAIN SETTING AND REFERENCE CONNECTION

.

VOUT 1

R

F

--------+

R

G

VIN()1

R

F

--------+

VREF()+=

R

G

The FB+ pin is used as a REF terminal to center or to adjust

the output. Because the FB+ pin is a high impedance input,

an economical resistor divider can be used to set the voltage

at the REF terminal without degrading or affecting the CMRR

performance. Any voltage applied to the REF terminal will

shift VOUT by VREF times the closed loop gain, which is set

by resistors RF and RG. See Figure 39.

The FB+ pin can also be connected to the other end of

resistor, RG. See Figure 40. Keeping the basic concept that

the EL8170 and EL8173 in-amps maintain constant

differential voltage across the input terminals and feedback

terminals (IN+ - IN- = FB+ - FB-), the transfer function of

Figure 40 can be derived.

EN_BAR

VOUT

VCM

VREF

VIN/2

VIN/2

3

2

8

5

2.9V to 5V

IN+

IN-

FB+

FB-

7

VS+

+

EL8170/3

+

-

VS-

4

RFRG

1

EN

6

EN_BAR

VOUT

FIGURE 40. REFERENCE CONNECTIONWITH AN AVAILABLE

VREF

R

VOUT 1

F

--------+

VIN()VREF()+=

R

G

A finite resistance RS in series with the VREF source, adds

an output offset of VIN*(RS/RG). As the series resistance Rs

approaches zero, the gain equation is simplified to the above

equation for Figure 40. VOUT is simply shifted by an amount

VREF.

External Resistor Mismatches

Because of the independent pair of feedback terminals

provided by the EL8170 and EL8173, the CMRR is not

degraded by any resistor mismatches. Hence, unlike a three

opamp and especially a two opamp in-amp, the EL8170 and

EL8173 reduce the cost of external components by allowing

the use of 1% or more tolerance resistors without sacrificing

CMRR performance. The EL8170 and EL8173 CMRR will be

108dB regardless of the tolerance of the resistors used.

Gain Error and Accuracy

The EL8173 has a Gain Error, EG, of 0.2% typical. The

EL8170 has an EG of 0.3% typical. The gain error indicated

in the electrical specifications table is the inherent gain error

of the EL8170 and EL8173 and does not include the gain

error contributed by the resistors. There is an additional gain

error due to the tolerance of the resistors used. The resulting

non-ideal transfer function effectively becomes:

12

VOUT 1

R

F

--------+

1E

R

G

++()–[]VIN××=

RGERFEG

FN7490.0

January 3, 2006

EL8170, EL8173

Where:

ERG = Tolerance of RG

ERF = Tolerance of RF

EG = Gain Error of the EL8170 or EL8173

The term [1 - (ERG +ERF +EG)] is the deviation from the

theoretical gain. Thus, (ERG +ERF +EG) is the total gain

error. For example, if 1% resistors are used for the EL8170,

the total gain error would be:

ERGERFEGtypical()++()±=

0.01 0.01 0.003++()±=

2.3%±=

Disable/Power-Down

The EL8170 and EL8173 can be powered down reducing

the supply current to typically 2.9µA. When disabled, the

output is in a high impedance state. The active low

bar pin has an internal pull down and hence can be left

floating and the in-amp enabled by default. When the

ENABLE bar is connected to an external logic, the in-amp will

power down when

power on when

ENABLE bar is pulled above 2V, and will

ENABLE bar is pulled below 0.8V.

ENABLE

13

FN7490.0

January 3, 2006

Package Outline Drawing

EL8170, EL8173

NOTE: The package drawing shown here may not be the latest version. To check the latest revision, please refer to the Intersil website at

http://www.intersil.com/design/packages/index.asp

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

14

FN7490.0

January 3, 2006

Loading...

Loading...