Intersil Corporation DG528, DG527, DG526, DG529 Datasheet

Semiconductor

DG526, DG527,

ODUCT

OBSOLETE PR

April 1999

FOR A POSSIBLE SUBSTITUTE PRODUCT

call Central Applications 1-800-442-7747

or email: centapp@harris.com

Features

• Direct RESET

• TTL and CMOS Compatible Address and Enable

Inputs

• Maximum Power Supply Rating . . . . . . . . . . . . . . . .44V

• Break-Before-Make Switching

• Alternate Source

Applications

• Data Acquisition Systems

• Communication Systems

• Automatic Test Equipment

• Microprocessor Controlled Systemd

DG528, DG529

Analog CMOS

Latchable Multiplexers

Description

The DG526, DG527, DG528, and DG529 are CMOS

Monolithic 16-Channel/Dual 4-Channel Analog Multiplexers.

Each device has on-chip address and control latches to simplify design in microprocessor based applications. The DG526

uses 4 address lines to control its 16 channels; the DG527,

DG528 both use 3 address lines to control their 8 channels;

and the DG529 uses 2 address lines to control its 4 channels.

The enable pin is used to enable the address latches during

the

WR pulse. It can be hard wired to the logic supply if one of

the channels will always be used (except during a reset) or it

can be tied to address decoding circuitry for memory mapped

operation. The

the state of any other latch or control line. The

to transfer the state of the address control lines to their

latches, except during a reset or when EN is low.

A channel in the ON state conducts signals equally well in

both directions. In the OFF state each channel blocks voltages up to the supply rails. The address inputs,

the enable input are TTL and CMOS compatible over the full

specified operation temperature range.

RS pin is used to clear all latches regardless of

WR pin is used

WR, RS and

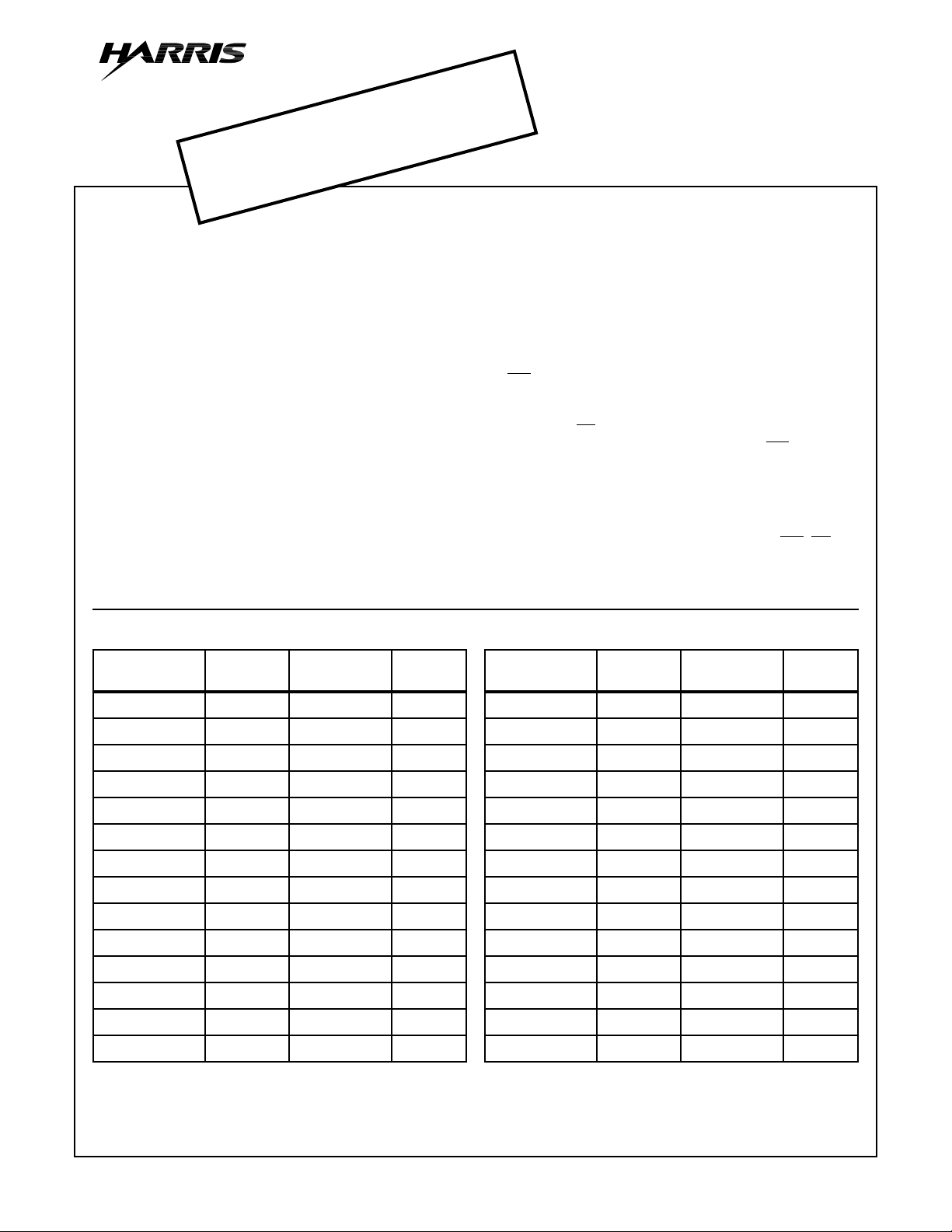

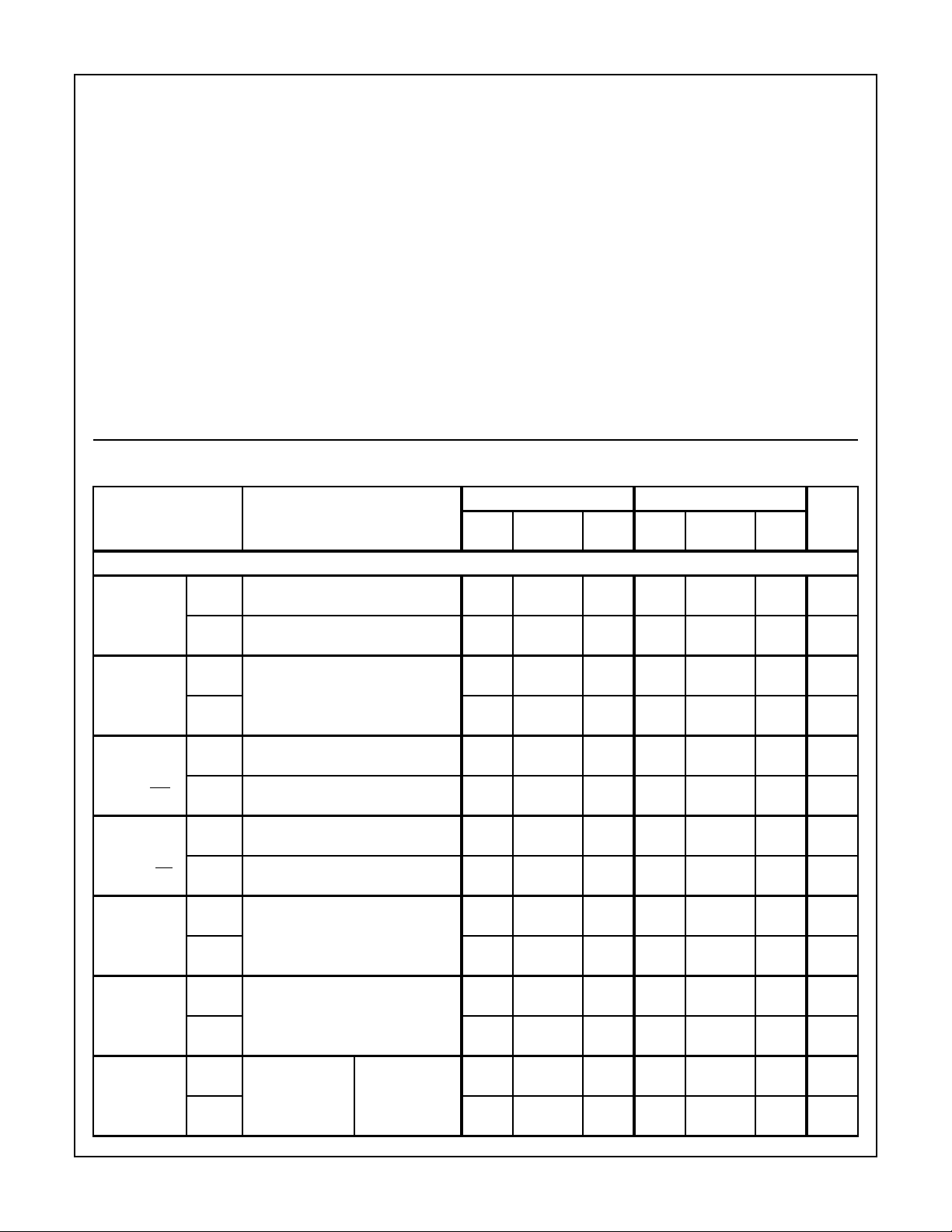

Part Number Information

PART

NUMBER

DG526AK -55 to 125 28 Ld CERDIP F28.6

DG526AK/883B -55 to 125 28 Ld CERDIP F28.6

DG526BK -25 to 85 28 Ld CERDIP F28.6

DG526BY -25 to 85 28 Ld SOIC M28.3

DG526CJ 0 to 70 28 Ld PDIP E28.6

DG526CK 0 to 70 28 Ld CERDIP F28.6

DG526CY 0 to 70 28 Ld SOIC M28.3

DG527AK -55 to 125 28 Ld CERDIP F28.6

DG527AK/883B -55 to 125 28 Ld CERDIP F28.6

DG527BK -25 to 85 28 Ld CERDIP F28.6

DG527BY -25 to 85 28 Ld SOIC M28.3

DG527CJ 0 to 70 28 Ld PDIP E28.6

DG527CK 0 to 70 28 Ld CERDIP F28.6

DG527CY 0 to 70 28 Ld SOIC M28.3

TEMP.

RANGE (oC) PACKAGE PKG. NO.

PART

NUMBER

DG528AK -55 to 125 18 Ld CERDIP F18.3

DG528AK/883B -55 to 125 18 Ld CERDIP F18.3

DG528BK -25 to 85 18 Ld CERDIP F18.3

DG528BY -25 to 85 18 Ld SOIC M18.3

DG528CJ 0 to 70 18 Ld PDIP E18.3

DG528CK 0 to 70 18 Ld CERDIP F18.3

DG528CY 0 to 70 18 Ld SOIC M18.3

DG529AK -55 to 125 18 Ld CERDIP F18.3

DG529AK/883B -55 to 125 18 Ld CERDIP F18.3

DG529BK -25 to 85 18 Ld CERDIP F18.3

DG529BY -25 to 85 18 Ld SOIC M18.3

DG529CJ 0 to 70 18 Ld PDIP E18.3

DG529CK 0 to 70 18 Ld CERDIP F18.3

DG529CY 0 to 70 18 Ld SOIC M18.3

TEMP.

RANGE (oC) PACKAGE PKG. NO.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1999

12-1

File Number 3139.2

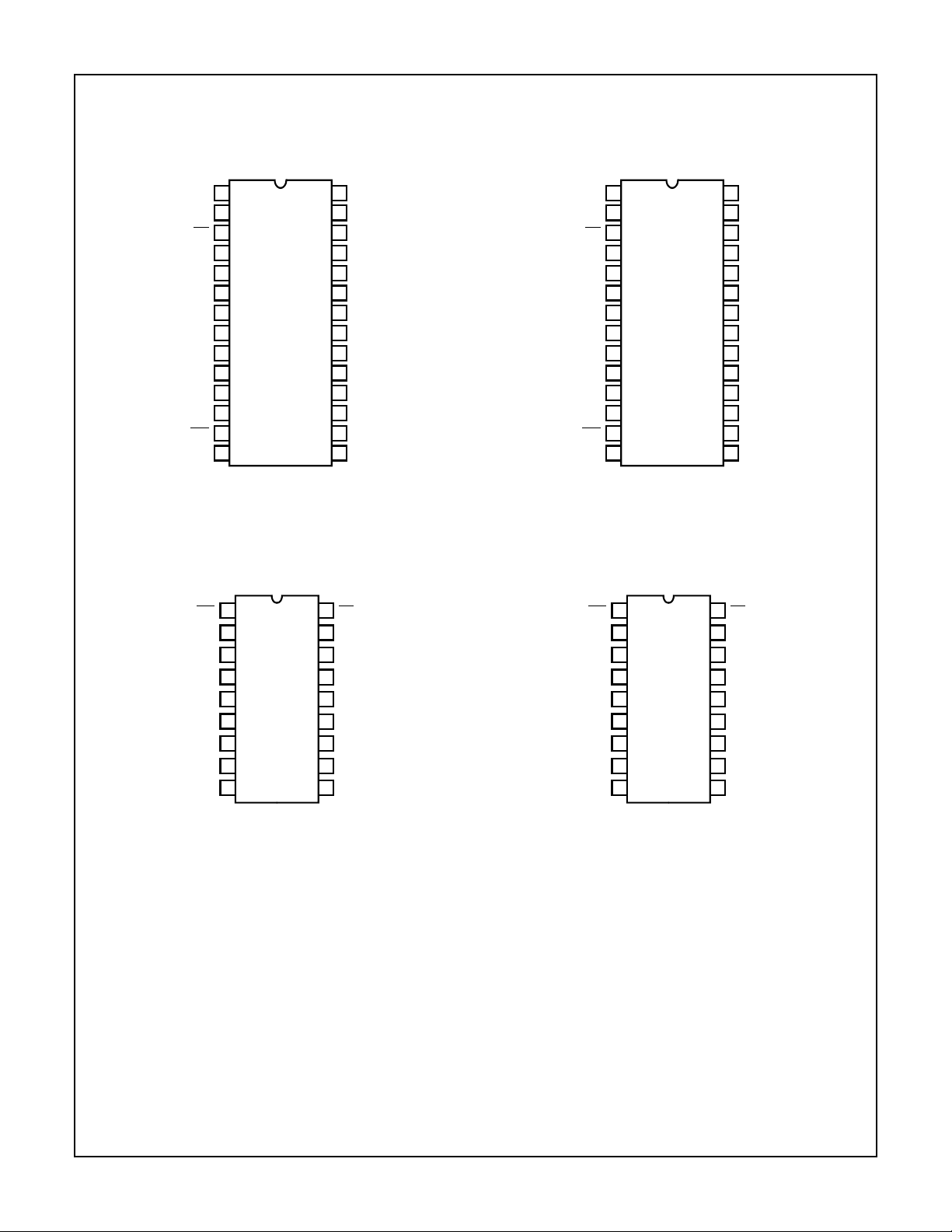

Pinouts

DG526

(PDIP, CERDIP, SOIC)

TOP VIEW

DG526, DG527, DG528, DG529

DG527

(PDIP, CERDIP, SOIC)

TOP VIEW

V+

1

2

NC

3

RS

S

4

16

S

5

15

S

6

14

S

7

13

S

8

12

S

9

11

S

10

10

S

11

9

GND

12

WR

13

14

A

3

DG528

(PDIP, CERDIP, SOIC)

TOP VIEW

1

WR

2

A

0

3

EN

4

V-

S

5

1

S

6

2

S

7

3

S

8

4

D

9

28

D

V-

27

26

S

8

S

25

7

S

24

6

S

23

5

S

22

4

S

21

3

20

S

2

S

19

1

EN

18

17

A

0

16

A

1

A

15

2

V+

D

RS

S

S

S

S

S

S

S

S

GND

WR

NC

8B

7B

6B

5B

4B

3B

2B

1B

1

2

B

3

4

5

6

7

8

9

10

11

12

13

14

28

D

B

V-

27

S

26

8A

S

25

7A

S

24

6A

S

23

5A

S

22

4A

S

21

3A

20

S

2A

S

19

1A

EN

18

17

A

0

16

A

1

A

15

2

DG529

(PDIP, CERDIP, SOIC)

TOP VIEW

18

RS

17

A

1

16

A

2

15

GND

V+

14

S

13

5

S

12

6

S

11

7

S

10

8

WR

S

S

S

S

A

EN

1A

2A

3A

4A

D

1

2

0

3

4

V-

5

6

7

8

9

A

18

RS

17

A

1

GND

16

V+

15

S

14

1B

S

13

2B

S

12

3B

11

S

4B

D

10

B

12-2

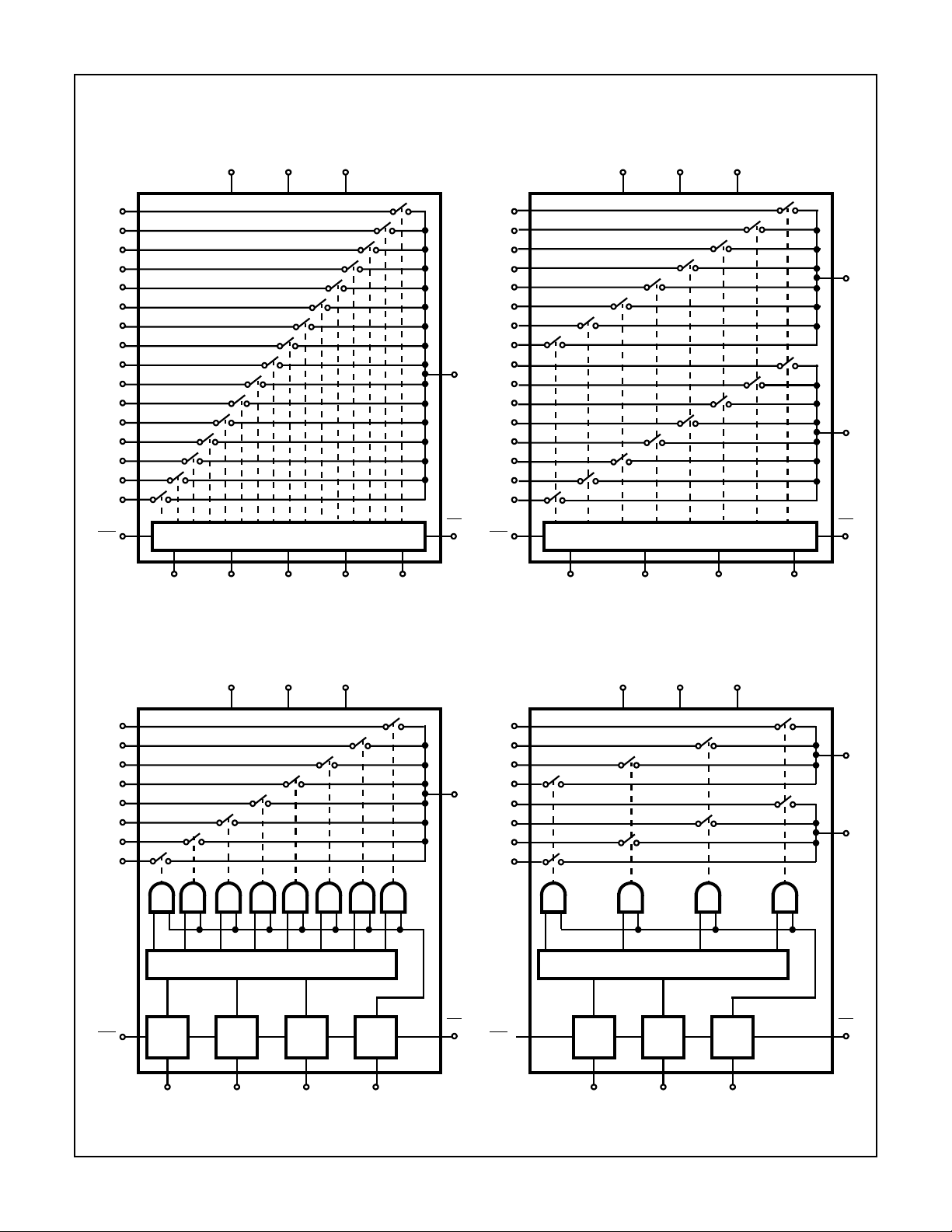

Functional Diagrams

DG526

16-CHANNEL SINGLE ENDED MULTIPLEXER

V+ V- GND

DG526, DG527, DG528, DG529

DG527

DIFFERENTIAL 8-CHANNEL MULTIPLEXER

V+ V- GND

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

S

WR

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

DECODER LOGIC AND LATCHES

3

A

2

A

1

DG528

8-CHANNEL SINGLE ENDED MULTIPLEXER

V+ V- GND

S

1A

S

2A

S

3A

RS

D

A

D

B

S

4A

S

5A

S

6A

S

7A

S

8A

S

D

1B

S

2B

S

3B

S

4B

S

5B

S

6B

S

7B

S

8B

RS

WR

A

0

ENA

DECODER LOGIC AND LATCHES

2

A

1

A

0

ENA

DG529

DUAL 4-CHANNEL MULTIPLEXER

V+ V- GND

S

S

S

S

S

S

S

S

WR

RS

S

1A

S

2A

S

3A

S

D

4A

S

1B

S

2B

S

3B

S

4B

DECODER LOGIC AND LATCHES

DECODER LOGIC

D

A

D

B

LATCHES

RS

1

2

3

4

5

6

7

8

DECODER LOGIC AND LATCHES

LATCHES

WR

A

2

A

1

A

0

EN

A

0

A

0

EN

12-3

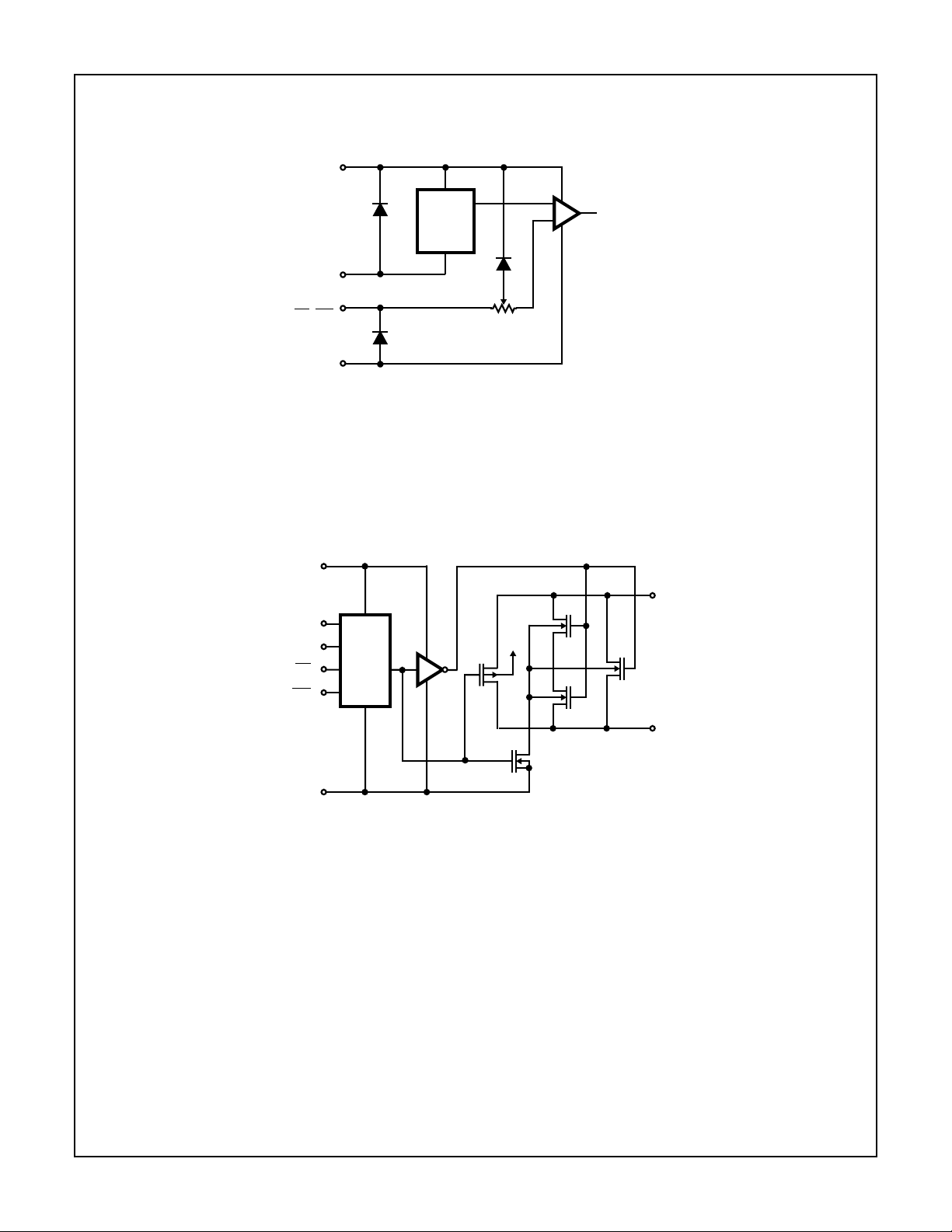

Schematic Diagrams

DG526, DG527, DG528, DG529

LOGIC INTERFACE AND LEVEL SHIFTER

V+

GND

A

, EN,

X

RS, WR

V+

AX‘

EN‘

RS‘

WR‘

V-

DE-

CODER

LOGIC

TRIP

POINT

REF

DECODER AND SWITCH

V+

+

-

TO

DECODER

S

X

D

X

V-

12-4

DG526, DG527, DG528, DG529

Absolute Maximum Ratings Thermal Information

V+ to V-. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +44V

V- to Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-25V

VIN to Ground (Note 1). . . . . . . . . . . . . . . . . . . . (V- - 2V), (V+ + 2V)

VS or VD to V+ (Note 1) . . . . . . . . . . . . . . . . . . . . . . . .+2V, (V- - 2V)

VS or VD to V- (Note 1). . . . . . . . . . . . . . . . . . . . . . . . -2V, (V+ + 2V)

Current, Any Terminal Except S or D . . . . . . . . . . . . . . . . . . . .30mA

Continuous Current, S or D . . . . . . . . . . . . . . . . . . . . . . . . . . .20mA

Peak Current, S or D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40mA

(Pulsed at 1ms, 10% Duty Cycle Max)

Operating Conditions

Operating Temperature

C Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0oC to 70oC

B Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -25oC to 85oC

A Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maxim um Ratings” ma y cause permanent damage to the device . This is a stress only rating and oper ation of

the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

18 Ld PDIP Package. . . . . . . . . . . . . . 90 N/A

18 Ld CERDIP Package . . . . . . . . . . . 75 22

18 Ld SOIC Package. . . . . . . . . . . . . . 95 N/A

28 Ld PDIP Package. . . . . . . . . . . . . . 60 N/A

28 Ld CERDIP Package . . . . . . . . . . . 55 18

28 Ld SOIC Package. . . . . . . . . . . . . . 70 N/A

Maximum Junction Temperature

Ceramic Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175oC

Plastic Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range

C Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-65oC to 125oC

A and B Suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . .-65oC to 150oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

Electrical Specifications (Note 3) V+ = +15V, V- = -15V, GND = 0V, WR = 0V, RS = 2.4V, EN = 2.4V, T

Unless Otherwise Specified

A SUFFIX B AND C SUFFIX

PARAMETER

DYNAMIC

Switching Time

of Multiplexer,

t

TRANSITION

Break-BeforeMake Interval,

t

OPEN

Enable and

Write Turn-ON

Time,

(EN, WR)

t

ON

Enable and

Reset Turn

OFF Time,

t

(EN, RS)

OFF

Off Isolation,

OIRR

Logic Input

Capacitance,

C

IN

Source OFF

Capacitance,

C

S(OFF)

DG526,

DG527

DG528,

DG529

DG526,

DG527

DG528,

DG529

DG526,

DG527

DG528,

DG529

DG526,

DG527

DG528,

DG529

DG526,

DG527

DG528,

DG529

DG526,

DG527

DG528,

DG529

DG526,

DG527

DG528,

DG529

(NOTE 6)

TEST CONDITIONS

See Figure 3 (Note 7) - 0.65 1 - 0.65 - µs

See Figure 3 - 0.6 1 - 0.6 - µs

See Figure 4 - 0.2 - - 0.2 - µs

See Figures 1, 6 (Note 7) - 0.7 1.5 - 0.7 - µs

See Figures 5, 6 (Note 7) - 1 1.5 - 1 - µs

See Figures 2, 7 (Note 7) - 0.4 1 - 0.4 - µs

See Figures 5, 6 (Note 7) - 0.4 1 - 0.4 - µs

VEN = 0V, R = 1kΩ, CL = 15pF,

VS = 7V

f = 1MHz - 6 - - 6 - pF

VS = 0V VEN = 0V,

, f = 500kHz (Note 4)

RMS

f = 140kHz

(NOTE 2)

TYP MAX MIN

- 0.2 - - 0.2 - µs

-55--55-dB

-68--68-dB

- 2.5 - - 2.5 - pF

-10--10-pF

-5--5-pF

(NOTE 2)

= 25oC,

A

TYP MAX

UNITSMIN

12-5

Loading...

Loading...