Page 1

®

DG411, DG412, DG413

Data Sheet June 20, 2007

Monolithic Quad SPST, CMOS Analog

Switches

The DG411 series monolithic CMOS analog switches are

drop-in replacements for the popular DG211 and DG212

series devices. They include four independent single pole

throw (SPST) analog switches, and TTL and CMOS

compatible digital inputs.

These switches feature lower analog ON-resistance (<35Ω)

and faster switch time (t

or DG212. Charge injection has been reduced, simplifying

sample and hold applications.

The improvements in the DG411 series are made possible

by using a high voltage silicon-gate process. An epitaxial

layer prevents the latch-up associated with older CMOS

technologies. The 44V maximum voltage range permits

controlling 40V

single-ended from +5V to 44V, or split from ±5V to ±20V.

The four switches are bilateral, equally matched for AC or

bidirectional signals. The ON-resistance variation with analog

signals is quite low over a ±15V analog input range. The

switches in the DG41 1 an d DG412 are identical, dif fering only

in the polarity of the selection logic. T wo of the switches in the

DG413 (#2 and #3) use the logic of the DG211 and DG411

(i.e., a logic “0” turns the switch ON) and the other two

switches use DG212 and DG412 positive logic. This permits

independent control of turn-on and turn-off times for SPDT

configurations, permitting “break-before-make” or “makebefore-break” operation with a minimum of external logic.

signals. Power supplies may be

P-P

<175ns) compared to the DG211

ON

FN3282.13

Features

• ON-Resistance (Max). . . . . . . . . . . . . . . . . . . . . . . . . 35Ω

• Low Power Consumption (P

• Fast Switching Action

(Max) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175ns

-t

ON

-t

(Max) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145ns

OFF

• Low Charge Injection

• Upgrade from DG211, DG212

• TTL, CMOS Compatible

• Single or Split Supply Operation

• Pb-Free Plus Anneal Available (RoHS Compliant)

). . . . . . . . . . . . . . . . . . <35µW

D

Applications

• Audio Switching

• Battery Operated Systems

• Data Acquisition

• Hi-Rel Systems

• Sample and Hold Circuits

• Communication Systems

• Automatic Test Equipment

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

Copyright Intersil Americas Inc. 1993, 1994, 1997, 1999, 2002, 2004-2007. All Rights Reserved

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Page 2

DG411, DG412, DG413

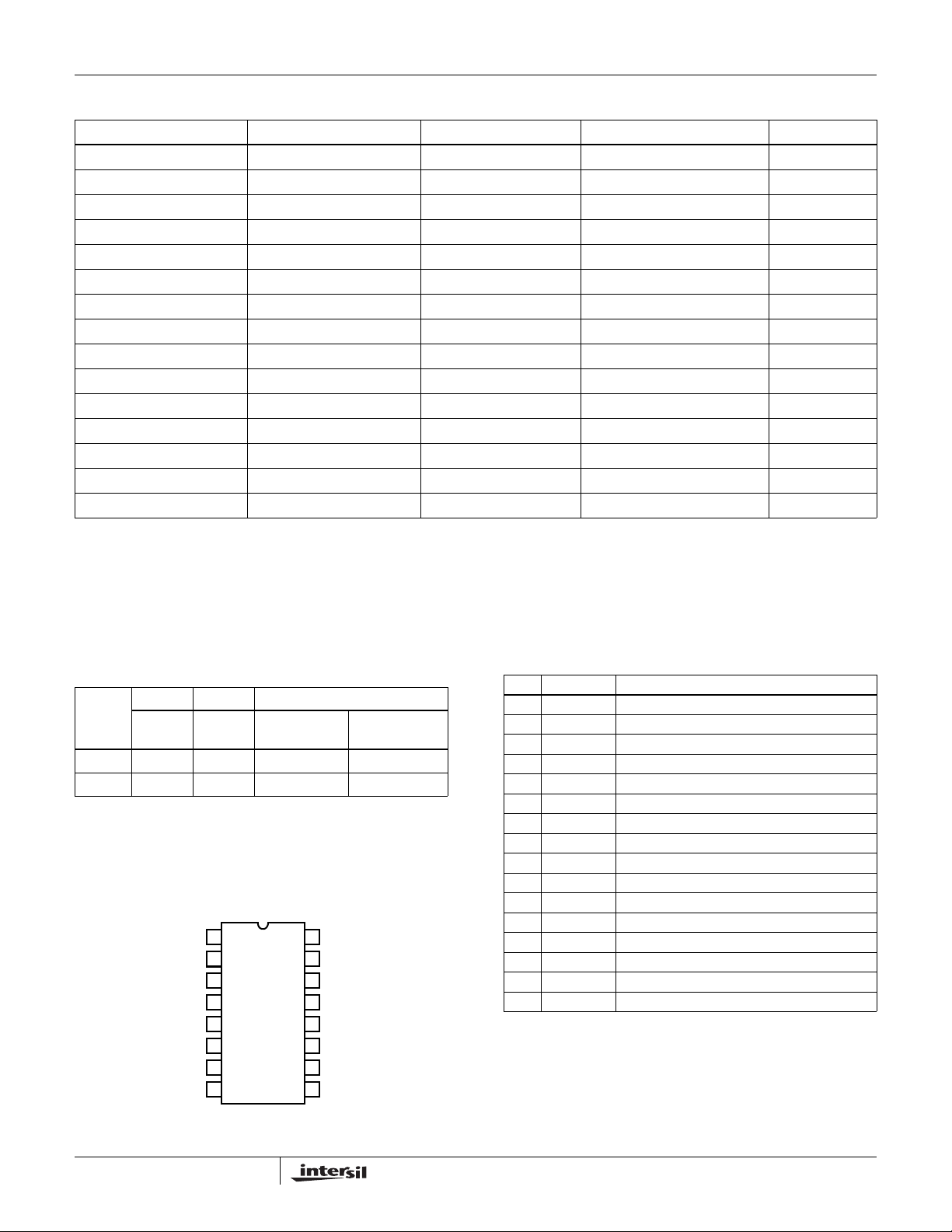

Ordering Information

PART NUMBER PART MARKING TEMP. RANGE (°C) PACKAGE PKG. DWG. #

DG411DJ DG411DJ -40 to +85 16 Ld PDIP E16.3

DG411DJZ (Note) DG411DJZ -40 to +85 16 Ld PDIP** (Pb-free) E16.3

DG411DY* DG411DY -40 to +85 16 Ld SOIC (150 mil) M16.15

DG411DYZ* (Note) DG411DYZ -40 to +85 16 Ld SOIC (150 mil) (Pb-free) M16.15

DG411DVZ* (Note) DG411 DVZ -40 to +85 16 Ld TSSOP (4.4mm) (Pb-free) M16.173

DG412DJ DG412DJ -40 to +85 16 Ld PDIP E16.3

DG412DJZ (Note) DG412DJZ -40 to +85 16 Ld PDIP** (Pb-free) E16.3

DG412DY* DG412DY -40 to +85 16 Ld SOIC (150 mil) M16.15

DG412DYZ* (Note) DG412DYZ -40 to +85 16 Ld SOIC (150 mil) (Pb-free) M16.15

DG412DVZ* (Note) DG412 DVZ -40 to +85 16 Ld TSSOP (4.4mm) (Pb-free) M16.173

DG413DJ DG413DJ -40 to +85 16 Ld PDIP E16.3

DG413DJZ (Note) DG413DJZ -40 to +85 16 Ld PDIP** (Pb-free) E16.3

DG413DY* DG413DY -40 to +85 16 Ld SOIC (150 mil) M16.15

DG413DYZ* (Note) DG413DYZ -40 to +85 16 Ld SOIC (150 mil) (Pb-free) M16.15

DG413DVZ* (Note) DG413 DVZ -40 to +85 16 Ld TSSOP (4.4mm) (Pb-free) M16.173

*Add “-T” suffix for tape and reel.

**Pb-free PDIPs can be used for through ho le wave so ld er p r ocessin g only. They are not intended for use in Re flow solder proce ssing

applications.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin

plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products

are MSL classified at Pb-free peak re flo w t em per atur e s th at me et or e xcee d the Pb -f re e re qu ire me nts of IP C/ JE DEC J ST D-02 0.

TRUTH TABLE

DG411 DG412 DG413

LOGIC

SWITCH SWITCH

SWITCH

1, 4

SWITCH

2, 3

0OnOff Off On

1 Off On On Off

NOTE: Logic “0” ≤0.8V. Logic “1” ≥2.4V.

Pinout

DG411, DG412, DG413

(16 LD PDIP, SOIC, TSSOP)

TOP VIEW

16

IN

D

S

GND

S

D

IN

1

1

2

1

3

1

4

V-

5

6

4

7

4

8

4

IN

2

15

D

2

14

S

2

13

V+

V

12

L

11

S

3

10

D

3

9

IN

3

Pin Descriptions

PIN SYMBOL DESCRIPTION

1IN

2D

3S

4 V- Negative Power Supply Terminal.

5 GND Ground Terminal (Logic Common).

6S

7D

8IN

9IN

10 D

11 S

12 V

13 V+ Positive Power Supply Terminal (Substrate).

14 S

15 D

16 IN

Logic Control for Switch 1.

1

Drain (Output) Terminal for Switch 1.

1

Source (Input) Terminal for Switch 1.

1

Source (Input) Terminal for Switch 4.

4

Drain (Output) Terminal for Switch 4.

4

Logic Control for Switch 4.

4

Logic Control for Switch 3.

3

Drain (Output) Terminal for Switch 3.

3

Source (Input) Terminal for Switch 3.

3

Logic Reference Voltage.

L

Source (Input) Terminal for Switch 2.

2

Drain (Output) Terminal for Switch 2.

2

Logic Control for Switch 2.

2

2

FN3282.13

June 20, 2007

Page 3

DG411, DG412, DG413

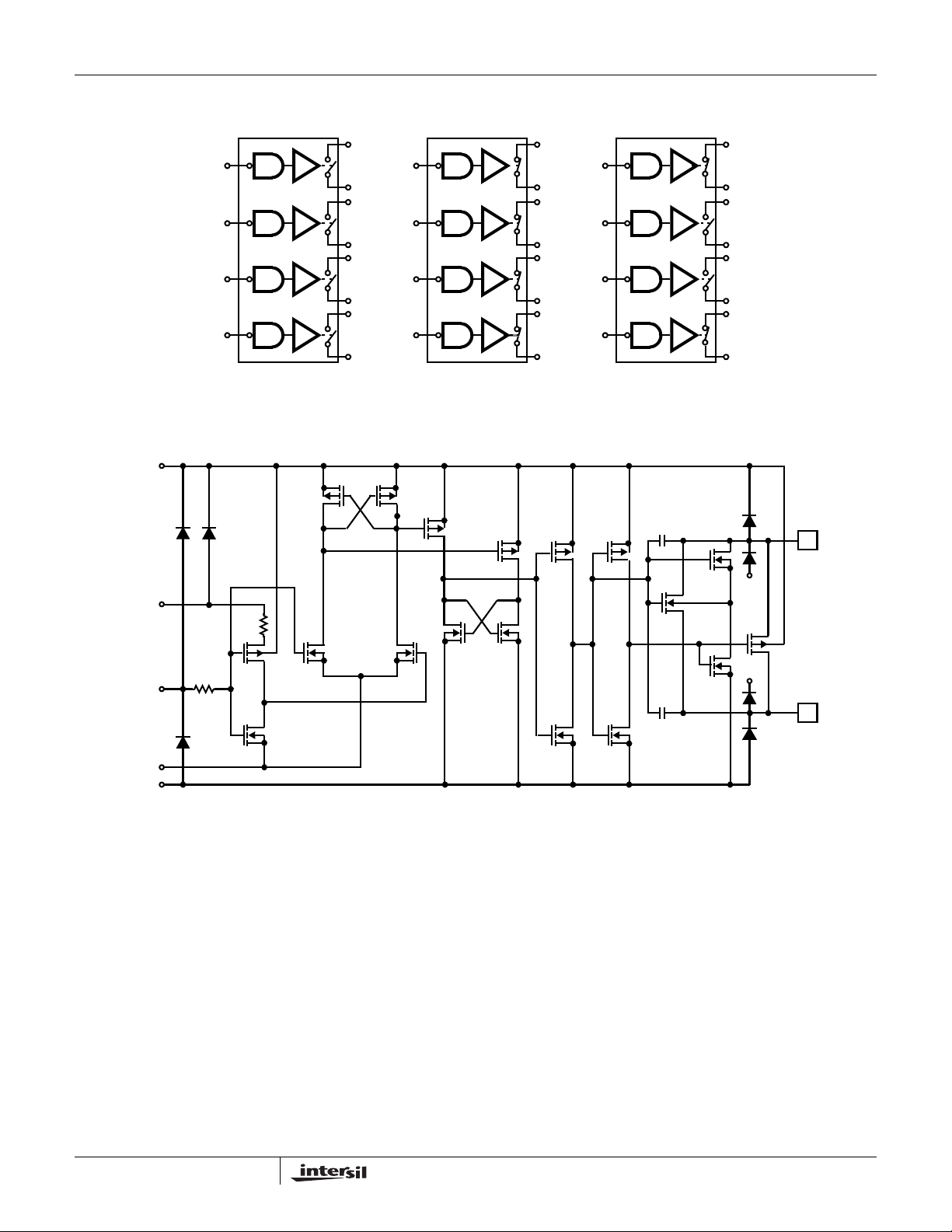

Functional Diagrams Four SPST Switches per Package Switches Shown for Logic “1” Input

DG411

S

1

IN

1

IN

2

IN

3

IN

4

IN

1

D

1

S

2

IN

2

D

2

S

3

IN

3

D

3

S

4

IN

4

D

4

DG412

DG413

S

1

IN

1

D

1

S

2

IN

2

D

2

S

3

IN

3

D

3

S

4

IN

4

D

4

Schematic Diagram (1 Channel)

V+

S

1

D

1

S

2

D

2

S

3

D

3

S

4

D

4

IN

GND

S

V-

V

L

V+

X

D

V-

3

FN3282.13

June 20, 2007

Page 4

DG411, DG412, DG413

Absolute Maximum Ratings Thermal Information

V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44V

GND to V-. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25V

V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . (GND -0.3V) to (V+) +0.3V

L

Digital Inputs, V

, VD (Note 1). . . . . (V-) -2V to (V+) + 2V or 30mA,

S

Whichever Occurs First

Continuous Current (Any Terminal) . . . . . . . . . . . . . . . . . . . . . 30mA

Peak Current, S or D (Pulsed 1ms, 10% Duty Cycle Max) . . 100mA

Operating Conditions

Voltage Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20V (Max)

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to +85°C

Input Low Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.8V (Max)

Input High Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.4V (Min)

Input Rise and Fall Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤20ns

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and

result in failures not covered by warranty.

NOTES:

1. Signals on S

is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

2. θ

JA

, DX, or INX exceeding V+ or V- will be clamped by internal diodes. Limit forward diode current to maximum current ratings.

X

Thermal Resistance (Typical, Note 2) θ

(°C/W)

JA

PDIP Package* . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

TSSOP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Maximum Junction Temperature (Plastic Packages). . . . . . .+150°C

Maximum Storage Temperature Range. . . . . . . . . .-65°C to +150°C

Pb-free reflow profile . . . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

(SOIC and TSSOP - Lead Tips Only)

*Pb-free PDIPs can be used for through hole wave solder

processing only. They are not intended for use in Reflow solder

processing applications.

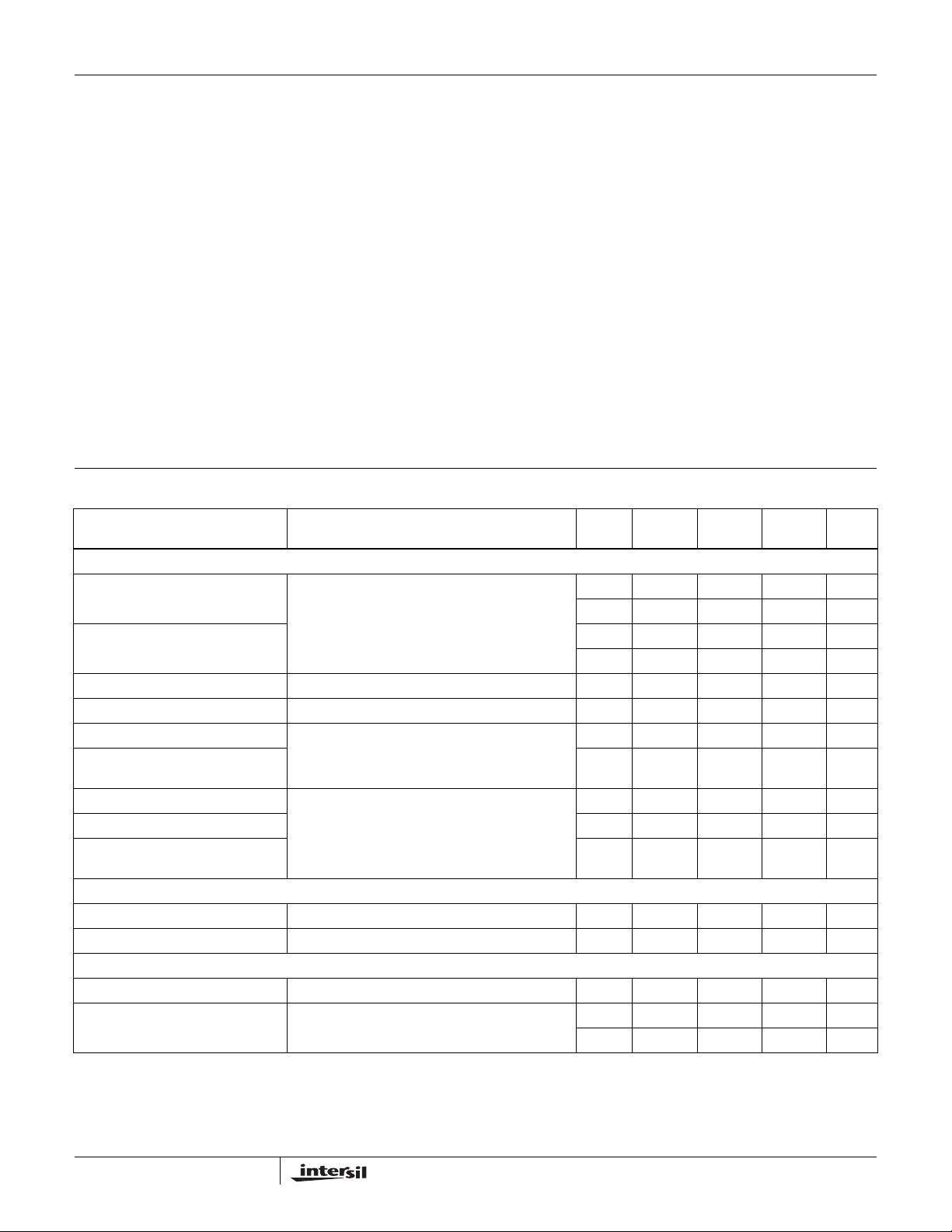

Electrical Specifications Test Conditions: V+ = +15V, V- = -15V, V

Unless Otherwise Specified.

PARAMETER TEST CONDITI ONS

= 5V, VIN = 2.4V, 0.8V (Note 3),

L

TEMP

(°C)

(Note 4)

MIN

TYP

(Note 5)

MAX

(Note 4) UNITS

DYNAMIC CHARACTERISTICS

Turn-ON Time, t

ON

RL = 300Ω, CL = 35pF, VS = ±10V (Figure 1) 25 - 110 175 ns

85 - - 220 ns

Turn-OFF Time, t

OFF

25 - 100 145 ns

85 - - 160 ns

Break-Before-Make Time Delay DG413 Only, R

Charge Injection, Q (Figure 3) C

= 10nF, VG = 0V, RG = 0Ω 25 - 5 - pC

L

= 300Ω, CL = 35pF (Figure 2) 25 - 25 - ns

L

OFF Isolation (Figure 5) RL = 50Ω, CL = 5pF, f = 1MHz 25 - 68 - dB

Crosstalk (Channel-to-Channel),

25 - -85 - dB

(Figure 4)

Source OFF Capacitance, C

Drain OFF Capacitance, C

Channel ON Capacitance,

C

+ C

D(ON)

S(ON)

S(OFF)

D(OFF)

f = 1MHz (Figure 6) 25 - 9 - pF

25 - 9 - pF

25 - 35 - pF

DIGITAL INPUT CHARACTERISTICS

Input Current V

Input Current V

Low, I

IN

High, I

IN

IL

IH

VIN Under Test = 0.8V, All Others = 2.4V Full -0.5 0.005 0.5 μA

VIN Under Test = 2.4V, All Others = 0.8V Full -0.5 0.005 0.5 μA

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, V

ANALOG

Drain-Source ON Resistance,

r

DS(ON)

±

IS = 10mA Full -15 - 15 V

±

IS = 10mA, VD = ±8.5V, V+ = 13.5V, V- = -13.5V 25 - 25 35 Ω

Full - - 45 Ω

4

FN3282.13

June 20, 2007

Page 5

DG411, DG412, DG413

Electrical Specifications Test Conditions: V+ = +15V, V- = -15V, V

Unless Otherwise Specified. (Continued)

PARAMETER TEST CONDITI ONS

Source OFF Leakage Current,

I

S(OFF)

Drain OFF Leakage Current,

I

D(OFF)

Channel ON Leakage Current,

I

+ I

D(ON)

S(ON)

V+ = 16.5V, V- = -16.5V, VD = ±15.5V, VS = 15.5V 25 -0.25 ±0.1 0.25 nA

V+ = 16.5V, V- = -16.5V, VS = VD = ±15.5V 25 -0.4 ±0.1 0.4 nA

= 5V, VIN = 2.4V, 0.8V (Note 3),

L

TEMP

(°C)

(Note 4)

±

Full -5 - +5 nA

25 -0.25 ±0.1 0.25 nA

Full -5 - +5 nA

Full -10 - +10 nA

MIN

TYP

(Note 5)

MAX

(Note 4) UNITS

POWER SUPPLY CHARACTERISTICS

Positive Supply Current, I+ V+ = 16.5V, V- = -16.5V, V

= 0V or 5V 25 - 0.0001 1 μA

IN

85 - - 5 μA

Negat i v e Su p p l y C ur r e n t , I- 25 -1 -0.0001 - μA

85 -5 - - μA

Logic Supply Current, I

L

25 - 0.0001 1 μA

85 - - 5 μA

Ground Current, I

GND

25 -1 -0.0001 - μA

85 -5 - - μA

Electrical Specifications (Single Supply) Test Conditions: V+ = +12V, V- = 0V, V

Unless Otherwise Specified.

PARAMETER TEST CONDITIONS

DYNAMIC CHARACTERISTICS

Turn-ON Time, t

Turn-OFF Time, t

ON

OFF

RL = 300Ω, CL = 35pF,

V

= 8V, (Figure 1)

S

Break-Before-Make Time Delay DG413 Only, R

C

= 35pF, VS = 8V

L

Charge Injection, Q C

= 10nF, VG = 6.0V, RG = 0Ω 25 - 25 - pC

L

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, V

Drain-Source ON-Resistance,

r

DS(ON)

ANALOG

IS = -10mA, VD = 3V, 8V

V+ = 10.8V

= 300Ω,

L

TEMP

(°C)

25 - 175 250 ns

85 - - 315 ns

25 - 95 125 ns

85 - - 140 ns

25 - 25 - ns

Full 0 - 12 V

25 - 40 80 Ω

Full - - 100 Ω

= 5V, VIN = 2.4V, 0.8V (Note 3),

L

MIN

(Note 4)

TYP

(Note 5)

MAX

(Note 4) UNITS

5

FN3282.13

June 20, 2007

Page 6

R

DG411, DG412, DG413

Electrical Specifications (Single Supply) Test Conditions: V+ = +12V, V- = 0V, V

Unless Otherwise Specified. (Continued)

TEMP

PARAMETER TEST CONDITIONS

(°C)

= 5V, VIN = 2.4V, 0.8V (Note 3),

L

MIN

(Note 4)

TYP

(Note 5)

MAX

(Note 4) UNITS

POWER SUPPLY CHARACTERISTICS

Positive Supply Current, I+ V+ = 13.2V, V- = 0V

V

= 0V or 5V

IN

25 - 0.0001 1 μA

85 - - 5 μA

Negative Supply Current, I- 25 -1 -0.0001 - μA

85 -5 - - μA

Logic Supply Current, I

L

25 - 0.0001 1 μA

85 - - 5 μA

Ground Current, I

GND

25 -1 -0.0001 - μA

85 -5 - - μA

NOTES:

= input voltage to perform proper function.

3. V

IN

4. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

5. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

Test Circuits and Waveforms

VO is the steady state output with the switch on. Feedthrough via switch capacitance may result in spikes at the leading and trailing

edge of the output waveform.

tr < 20ns

< 20ns

t

f

90%

LOGIC

INPUT

SWITCH

INPUT

SWITCH

OUTPUT

3V

t

50%

V

O

ON

90%

t

OFF

0V

V

S

0V

NOTE: Logic input waveform is inverted for sw itches that have the

opposite logic sense.

FIGURE 1A. MEASUREMENTS POINTS

FIGURE 1. SWITCHING TIMES

3V

LOGIC

INPUT

SWITCH

OUTPUT

SWITCH

OUTPUT

(V01)

V

O2

0V

V

S1

90%

0V

V

S2

90%

0V

t

D

t

D

FIGURE 2A. MEASUREMENT POINTS FIGURE 2B. TEST CIRCUITS

FIGURE 2. BREAK-BEFORE-MAKE TIME

V+

V-

-15V

SWITCH

INPUT

LOGIC

INPUT

V

L

S

1

IN

1

GND

Repeat test for all IN and S.

For load conditions, see Specifications. C

capacitance.

VOV

=

S

L

------------------------------------

RLr

+

DS ON()

FIGURE 1B. TEST CIRCUIT

+15V+5V

GND

V+

D

1

D

2

R

L2

300Ω

V-

-15V

V

S1

V

S2

LOGIC

INPUT

= 10V

= 10V

IN1, IN

V

L

S

1

S

2

2

+15V+5V

SWITCH

D

1

includes fixture and stray

L

V

O2

300Ω

C

L2

35pF

OUTPUT

R

L

R

C

L1

CL includes fixture and

stray capacitance.

L

V

V

O1

C

L1

35pF

O

6

FN3282.13

June 20, 2007

Page 7

DG411, DG412, DG413

Test Circuits and Waveforms (Continued)

V

G

SIGNAL

GENERATOR

R

G

GND

FIGURE 3A. TEST CIRCUIT

V+

C

V

0dBm

S

V+

VIN = 3V

+15V

SWITCH

OUTPUT

D

1

V-

V

O

IN

X

OFF

C

L

OFF OFF

IN

X

NOTE: IN

dependent on switch configuration, input polarity

X

Q = ΔV

ON

ON

x C

O

ΔV

O

OFF

L

determined by sense of switch.

FIGURE 3B. MEASUREMENT POINTS

FIGURE 3. CHARGE INJECTION

+15V

V+

C

V

D

50Ω

SIGNAL

GENERATOR

0dBm

V

S

ANALYZER

IN

-15V

X

V-

C

0V, 2.4V

R

L

IN

1

V

D

GND

-15V

IN

2

V-

C

0V, 2.4V

NC

ANALYZER

V

D

R

L

GND

FIGURE 4. CROSSTALK TEST CIRCUIT FIGURE 5. OFF ISOLATION TEST CIRCUIT

+15V

V+

C

V

S

IN

0V, 2.4V

-15V

X

V-

C

IMPEDANCE

ANALYZER

f = 1MHz

V

D

GND

0V, 2.4V

FIGURE 6. SOURCE/DRAIN CAPACITANCES TEST CIRCUIT

7

FN3282.13

June 20, 2007

Page 8

DG411, DG412, DG413

Application Information

Single Supply Operation

The DG411, DG412, DG413 can be operated with unipolar

supplies from 5V to 44V. These devices are characterized

and tested for single supply operation at 12V to facilit ate the

majority of applications. To function properly, 12V is tied to

Pins 13 and 0V is tied to Pin 4.

Pin 12 still requires 5V for TTL compatible switching.

V

IN1

V

IN2

Summing Amplifier

When driving a high impedance, high capacitance load such

as shown in Figure 7, where the inputs to the summing

amplifier have some noise filtering, it is necessary to have

shunt switches for rapid discharge of the filter capacitor, thus

preventing offsets from occurring at the output.

R

1

R

3

R

2

C

1

R

5

R

4

+

V

OUT

C

2

DG413

FIGURE 7. SUMMING AMPLIFIER

R

6

8

FN3282.13

June 20, 2007

Page 9

Typical Performance Curves

DG411, DG412, DG413

50

A: ±5V

45

B: ±8V

C: ±10V

40

D: ±12V

E: ±15V

35

F: ±20V

30

(Ω)

25

20

DS(ON)

r

15

10

5

0

-20 -15 -10 -5 0 5 2010 15

DRAIN VOLTAGE (V)

A

B

C

D

E

TA = +25°C

FIGURE 8. ON RESISTANCE vs VD AND POWER SUPPL Y

F

240

V+ = 15V, V- = -15V

210

V

= 5V, VS = 10V

L

180

150

(ns)

120

OFF

, t

90

ON

t

60

30

0

-55 -15 5 25 45 65 12585 105

-35

TEMPERATURE (°C)

t

ON

t

OFF

FIGURE 9. SWITCHING TIME vs TEMPERATURE

VOLTAGE

40

V+ = 15V, V- = -15V

30

= 5V, TA = +25°C

V

L

20

I

S, VD

I

S(OFF)

(V)

D(OFF)

I

D(ON)

10

0

(pA)

-10

D

, I

S

-20

I

-30

-40

-50

-60

-15 -5 0 5 10 15

-10

V

+ I

S(ON)

100mA

SUPPLY

I

V+ = 15V, V- = -15V

V

= 5V

10mA

100μA

100nA

L

1mA

10μA

1μA

1SW

10nA

10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

I+, I-

4SW

4SW

1SW

I

L

FIGURE 10. LEAKAGE CURRENTS vs ANALOG VOLTAGE FIGURE 11. SUPPLY CURRENT vs INPUT SWITCHING

FREQUENCY

100

V+ = 15V, V- = -15V

= 5V

V

L

80

60

40

20

Q (pC)

0

-20

-40

-60

CL = 1nF

-15 -5 0 5 10 15

-10

(V)

V

S

CL = 10nF

140

V+ = 15V, V- = -15V

120

= 5V

V

L

100

80

60

40

Q (pC)

20

0

-20

-40

-60

-15 -5 0 5 10 15

-10

(V)

V

D

CL = 10nF

CL = 1nF

FIGURE 12. CHARGE INJECTION vs SOURCE VOLTAGE FIGURE 13. CHARGE INJECTION vs DRAIN VOLTAGE

9

FN3282.13

June 20, 2007

Page 10

Die Characteristics

DG411, DG412, DG413

DIE DIMENSIONS:

2760mm x 1780mm x 485mm

METALLIZATION:

Type: SiAl

Thickness: 12k

Å ±1kÅ

Metallization Mask Layout

S1(3)

PASSIVATION:

Type: Nitride

Thickness: 8kÅ ±1kÅ

WORST CASE CURRENT DENSITY:

1.5 x 10

DG411, DG412, DG413

D

1

(2) (1) (16)

IN

1

IN

5

2

A/cm

2

(15) D

2

(14) S

2

V- (4)

GND (5)

(6)

S

4

(13) V+ SUBSTRATE

(12) V

L

(11) S

3

D

4

IN

4

IN

3

(10)(9)(8)(7)

D

3

10

FN3282.13

June 20, 2007

Page 11

DG411, DG412, DG413

Thin Shrink Small Outline Plastic Packages (TSSOP)

N

INDEX

AREA

123

-A-

E1

SEATING PLANE

D

E

-B-

A

-C-

α

e

b

0.10(0.004) C AM BS

M

NOTES:

1. These package dimensions are within allowable dimensions of

JEDEC MO-153-AB, Issue E.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate

burrs. Mold flash, protrusion and gate burrs shall not exceed

0.15mm (0.006 inch) per side.

4. Dimension “E1” does not include interlead flash or protrusions.

Interlead flash and protrusions shall not exceed 0.15mm (0.006

inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual

index feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. Dimension “b” does not include dambar protrusion. Allowable

dambar protrusion shall be 0.08mm (0.003 inch) total in excess

of “b” dimension at maximum material condition. Minimum space

between protrusion and adjacent lead is 0.07mm (0.0027 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact. (Angles in degrees)

A1

c

0.10(0.004)

11

FN3282.13

June 20, 2007

Page 12

DG411, DG412, DG413

Dual-In-Line Plastic Packages (PDIP)

N

D1

E1

-B-

-C-

A1

A2

E

A

L

e

C

C

L

e

A

C

e

B

INDEX

AREA

BASE

PLANE

SEATING

PLANE

D1

B1

12 3 N/2

-AD

e

B

0.010 (0.25) C AM BS

NOTES:

1. Controlling Dimensions: INCH. In case of conflict between English and

Metric dimensions, the inch dimensions control.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication No. 95.

4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

5. D, D1, and E1 dimensions do not include mold flash or protrusions.

Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

6. E and are measured with the leads constrained to be perpendic-

7. e

e

A

ular to datum .

and eC are measured at the lead tips with the leads unconstrained.

B

e

must be zero or greater.

C

-C-

8. B1 maximum dimensions do not include dambar protrusions. Dambar

protrusions shall not exceed 0.010 inch (0.25mm).

9. N is the maximum number of terminal positions.

10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3,

E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

E16.3 (JEDEC MS-001-BB ISSUE D)

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A - 0.210 - 5.33 4

A1 0.015 - 0.39 - 4

A2 0.115 0.195 2.93 4.95 -

B 0.014 0.022 0.356 0.558 B1 0.045 0.070 1.15 1.77 8, 10

C 0.008 0.014 0.204 0.355 -

D 0.735 0.775 18.66 19.68 5

D1 0.005 - 0.13 - 5

E 0.300 0.325 7.62 8.25 6

E1 0.240 0.280 6.10 7.11 5

e 0.100 BSC 2.54 BSC -

e

A

e

B

0.300 BSC 7.62 BSC 6

- 0.430 - 10.92 7

L 0.115 0.150 2.93 3.81 4

N16 169

NOTESMIN MAX MIN MAX

Rev. 0 12/93

12

FN3282.13

June 20, 2007

Page 13

DG411, DG412, DG413

Small Outline Plastic Packages (SOIC)

N

INDEX

AREA

123

-A-

E

-B-

SEATING PLANE

D

A

-C-

0.25(0.010) BM M

H

L

h x 45°

α

e

B

0.25(0.010) C AM BS

M

NOTES:

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead

flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater above

the seating plane, shall not exceed a maximum value of 0.61mm

(0.024 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions are

not necessarily exact.

A1

C

0.10(0.004)

M16.15 (JEDEC MS-012-AC ISSUE C)

16 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

INCHES MILLIMETERS

SYMBOL

A 0.0532 0.0688 1.35 1.75 -

A1 0.0040 0.0098 0.10 0.25 -

B 0.013 0.020 0.33 0.51 9

C 0.0075 0.0098 0.19 0.25 D 0.3859 0.3937 9.80 10.00 3

E 0.1497 0.1574 3.80 4.00 4

e 0.050 BSC 1.27 BSC H 0.2284 0.2440 5.80 6.20 h 0.0099 0.0196 0.25 0.50 5

L 0.016 0.050 0.40 1.27 6

N16 167

α

0° 8° 0° 8° -

NOTESMIN MAX MIN MAX

Rev. 1 6/05

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation’s quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without

notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implicat ion or oth erwise u nde r any p a tent or p at ent r ights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

13

FN3282.13

June 20, 2007

Loading...

Loading...