Intersil Corporation DG408, DG409 Datasheet

DG408, DG409

Data Sheet June 1999

Single 8-Channel/Differential 4-Channel,

CMOS Analog Multiplexers

The DG408 Single 8-Channel, and DG409 Differential

4-Channel monolithic CMOS analog multiplexersaredrop-in

replacements for the popular DG508A and DG509A series

devices. They each include an array of eight analog

switches, a TTL/CMOS compatible digital decode circuit for

channel selection, a voltage reference for logic thresholds

and an ENABLE input for device selection when several

multiplexers are present.

The DG408 and DG409 feature lower signal ON resistance

(<100Ω) and faster switch transition time (t

TRANS

< 250ns)

compared to the DG508A or DG509A. Charge injection has

been reduced, simplifyingsampleandhold applications. The

improvements in the DG408 series are made possible by

using a high-voltage silicon-gate process. An epitaxial layer

prevents the latch-up associated with older CMOS

technologies. Power supplies may be single-ended from +5V

to +34V, or split from ±5V to ±20V.

The analog switches are bilateral, equally matched for AC or

bidirectional signals. The ON resistance variation with

analog signals is quite low over a ±5V analog input range.

Ordering Information

PART

NUMBER

DG408DJ -40 to 85 16 Ld PDIP E16.3

DG408DY -40 to 85 16 Ld SOIC M16.15

DG409DJ -40 to 85 16 Ld PDIP E16.3

DG409DY -40 to 85 16 Ld SOIC M16.15

TEMP. RANGE

(oC) PACKAGE PKG. NO.

File Number

3283.5

Features

• ON Resistance (Max, 25oC). . . . . . . . . . . . . . . . . . . 100Ω

• Low Power Consumption (P

) . . . . . . . . . . . . . . . <11mW

D

• Fast Switching Action

-t

TRANS

-t

ON/OFF(EN)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .<250ns

. . . . . . . . . . . . . . . . . . . . . . . . . . . .<150ns

• Low Charge Injection

• Upgrade from DG508A/DG509A

• TTL, CMOS Compatible

• Single or Split Supply Operation

Applications

• Data Acquisition Systems

• Audio Switching Systems

• Automatic Testers

• Hi-Rel Systems

• Sample and Hold Circuits

• Communication Systems

• Analog Selector Switch

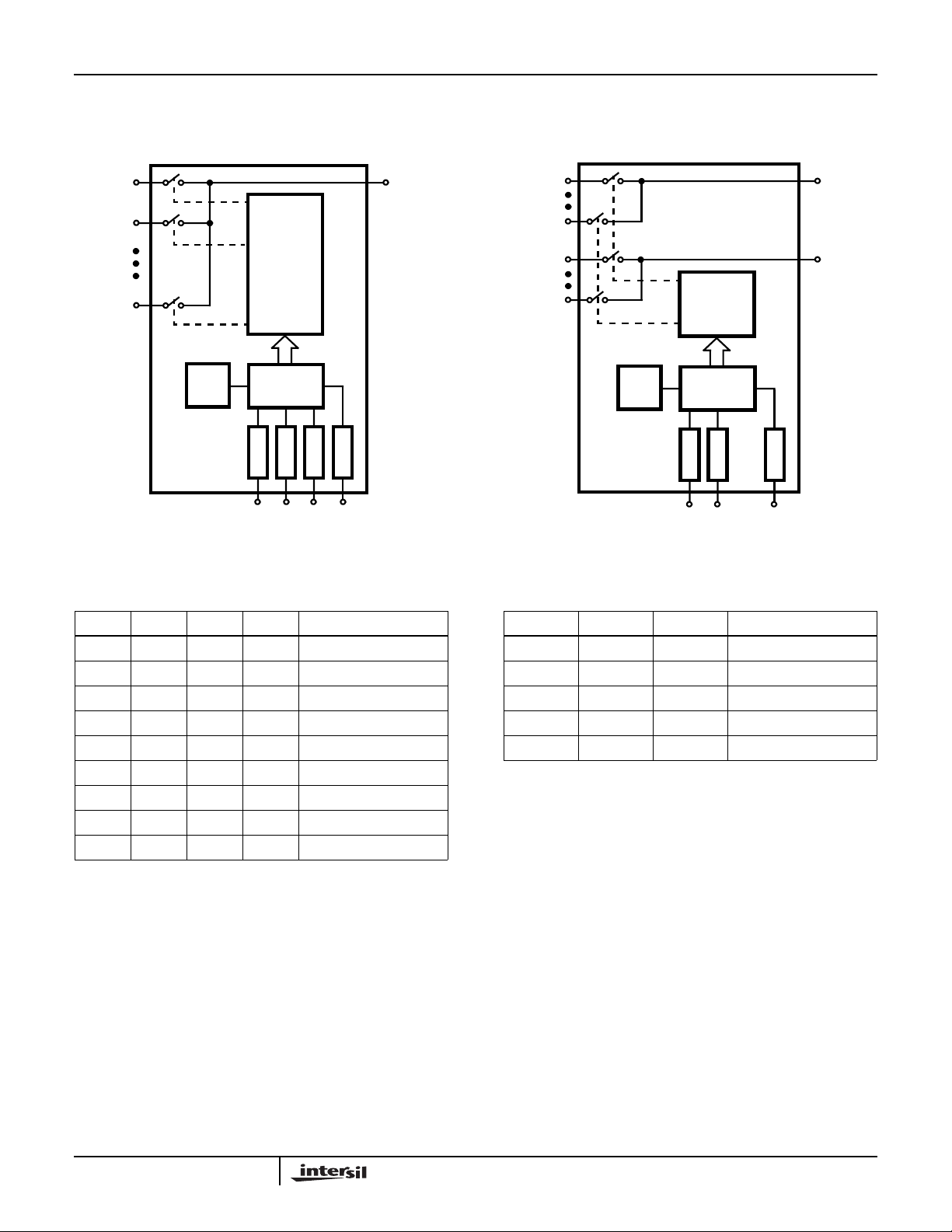

Pinouts

DG408 (PDIP, SOIC)

TOP VIEW

A

16

1

A

15

2

14

GND

13

V+

S

12

5

S

11

6

S

10

7

S

9

8

EN

A

1

0

2

3

V-

S

4

1

S

5

2

S

6

3

S

7

4

8

D

DG409 (PDIP, SOIC)

TOP VIEW

A

A

1

0

2

EN

3

V-

S

4

1A

S

5

2A

S

6

3A

S

7

4A

D

8

A

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

16

1

15

GND

14

V+

S

13

1B

S

12

2B

S

11

3B

S

10

4B

D

9

B

| Copyright © Intersil Corporation 1999

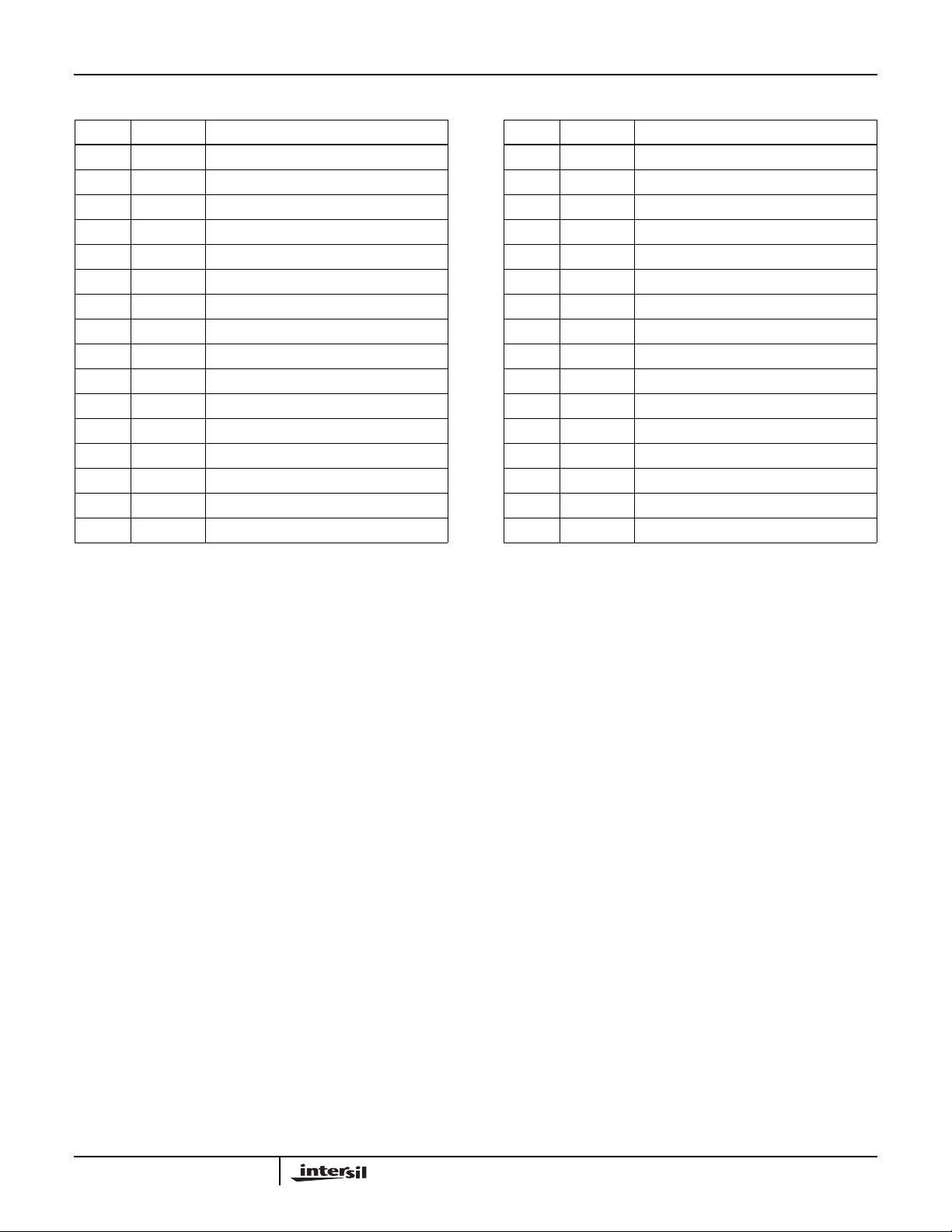

Functional Block Diagrams

DG408 DG409

DG408, DG409

S

1

S

2

S

8

5V

REF

DIGITAL

†

INPUT

PROTECTION

DECODER/

DRIVER

LEVEL

SHIFT

†† ††

A0A1A2EN

D

TRUTH TABLE DG408

A

A

2

A

1

EN ON SWITCH

0

X X X 0 NONE

0001 1

0011 2

0101 3

0111 4

1001 5

1011 6

1101 7

1111 8

S

1A

S

4A

S

1B

S

4B

5V

REF

DIGITAL

†

INPUT

PROTECTION

DECODER/

DRIVER

LEVEL

SHIFT

A0A

1

†††

EN

TRUTH TABLE DG409

A

1

A

0

EN ON SWITCH

X X 0 NONE

001 1

011 2

101 3

111 4

NOTES:

1. VAH Logic “1” ≥2.4V.

2. VAL Logic “0” ≤0.8V.

D

A

D

B

2

DG408, DG409

Pin Descriptions - (DG408)

PIN SYMBOL DESCRIPTION

1A0Logic Decode Input (Bit 0, LSB)

2 EN Enable Input

3 V- Negative Power Supply Terminal

4S1Source (Input) for Channel 1

5S2Source (Input) for Channel 2

6S3Source (Input) for Channel 3

7S4Source (Input) for Channel 4

8 D Drain (Output)

9S8Source (Input) for Channel 8

10 S

11 S

12 S

13 V+ Positive Power Supply Terminal (Substrate)

14 GND Ground Terminal (Logic Common)

15 A

16 A

Source (Input) for Channel 7

7

Source (Input) for Channel 6

6

Source (Input) for Channel 5

5

Logic Decode Input (Bit 2, MSB)

2

Logic Decode Input (Bit 1)

1

Pin Descriptions - (DG409)

PIN SYMBOL DESCRIPTION

1A0Logic Decode Input (Bit 0, LSB)

2 EN Enable Input

3 V- Negative Power Supply Terminal

4S1ASource (Input) for Channel 1a

5S2ASource (Input) for Channel 2a

6S3ASource (Input) for Channel 3a

7S4ASource (Input) for Channel 4a

8DADrain a (Output a)

9DBDrain b (Output b)

10 S

11 S

12 S

13 S

14 V+ Positive Power Supply Terminal

15 GND Ground Terminal (Logic Common)

16 A

Source (Input) for Channel 4b

4B

Source (Input) for Channel 3b

3B

Source (Input) for Channel 2b

2B

Source (Input) for Channel 1b

1B

Logic Decode Input (Bit 1, MSB)

1

3

DG408, DG409

Absolute Maximum Ratings Thermal Information

V+ to V- . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44.0V

GND to V-. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25V

Digital Inputs, VS, VD (Note 3). . . . . .(V-) -2V to (V+) + 2V or 20mA,

Whichever Occurs First

Continuous Current (Any Terminal) . . . . . . . . . . . . . . . . . . . . . 30mA

Peak Current, S or D (Pulsed 1ms, 10% Duty Cycle Max) . . 100mA

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operationofthe

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

3. Signals on SX, DX, EN or AX exceeding V+ or V- are clamped by internal diodes. Limit diode current to maximum current ratings.

4. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 4) θJA (oC/W)

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 125oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC - Lead Tips Only)

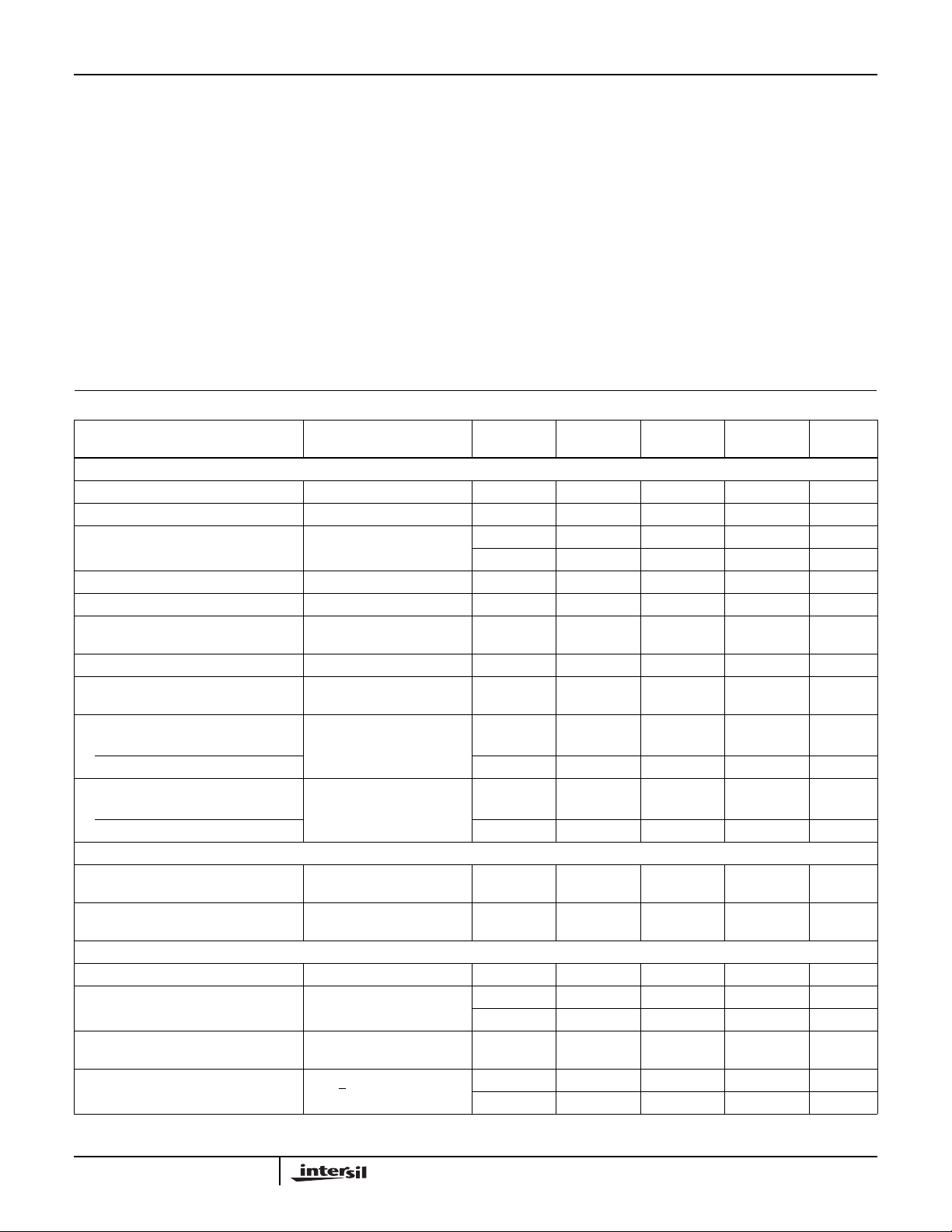

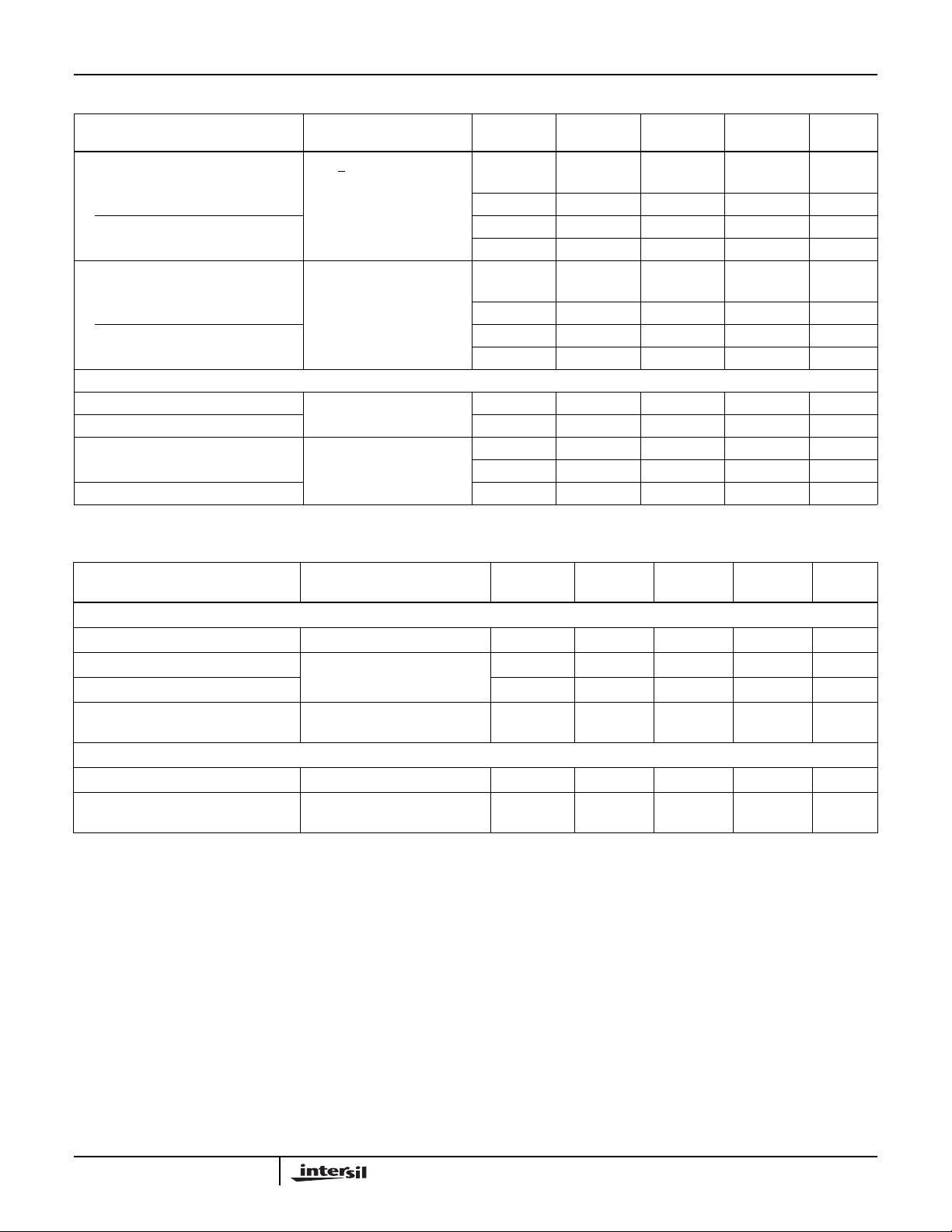

Electrical Specifications Test Conditions: V+ = +15V, V- = -15V, V

PARAMETER TEST CONDITIONS TEMP (oC)

= 0.8V, VAH = 2.4V, Unless Otherwise Specified

AL

(NOTE 5)

MIN

(NOTE 6)

TYP

(NOTE 5)

MAX UNITS

DYNAMIC CHARACTERISTICS

Transition Time, t

TRANS

Break-Before-Make Interval, t

Enable Turn-ON Time, t

ON(EN)

OPEN

(See Figure 1) Full - 160 250 ns

(See Figure 3) 25 10 - - ns

(See Figure 2) 25 - 115 150 ns

Full - - 225 ns

Enable Turn-OFF Time, t

OFF(EN)

(See Figure 2) Full - 105 150 ns

Charge Injection, Q CL = 10nF, VS = 0V 25 - 20 - pC

OFF Isolation VEN = 0V, RL = 1kΩ,

25 - -75 - dB

f = 100kHz (Note 9)

Logic Input Capacitance, C

Source OFF Capacitance, C

IN

S(OFF)

f = 1MHz 25 - 8 - pF

VEN = 0V, VS = 0V,

25 - 3 - pF

f = 1MHz

Drain OFF Capacitance, C

D(OFF)

DG408 25 - 26 - pF

VEN = 0V, VD = 0V,

f = 1MHz

DG409 25 - 14 - pF

Drain ON Capacitance, C

D(ON)

DG408 25 - 37 - pF

VEN = 3V, VD = 0V,

f = 1MHz, VA = 0V or 3V

DG409 25 - 25 - pF

DIGITAL INPUT CHARACTERISTICS

Logic Input Current,

Input Voltage High, I

Logic Input Current,

Input Voltage Low, I

AH

AL

VA = 2.4V, 15V Full -10 - 10 µA

VEN = 0V, 2.4V,

Full -10 - 10 µA

VA = 0V

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, V

ANALOG

Drain-Source ON Resistance,

r

DS(ON)

r

Matching Between Channels,

DS(ON)

∆r

DS(ON)

Source OFF Leakage Current, I

VD = ±10V, IS= -10mA

(Note 7)

VD = 10V, -10V (Note 8) 25 - - 15 Ω

S(OFF)VEN

VD = +10V

= 0V, VS = ±10V,

Full -15 - 15 V

25 - 40 100 Ω

Full - - 125 Ω

25 -0.5 - 0.5 nA

Full -5 - 5 nA

4

DG408, DG409

Electrical Specifications Test Conditions: V+ = +15V, V- = -15V, V

PARAMETER TEST CONDITIONS TEMP (oC)

Drain OFF Leakage Current, I

D(OFF)

DG408 25 -1 - 1 nA

VEN = 0V, VD = ±10V,

VS = +10V

= 0.8V, VAH = 2.4V, Unless Otherwise Specified (Continued)

AL

(NOTE 5)

MIN

(NOTE 6)

TYP

(NOTE 5)

MAX UNITS

Full -20 - 20 nA

DG409 25 -1 - 1 nA

Full -10 - 10 nA

Drain ON Leakage Current, I

D(ON)

VS = VD = ±10V (Note 7)

DG408 25 -1 - 1 nA

Full -20 - 20 nA

DG409 25 -1 - 1 nA

Full -10 - 10 nA

POWER SUPPLY CHARACTERISTICS

Positive Supply Current, I+ VEN= 0V, VA= 0V (Standby) Full - 10 75 µA

Negative Supply Current, I- Full -75 1 - µA

Positive Supply Current, I+ VEN = 2.4V, VA = 0V

(Enabled)

25 - 0.2 0.5 mA

Full - - 2 mA

Negative Supply Current, I- Full -500 - - µA

Electrical Specifications Single Supply Test Conditions: V+ = 12V, V- = 0V, V

= 0.8V, VAH = 2.4V,

AL

Unless Otherwise Specified

PARAMETER

TEST

CONDITION TEMP (oC)

(NOTE 5)

MIN

(NOTE 6)

TYP

(NOTE 5)

MAX UNITS

DYNAMIC CHARACTERISTICS

Switching Time of Multiplexer, t

Enable Turn-ON Time, t

Enable Turn-OFF Time, t

TRANSVS1

ON(EN)

OFF(EN)

Charge Injection, Q CL = 10nF, V

= 8V, VS8 = 0V, VIN = 2.4V 25 - 180 - ns

V

= 2.4V, V

INH

VS1 = 5V

R

= 0Ω

GEN

INL

GEN

= 0V,

= 0V,

25 - 180 - ns

25 - 120 - ns

25 - 5 - pC

ANALOG SWITCH CHARACTERISTICS

Analog Signal Range, V

ANALOG

Drain-Source ON-Resistance,

r

DS(ON)

VD = 3V, 10V, IS = -1mA

(Note 7)

Full 0 - 12 V

25 - 90 - Ω

NOTES:

5. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

6. Typical values are for DESIGN AID ONLY, not guaranteed nor production tested.

7. Sequence each switch ON.

8. ∆r

DS(ON)

= r

DS(ON)

(Max) - r

DS(ON)

(Min).

9. Worst case isolation occurs on channel 4 due to proximity to the drain pin.

5

Loading...

Loading...