March 1997

CDP1854A,

CDP1854AC

Programmable Universal Asynchronous

Receiver/Transmitter (UART)

Features

• Two Operating Modes

- Mode 0 - Functionally Compatible with Industry

Types Such as the TR1602A and CDP6402

- Mode 1 - Interfaces Directly with CDP1800-Series

Microprocessors without Additional Components

• Full or Half Duplex Operation

• Parity, Framing and Overrun Error Detection

• Baud Rate

- DC to 200K Bits/s at V

- DC to 400K Bits/s at V

• Fully Programmable with Externally Selectable Word

Length (5-8 Bits), Parity Inhibit, Even/Odd Parity, and

1, 1-1/2, or 2 Stop Bits

• False Start Bit Detection

. . . . . . . . . . . . . . . . . . . . 5V

DD

. . . . . . . . . . . . . . . . . . . .10V

DD

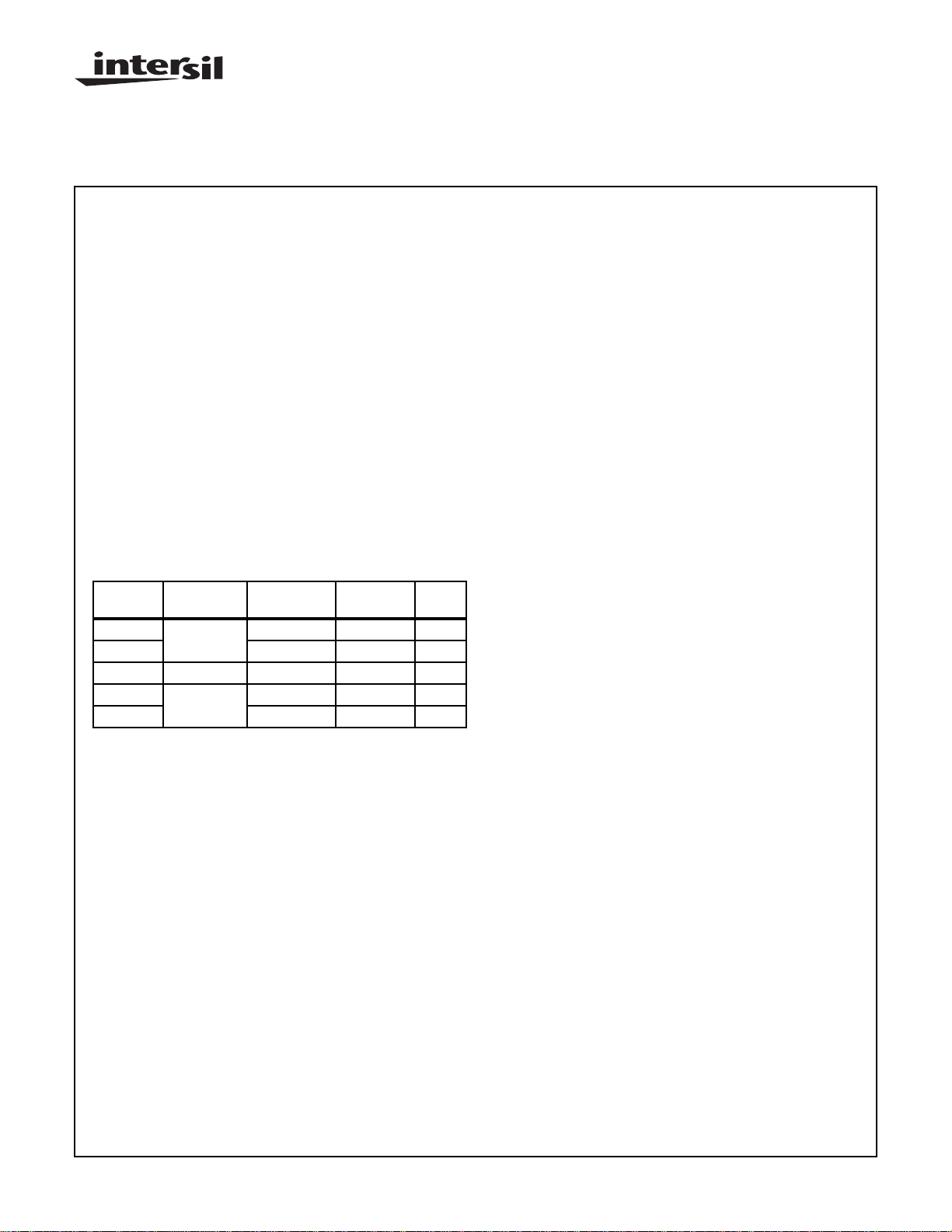

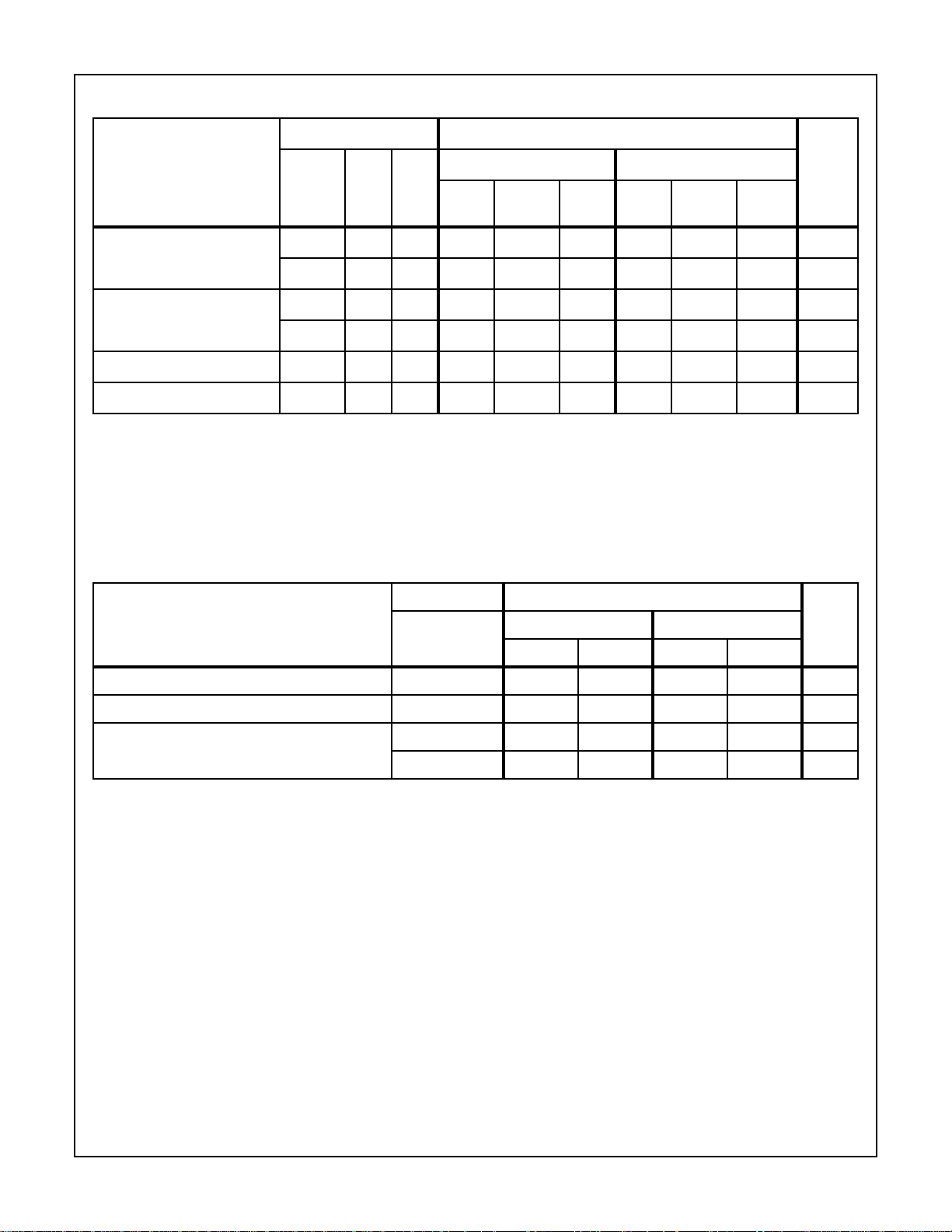

Ordering Information

TEMP.

PACKAGE

PDIP -40oC to +85oC CDP1854ACE CDP1854AE

Burn-In CDP1854ACEX CDP1854AEX

PLCC -40oC to +85oC CDP1854ACQ CDP1854AQ

SBDIP -40oC to +85oC CDP1854ACD CDP1854AD

Burn-In CDP1854ACDX -

RANGE

5V/200K

BAUD

10V/400K

BAUD

PKG.

NO.

E40.6

E40.6

N44.65

D40.6

D40.6

Description

The CDP1854A and CDP1854AC are silicon-gate CMOS

Universal Asynchronous Receiver/Transmitter (UART) circuits. They are designed to provide the necessary formatting

and control for interfacing between serial and parallel data.

For example , these U AR Ts can be used to interface between

a peripheral or terminal with serial I/O ports and the 8-bit

CDP1800-series microprocessor parallel data bus system.

The CDP1854A is capable of full duplex operation, i.e.,

simultaneous conversion of serial input data to parallel output data and parallel input data to serial output data.

The CDP1854A UART can be prog rammed to operate in one

of two modes by using the mode control input. When the

input is high (MODE = 1), the CDP1854A is directly compatible with the CDP1800-series microprocessor system without

additional interface circuitry. When the mode input is low

(MODE = 0), the device is functionally compatible with industry standard UART’s such as the TR1602A and CDP6402. It

is also pin compatible with these types, except that pin 2 is

used for the mode control input.

The CDP1854A and the CDP1854AC are functionally identical. The CDP1854A has a recommended operating voltage

range of 4V to 10.5V, and the CDP1854AC has a recommended operating voltage range of 4V to 6.5V.

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

5-42

File Number 1193.2

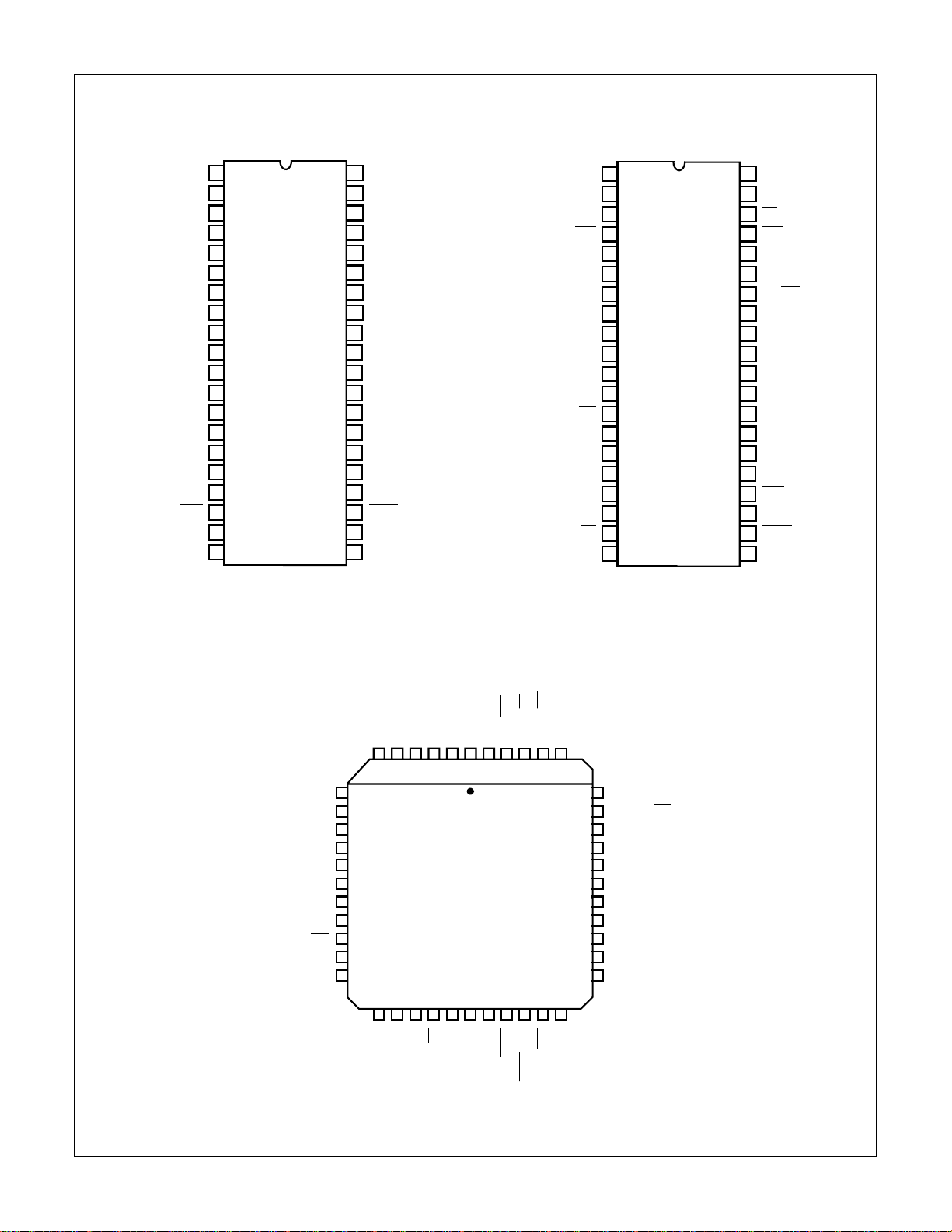

Pinouts

40 LEAD SBDIP, PDIP (MODE 0)

TOP VIEW

CDP1854A, CDP1854AC

40 LEAD SBDIP, PDIP (MODE 1)

TOP VIEW

V

DD

MODE (VSS)

V

SS

RRD

R BUS 7

R BUS 6

R BUS 5

R BUS 4

R BUS 3

R BUS 2

R BUS 1

R BUS 0

PE

FE

OE

SFD

R CLOCK

DAR

DA

SDI

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

T CLOCK

EPE

WLS 1

WLS 2

SBS

PI

CRL

T BUS 7

T BUS 6

T BUS 5

T BUS 4

T BUS 3

T BUS 2

T BUS 1

T BUS 0

SD0

TSRE

THRL

THRE

MR

V

DD

MODE (VDD)

V

SS

CS2

R BUS 7

R BUS 6

R BUS 5

R BUS 4

R BUS 3

R BUS 2

R BUS 1

R BUS 0

INT

FE

PE/OE

RSEL

R CLOCK

TPB

DA

SDI

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

NC = NO CONNECT

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

T CLOCK

CTS

ES

PS1

NC

CS3

RD/

WR

T BUS 7

T BUS 6

T BUS 5

T BUS 4

T BUS 3

T BUS 2

T BUS 1

T BUS 0

SD0

RTS

CS1

THRE

CLEAR

R BUS 6

R BUS 5

R BUS 4

R BUS 3

R BUS 2

NC

R BUS 1

R BUS 0

INT)

PE(

FE

OE(PE/OE)

NOTE:

MODE 0(MODE 1)

44 LEAD PLCC (Q SUFFIX)

TOP VIEW

CS2)

SS

R BUS 7

RRD (

MODE

V

V

7

8

9

10

11

12

13

14

15

16

17

20 21 22 23 24 25 261918

DA)

DAR

DA(

R CLOCK

(TPB)

SFD (RSEL)

DD

NC

T CLOCK

44 43 42 41 40

123456

NC

SDI

CLEAR)

MR(

ES)

EPE (CTS)

WLS1 (

THRE)

THRL(CS1)

THRE(

PSI)

WLS2 (

SBS (NC)

2827

SD0

RTS)

TSRE(

PI (CS3)

39

38

CRL(RD/

WR)

37

T BUS 7

36

T BUS 6

35

T BUS 5

34

NC

33

T BUS 4

32

T BUS 3

31

T BUS 2

30

T BUS 1

29

T BUS 0

5-43

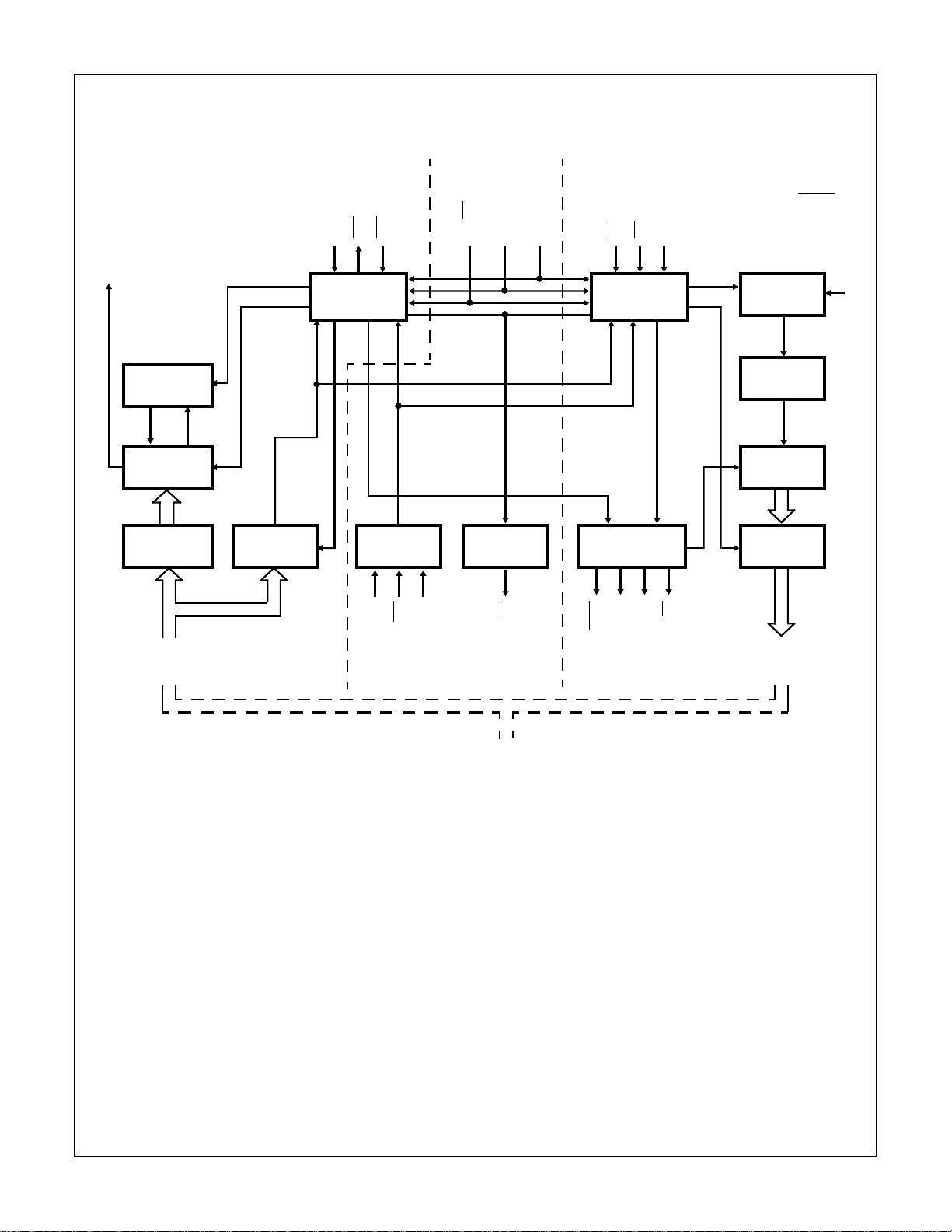

Block Diagram

Mode Input High (Mode = 1)

SDO

25

CDP1854A, CDP1854AC

TRANSMITTER SECTION

T CLOCK

RTS

CTS

40 24 39

TRANSMITTER

TIMING &

CONTROL

CDP1802

INTERFACE

RD/WR

TPB

34 18 16

RECEIVER SECTION

RSEL

38 37 17

ES

PSI

RECEIVER

TIMING &

CONTROL

R CLOCK

1, 2 = V

3 = V

21 = CLEAR

36 = NC

SHIFT

REGISTER

DD

SS

20

SDI

PARITY

GEN

TRANSMITTER

SHIFT

REGISTER

TRANSMITTER

HOLDING

REGISTER

TRANSMITTER BUS

(26 - 33)

(SEE NOTE 1)

NOTE: 1. User Interconnect

FIGURE 1. MODE 1 BLOCK DIAGRAM (CDP1800-SERIES MICROPROCESSOR COMPATIBLE)

CONTROL

REG

23

SELECT

LOGIC

4 35

CS1

CS2

CS3

INT

13

INT

(SEE NOTE 1)

STATUS

REGISTER

22 14 15

FE

THRE

19

PE/OE

RECEIVER

HOLDING

REGISTER

MUX

THREE-STATE

DRIVERS

DA

RECEIVER BUS

(5-12)

(SEE NOTE 1)

5-44

CDP1854A, CDP1854AC

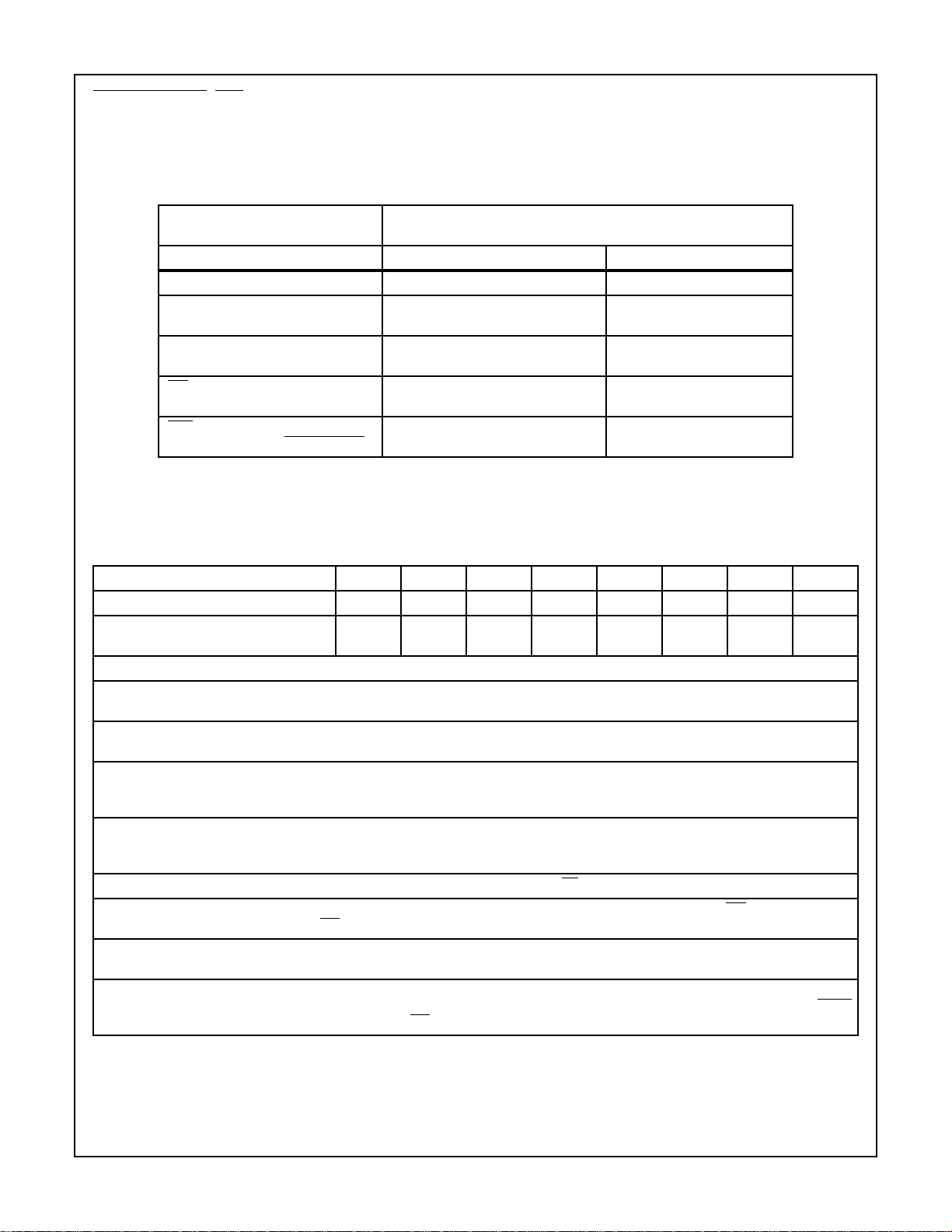

Absolute Maximum Ratings Thermal Information

DC Supply-Voltage Range, (VDD)

(Voltages Referenced to VSS Terminal)

CDP1854A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5 to +11V

CDP1854AC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5 to +7V

Input Voltage Range, All Inputs . . . . . . . . . . . . . .-0.5 to VDD + 0.5V

DC Input Current, Any One Input. . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Device Dissipation Per Output Transistor

TA = Full Package-Temperature Range . . . . . . . . . . . . . . 100mW

Operating-Temperature Range (TA)

Package Type D . . . . . . . . . . . . . . . . . . . . . . . . .-55oC to +125oC

Package Type E and Q . . . . . . . . . . . . . . . . . . . . .-40oC to +85oC

CAUTION: Stresses above those listed in “Absolute Maxim um Ratings” ma y cause permanent damage to the device . This is a stress only rating and oper ation of

the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

SBDIP Package. . . . . . . . . . . . . . . . . . 55 15

PDIP Package. . . . . . . . . . . . . . . . . . . 50 N/A

PLCC Package . . . . . . . . . . . . . . . . . . 46 N/A

Maximum Junction Temperature

Plastic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+150oC

Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

Maximum Storage Temperature Range (T

) . . .-65oC to +150oC

STG

Maximum Lead Temperature (Soldering 10s):

At Distance 1/16 ±1/32 inch (1.59 ±0.79mm) . . . . . . . . . .+265oC

NOTE: Printed circuit board mount: 57mm x 57mm minimum area x

1.6mm thick G10 epoxy glass, or equivalent.

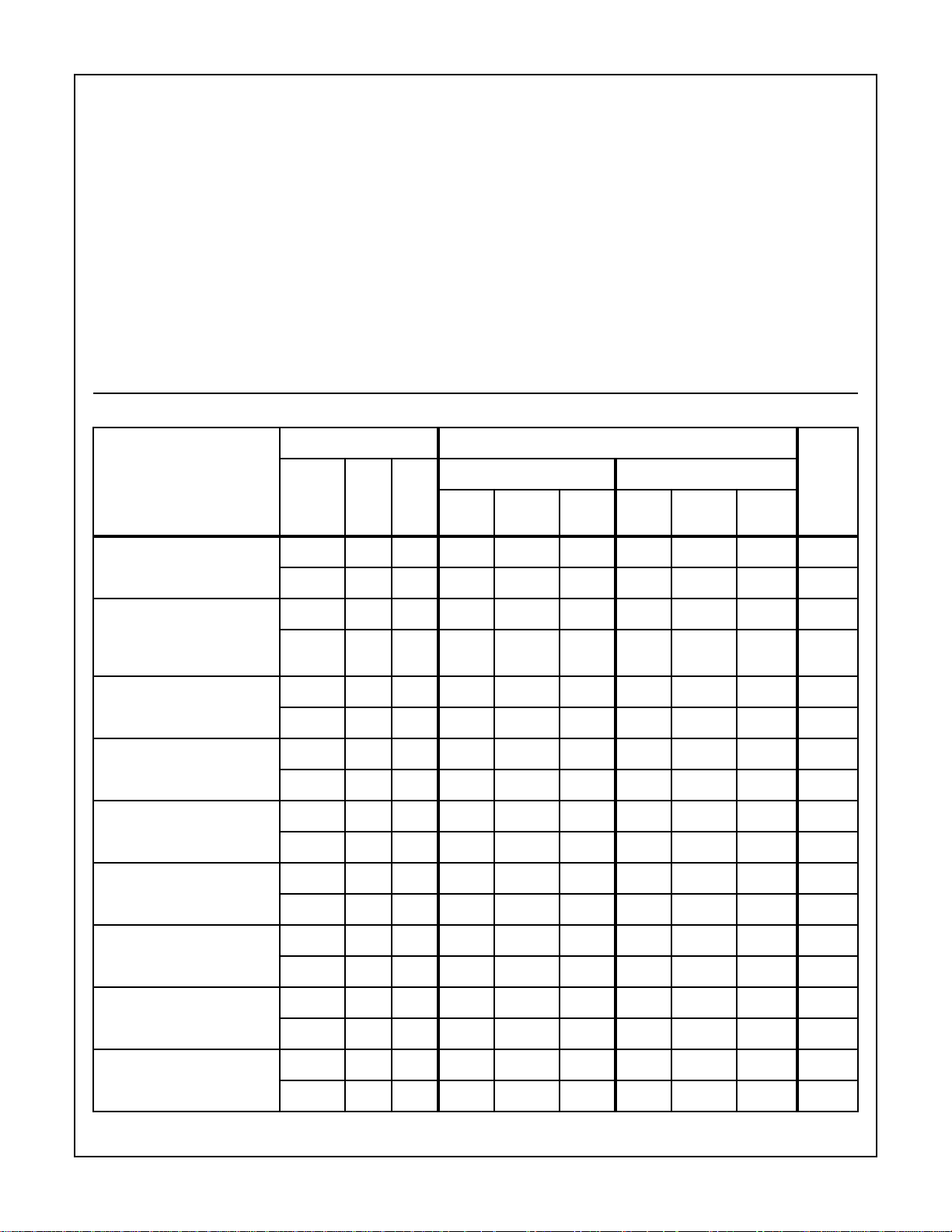

Static Electrical Specifications at T

CONDITIONS LIMITS

V

PARAMETER

Quiescent Device

Current

Output Low Drive

(Sink) Current

(Except pins 24 and

25)

Output High Drive

(Source) Current

Output Low Drive

(Sink) Current

(Pins 24 and 25)

Output Voltage

Low-Level (Note 2)

I

DD

I

OL

I

OH

I

OL

V

OL

O

(V)

- 0, 5 5 - 0.01 50 - 0.02 200 µA

- 0, 10 10 - 1 200 - - - µA

0.4 0, 5 5 1 2 - 1 2 - mA

0.5 0, 10 10 2 4 - - - - mA

4.6 0, 5 5 -0.55 -1.1 - -0.55 -1.1 - mA

9.5 0, 10 10 -1.3 -2.6 - - - - mA

0.4 0, 5 5 1.6 3.5 - 1.6 3.5 - mA

0.5 0, 10 10 3.2 7 - - - - mA

- 0, 5 5 - 0 0.1 - 0 0.1 V

- 0, 10 10 - 0 0.1 - - - V

= -40oC to +85oC, Unless Otherwise Noted

A

CDP1854A CDP1854AC

V

(V)

V

IN

DD

(V)

MIN

(NOTE 1)

TYP MAX MIN

(NOTE 1)

TYP MAX

UNITS

Output Voltage

High-Level (Note 2)

Input Low Voltage V

Input High Voltage V

Input Current I

V

OH

- 0, 5 5 4.9 5 - 4.9 5 - V

- 0, 10 10 9.9 10 - - - - V

0.5, 4.5 - 5 - - 1.5 - - 1.5 V

IL

0.5, 9.5 - 10 - - 3 - - - V

0.5, 4.5 - 5 3.5 - - 3.5 - - V

IH

0.5, 9.5 - 10 7 - - - - - V

IN

- 0, 5 5 - - ±1- - ±1 µA

- 0, 10 10 - - ±2- - - µA

5-45

CDP1854A, CDP1854AC

Static Electrical Specifications at T

= -40oC to +85oC, Unless Otherwise Noted (Continued)

A

CONDITIONS LIMITS

CDP1854A CDP1854AC

PARAMETER

Three-State Output

I

OUT

V

O

(V)

0, 5 0, 5 5 - - ±1- - ±1 µA

V

(V)

V

IN

DD

(V)

MIN

(NOTE 1)

TYP MAX MIN

(NOTE 1)

TYP MAX

UNITS

Leakage Current

0, 10 0, 10 10 - - ±10 - - - µA

Operating Current

I

DD1

- 0, 5 5 - 1.5 - - 1.5 - mA

(Note 3)

- 0, 10 10 - 6 - - - - mA

Input Capacitance C

Output Capacitance C

IN

OUT

- - - - 5 7.5 - 5 7.5 pF

- - - - 10 15 - 10 15 pF

NOTES:

1. Typical values are for TA= 25oC.

2. IOL = IOH = 1µA.

3. Operating current is measured at 200kHz or VDD = 5V and 400kHz for VDD = 10V in a CDP1800-series microprocessor system, with

open outputs.

Operating Conditions At T

= Full Package-Temperature Range. For maximum reliability, operating conditions should be selected so

A

that operation is always within the following ranges:

CONDITIONS LIMITS

CDP1854A CDP1854AC

V

PARAMETER

DD

(V)

MIN MAX MIN MAX

UNITS

DC Operating Voltage Range - 4 10.5 4 6.5 V

Input Voltage Range - V

SS

V

DD

V

SS

V

DD

V

Baud Rate (Receive or Transmit) 5 - 200 - 200 K bits/s

10 - 400 - - K bits/s

5-46

CDP1854A, CDP1854AC

Functional Definitions for CDP1854A

Terminals Mode 1 CDP1800-Series

Microprocessor Compatible

SIGNAL: FUNCTION

VDD:

Positive supply voltage.

MODE SELECT (MODE):

A high-level voltage at this input selects CDP1800-series

microprocessor Mode operation.

:

V

SS

Ground

CHIP SELECT 2 (CS2):

A low-level voltage at this input together with CS1 and CS3

selects the CDP1854A UART.

RECEIVER BUS (R BUS 7 - R BUS 0):

Receiver parallel data outputs (may be exter nally connected

to corresponding transmitter bus terminals).

INTERRUPT (INT):

A low-level voltage at this output indicates the presence of

one or more of the interrupt conditions listed in Table 1.

FRAMlNG ERROR (FE):

A high-level voltage at this output indicates that the received

character has no valid stop bit, i.e., the bit f ollowing the parity

bit (if programmed) is not a high-level voltage. This output is

updated each time a character is transferred to the Receiver

Holding Register.

PARITY ERROR or OVERRUN ERROR (PE/OE):

A high-level v oltage at this output indicates that either the PE

or OE bit in the Status Register has been set (see Status

Register Bit Assignment, Table 2).

REGISTER SELECT (RSEL):

This input is used to choose either the Control/Status

Registers (high input) or the transmitter/receiver data

registers (low input) according to the truth table in Table 3.

RECEIVER CLOCK (RCLOCK):

Clock input with a frequency 16 times the desired receiver

shift rate.

TPB:

A positive input pulse used as a data load or reset strobe.

DATA AVAILABLE (DA):

A low-level voltage at this output indicates that an entire

character has been received and transferred to the Receiver

Holding Register.

SERIAL DATA IN (SDl):

Serial data received on this input line enters the Receiver

Shift Register at a point determined by the character length.

A high-level input voltage must be present when data is not

being received.

CLEAR (CLEAR):

A low-level voltage at this input resets the Interrupt FlipFlop, Receiver Holding Register, Control Register, and

Status Register, and sets SERIAL DATA OUT (SDO) high.

TRANSMlTTER HOLDING REGISTER EMPTY (THRE):

A low-level voltage at this output indicates that the

Transmitter Holding Register has transferred its contents to

the Transmitter Shift Register and may be reloaded with a

new character.

CHIP SELECT 1 (CS1):

A high-level voltage at this input together with

selects the UART.

REQUEST TO SEND (RTS):

This output signal tells the peripheraI to get ready to receive

data.

CLEAR TO SEND (CTS) is the response from the

peripheral.

latched in the Transmitter Holding Register or TR is set high,

and is reset high when both the Transmitter Holding Register

and Transmitter Shift Register are empty and TR is low.

SERAL DATA OUTPUT (SDO):

The contents of the Transmitter Shift Register [star t bit, data

bits, parity bit, and stop bit(s)] are serially shifted out on this

output. When no character is being transmitted, a high level

is maintained. Start of transmission is defined as the

transition of the start bit from a high-level to a low-level

output voltage.

TRANSMlTTER BUS (T BUS 0 - T BUS 7):

Transmitter parallel data input. These may be externally

connected to corresponding Receiver bus terminals.

RD/

WR:

A low-level v oltage at this input gates data from the tr ansmitter

bus to the Transmitter Holding Register or the Control Register as chosen by register select. A high-level voltage gates

data from the Receiver Holding Register or the Status Register, as chosen by register select, to the receiver bus.

CHIP SELECT 3 (CS3):

With high-level voltage at this input together with CS1 and

CS2 selects the UART.

PERIPHERAL STATUS INTERRUPT (PSI):

A high-to-low transition on this input line sets a bit in the

Status Register and causes an

EXTERNAL STATUS (ES):

RTS is set to a low-level voltage when data is

INTERRUPT (INT = low).

CS2 and CS3

A low-level voltage at this input sets a bit in the Status

Register.

5-47

CDP1854A, CDP1854AC

CLEAR TO SEND (CTS):

When this input from peripheral is high, transfer of a

character to the Transmitter Shift Register and shifting of

serial data out is inhibited.

TABLE 1. INTERRUPT SET AND RESET CONDITIONS

(NOTE 1)

SET (INT = LOW) RESET (INT = HIGH)

CAUSE CONDITION TIME

DA (Receipt of Data) Read of Data TPB Leading Edge

THRE (Note 2)

(Ability to Reload)

THRE • TSRE

(Transmitter Done)

PSI

(Negative Edge)

CTS

(Positive Edge when THRE • TSRE)

NOTES:

1. Interrupts will occur only after the IE bit in the Control Register (see Table 4) has been set.

2. THRE will cause an interrupt only after the TR bit in the Control Register (see Table 4) has been set.

TABLE 2. STATUS REGISTER BIT ASSIGNMENT

Read of Status or Write of Character TPB Leading Edge

Read of Status or Write of Character TPB Leading Edge

Read of Status TPB Trailing Edge

Read of Status TPB Leading Edge

TRANSMITTER CLOCK (TCLOCK):

Clock input with a frequency 16 times the desired transmitter

shift rate.

BIT 76543210

SIGNAL THRE TSRE PSI ES FE PE OE DA

ALSO AVAILABLE AT TERMINAL

† Polarity reversed at output terminal.

BIT SIGNAL: FUNCTION

0 DATA AVAILABLE (DA): When set high, this bit indicates that an entire character has been received and transferred to the Receiver

Holding Register. This signal is also available at Term. 19 but with its polarity reversed.

1 OVERRUN ERROR (OE): When set high, this bit indicates that the Data Available bit was not reset before the next character was

transferred to the Receiver Holding Register. This signal OR’ed with PE is output at Term. 15.

2 PARITY ERROR (PE): When set high, this bit indicates that the received parity bit does not compare to that programmed by the EVEN

PARITY ENABLE (EPE) control. This bit is updated each time a character is transferred to the Receiver Holding Register. This signal

OR’ed with OE is output at Term. 15.

3 FRAMlNG ERROR (FE): When set high, this bit indicates that the received character has no valid stop bit, i.e., the bit following the

parity bit (if programmed) is not a high-level voltage. This bit is updated each time a character is transferred to the Receiver Holding

Register. This signal is also available at Term. 14.

4 EXTERNAL STATUS (ES): This bit is set high by a low-level input at Term. 38 (ES).

5 PERIPHERAL STATUS INTERRUPT (PSI): This bit is set high by a high-to-low voltage transition of Term. 37 (PSI). The INTERRUPT

output (Term. 13) is also asserted (lNT = Iow) when this bit is set.

6 TRANSMlTTER SHIFT REGISTER EMPTY (TSRE): When set high, this bit indicates that the T ransmitter Shift Register has complet-

ed serial transmission of a full character including stop bit(s). It remains set until the start of transmission of the next character.

7 TRANSMlTTER HOLDING REGISTER EMPTY (THRE): When set high, this bit indicates that the Transmitter Holding Register has

transferred its contents to the Transmitter Shift Register and may be reloaded with a new character . Setting this bit also sets theTHRE

output (Term. 22) low and causes an INTERRUPT (lNT = low), if TR is high.

22† - - - 14 15 15 19†

5-48