Intersil Corporation CDP1852C Datasheet

CDP1852,

CDP1852C

March 1997

Features

• Static Silicon-Gate CMOS Circuitry

• Parallel 8-Bit Data Register and Buffer

• Handshaking Via Service Request Flip-Flop

• Low Quiescent and Operating Power

• Interfaces Directly with CDP1800-Series

Microprocessors

• Single Voltage Supply

o

• Full Military Temperature Range (-55

C to +125oC)

Ordering Information

PACKAGE TEMP. RANGE 5V 10V

PDIP -40oC to +85oC CDP1852CE CDP1852E E24.6

SBDIP -40oC to +85oC CDP1852CD CDP1852D D24.6

PKG.

NO.

Byte-Wide Input/Output Port

Description

The CDP1852 and CDP1852C are parallel, 8-bit, mode-programmable input/output ports. They are compatible and will

interface directly with CDP1800-series microprocessors. They

are also useful as 8-bit address latches when used with the

CDP1800 multiplexed address bus and as I/O ports in generalpurpose applications.

The mode control is used to program the device as an input port

(mode = 0) or as an output port (mode = 1). The

can be used as a signal to indicate when data is ready to be

transferred. In the input mode, a peripheral device can strobe

data into the CDP1852, and microprocessor can read that data

by device selection. In the output mode, a microprocessor

strobes data into the CDP1852, and handshaking is established

with a peripheral device when the CDP1852 is deselected.

In the input mode, data at the data-in terminals (DI0-DI7) is

strobed into the port’s 8-bit register by a high (1) level on the

clock line. The negative high-to-low transition of the clock

latches the data in the register and sets the service request output low (

(CS1/

SR/SR = 0). When CS1/CS1 and CS2 are high

CS1 and CS2 = 1), the three-state output drivers are

enabled and data in the 8-bit register appear at the data-out terminals (D00-D07). When either CS1/

CS1 or CS2 = 0), the data-out terminals are three-stated

(CS1/

CS1 or CS2 goes low

and the service request output returns high (

In the output mode, the output drivers are enabled at all times.

Data at the data-in terminals (DI0-DI7) is strobed into the 8-bit

register when CS1/

CS1 is low (CS1/CS1 = 0) and CS2 and the

clock are high (1), and are present at the data-out terminals

(D00-D07). The negative high-to-low transition of the clock

latches the data in the register. The

SR/SR = 1) when the device is deselected (CS1/CS1 = 1 or

(

CS2 = 0) and returns low (

SR/SR = 0) on the following trailing

SR/SR output goes high

edge of the clock.

SR/SR output

SR/SR =1).

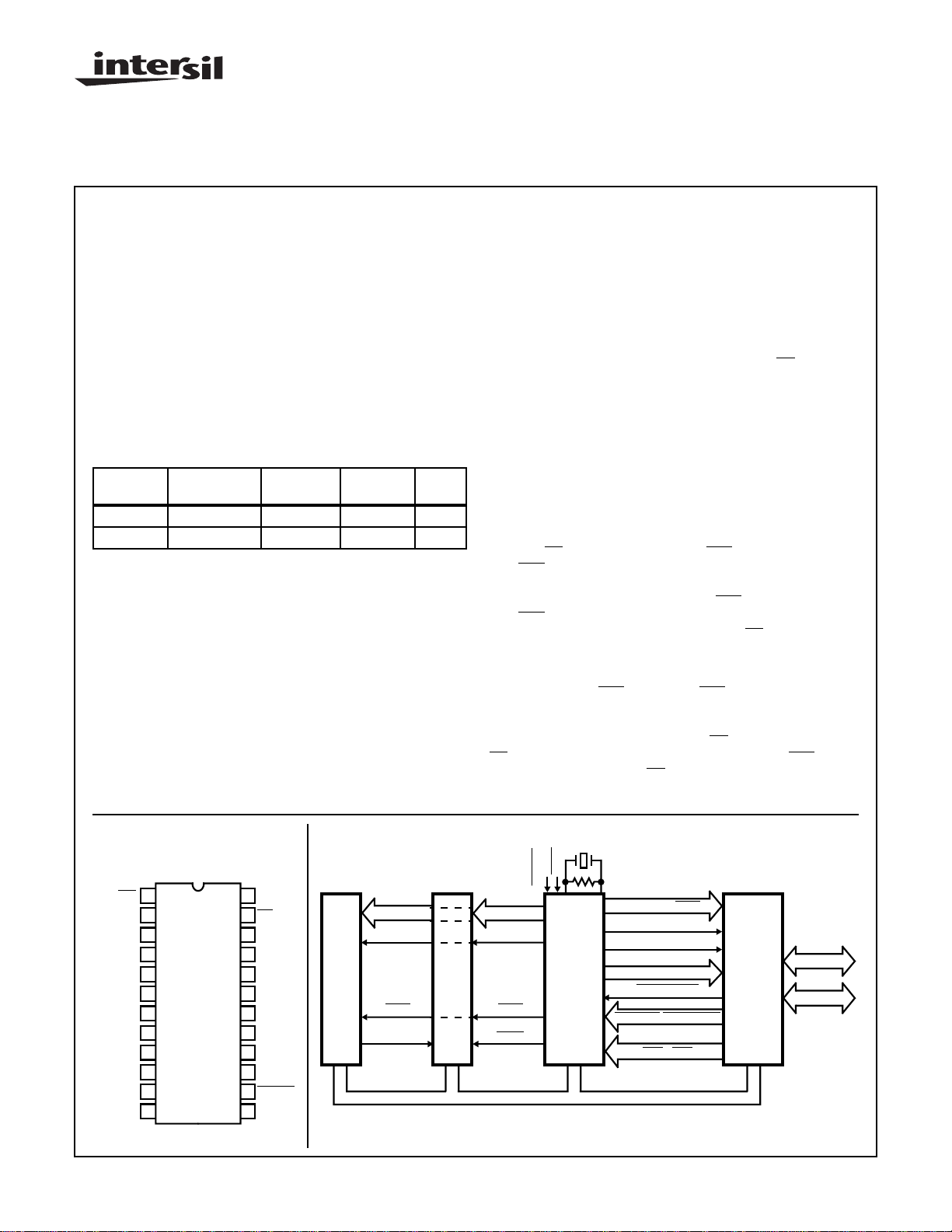

Pinout

24 LEAD DIP

TOP VIEW

1

CSI

CSI/

MODE

2

DI0

3

DO0

4

5

DI1

DO1

6

DI2

7

DO2

8

DI3

9

DO3

10

CLOCK

11

V

12

SS

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

24

23

22

21

20

19

18

17

16

15

14

13

V

DD

SR/SR

DI7

DO7

DI6

DO6

DI5

DO5

DI4

DO4

CLEAR

CS2

Typical CDP1802 Microprocessor System

WAIT

CLEAR

ADDR BUS

TPA

MRD

CEO

| Copyright © Intersil Corporation 1999

ADDR BUS

TPA

RAMROM

MRD

MWR

BIDIRECTIONAL DATA BUS

4-19

CPU

CDP1802

FIGURE 1.

N0 - N2

MRD

TPB

Q

SC0 SC1

INTERRUPT

DMA - IN DMA - OUT

EF1 - EF4

I/O

CDP1852

File Number

DAT A

CONTROL

1166.2

CDP1852, CDP1852C

Absolute Maximum Ratings Thermal Information

DC Supply-voltage Range, (VDD)

(Voltage Referenced to VSSTerminal)

CDP1852 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5 to +11V

CDP1852C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5 to +7V

Input Voltage Range, All Inputs . . . . . . . . . . . . . . -0.5 to VDD +0.5V

DC Input Current, Any One Input. . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Device Dissipation Per Output Transistor . . . . . . . . . . . . . . . 100mW

For TA = Full Package-Temperature Range

(All Package Type)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Thermal Resistance (Typical) θJA (oC/W) θJC (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . 65 N/A

SBDIP Package. . . . . . . . . . . . . . . . . . 65 20

Operating-Temperature Range (TA)

Package Type D, H . . . . . . . . . . . . . . . . . . . . . . .-55oC to +125oC

Package Type E. . . . . . . . . . . . . . . . . . . . . . . . . . .-40oC to +85oC

Storage Temperature Range (T

) . . . . . . . . . . . .-65oC to +150oC

STG

Lead Temperature (During Soldering): . . . . . . . . . . . . . . . . . +265oC

At Distance 1/16 ± 1/32 inch (1.59 ± 0.79mm)

from Case for 10s max

Operating Conditions At T

= Full Package Temperature Range. For Maximum Reliability, Operating Conditions Should be

A

Selected so that Operation is Always within the Following Ranges:

LIMITS

CDP1852 CDP1852C

PARAMETER

MIN MAX MIN MAX

DC Operating Voltage Range 4 10.5 4 6.5 V

Input Voltage Range V

SS

V

DD

V

SS

V

DD

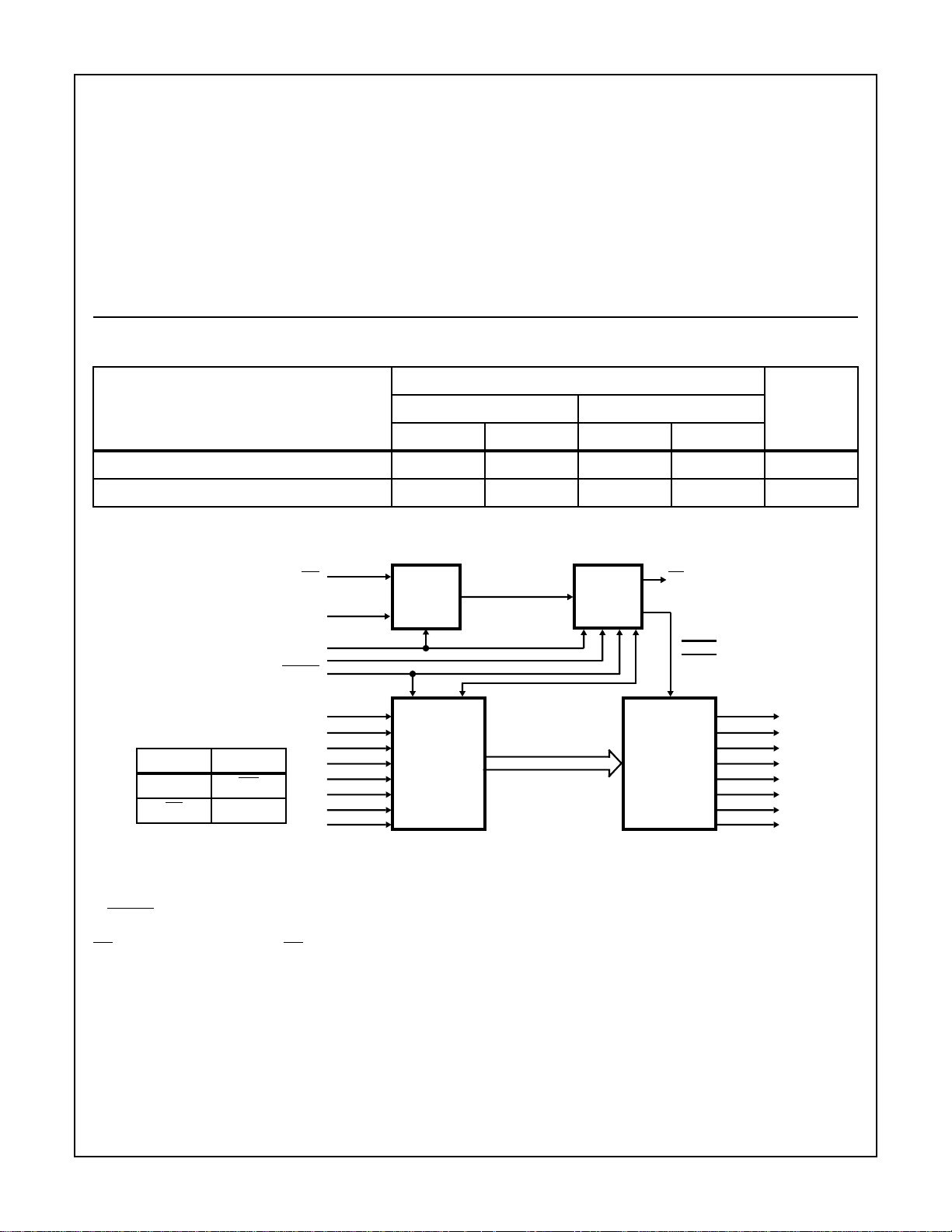

Functional Diagram

MODE 0 MODE 1

P1 CSI CSI

P23 SR SR

CSI/

CSI

(NOTE 1)

CS2

MODE

CLOCK

CLEAR

DI0

DI1

DI2

DI3

DI4

DI5

DI6

DI7

13

11

14

16

18

20

22

1

2

3

5

7

9

DEVICE

SELECT

DECODE

RESET

8-BIT

DAT A

REGISTER

CONTROL

LOGIC

CLOCK

23

SR/SR

(NOTE 1)

24

12

ENABLE

THREE-

STATE

OUTPUT

DRIVERS

V

DD

V

SS

4

DO0

6

DO1

8

DO2

10

DO3

15

DO4

17

DO5

19

DO6

21

DO7

UNITS

V

NOTE:

1. Polarity depends on mode.

FIGURE 2. FUNCTIONAL BLOCK DIAGRAM FOR CDP1852

A CLEAR control is provided for resetting the port’s register

(DO0-DO7 = 0) and service request flip-flop (input mode:

SR/ SR = 1 and output mode: SR/SR = 0).

The CDP1852 is functionally identical to the CDP1852C.

The CDP1852 has a recommended operating voltage range

of 4 to 10.5 volts, and the CDP1852C has a recommended

operating voltage range of 4 to 6.5 volts.

The CDP1852 and CDP1852C are supplied in 24-lead,

hermetic, dual-in-line ceramic packages (D suffix), in 24-lead

dual-in-line plastic packages (E suffix). The CDP1852C is

also available in chip form (H suffix).

4-20

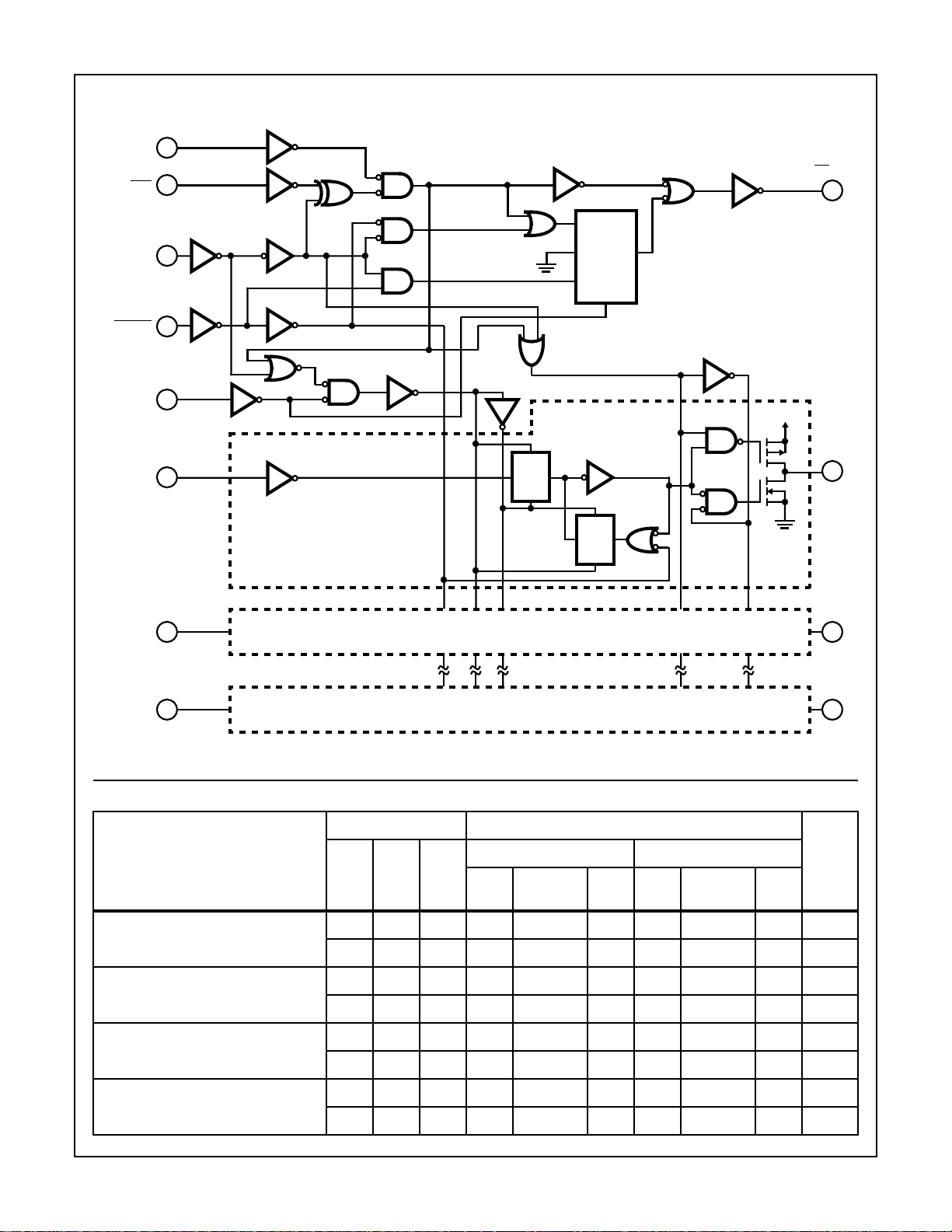

Logic Diagram

13

CS2

MODE

1

2

14

CS1/CS1

CLEAR

CDP1852, CDP1852C

V

SS

SR/SR

23

S

D

Q

R

CL

SERVICE

REQUEST

LATCH

DI0

DI1

DI7

11

3

5

22

CLOCK

Static Electrical Specifications At T

p

TG

n

p

TG

n

FIGURE 3. CDP1852 LOGIC DIAGRAM

= -40oC to +85oC, Unless Otherwise Specified

A

CONDITIONS LIMITS

V

DD

p

DO0

4

n

V

SS

DO1

6

DO7

21

PARAMETER

Quiescent Device Current I

Output Low Drive

(Sink) Current

Output High Drive

(Source) Current

Output Voltage Low-Level

(Note 2)

CDP1852 CDP1852C

V

V

DD

(V)

V

IN

DD

(V)

MIN

O

(V)

- 0, 5 5 - - 10 - - 50 µA

(NOTE1)

TYP MAX MIN

(NOTE1)

TYP MAX

UNITS

- 0, 10 10 - - 100 - - - µA

I

0.4 0, 5 5 1.6 3.2 - 1.6 3.2 - mA

OL

0.5 0, 10 10 3 6 - - - - mA

I

4.6 0, 5 5 -1.15 -2.3 - -1.15 -2.3 - mA

OH

9.5 0, 10 10 -3 -6 - - - - mA

V

OL

- 0, 5 5 - 0 0.1 - 0 0.1 V

- 0, 10 10 - 0 0.1 - - - V

4-21

Loading...

Loading...