March 1997

TM

CDP1805AC,

CDP1806AC

CMOS 8-Bit Microprocessor with On-Chip RAM†

and Counter/Timer

Features

• Instruction Time of 3.2µs, -40oC to +85oC

• 123 Instructions - Upwards Software Compatible With

CDP1802

• BCD Arithmetic Instructions

• Low-Power IDLE Mode

• Pin Compatible With CDP1802 Except for Terminal 16

• 64K-Byte Memory Address Capability

• 64 Bytes of On-Chip RAM

• 16 x 16 Matrix of On-Board Registers

• On-Chip Crystal or RC Controlled Oscillator

• 8-Bit Counter/Timer

n

†

Description

The CDP1805AC and CDP1806AC are functional and performance enhancements of the CDP1802 CMOS 8-bit register-oriented microprocessor series and are designed for use

in general-purpose applications.

The CDP1805AC hardware enhancements include a 64byte RAM and an 8-bit presettable down counter. The

Counter/Timer which generates an internal interrupt request,

can be programmed for use in timebase, event-counting,

and pulse-duration measurement applications. The

Counter/Timer underflow output can also be directed to the

Q output terminal. The CDP1806AC hardware enhancements are identical to the CDP1805AC, except the

CDP1806AC contains no on-chip RAM.

The CDP1805AC and CDP1806AC software enhancements

include 32 more instructions than the CDP1802. The 32 new

software instructions add subroutine call and return capability , enh anced data transfe r manip ulatio n, Coun ter/Timer control, improved interrupt handling, single-instruction loop

counting, and BCD arithmetic.

Upwards software and hardware compatibility is maintained

when substituting a CDP1805AC or CDP1806AC for other

CDP1800-series microprocessors. Pinout is identical except

for the replacement of V

the replacement of V

with ME on the CDP1805AC and

CC

with VDD on the CDP1806AC.

CC

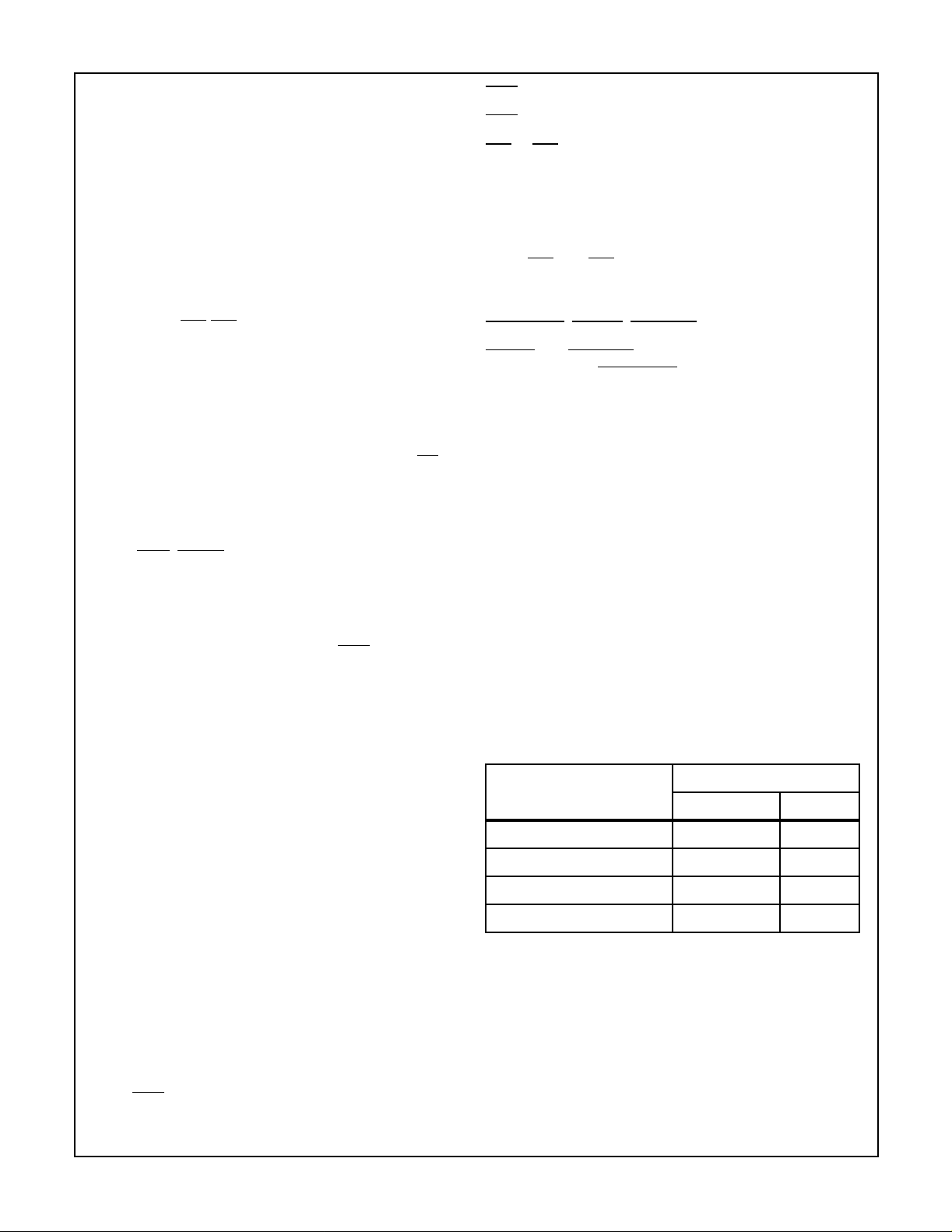

Ordering Information

CDP1805AC CDP1806AC TEMPERATURE RANGE PACKAGE PKG. NO.

o

CDP1805ACE CDP1806ACE -40

- CDP1806ACEX Burn-In

CDP1805ACQ CDP1806ACQ -40

CDP1805ACD CDP1806ACD -40

CDP1805ACDX - Burn-In

† CDP1805AC Only

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

Copyright © Intersil Americas Inc. 2002. All Rights Reserved

| Intersil (and design) is a trademark of Intersil Americas Inc.

C to +85oC Plastic DIP E40.6

o

C to +85oC PLCC N44.65

o

C to +85oC SBDIP D40.6

1

File Number 1370.2

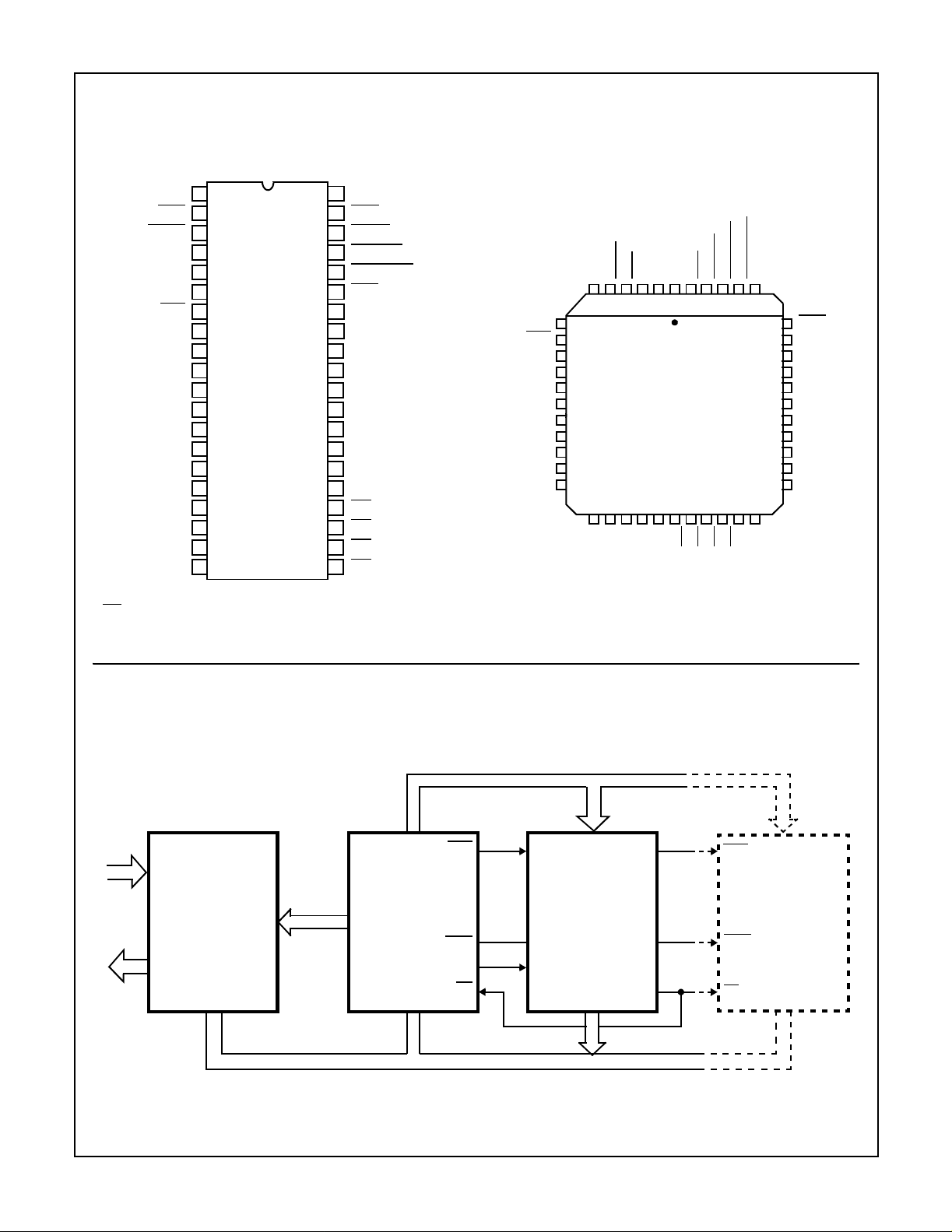

Pinouts

CDP1805AC, CDP1806AC

(PDIP, SBDIP)

TOP VIEW

CDP1805AC, CDP1806AC

CDP1805AC, CDP1806AC

(PLCC, PACKAGE TYPE Q)

TOP VIEW

† ME

for CDP1805AC

for CDP1806AC

V

DD

CLOCK

WAIT

CLEAR

SC1

SC0

MRD

BUS 7

BUS 6

BUS 5

BUS 4

BUS 3

BUS 2

BUS 1

BUS 0

N2

N1

N0

V

SS

1

2

3

4

Q

5

6

7

8

9

10

11

12

13

14

15

†

16

17

18

19

20

V

40

XTAL

39

38

DMA IN

37

DMA OUT

36

INTERRUPT

35

MWR

TPA

34

TPB

33

MA7

32

MA6

31

MA5

30

MA4

29

MA3

28

MA2

27

MA1

26

MA0

25

EF1

24

23

EF2

22

EF3

21

EF4

DD

SC0

MRD

BUS 7

BUS 6

BUS 5

NC

BUS 4

BUS 3

BUS 2

BUS 1

BUS 0

7

8

9

10

11

12

13

14

15

16

17

SC1QCLEAR

20 21 22 23 24 25 261918

†

N2N1N0

WAIT

CLOCKNCVDDXTAL

123456

SS

NC

V

DMA - IN

DMA - OUT

44 43 42 41 40

EF3

EF2

EF4

EF1

INTERRUPT

39

38

37

36

35

34

33

32

31

30

29

2827

MA0

MWR

TPA

TPB

MA7

MA6

NC

MA5

MA4

MA3

MA2

MA1

Schematic

IN

OUT

CDP1851

PIO

BUS0 - BUS7

FIGURE 1. TYPICAL CDP1805AC, CDP1806AC SMALL MICROPROCESSOR SYSTEM

CONTROL

MA0 - MA7

CDP1805AC WITH

RAM, COUNTER/TIMER

CDP1806AC WITH

COUNTER/TIMER

BUS0 - BUS7

MRD

MWR

TPA

ME

TPA

(CDP1805AC ONLY)

8-BIT DATA BUS

ADDRESS BUS

MA0 - MA7

CDP1833

1K BYTE ROM

BUS0 - BUS7

CEO

MA0-MA4

MRD

CDP1824

32 BYTE RAM

(USED WITH

CDP1806AC ONLY)

MWR

CS

BUS0-BUS4

2

CLOCK

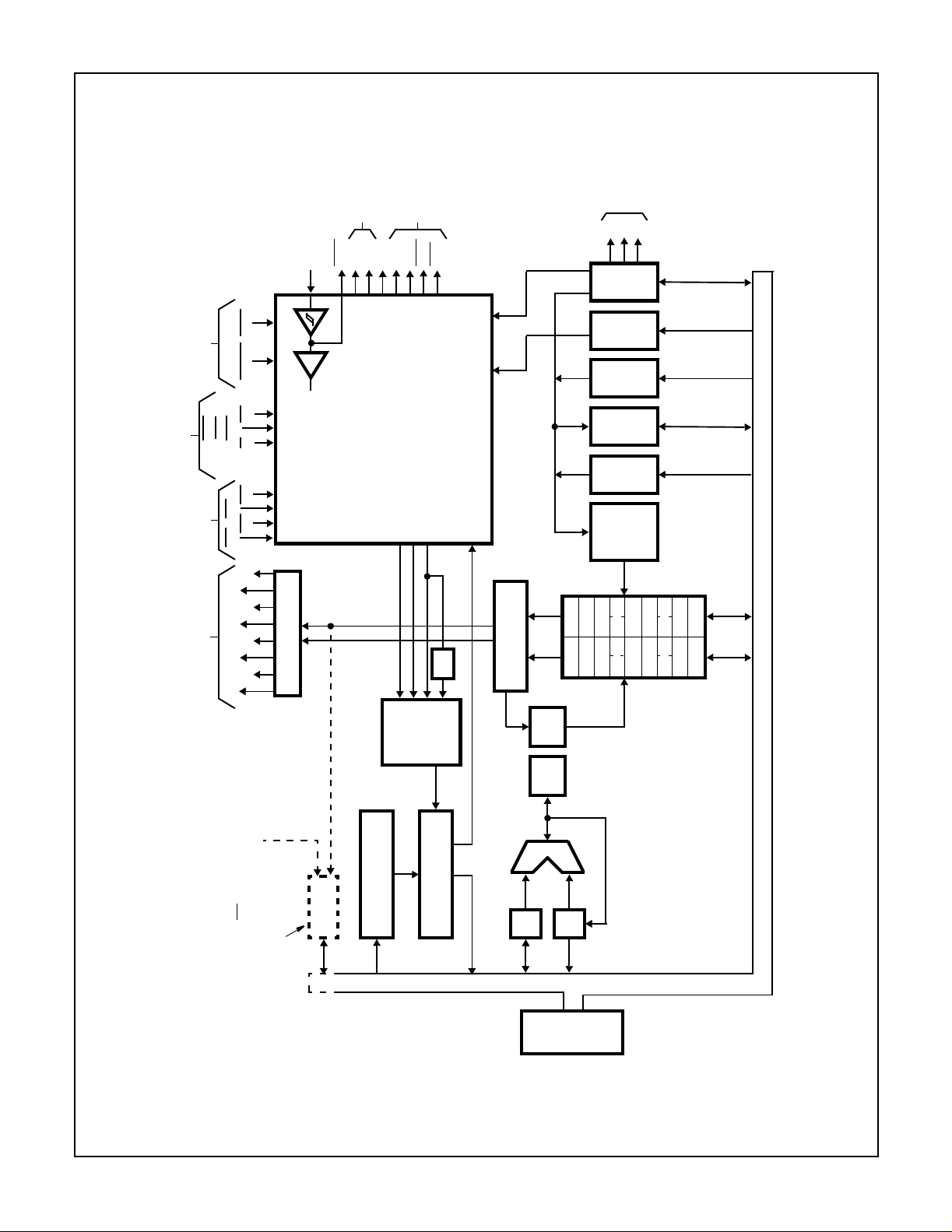

CDP1805AC, CDP1806AC

STATE

CODES

SYSTEM

TIMING

XTAL

SCO

SCI

Q LOGIC

TPA

TPB

MWR

MRD

I/O

COMMANDS

N0N1N2

N

(4)

WAIT

CONTROL

CLEAR

INTIN

OUT

DMA

DMA

I/O REQUESTS

EF4

EF3

EF2

I/O FLAGS

EF1

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MEMORY ADDRESS LINES

LOGIC

CLOCK

TIMING LOGIC

CONTROL AND

EF1

MUX

TC

DECODE

INSTRUCTION

INTERRUPT

EF2

TPA

LOGIC

ARRAY

REGISTER

A

(16)

÷ 32

INCR/

DF

DECR

(1)

MODE

CONTROL

CLK

I

(4)

P

(4)

T

(8)

X

(4)

AND

LATCH

R(2).0

R(2).1

DECODE

R(9).0

R(A).0

R(9).1

R(A).1

R(F).0

R(E).0

R(F).1

R(E).1

8-BIT BIDIRECTIONAL DATA BUS

R

R(0).0

R(1).0

R(0).1

R(1).1

ALU

8-BIT

COUNTER/TIMER

B

D

(8)

(8)

BUS 0

BUS 1

BUS 2

BUS 3

BUS 4

ME FOR CDP1805AC

FOR CDP1806AC

DD

V

CDP1805AC

RAM

64-BYTE

ONLY

REGISTER (CH)

COUNTER HOLDING

FIGURE 2. BLOCK DIAGRAM FOR CDP1805AC AND CDP1806AC

3

BUS 5

BUS 6

BUS 7

CDP1805AC, CDP1806AC

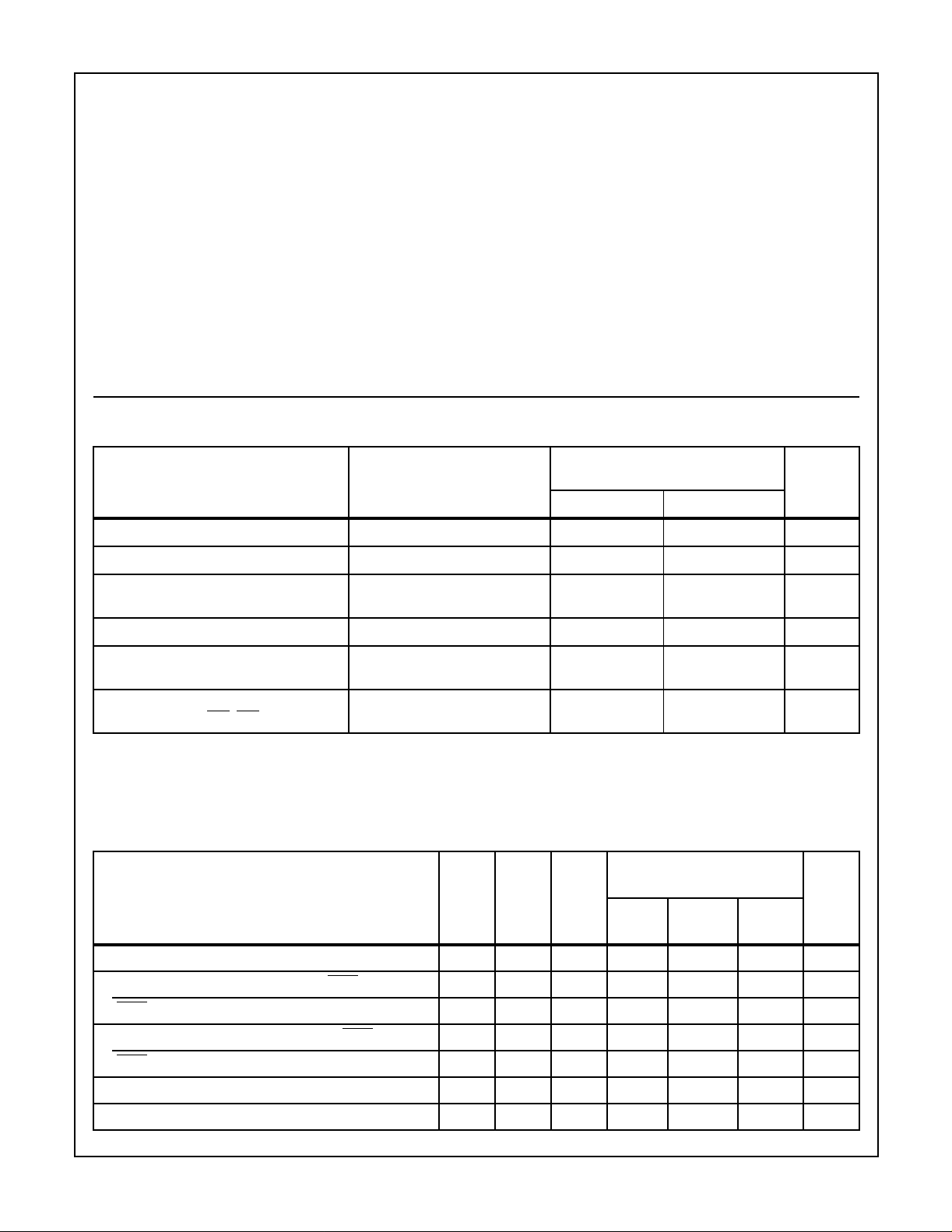

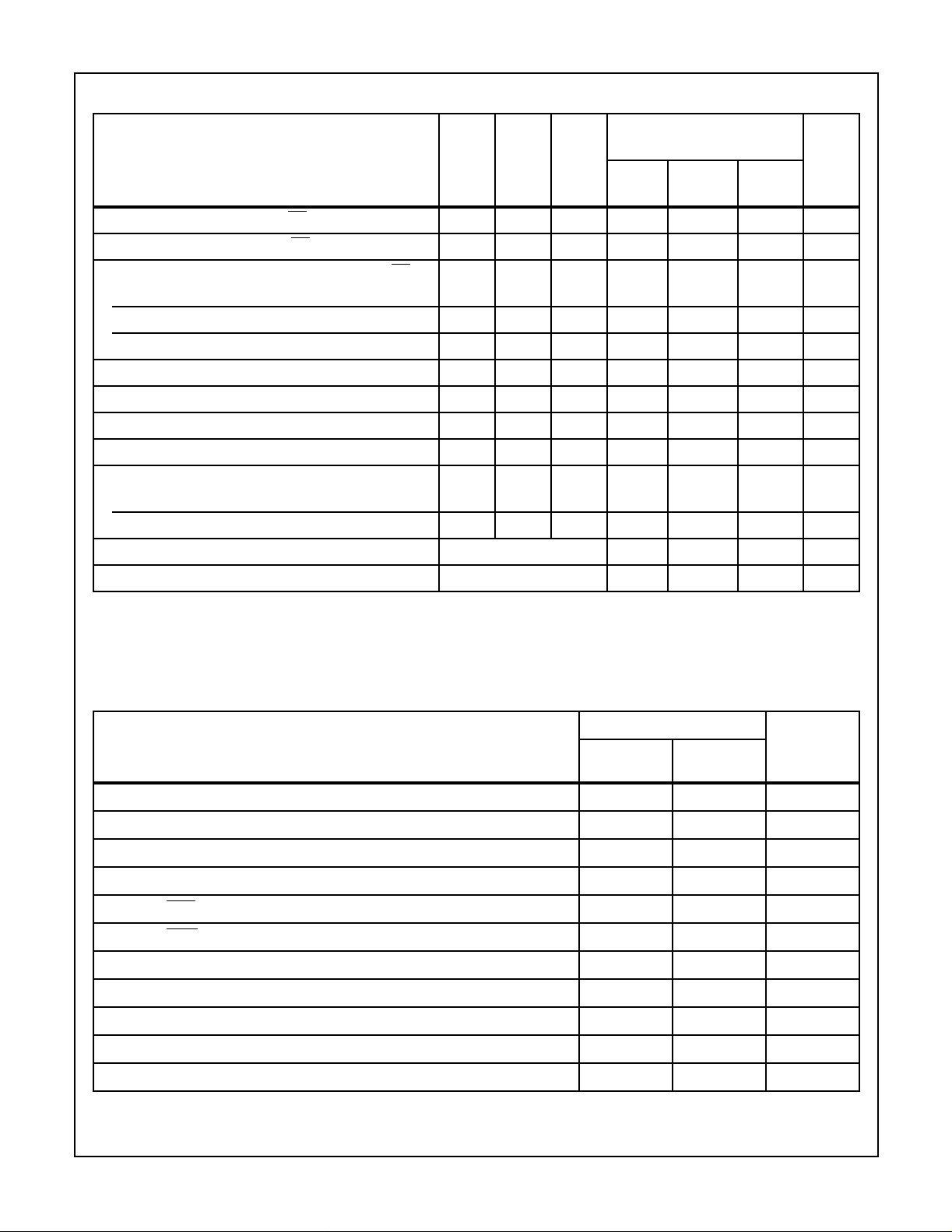

Absolute Maximum Ratings Thermal Information

DC Supply Voltage Range, (VDD)

(All Voltages Referenced to V

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to V

DC Input Current, any One Input. . . . . . . . . . . . . . . . . . . . . . . . .± 10mA

Terminal). . . . . . . . . -0.5V to +7V

SS

DD

+0.5V

Thermal Resistance (Typical, Note 2) θ

PDIP Package. . . . . . . . . . . . . . . . . . . 50 N/A

PLCC Package . . . . . . . . . . . . . . . . . . 46 N/A

SBDIP Package. . . . . . . . . . . . . . . . . . 55 15

Device Dissipation Per Output Transistor

= Full Package Temperature Range . . . . . . . . . . . . . . 100mW

T

A

Operating Temperature Range (T

Package Type D . . . . . . . . . . . . . . . . . . . . . . . . .-55

)

A

Package Type E and Q . . . . . . . . . . . . . . . . . . . . .-40

Storage Temperature Range (T

Lead Temperature (During Soldering)

). . . . . . . . . . . .-65oC to +150oC

STG

At Distance 1/16 ±1/32in (1.59 ± 0.79mm) from case for

10s Max. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+265

Printed Circuit Board Mount: 57mm x 57mm Minimum Area x 1.6mm

Thick G10 Epoxy Glass, or Equivalent.

CAUTION: Stresses above t hos e l iste d in “Absolute Maxi mum Ra ti ng s” m ay cau se per ma nent damage to the d evice . T his is a stress only rating and operati on

of the device at these or any other conditions above those in dica ted in the operational sections of this specification is not implied.

(oC/W) θJC (oC/W)

JA

o

C to +125oC

o

C to +85oC

o

C

Recommended Operating Conditions T

= Full-Package Temperature Range. For maximum reliability, operating conditions

A

should be selected so that operation is always within the following ranges.

CDP1805ACD, CDP1805ACE

PARAMETER

TEST CONDITIONS

V

DD

(V)

CDP1806ACD, CDP1806ACE

UNITSMIN MAX

DC Operating Voltage Range - 4 6.5 V

Input Voltage Range - V

Minimum Instruction Time (Note 1)

(f

= 5MHz)

CL

53.2-µs

SS

V

DD

V

Maximum DMA Transfer Rate 5 - 0.625 Mbyte/s

Maximum Clock Input Frequency,

Load Capacitance (C

) = 50pF

L

Maximum External Counter/Timer Clock

Input Frequency to EF1

, EF2

5DC5MHz

5DC2MHz

NOTES:

1. Equals 2 machine cycles - one Fetch and one Execute operation for all instructions except Long Branch, Long Skip, NOP, and “68” family

instructions, which are more than two cycles.

is measured with the component mounted on an evaluation PC board in free air.

2. θ

JA

Static Electrical Specifications at T

= -40oC to +85oC, VDD ±5%, Except as Noted

A

CDP1805ACD, CDP1805ACE

CDP1806ACD, CDP1806ACE

PARAMETER

Quiescent Device Current, I

Output Low Drive (Sink) Current, (Except XTAL

Output, I

XTAL

OL

DD

), I

Output High Drive (Source) Current (Except XTAL

XTAL

, I

OH

Output Voltage Low Level, V

Output Voltage High Level, V

OL

OH

OL

, I

OH

V

(V)

V

O

(V)

V

IN

DD

(V)

(NOTE 3)

TYP MAX

UNITSMIN

- 0, 5 5 - 50 200 µA

0.4 0, 5 5 1.6 4 - mA

0.4 5 5 0.2 0.4 - mA

4.6 0, 5 5 -1.6 -4 - mA

4.6 0 5 -0.1 -0.2 - mA

-0, 55 - 0 0.1 V

-0, 554.9 5 - V

4

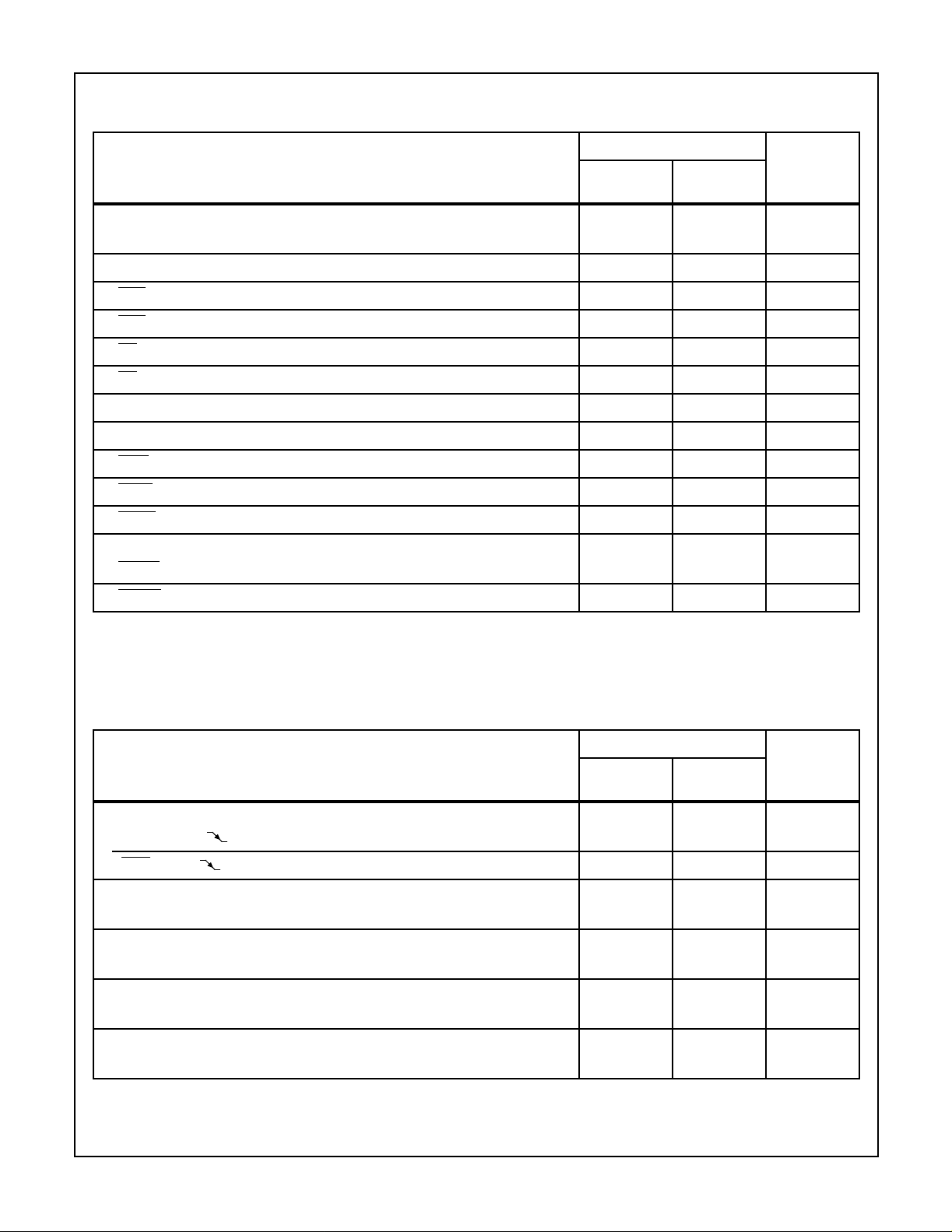

CDP1805AC, CDP1806AC

Static Electrical Specifications at T

= -40oC to +85oC, VDD ±5%, Except as Noted (Continued)

A

CDP1805ACD, CDP1805ACE

CDP1806ACD, CDP1806ACE

PARAMETER

Input Low Voltage (BUS0 - BUS7, ME), V

Input High Voltage (BUS0 - BUS7, ME

), V

IL

IH

Schmitt Trigger Input Voltage (Except BUS0 - BUS7, ME

Positive Trigger Threshold, V

Negative Trigger Threshold, V

Hysteresis, V

H

Input Leakage Current, I

Three-State Output Leakage Current, I

Input Capacitance, C

Output Capacitance, C

IN

OUT

P

N

IN

OUT

V

(V)

0.5, 4.5 - 5 - - 1.5 V

0.5, 4.5 - 5 3.5 - - V

)

0.5, 4.5 - 5 2.2 2.9 3.6 V

0.5, 4.5 - 5 0.9 1.9 2.8 V

0.5, 4.5 - 5 0.3 0.9 1.6 V

-0, 55 - ±0.1 ±5 µA

0, 5 0, 5 5 - ±0. 2 ±5 µA

---- 5 7.5pF

---- 10 15pF

V

O

(V)

V

IN

DD

(V)

(NOTE 3)

TYP MAX

Total Power Dissipation (Note 4)

Run - - 5 - 35 50 mW

Idle “00” at M (0000) - - 5 - 12 18 mW

UNITSMIN

Minimum Data Retention Voltage, V

Data Retention Current, I

DR

DR

NOTES:

3. Typical values are for T

4. External clock: f = 5MHz, t

= +25oC and nominal VDD.

A

, tF = 10ns; CL = 50pF.

R

Dynamic Electrical Specifications at T

V

PARAMETER

Propagation Delay Times

Clock to TPA, TPB, t

Clock-to-Memory High-Address Byte, t

Clock-to-Memory Low-Address Byte, t

Clock to MRD

Clock to MWR

, t

PLH

, t

PLH

Clock to (CPU DATA to BUS), t

Clock to State Code, t

Clock to Q, t

Clock to N, t

PLH

PLH

, t

, t

Clock to Internal RAM Data to BUS, t

, t

PLH

PHL

, t

PLH

PHL

, t

PLH

PHL

, t

PHL

, t

(See Note 5) 150 275 ns

PHL

, t

PLH

PHL

, t

PLH

PHL

PHL

PHL

, t

PLH

PHL

VDD = V

DR

-22.4V

VDD = 2.4 - 25 100 µA

= -40o to +85oC; CL = 50pF; Input tR, tF = 10ns; Input Pulse Levels = 0.1V to

A

-0.1V; VDD = 5V, ±5%.

DD

CDP1805AC CDP1806AC

(NOTE 5)

TYP MAX

150 275 ns

325 550 ns

275 450 ns

200 325 ns

375 625 ns

225 400 ns

250 425 ns

250 425 ns

420 650 ns

UNITS

5

CDP1805AC, CDP1806AC

Dynamic Electrical Specifications at T

= -40o to +85oC; CL = 50pF; Input tR, tF = 10ns; Input Pulse Levels = 0.1V to

A

-0.1V; VDD = 5V, ±5%. (Continued)

V

DD

PARAMETER

Minimum Set-Up And Hold Times (Note 2)

Data Bus Input Set-Up, t

Data Bus Input Hold, t

DMA

DMA

ME

Set-Up, t

ME

Hold, t

Set-Up, t

Hold, t

SU

H

SU

H

Interrupt Set-Up, t

Interrupt Hold, t

WAIT

Set-Up, t

EF1-4

Set-Up, t

EF1 -4

Hold, t

H

SU

SU

H

SU

H

SU

Minimum Pulse Width Times (Note 6)

CLEAR

CLOCK

Pulse Width, t

Pulse Width, t

WL

W

NOTES:

5. Typical values are for T

= 25o C and nominal V

A

DD

.

6. Maximum limits of minimum characteristics are the values above which all devices function.

CDP1805AC CDP1806AC

(NOTE 5)

TYP MAX

UNITS

-100 0 ns

125 225 ns

-75 0 ns

100 175 ns

125 320 ns

050ns

-100 0 ns

100 175 ns

20 50 ns

-125 0 ns

175 300 ns

100 175 ns

75 100 ns

Timing Specifications as a function of T (T =

1

/f

) at TA = -40 to +85oC, VDD = 5V, ±15%

CLOCK

CDP1805AC, CDP1806AC

(NOTE 7)

PARAMETER

MAX

High-Order Memory-Address Byte

Set-Up to TPA Time, t

MRD

to TPA Time, t

SU

SU

2T-275 2T -175 ns

T/2 -100 T/2 -75 ns

High-Order Memory-Address Byte

Hold after TPA Time, t

H

T/2 +75 T/2 +100 ns

Low-Order Memory-Address Byte

Hold after WR Time, t

H

T +180 T +240 ns

CPU Data to Bus

Hold after WR Ti me, t

H

Required Memory Access Time, t

ACC

T +110 T +150 ns

Address to Data 4.5T -440 4.5T -330 ns

NOTE:

7. Typical values are for T

= +25oC and nominal VDD.

A

UNITSTYP

6

CDP1805AC, CDP1806AC

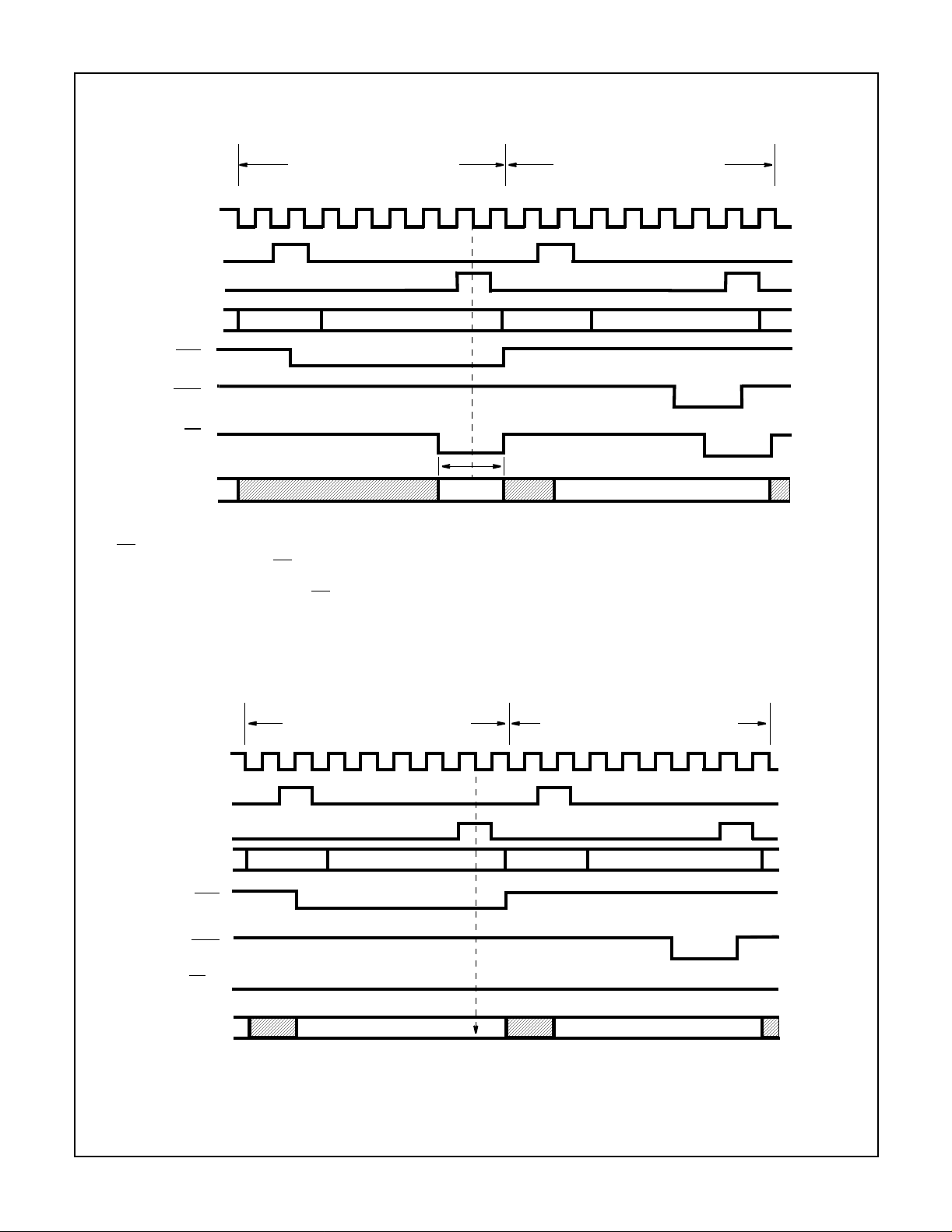

Timing Waveforms For Possible Operating Modes

INTERNAL RAM READ CYCLE INTERNAL RAM WRITE CYCLE

00 10 20 30 40 50 60 70 00 10 20 30 40 50 60 70

CLOCK

01 11 21 31 41 51 61 71 01 11 21 31 41 51 61 71

TPA

TPB

MEMORY

ADDRESS

MRD

MWR

†ME

DATA

BUS

IN

HIGH BYTE LOW BYTE HIGH BYTE LOW BYTE

VALID DATA FROM MEMORY

VALID DATA FROM CPU

NOTE:

has a minimum setup and hold time with respect to the beginning of clock 70. For a memory read operation, RAM data will appear on

8. ME

the data bus during the time ME

is active after clock 31. The time shown can be longer, if for instance, a DMA out operation is performed

on internal RAM data, to allow data enough time to be latched into an external device. The internal RAM is automatically deselected at

the end of clock 71 independent of ME

.

† For CDP1805AC only.

FIGURE 3. INTERNAL MEMORY OPERATION TIMING WAVEFORMS

EXTERNAL MEMORY READ CYCLE EXTERNAL MEMORY WRITE CYCLE

00 10 20 30 40 50 60 70 00 10 20 30 40 50 60 70

CLOCK

TPA

01 11 21 31 41 51 61 71 01 11 21 31 41 51 61 71

TPB

MEMORY

ADDRESS

MRD

MWR

†ME IN

(HIGH)

DATA

BUS

NOTE:

† For CDP1805AC only.

HIGH BYTE LOW BYTE LOW BYTEHIGH BYTE

DATA LATCHED IN CPU VALID DATA FROM CPU

FIGURE 4. EXTERNAL MEMORY OPERATION TIMING W AVEFORMS

7

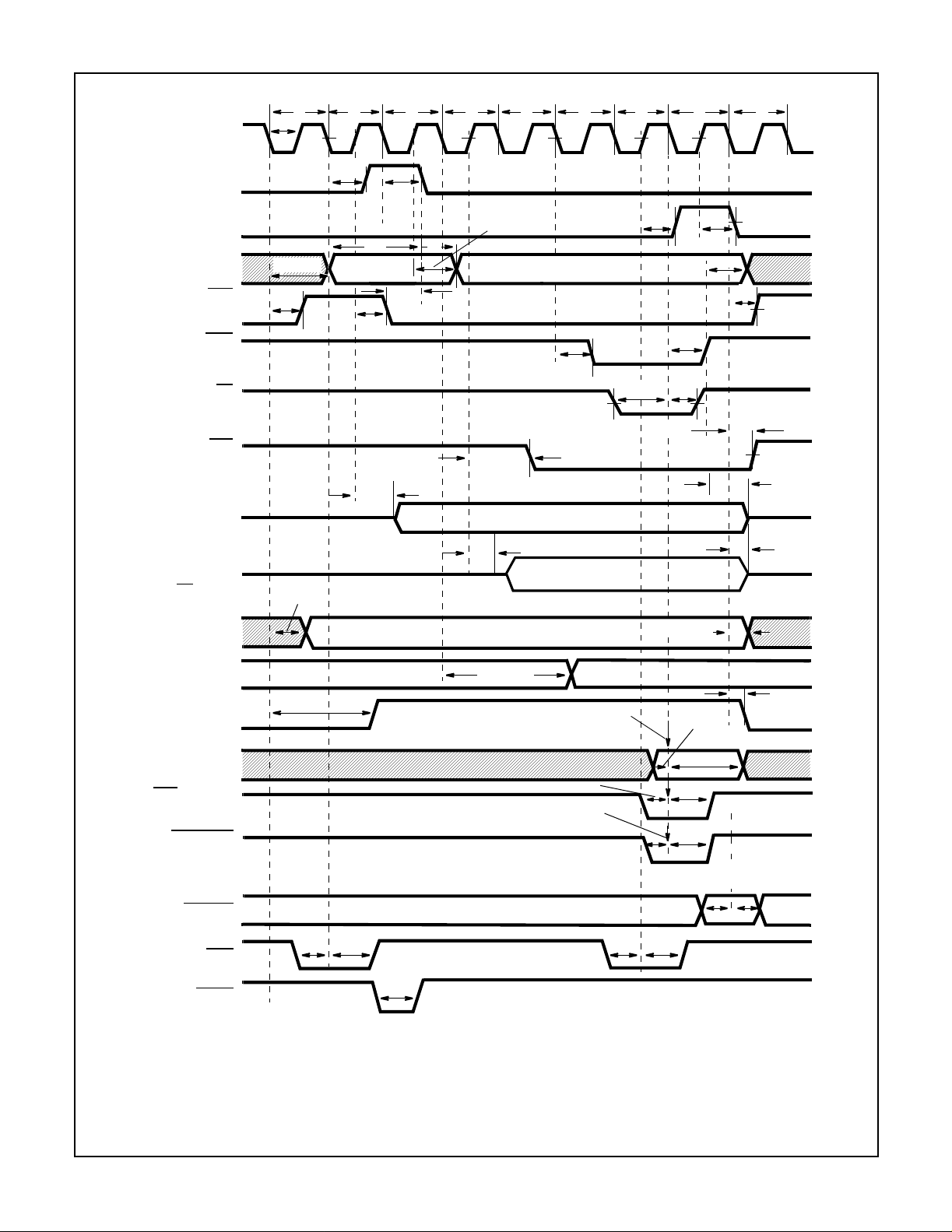

CDP1805AC, CDP1806AC

CLOCK

TPA

TPB

MEMORY

ADDRESS

MRD

(MEMORY

READ CYCLE)

MWR

(MEMORY

WRITE CYCLE)

† ME

(MEMORY

ENABLE)

†† EMS

(EXTERNAL

MEMORY

SELECT)

DATA FROM

CPU TO BUS

DATA FROM

INTERNAL MEMORY

TO BUS (ME

= LOW)

t

W

1 2 3 4 5 6 7 0

00 01 10 11 20 21 30 31 40 41 50 51 60 61 70071 00 01

t

PLH, tPHL

t

PLH

t

PLH,

t

PHL

t

PLH

HIGH ORDER

ADDRESS BYTE

t

PLH,

t

t

SU

PHL

t

t

PHL

t

SU

PHL

t

t

PLH, tPHL

t

H

LOW ORDER

ADDRESS BYTE

t

IS ALLOWABLE

SU

INTERNAL RAM

ACCESS TIME

t

PLH

t

PHL

t

PHL

t

PHL

PLH

t

SU

t

PLH

t

PLH

t

t

PHL

t

H

t

PHL

H

t

H

t

PLH, tPLH

t

SUtH

t

PLH, tPHL

t

SU

t

H

t

t

SU

H

t

t

SU

H

SAMPLED END OF S0

FLAG LINES

t

SUtH

STATE CODES

N0, N1, N2

(I/O EXECUTION

CYCLE)

DATA FROM

BUS TO CPU

DMA REQUEST

INTERRUPT

REQUEST

EF1 - EF4

Q

t

PLH

t

PLH, tPHL

DATA LATCHED

IN CPU

DMA SAMPLED (S1, S2, S3)

INTERRUPT

SAMPLED (S1, S2)

t

SUtH

WAIT

t

CLEAR

WL

NOTES:

† This Timing Diagram is used to show signal relationships only, and does not represent any specific machine cycle.

† All measurements are referenced to 50% point of the wave forms.

† Shaded areas indicate “don’t care” or undefined state. Multiple transitions may occur during this period.

† For the run (RAM only) mode only.

†† For the run (RAM/ROM) mode only.

FIGURE 5. TIMING WAVEFORMS

t

PHL

8

CDP1805AC, CDP1806AC

Enhanced CDP1805AC and CDP1806AC

Operation

MRD

= VDD: Input data from I/O to CPU and memory.

MRD

= VSS: Output data from Memory to I/O.

Timing

Timing for th e CDP1 805 AC and C DP 18 06AC is the sa me as

the CDP1802 microprocessor series, with the following

exceptions:

• 4.5 Clock Cycles Are Provided for Mem ory Access Instea d

of 5.

• Q Changes 1/2 Clock Cycle Earlier During the SEQ and

REQ Instructions.

• Flag Lines (EF1

-EF4) Are Sampled at the End of the S0

Cycle Instead of at the Beginning of the S1 Cycle.

• Pause Can Only Occur on the Low-To-High Transition of

Either TPA or TPB, Instead of any Negative Clock Transition.

Special Features

Schmitt triggers are provided on all inputs, except ME

and

BUS 0-BUS 7, for maximum immunity from noise and slow

signal transitions. A Schmitt Trigger in the oscillator section

allows ope ration with an RC or crystal.

The CDP1802 Series LOAD mode is not retained. This

mode (WAIT

, CLEAR = 0) is not allowed on the CD P180 5AC

and CDP1806AC.

A low power mode is provided, whic h is initi ated via the ID LE

instruction. In th is m ode all external sig na ls, except the osci llator, are stopped on the low-to-high transition of TPB. All

outputs remain in their previous states, MRD

is set to a logic

“1”, and the data bus floats. The IDLE mode is exited by a

DMA or INT condition. The INT includes both external interrupts and interrupts generated by the Counter/Timer. The

only restrictions are that the Timer mode, which uses the

TPA ÷ 32 clock source, and the underflow condition of the

Pulse Width Measurement modes are not available to exit

the IDLE mode.

EF1

to EF4 (4 Flags)

These inputs enable the I/O controllers to transfer status

information to the processor. The levels can be tested by the

conditional branch instructions. They can be used in conjunction with the INTERRUPT request line to establish interrupt priorities. The flag(s) are sampled a t the end of every S0

cycle. EF1 and EF2 are also used for event counting and

pulse width measurement in conjunction with the

Counter/Timer.

INTERRUPT

DMA-lN

S2, and S3 cycle. INTERRUPT

, DMA-IN, DMA-OUT (3 I/O Requests)

and DMA-OUT are sampled duri ng TPB every S1 ,

is sampled during TPB e ver y

S1 and S2 cycle.

Interrupt Action - X and P are stored in T after executing

current instruction; designator X is set to 2; designator P is

set to 1; interrupt enable (MIE) is reset to 0 (inhibit); and

instruction execution is resumed. The interrupt action

requires one machine cycle (S3).

DMA Action - Finish executing current instruction; R(0)

points to memory area for data transfer; data is loaded into

or read out of memory; and R(0) is incremented.

NOTE: In the event of concurrent DMA and INTERRUPT requests,

DMA-IN has priority followed by DMA-OUT and then INTERRUPT.

(The interrupt request is not internally latched and must be held true

after DMA).

SC0, SC1, (2 State Code Lines)

These outputs indicate that the CPU is: 1) fetching an

instructio n, o r 2 ) e x ec uti ng a n i ns tr uc t ion, or 3) pr oce s si ng a

DMA request, or 4) acknowledging an interrupt request. The

levels of state code are tabulated below. All states are valid

at TPA.

STATE CODE LINES

Signal Descriptions

Bus 0 to Bus 7 (Data Bus)

8-Bit bidirectional DATA BUS lines. These lines are used for

transferring data between the memory, the microprocessor,

and I/O devices.

N0 to N2 (I/O) Lines

Activated by an I/O instruction to signal the I/O control logic

of a data transfer between memory and I/O interface. These

lines can be used to issue command codes or device selection codes to the I/O devices. The N-bits are low at all times

except when an I/O instruction is being executed. During this

time their state is the same as the corresponding bits in the

N Register. The direction of data flow is defined in the I/O

instruction by bit N3 (internally) and is indicated by the level

of the MRD

Signal:

STATE TYPE

S0 (Fetch) L L

S1 (Execute) L H

S2 (DMA) H L

S3 (Interrupt) H H

NOTE: H = V

DD

, L = V

SS.

SC1 SC0

TPA, TPB (2 Timing Pulses)

Positive pulses that occurrence in each machine cycle (TPB

follows TPA). They ar e used by I/O controll ers to interpret

codes and to time interaction with the data bus. The trailing

edge of TPA is used by the memo ry syst em to latch th e highorder byte of the multiplexed 16-bit memory address.

9

Loading...

Loading...