Intersil Corporation CD54AC112F3A, CD54ACT112F3A Datasheet

SEMICONDUCTOR

COMPLETE DATA SHEET

CD54AC112/3A

CD54ACT112/3A

June 1997

COMING SOON!

Description

The CD54AC112/3A and CD54ACT112/3A are dual “J-K”

flip-flops with set and reset that utilize the Harris Advanced

CMOS Logic technology. These flip-flops have independent

J, K,

Set, Reset and Clock inputs and Q and Q outputs. The

CD54AC112/3A and CD54ACT112/3A changes state on the

negative-going transition of the clock.

accomplished asynchronously by low-level inputs.

The CD54AC112/3A and CD54ACT112/3A are supplied in

16 lead dual-in-line ceramic packages (F suffix).

ACT INPUT LOAD TABLE

INPUT UNIT LOAD (NOTE 1)

J, CP, CP 1

K 0.53

S, R 0.58

NOTE:

1. Unit load is∆I

Table, e.g., 2.4mA Max at +25oC.

limit specified in DC Electrical Specifications

CC

Set and Reset are

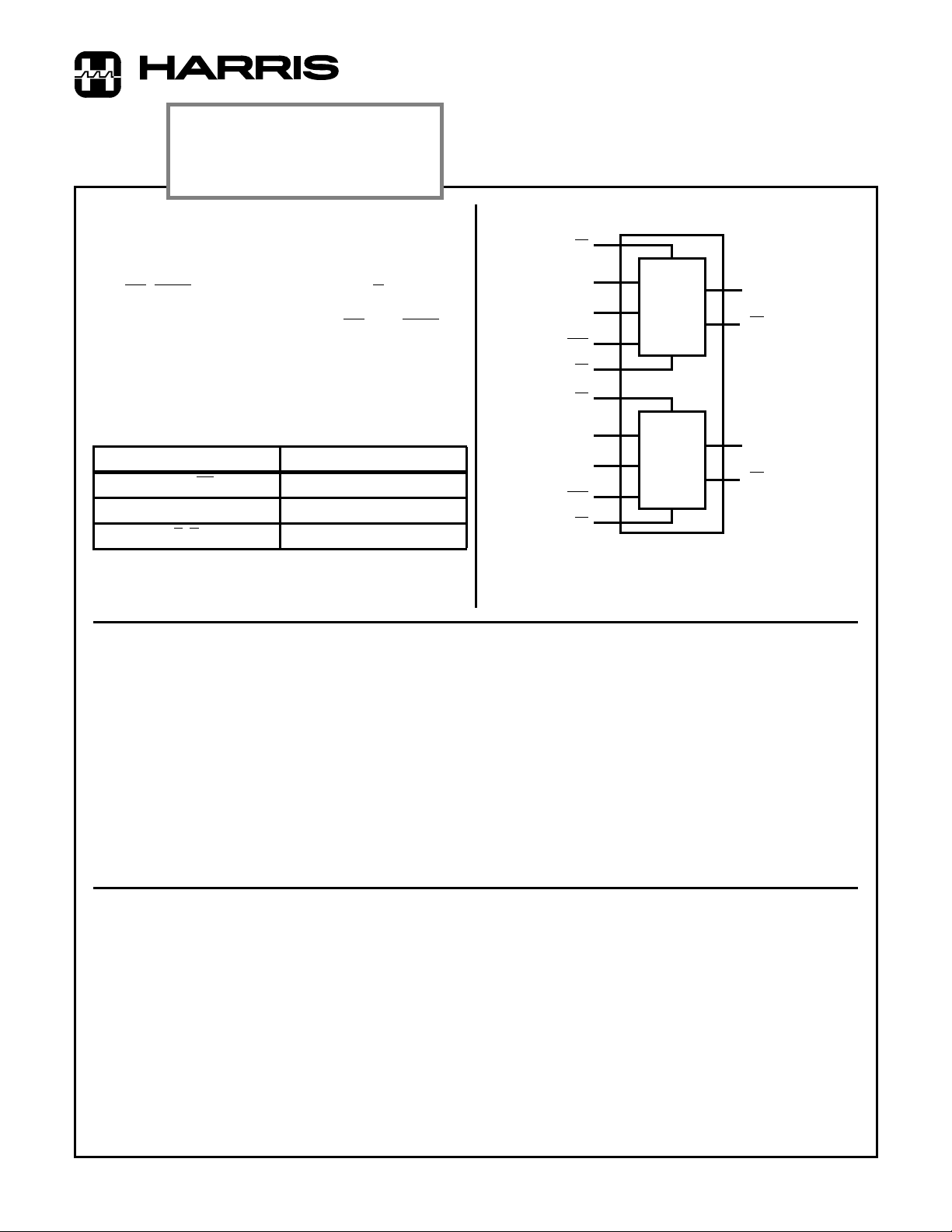

Dual “J-K” Flip-Flop with Set and Reset

Functional Diagram

4

1S

1K

1CP

1R

2S

2K

2CP

2R

3

1J

2

1

15

10

11

2J

12

13

14

FF 1

FF 2

5

1Q

6

1Q

9

2Q

7

2Q

GND = 8

V

= 16

CC

Absolute Maximum Ratings

DC Supply Voltage, VCC. . . . . . . . . . . . . . . . . . . . . . . . -0.5V to +6V

DC Input Diode Current, I

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . . . . .±20mA

DC Output Diode Current, I

For VO < -0.5V or VO > VCC + 0.5V. . . . . . . . . . . . . . . . . . . . .±50mA

DC Output Source or Sink Current, Per Output Pin, I

For VO > -0.5V or VO < VCC + 0.5V. . . . . . . . . . . . . . . . . . . . .±50mA

DC VCC or GND Current, ICC or I

For Up to 4 Outputs Per Device, Add ±25mA For Each

Additional Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±100mA

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IK

OK

O

GND

Power Dissipation Per Package, P

TA = -55oC to +100oC (Package F) . . . . . . . . . . . . . . . . . . 500mW

TA = +100oC to +125oC (Package F) . . . . . . . .Derate Linearly at

Operating Temperature Range, T

Package Type F. . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to +125oC

Storage Temperature, T

Lead Temperature (During Soldering)

At Distance 1/16in. ± 1/32in. (1.59mm ± 0.79mm)

From Case For 10s Max . . . . . . . . . . . . . . . . . . . . . . . . . . +265oC

Unit Inserted Into a PC Board (Min Thickness 1/16in., 1.59mm)

With Solder Contacting Lead Tips Only. . . . . . . . . . . . . . . +300oC

STG

D

8mW/oC to 300mW

A

. . . . . . . . . . . . . . . . . .-65oC to +150oC

Recommended Operating Conditions

Supply Voltage Range, V

Unless Otherwise Specified, All Voltages Referenced to GND

TA = Full Package Temperature Range

CD54AC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1.5V to 5.5V

CD54ACT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, VI, VO. . . . . . . . . . . . . . . . . . 0V to V

CC

Operating Temperature, TA . . . . . . . . . . . . . . . . . . .-55oC to +125oC

Input Rise and Fall Slew Rate, dt/dv

at 1.5V to 3V (AC Types) . . . . . . . . . . . . . . . . . . . 0ns/V to 50ns/V

at 3.6V to 5.5V (AC Types) . . . . . . . . . . . . . . . . . 0ns/V to 20ns/V

at 4.5V to 5.5V (AC Types) . . . . . . . . . . . . . . . . . 0ns/V to 10ns/V

CC

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures.

Copyright

© Harris Corporation 1994

1

File Number

3886

Loading...

Loading...