CD4066BMS

December 1992

Features

• For Transmission or Multiplexing of Analog or Digital

Signals

• High Voltage Types (20V Rating)

• 15V Digital or ±7.5V Peak-to-Peak Switching

• 125Ω Typical On-State Resistance for 15V Operation

• Switch On-State Resistance Matched to Within 5Ω

Over 15V Signal Input Range

• On-State Resistance Flat Over Full Peak-to-Peak Signal Range

• High On/Off Output Voltage Ratio

- 80dB Typ. at FIS = 10kHz, RL = 1kΩ

• High Degree of Linearity: <0.5% Distortion Typ. at

FIS = 1kHz, VIS = 5Vp-p, VDD - VSS ≥ 10V, RL = 10kΩ

• Extremely Low Off-State Switch Leakage Resulting in

Very Low Offset Current and High Effective Off-State

Resistance: 10pA Typ. at VDD - VSS = 10V, T

• Extremely High Control Input Impedance (Control Circuit Isolated from Signal Circuit): 10

12

Ω Typ.

• Low Crosstalk Between Switches: -50dB Typ. at FIS =

8MHz, RL = 1kΩ

• Matched Control Input to Signal Output

Capacitance: Reduces Output Signal Transients

= +25oC

A

CMOS Quad Bilateral Switch

Description

CD4066BMS is a quad bilateral switch intended for the

transmission or multiplexing of analog or digital signals. It is

pin for pin compatible with CD4016B, but exhibits a much

lower on state resistance. In addition, the on-state resistance

is relatively constant over the full input signal range.

The CD4066BMS consists of four independent bilateral

switches. A single control signal is required per switch. Both

the p and the n device in a given switch are biased on or off

simultaneously by the control signal. As shown in Figure 1,

the well of the n channel device on each switch is either tied

to the input when the switch is on or to VSS when the switch

is off. This configuration eliminates the variation of the switch

transistor threshold voltage with input signal, and thus keeps

the on-state resistance low over the full operating signal

range.

The advantages over single channel switches include peak

input signal voltage swings equal to the full supply voltage,

and more constant on-state impedance over the input signal

range. For sample and hold applications, however, the

CD4016B is recommended.

The CD4066BMS is supplied in these 14-lead outline packages:

Braze Seal DIP H4Q

Frit Seal DIP H1B

Ceramic Flatpack H3W

• Frequency Response, Switch on = 40MHz (Typ.)

• 100% Tested for Quiescent Current at 20V

Pinout

• 5V, 10V and 15V Parametric Ratings

• Meets All Requirements of JEDEC Tentative Standard

No. 13B, “Standard Specifications for Description of

“B” Series CMOS Devices”

Applications

• Analog Signal Switching/Multiplexing

- Signal Gating - Modulator

- Squelch Control - Demodulator

- Chopper - Commutating Switch

• Digital Signal Switching/Multiplexing

• Transmission Gate Logic Implementation

• Analog to Digital & Digital to Analog Conversion

• Digital Control of Frequency, Impedance, Phase, and

Analog Signal Gain

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

7-966

IN/OUT A

OUT/IN A

OUT/IN B

IN/OUT B

CONT B

CONT C

VSS

CD4066BMS

TOP VIEW

1

2

3

4

5

6

7

14

VDD

13

CONT A

12

CONT D

11

IN/OUT D

10

OUT/IN D

9

OUT/IN C

8

IN/OUT C

File Number

3319

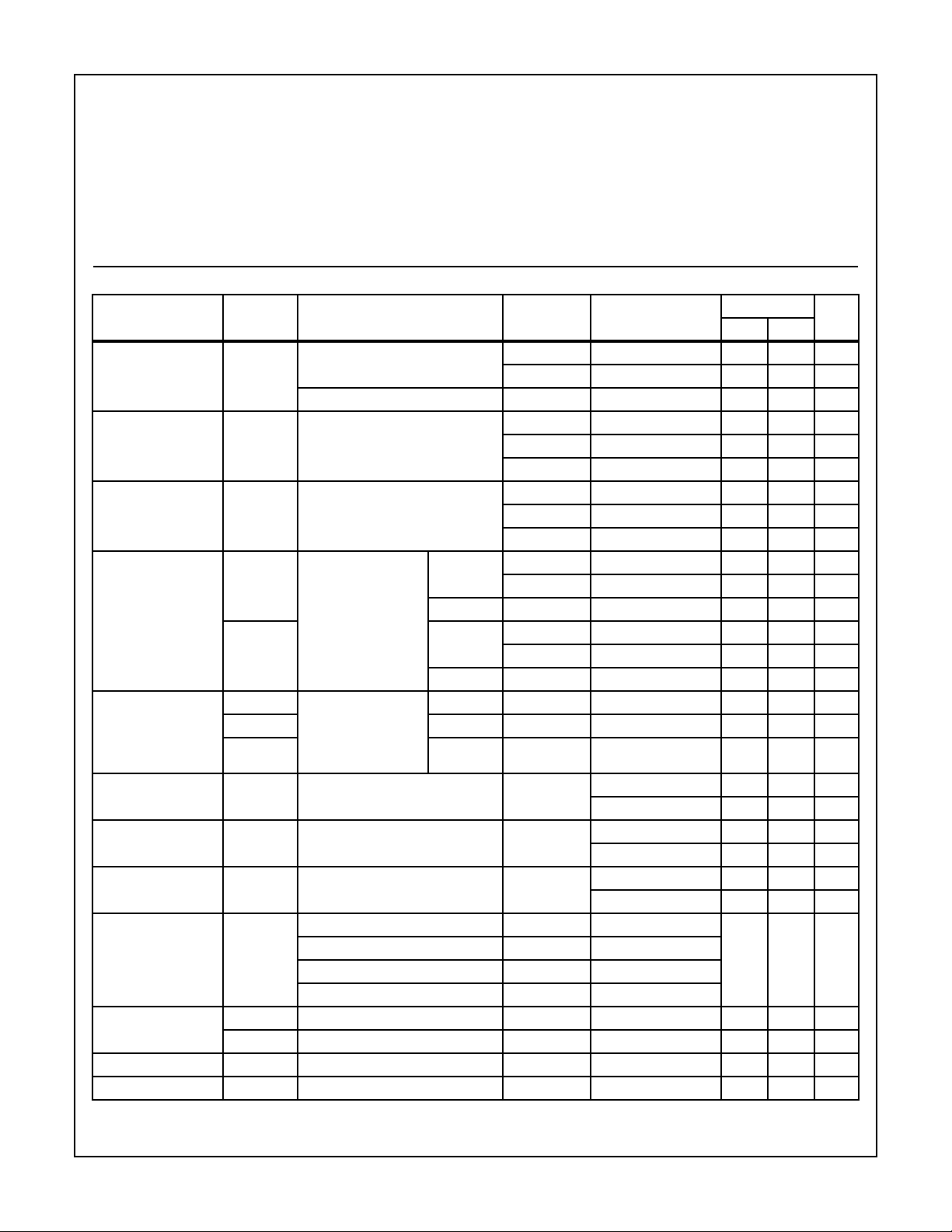

Specifications CD4066BMS

Absolute Maximum Ratings Reliability Information

DC Supply Voltage Range, (VDD) . . . . . . . . . . . . . . . -0.5V to +20V

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VDD +0.5V

DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Operating Temperature Range. . . . . . . . . . . . . . . . -55

Package Types D, F, K, H

Storage Temperature Range (TSTG) . . . . . . . . . . . -65

o

C to +125oC

o

C to +150oC

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for

10s Maximum

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1)

Supply Current IDD VDD = 20V, VIN = VDD or GND 1 +25

VDD = 18V, VIN = VDD or GND 3 -55oC - 0.5 µA

Input Leakage Current IIL VC = VDD or GND 1 +25

Input Leakage Current IIH VC = VDD or GND 1 +25oC - 100 nA

Input/Output Leakage

Current (Switch OFF)

IOZL VC = 0V, VIS = 18V,

VOS = 0V, VIS = 0V,

VDD = 20 1 +25oC -100 - nA

VOS = 18V

VDD = 18V 3 -55oC -100 - nA

IOZH VDD = 20 1 +25oC - 100 nA

VDD = 18V 3 -55oC - 100 nA

On Resistance RON5 VC = VDD, RL = 10kW

RON10 VDD = 10V 1 +25oC 400 - Ω

returned to VDD VSS/2

VDD = 5V 1 +25oC 1050 - Ω

RON15 VDD = 15V 1 +25oC 240 - Ω

VIS = VSS to VDD

On Resistance RON5 VDD = 5V 1, 2 +125oC - 1300 Ω

On Resistance RON10 VDD = 10V 1, 2 +125oC - 550 Ω

On Resistance RON15 VDD = 15V 1, 2 +125oC - 320 Ω

Functional

(Note 3)

F VDD = 2.8V, VIN = VDD or GND 7 +25oC VOH >

VDD = 20V, VIN = VDD or GND 7 +25oC

VDD = 18V, VIN = VDD or GND 8A +125oC

VDD = 3V, VIN = VDD or GND 8B -55oC

Switch Threshold

RL = 100k to VDD

SWTHRH5 VDD = 5V, VC = 1.5V, VIS = GND 1, 2, 3 +25oC, +125oC, -55oC 4.1 - V

SWTHRH15 VDD = 15V, VC = 2V, VIS = GND 1, 2, 3 +25oC, +125oC, -55oC 14.1 - V

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1 +25oC -2.8 -0.7 V

P Threshold Voltage VPTH VSS = 0V, IDD = 10µA 1 +25oC 0.7 2.8 V

Thermal Resistance . . . . . . . . . . . . . . . . θ

Ceramic DIP and FRIT Package. . . . . 80oC/W 20oC/W

Flatpack Package . . . . . . . . . . . . . . . . 70

Maximum Package Power Dissipation (PD) at +125oC

For TA = -55

For TA = +100

o

C

Device Dissipation per Output Transistor . . . . . . . . . . . . . . . 100mW

o

C to +100oC (Package Type D, F, K). . . . . . 500mW

o

C to +125oC (Package Type D, F, K) . . . . .Derate

Linearity at 12mW/oC to 200mW

ja

o

C/W 20oC/W

For TA = Full Package Temperature Range (All Package Types)

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

GROUP A

LIMITS

SUBGROUPS TEMPERATURE

o

C - 0.5 µA

2 +125oC-50µA

o

C -100 - nA

2 +125oC -1000 - nA

3 -55oC -100 - nA

2 +125oC - 1000 nA

3 -55oC - 100 nA

2 +125oC -1000 - nA

2 +125oC - 1000 nA

-55oC - 800 Ω

-55oC - 310 Ω

-55oC - 220 Ω

VOL <

VDD/2

VDD/2

θ

jc

UNITSMIN MAX

V

7-967

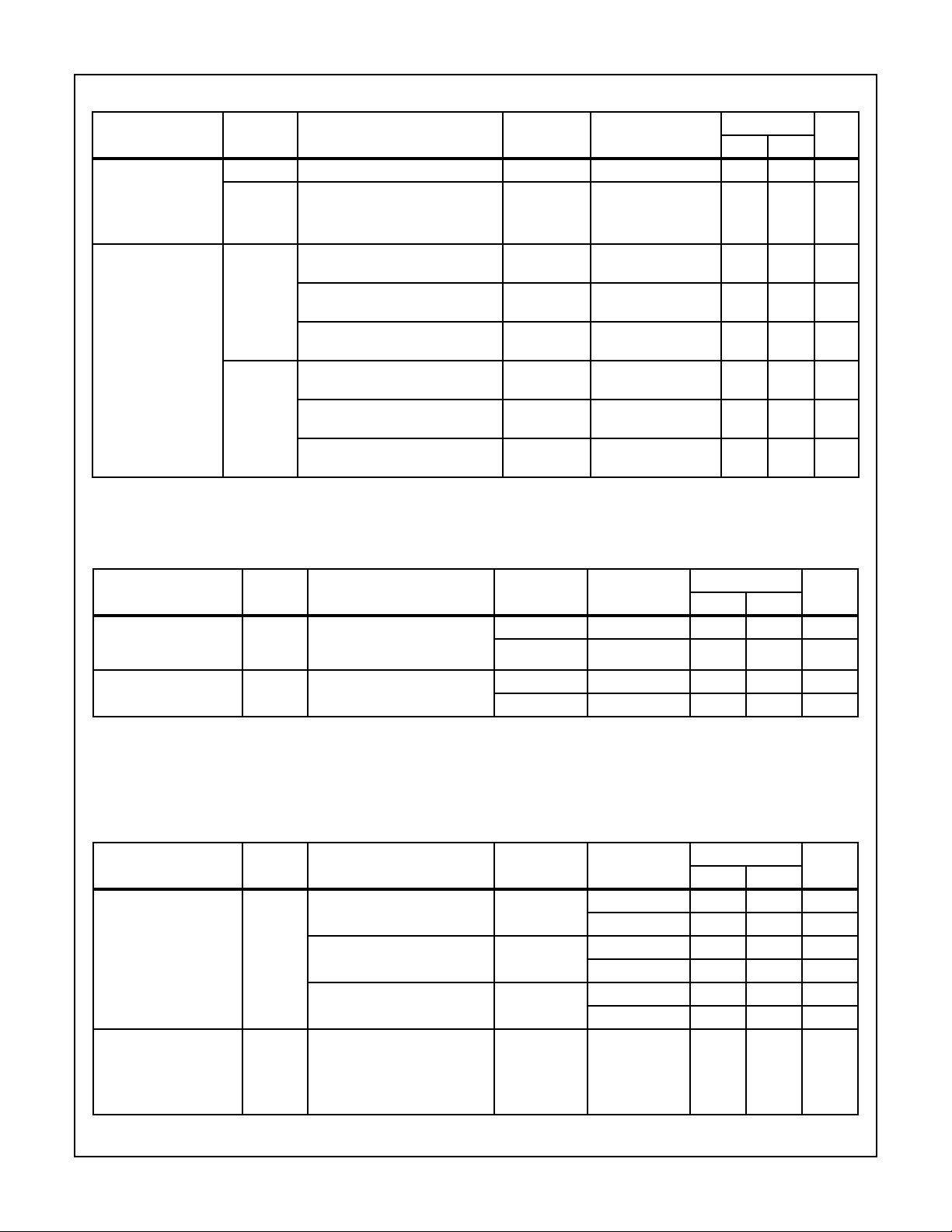

Specifications CD4066BMS

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1)

Control Input Low

Voltage (Note 2)

|IIS| < 10µa, VIS = VSS,

VOS = VDD and

VIS = VDD, VOS = VSS

Control Input High

Voltage

(Note 2, Figure 2)

VIS = VSS and VIS =

VDD

NOTES: 1. All voltages referenced to device GND, 100% testing being

implemented.

2. Go/No Go test with limits applied to inputs.

VILC5 VDD = 5V 1, 2, 3 +25oC, +125oC, -55oC- 1 V

VILC15 VDD = 15V 1, 2, 3 +25oC, +125oC, -55oC- 2 V

VIHC VDD = 5V, |IIS| = .51mA, 4.6V <

VOS < 0.4V

VDD = 5V, |IIS| = .36mA, 4.6V <

VOS < 0.4V

VDD = 5V, |IIS| = .64mA, 4.6V <

VOS < 0.4V

VIHC VDD = 15V, |IIS| = 3.4mA, 13.5V <

VOS <1.5V

VDD = 15V, |IIS| = 2.4mA, 13.5V <

VOS < 1.5V

VDD = 15V, |IIS| = 4.2mA, 13.5V <

VOS <1.5V

GROUP A

SUBGROUPS TEMPERATURE

1 +25oC 3.5 - V

2 +125oC 3.5 - V

3 -55oC 3.5 - V

1 +25oC11-V

2 +125oC11-V

3 -55oC11-V

3. VDD = 2.8V/3.0V, RL = 100K to VDD

VDD = 20V/18V, RL = 10K to VDD

LIMITS

UNITSMIN MAX

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

GROUP A

PARAMETER SYMBOL CONDITIONS

Propagation Delay

Signal Input to Signal

Output

Propagation Delay

Turn-On, Turn-Off

NOTES:

1. CL = 50pF, RL = 1K, Input TR, TF < 20ns.

2. -55oC and +125oC limits guaranteed, 100% testing being implemented.

3. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

Supply Current IDD VDD = 5V, VIN = VDD or GND 1, 2 -55oC, +25oC - 0.25 µA

Control Input Low

Voltage

|IIS| < 10µa, VIS = VSS,

VOS = VDD and

VIS = VDD, VOS = VSS

TPLH

TPHL

TPHZ/ZH

TPLZ/ZL

VILC10 VDD = 10V 1, 2 +25oC, +125oC,

VC = VDD = 5V, VSS = GND

(Notes 2, 3)

VIS = VDD = 5V (Notes 1, 2) 9 +25oC - 70 ns

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

VDD = 10V, VIN = VDD or GND 1, 2 -55oC, +25oC - 0.5 µA

VDD = 15V, VIN = VDD or GND 1, 2 -55oC, +25oC - 0.5 µA

SUBGROUPS TEMPERA TURE

9 +25oC - 40 ns

10, 11 +125oC, -55oC - 54 ns

10, 11 +125oC, -55oC - 95 ns

+125oC - 7.5 µA

+125oC-15µA

+125oC-30µA

-55oC

LIMITS

UNITSMIN MAX

LIMITS

UNITSMIN MAX

-2V

7-968

Loading...

Loading...