Intersil Corporation CD4050BMS Datasheet

CD4050BMS

December 1992 File Number 3193

CMOS Hex Buffer/Converter

The CD4050BMS is an non-inverting hex buffer and features

logic level conversion using only one supply voltage (VCC).

The input signal high level (VIH) can exceed the VCC supply

voltage when this device is used for logic level conversions.

This device is intended for use as CMOS to DTL/TTL

converters and can drive directly two DTL/TTL loads. (VCC

= 5V, VOL ≤ 0.4V, and IOL ≥ 3.3mA.

The CD4050BMS is designated as replacement for

CD4010B. Because the CD4050BMS requires only one

power supply, it is preferred over the CD4010B and should

be used in place of the CD4010B in all inverter, current

driver, or logic level conversion applications. In these applications the CD4050BMS is pin compatible with the

CD4010B, and can be substituted for this device in existing

as well as in new designs. Terminal No. 16 is not connected

internally on the CD4050BMS, therefore, connection to this

terminal is of no consequence to circuit operation. For applications not requiring high sink current or voltage conversion,

the CD4069UB Hex Inverter is recommended.

The CD4050BMS is supplied in these 16 lead outline packages:

Braze Seal DIP H4T

Frit Seal DIP H1E

Ceramic Flatpack H3X

Features

• High Voltage Type (20V Rating)

• Non-Inverting Type

• High Sink Current for Driving 2 TTL Loads

• High-to-Low Level Logic Conversion

• 100% Tested for Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full Pack-

age Temperature Range; 100nA at 18V and +25

o

C

• 5V, 10V and 15V Parametric Ratings

Applications

• CMOS to DTL/TTL Hex Converter

• CMOS Current “Sink” or “Source” Driver

• CMOS High-to-Low Logic Level Converter

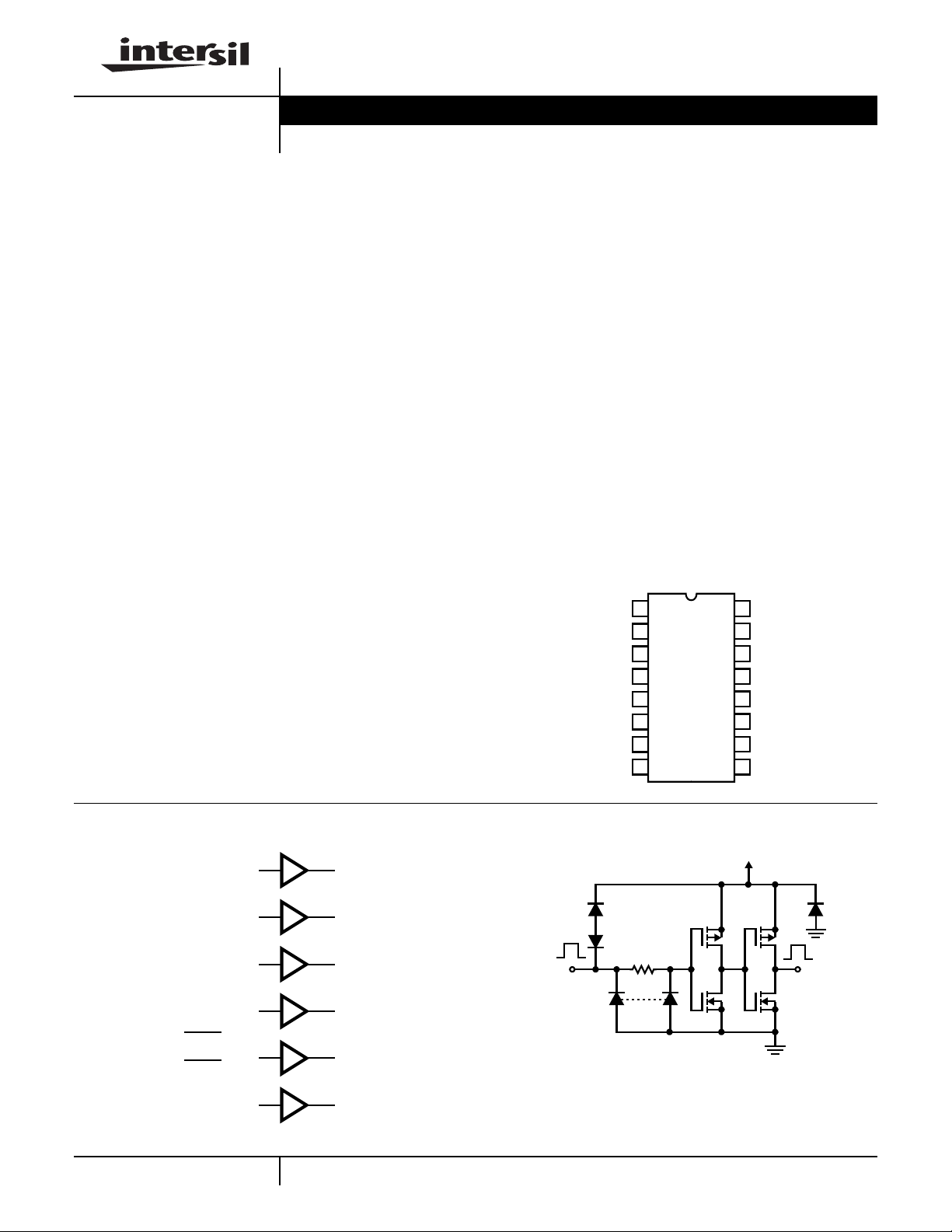

Pinout

VCC

G = A

H = B

I = C

VSS

1

2

3

A

4

B

5

6

C

7

8

CD4050BMS

TOP VIEW

NC

16

L = F

15

F

14

NC

13

K = E

12

E

11

J = D

10

D

9

Functional Diagram Schematic Diagram

32

A G = A

54

B H = B

VCC

VSS

NC = 13

NC = 16

C I = C

D J = D

1

8

E K = E

F L = F

4-1

76

910

11 12

14 15

IN

FIGURE 1. SCHEMATIC DIAGRAM, 1 OF 6 IDENTICAL UNITS

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

www.intersil.com or 407-727-9207

R

VCC

P

N

| Copyright © Intersil Corporation 1999

P

OUT

N

VSS

CD4050BMS

Absolute Maximum Ratings Reliability Information

DC Supply Voltage Range, (VDD) . . . . . . . . . . . . . . . .-0.5V to +20V

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . . . . . . . . . . . -0.5V to VDD +0.5V

DC Input Current, Any One Input. . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Operating Temperature Range . . . . . . . . . . . . . . . -55oC to +125oC

Package Types D, F, K, H

Storage Temperature Range (TSTG). . . . . . . . . . . -65oC to +150oC

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265oC

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for

10s Maximum

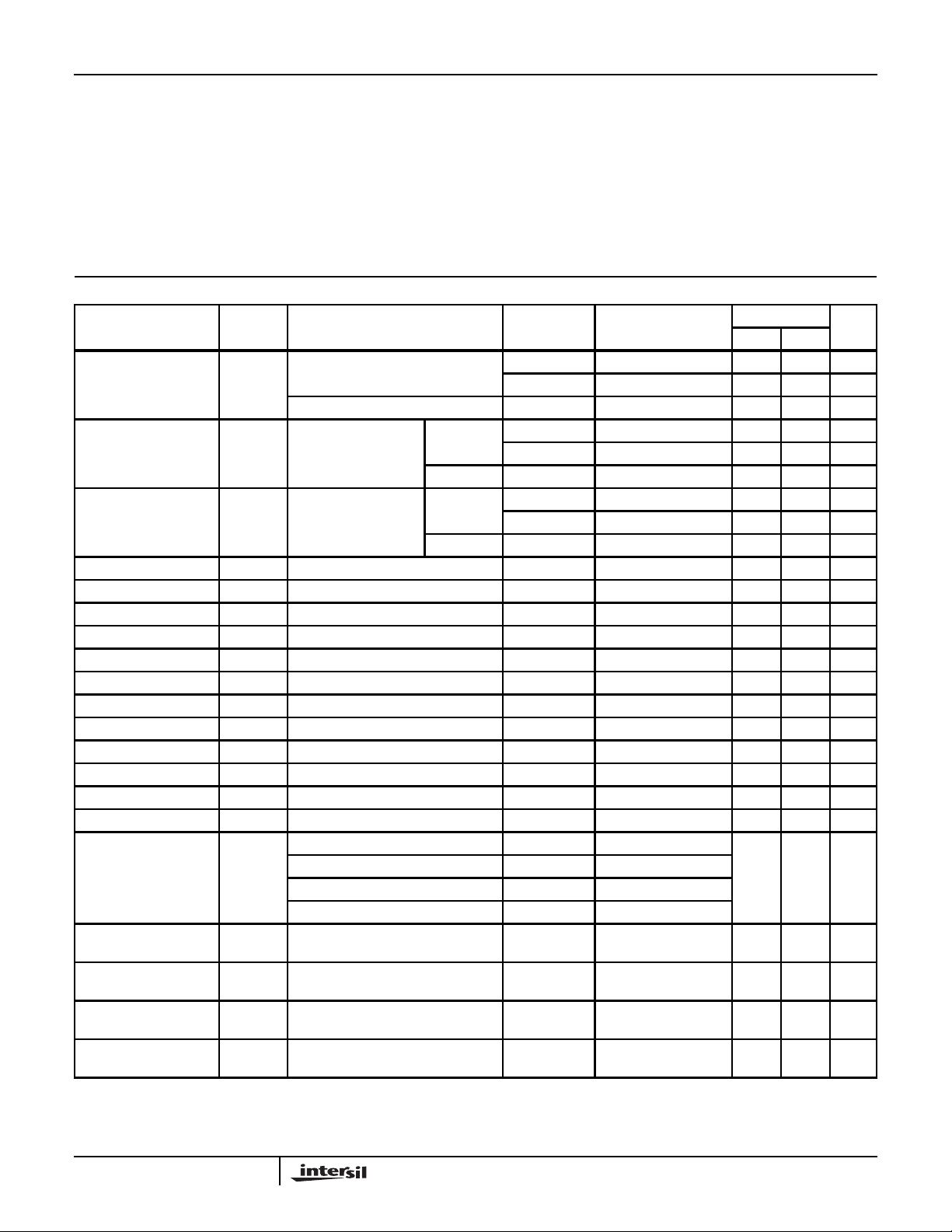

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1)

Supply Current IDD VDD = 20V, VIN = VDD or GND 1 +25

VDD = 18V, VIN = VDD or GND 3 -55

Input Leakage Current IIL VIN = VDD or GND VDD = 20 1 +25

VDD = 18V 3 -55

Input Leakage Current IIH VIN = VDD or GND VDD = 20 1 +25

VDD = 18V 3 -55

Output Voltage VOL15 VDD = 15V, No Load 1, 2, 3 +25

Output Voltage VOH15 VDD = 15V, No Load (Note 3) 1, 2, 3 +25

Output Current (Sink) IOL4 VDD = 4.5V, VOUT = 0.4V 1 +25

Output Current (Sink) IOL5 VDD = 5V, VOUT = 0.4V 1 +25

Output Current (Sink) IOL10 VDD = 10V, VOUT = 0.5V 1 +25

Output Current (Sink) IOL15 VDD = 15V, VOUT = 1.5V 1 +25

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1 +25

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1 +25

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1 +25

Output Current (Source) IOH15 VDD = 15V, VOUT = 13.5V 1 +25

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1 +25

P Threshold Voltage VPTH VSS = 0V, IDD = 10µA 1 +25

Functional F VDD = 2.8V, VIN = VDD or GND 7 +25

VDD = 20V, VIN = VDD or GND 7 +25

VDD = 18V, VIN = VDD or GND 8A +125

VDD = 3V, VIN = VDD or GND 8B -55

Input Voltage Low

VIL VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25

(Note 2)

Input Voltage High

VIH VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25

(Note 2)

Input Voltage Low

(Note 2)

Input Voltage High

(Note 2)

VIL VDD = 15V, VOH > 13.5V,

VOL < 1.5V

VIH VDD = 15V, VOH > 13.5V,

VOL < 1.5V

NOTES: 1. All voltages referenced to device GND, 100% testing being im-

plemented.

2. Go/No Go test with limits applied to inputs.

Thermal Resistance. . . . . . . . . . . . . . . . θ

Ceramic DIP and FRIT Package . . . . 80oC/W 20oC/W

Flatpack Package. . . . . . . . . . . . . . . . 70oC/W 20oC/W

Maximum Package Power Dissipation (PD) at +125oC

For TA = -55oC to +100oC (Package Type D, F, K) . . . . . .500mW

For TA = +100oC to +125oC (Package Type D, F, K) . . . . . Derate

Device Dissipation per Output Transistor. . . . . . . . . . . . . . . .100mW

For TA = Full Package Temperature Range (All Package Types)

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+175oC

GROUP A

SUBGROUPS TEMPERATURE

2 +125

2 +125

2 +125

o

C, +125oC, -55oC - 50 mV

o

C, +125oC, -55oC 14.95 - V

o

C, +125oC, -55oC - 1.5 V

o

C, +125oC, -55oC 3.5 - V

o

1, 2, 3 +25

1, 2, 3 +25

C, +125oC, -55oC- 4 V

o

C, +125oC, -55oC11 - V

3. For accuracy,voltage ismeasured differentiallyto VDD.Limit is

0.050V max.

ja

θ

jc

Linearity at 12mW/oC to 200mW

LIMITS

UNITSMIN MAX

o

C-2µA

o

C - 200 µA

o

C-2µA

o

C -100 - nA

o

C -1000 - nA

o

C -100 - nA

o

C - 100 nA

o

C - 1000 nA

o

C - 100 nA

o

C 2.6 - mA

o

C 3.2 - mA

o

C 8.0 - mA

o

C24-mA

o

C - -0.8 mA

o

C - -3.2 mA

o

C - -1.8 mA

o

C - -6.0 mA

o

C -2.8 -0.7 V

o

C 0.7 2.8 V

o

C VOH >

o

C

o

C

o

C

VDD/2

VOL <

VDD/2

V

4-2

CD4050BMS

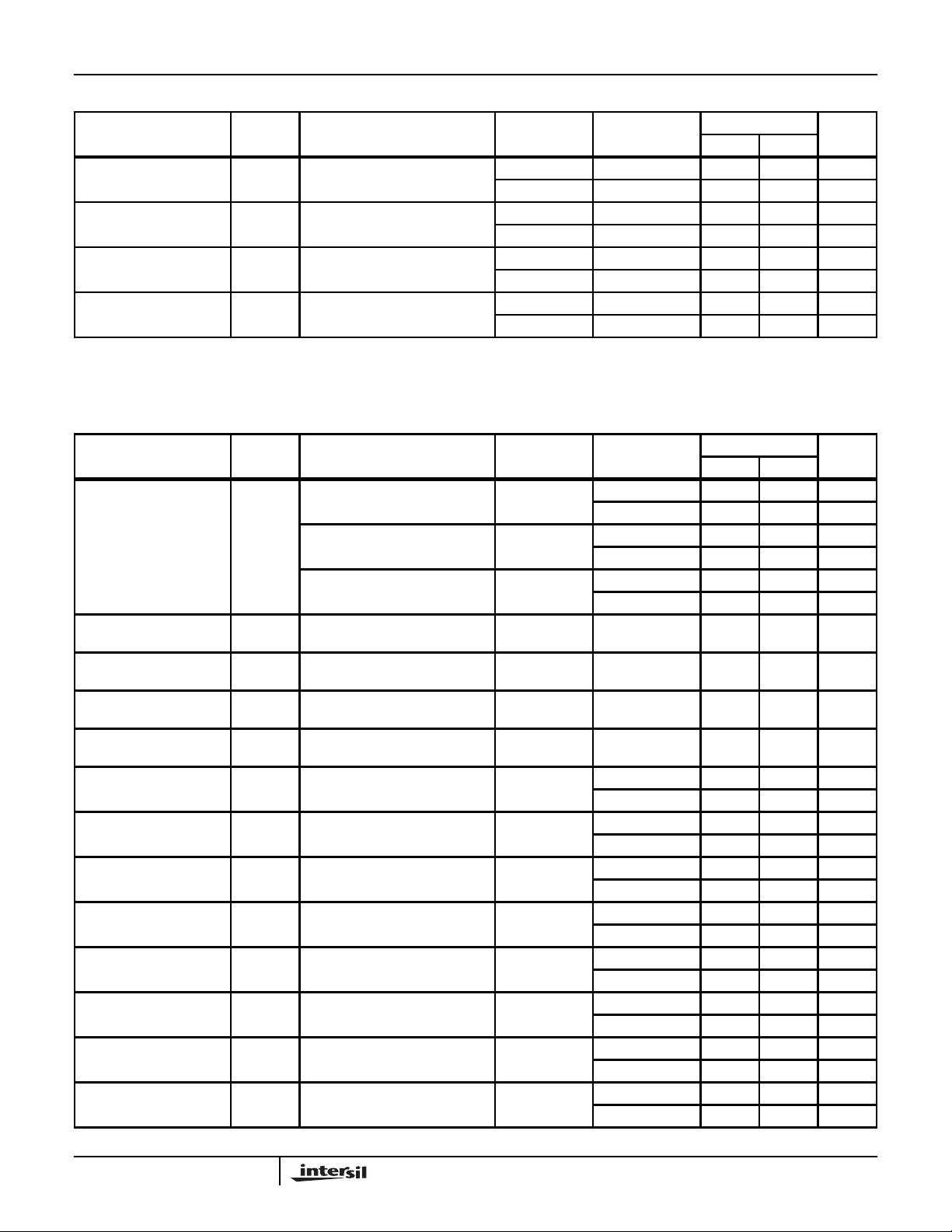

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

GROUP A

PARAMETER SYMBOL CONDITIONS (NOTE 1, 2)

Propagation Delay TPHL VDD = 5V, VIN = VDD or GND 9 +25

Propagation Delay TPLH VDD = 5V, VIN = VDD or GND 9 +25oC - 140 ns

Transition Time TTHL VDD = 5V, VIN = VDD or GND 9 +25oC - 60 ns

Transition Time TTLH VDD = 5V, VIN = VDD or GND 9 +25oC - 160 ns

NOTES:

1. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

2. -55oC and +125oC limits guaranteed, 100% testing being implemented.

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

Supply Current IDD VDD = 5V, VIN = VDD or GND 1, 2 -55

VDD = 10V, VIN = VDD or GND 1, 2 -55oC, +25oC- 2 µA

VDD = 15V, VIN = VDD or GND 1, 2 -55oC, +25oC- 2 µA

Output Voltage VOL VDD = 5V, No Load 1, 2 +25oC, +125oC, -

Output Voltage VOL VDD = 10V, No Load 1, 2 +25oC, +125oC, -

Output Voltage VOH VDD = 5V, No Load 1, 2 +25oC, +125oC, -

Output Voltage VOH VDD = 10V, No Load 1, 2 +25oC, +125oC, -

Output Current (Sink) IOL4 VDD = 4.5V, VOUT = 0.4V 1, 2 +125oC 1.8 - mA

Output Current (Sink) IOL5 VDD = 5V, VOUT = 0.4V 1, 2 +125oC 2.4 - mA

Output Current (Sink) IOL10 VDD = 10V, VOUT = 0.5V 1, 2 +125oC 5.6 - mA

Output Current (Sink) IOL15 VDD = 15V, VOUT = 1.5V 1, 2 +125oC18-mA

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1, 2 +125oC - -0.48 mA

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1, 2 +125oC - -1.55 mA

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1, 2 +125oC - -1.18 mA

Output Current (Source) IOH15 VDD =15V, VOUT = 13.5V 1, 2 +125oC - -3.1 mA

SUBGROUPS TEMPERATURE

o

C - 110 ns

10, 11 +125oC, -55oC - 149 ns

10, 11 +125oC, -55oC - 189 ns

10, 11 +125oC, -55oC - 81 ns

10, 11 +125oC, -55oC - 216 ns

o

C, +25oC- 1 µA

+125oC-30µA

+125oC-60µA

+125oC - 120 µA

55oC

55oC

55oC

55oC

-55oC 3.3 - mA

-55oC 4.0 - mA

-55oC10-mA

-55oC26-mA

-55oC - -0.81 mA

-55oC - -2.6 mA

-55oC - -2.0 mA

-55oC - -5.2 mA

LIMITS

UNITSMIN MAX

LIMITS

UNITSMIN MAX

-50mV

-50mV

4.95 - V

9.95 - V

4-3

Loading...

Loading...