Intersil Corporation CD4031BMS Datasheet

CD4031BMS

December 1992

Features

• High Voltage Type (20V Rating)

• Fully Static Operation: DC to 12MHz (typ.) at VDD VSS = 15V

• Standard TTL Drive Capability on Q Output

• Recirculation Capability

• Three Cascading Modes:

- Direct Clocking for High-Speed Operation

- Delayed Clocking for Reduced Clock Drive Require-

ments

- Additional 1/2 Stage for Slow Clocks

• 100% Tested For Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full

Package-Temperature Range;

- 100nA at 18V and +25

o

C

• Noise Margin (Over Full Package T emperature Range):

- 1V at VDD = 5V

- 2V at VDD = 10V

- 2.5V at VDD = 15V

• 5V, 10V and 15V Parametric Ratings

• Meets All Requirements of JEDEC Tentative Standard

No. 13B, “Standard Specifications for Description of

‘B’ Series CMOS Devices”

Applications

• Serial Shift Registers

• Time Delay Circuits

CMOS 64-Stage Static Shift Register

Description

The CD4031BMS is a static shift register that contains 64 Dtype, master-slave flip-flop stages and one stage which is a

D-type master flip-flop only (referred to as a 1/2 stage).

The logic level present at the DATA input is transferred into

the first stage and shifted one stage at each positive-going

clock transition. Maximum clock frequencies up to 12MHz

(typical) can be obtained. Because fully static operation is

allowed, information can be permanently stored with the

clock line in either the low or high state. The CD4031BMS

has a MODE CONTROL input that, when in the high state,

allows operation in the recirculating mode. The MODE CONTROL input can also be used to select between two separate data sources. Register packages can be cascaded and

the clock lines driven directly for high-speed operation. Alternatively, a delayed clock output (CLD) is provided that

enables cascading register packages while allowing reduced

clock drive fan-out and transition-time requirements. A third

cascading option makes use of the Q’ output from the 1/2

stage, which is available on the next negative-going transition of the clock after the Q output occurs. This delayed output, like the delayed clock CLD, is used with clocks having

slow rise and fall times.

The CD4031BMS is supplied in these 16 lead outline packages:

Braze Seal DIP H4X

Frit Seal DIP H1F

Ceramic Flatpack H6W

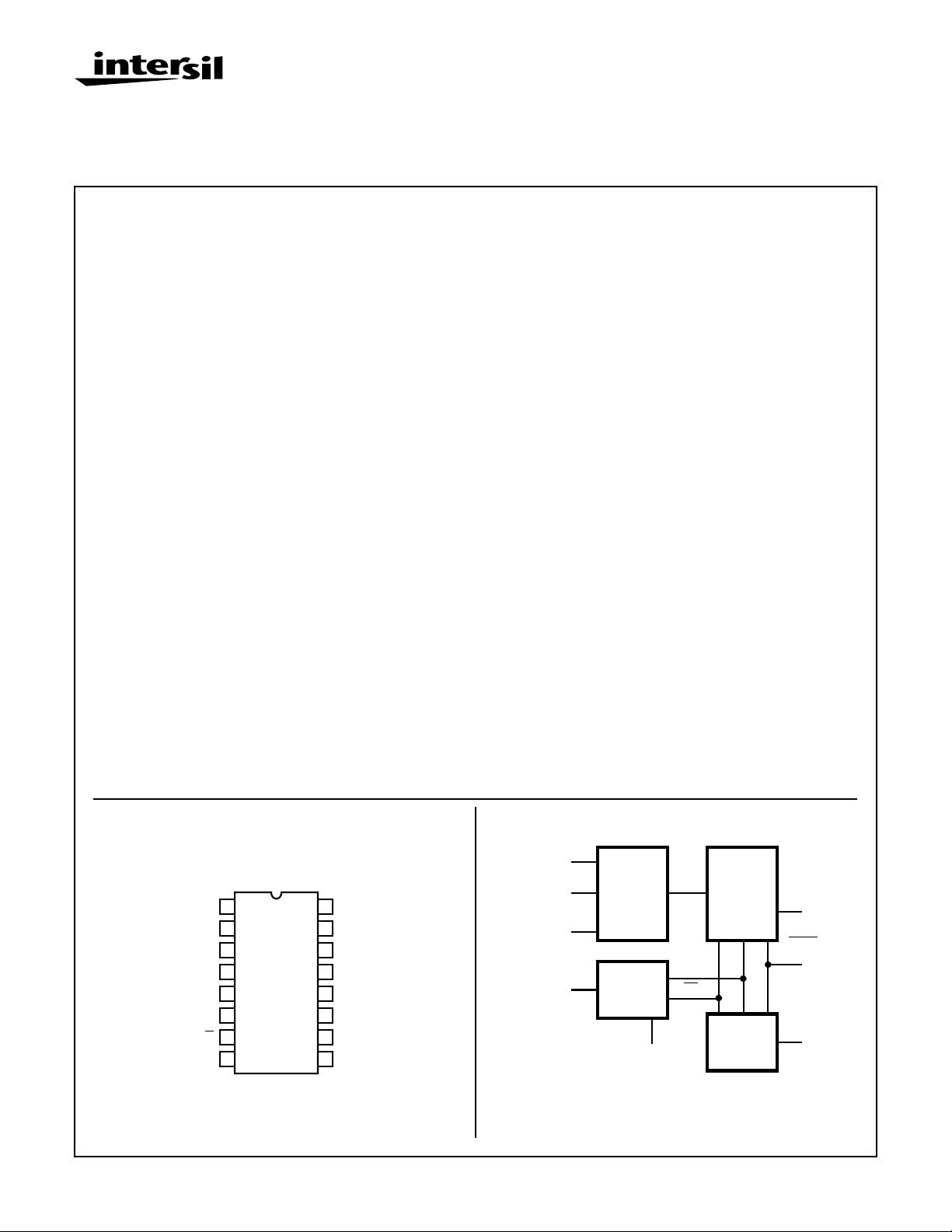

Pinout

CD4031BMS

TOP VIEW

RECIRCULATE

DATA IN 2

CLOCK INHIBIT

NC = NO CONNECTION

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

NC

NC

VSS

1

2

3

4

5

Q’

6

Q

7

Q

8

VDD

16

15

DATA IN 1

NC

14

NC

13

NC

12

NC

11

MODE CONTROL

10

CLD

9

Functional Diagram

DATA 1

IN

MODE

CONT.

RECIRC

DATA 2

IN

CLOCK

IN

VDD = 16

VSS = 8

NC = 3, 4, 11, 12, 13, 14

7-816

15

10

1

2

CONTROL

LOGIC

CLOCK

LOGIC

9

DELAYED

CLOCK

OUT

CL

CL

64

STAGES

1/2

STAGE

File Number

DATA

OUT

6

DATA

OUT

7

Q’

5

3306

Specifications CD4031BMS

Absolute Maximum Ratings Reliability Information

DC Supply Voltage Range, (VDD) . . . . . . . . . . . . . . . -0.5V to +20V

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VDD +0.5V

DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Operating Temperature Range. . . . . . . . . . . . . . . . -55

Package Types D, F, K, H

Storage Temperature Range (TSTG) . . . . . . . . . . . -65

o

C to +125oC

o

C to +150oC

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for

10s Maximum

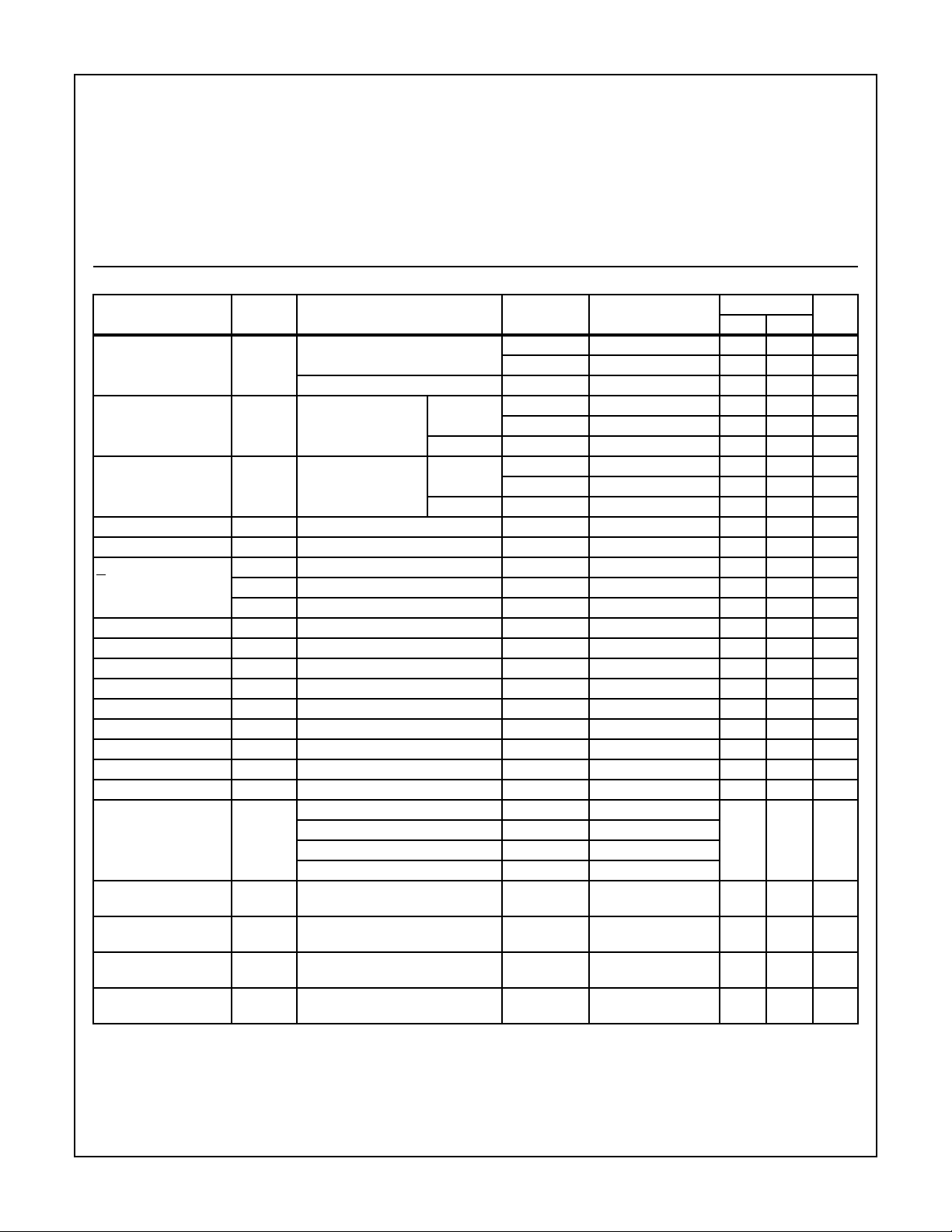

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1)

Supply Current IDD VDD = 20V, VIN = VDD or GND 1 +25oC-10µA

VDD = 18V, VIN = VDD or GND 3 -55

Input Leakage Current IIL VIN = VDD or GND VDD = 20 1 +25

VDD = 18V 3 -55oC -100 - nA

Input Leakage Current IIH VIN = VDD or GND VDD = 20 1 +25oC - 100 nA

VDD = 18V 3 -55oC - 100 nA

Output Voltage VOL15 VDD = 15V, No Load 1, 2, 3 +25oC, +125oC, -55oC - 50 mV

Output Voltage VOH15 VDD = 15V, No Load (Note 3) 1, 2, 3 +25oC, +125oC, -55oC 14.95 - V

Output Current

Q, Q’, CLD

IOL5 VDD = 5V, VOUT = 0.4V 1 +25oC 0.51 - mA

IOL10 VDD = 10V, VOUT = 0.5V 1 +25oC 1.3 - mA

IOL15 VDD = 15V, VOUT = 1.5V 1 +25oC 3.4 - mA

Output Current Q IOL5 VDD = 5V, VOUT = 0.4V 1 +25oC 2.04 - mA

Output Current Q IOL10 VDD = 10V, VOUT = 0.5V 1 +25oC 5.2 - mA

Output Current Q IOL15 VDD = 15V, VOUT = 1.5V 1 +25oC 13.6 - mA

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1 +25oC - -0.51 mA

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1 +25oC - -1.6 mA

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1 +25oC - -1.3 mA

Output Current (Source) IOH15 VDD = 15V, VOUT = 13.5V 1 +25oC - -3.4 mA

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1 +25oC -2.8 -0.7 V

P Threshold Voltage VPTH VSS = 0V, IDD = 10µA 1 +25oC 0.7 2.8 V

Functional F VDD = 2.8V, VIN = VDD or GND 7 +25oC VOH >

VDD = 20V, VIN = VDD or GND 7 +25oC

VDD = 18V, VIN = VDD or GND 8A +125oC

VDD = 3V, VIN = VDD or GND 8B -55oC

Input Voltage Low

VIL VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25oC, +125oC, -55oC - 1.5 V

(Note 2)

Input Voltage High

VIH VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25oC, +125oC, -55oC 3.5 - V

(Note 2)

Input Voltage Low

(Note 2)

Input Voltage High

(Note 2)

VIL VDD = 15V, VOH > 13.5V,

VOL < 1.5V

VIH VDD = 15V, VOH > 13.5V,

VOL < 1.5V

NOTES: 1. All voltages referenced to device GND, 100% testing being

implemented.

2. Go/No Go test with limits applied to inputs.

Thermal Resistance . . . . . . . . . . . . . . . . θ

Ceramic DIP and FRIT Package. . . . . 80oC/W 20oC/W

Flatpack Package . . . . . . . . . . . . . . . . 70

Maximum Package Power Dissipation (PD) at +125oC

For TA = -55

For TA = +100

o

C

Device Dissipation per Output Transistor . . . . . . . . . . . . . . . 100mW

o

C to +100oC (Package Type D, F, K). . . . . . 500mW

o

C to +125oC (Package Type D, F, K) . . . . .Derate

Linearity at 12mW/oC to 200mW

ja

o

C/W 20oC/W

For TA = Full Package Temperature Range (All Package Types)

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

GROUP A

LIMITS

SUBGROUPS TEMPERATURE

2 +125oC - 1000 µA

o

C-10µA

o

C -100 - nA

2 +125oC -1000 - nA

2 +125oC - 1000 nA

VOL <

VDD/2

VDD/2

1, 2, 3 +25oC, +125oC, -55oC- 4 V

1, 2, 3 +25oC, +125oC, -55oC11 - V

3. For accuracy, voltage is measured differentially to VDD. Limit

is 0.050V max.

θ

jc

UNITSMIN MAX

V

7-817

Specifications CD4031BMS

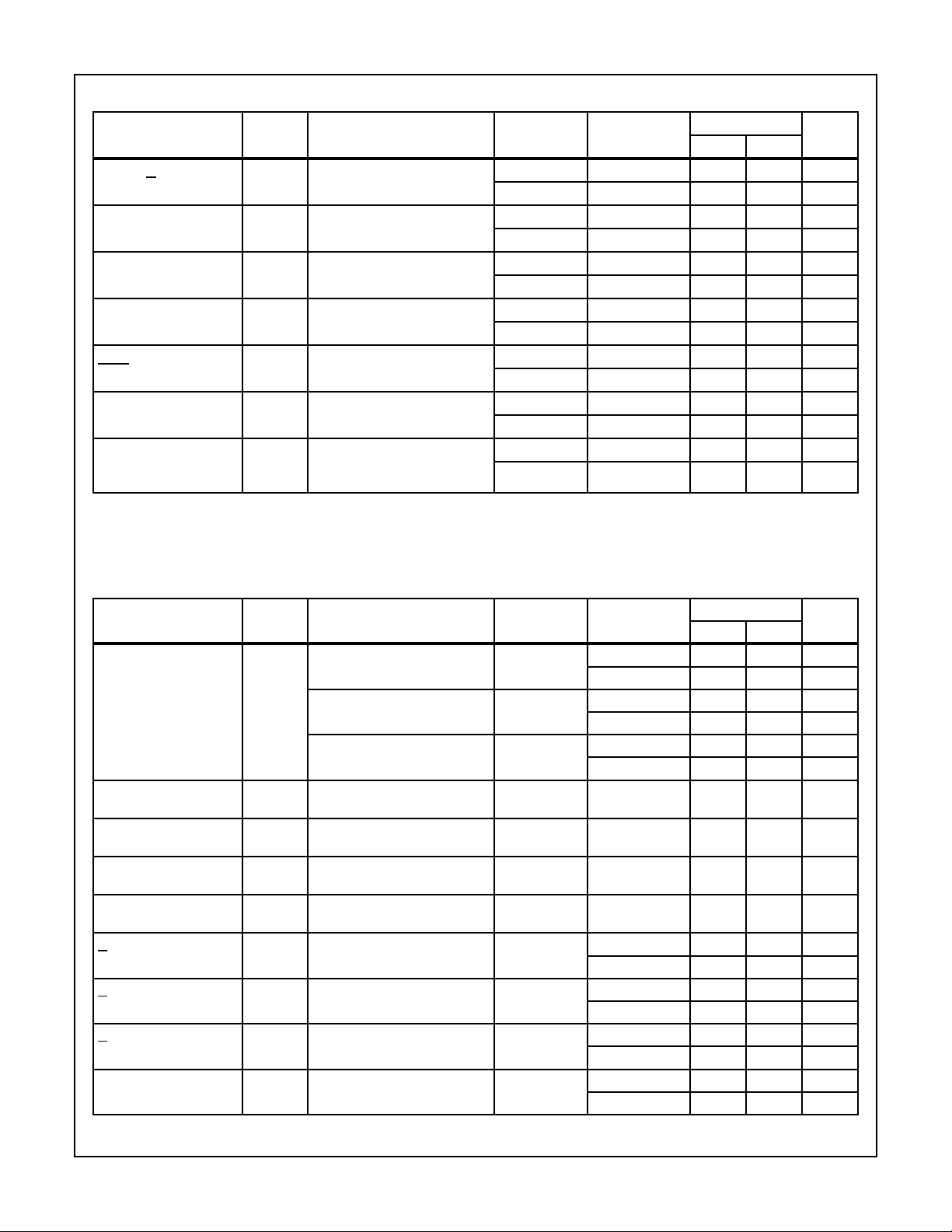

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1, 2)

Propagation Delay

Clock to Q

Propagation Delay

Clock to Q

Propagation Delay

Clock to Q

Propagation Delay

Clock to Q’

Propagation Delay

Clock to CLD

Transition Time TTHL

Maximum Clock Input

Frequency (See Note 5;

Table 3)

NOTES:

1. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

2. -55oC and +125oC limits guaranteed, 100% testing being implemented.

TPHL1

TPLH1

TPLH2 VDD = 5V, VIN = VDD or GND 9 +25oC - 500 ns

TPHL2 VDD = 5V, VIN = VDD or GND 9 +25oC - 380 ns

TPLH3

TPHL3

TPHL4

TPLH4

TTLH

FCL VDD = 5V, VIN = VDD or GND 9 +25oC 2 - MHz

VDD = 5V, VIN = VDD or GND 9 +25oC - 500 ns

VDD = 5V, VIN = VDD or GND 9 +25oC - 380 ns

VDD = 5V, VIN = VDD or GND 9 +25oC - 200 ns

VDD = 5V, VIN = VDD or GND 9 +25oC - 200 ns

GROUP A

SUBGROUPS TEMPERATURE

10, 11 +125oC, -55oC - 675 ns

10, 11 +125oC, -55oC - 675 ns

10, 11 +125oC, -55oC - 513 ns

10, 11 +125oC, -55oC - 513 ns

10, 11 +125oC, -55oC - 270 ns

10, 11 +125oC, -55oC - 270 ns

10, 11 +125oC, -55oC 1.48 - MHz

LIMITS

UNITSMIN MAX

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

LIMITS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

Supply Current IDD VDD = 5V, VIN = VDD or GND 1, 2 -55oC, +25oC- 5 µA

+125oC - 150 µA

VDD = 10V, VIN = VDD or GND 1, 2 -55oC, +25oC- 10µA

+125oC - 300 µA

VDD = 15V, VIN = VDD or GND 1, 2 -55oC, +25oC- 10µA

+125oC - 600 µA

Output Voltage VOL VDD = 5V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Voltage VOL VDD = 10V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Voltage VOH VDD = 5V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Voltage VOH VDD = 10V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Current (Sink)

Q, Q’, CLD Outputs

Output Current (Sink)

Q, Q’, CLD Outputs

Output Current (Sink)

Q, Q’, CLD Outputs

Output Current (Sink)

Q Outputs

IOL5 VDD = 5V, VOUT = 0.4V 1, 2 +125oC 0.36 - mA

-55oC 0.64 - mA

IOL10 VDD = 10V, VOUT = 0.5V 1, 2 +125oC 0.9 - mA

-55oC 1.6 - mA

IOL15 VDD = 15V, VOUT = 1.5V 1, 2 +125oC 2.4 - mA

-55oC 4.2 - mA

IOL5 VDD = 5V, VOUT = 0.4V 1, 2 +125oC 1.44 - mA

-55oC 2.56 - mA

-50mV

-50mV

4.95 - V

9.95 - V

UNITSMIN MAX

7-818

Loading...

Loading...