Intersil Corporation CD4015BMSFN3295 Datasheet

7-89

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

CD4015BMS

CMOS Dual 4-Stage Static Shift Register

With Serial Input/Parallel Output

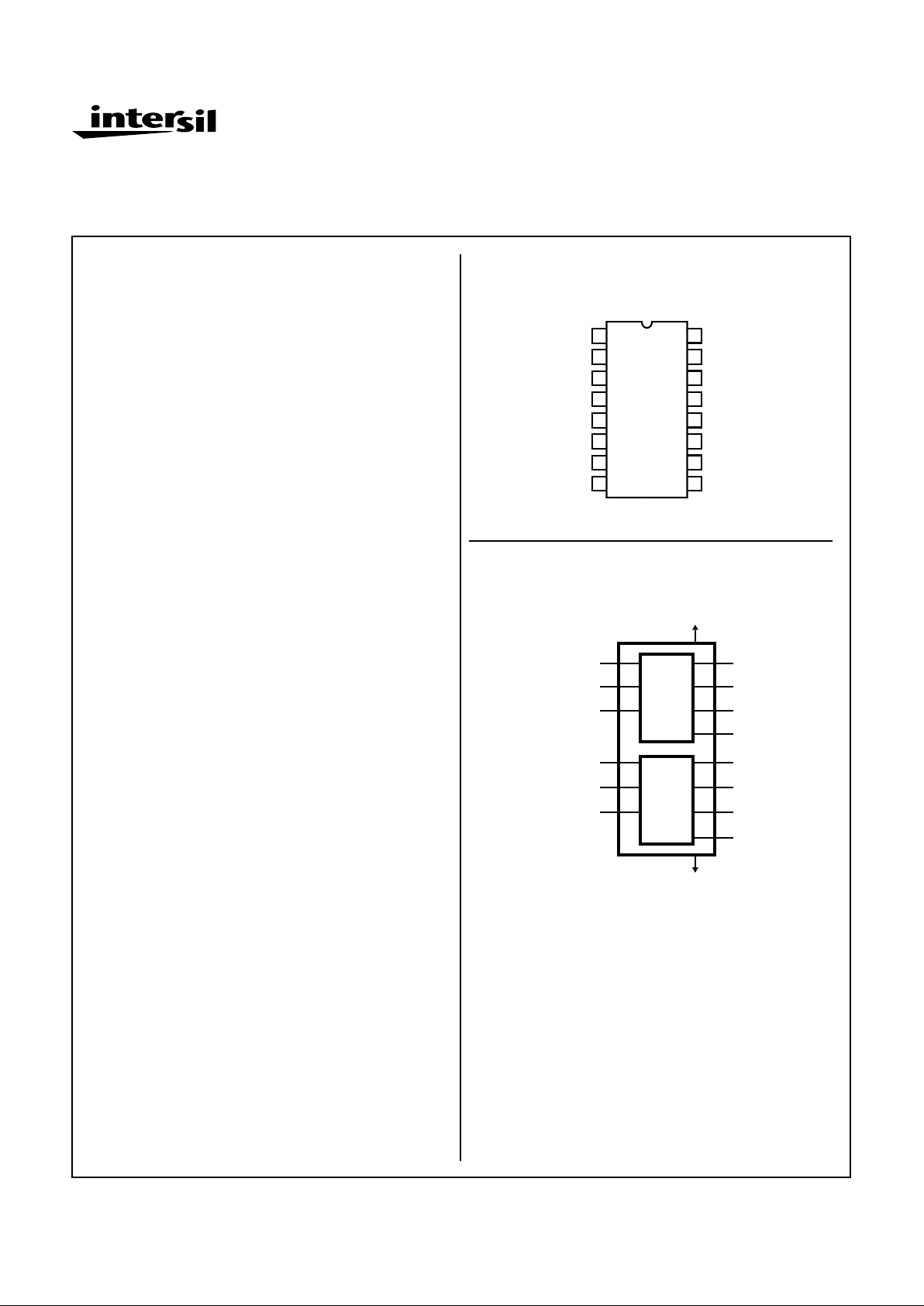

Pinout

CD4015BMS

TOP VIEW

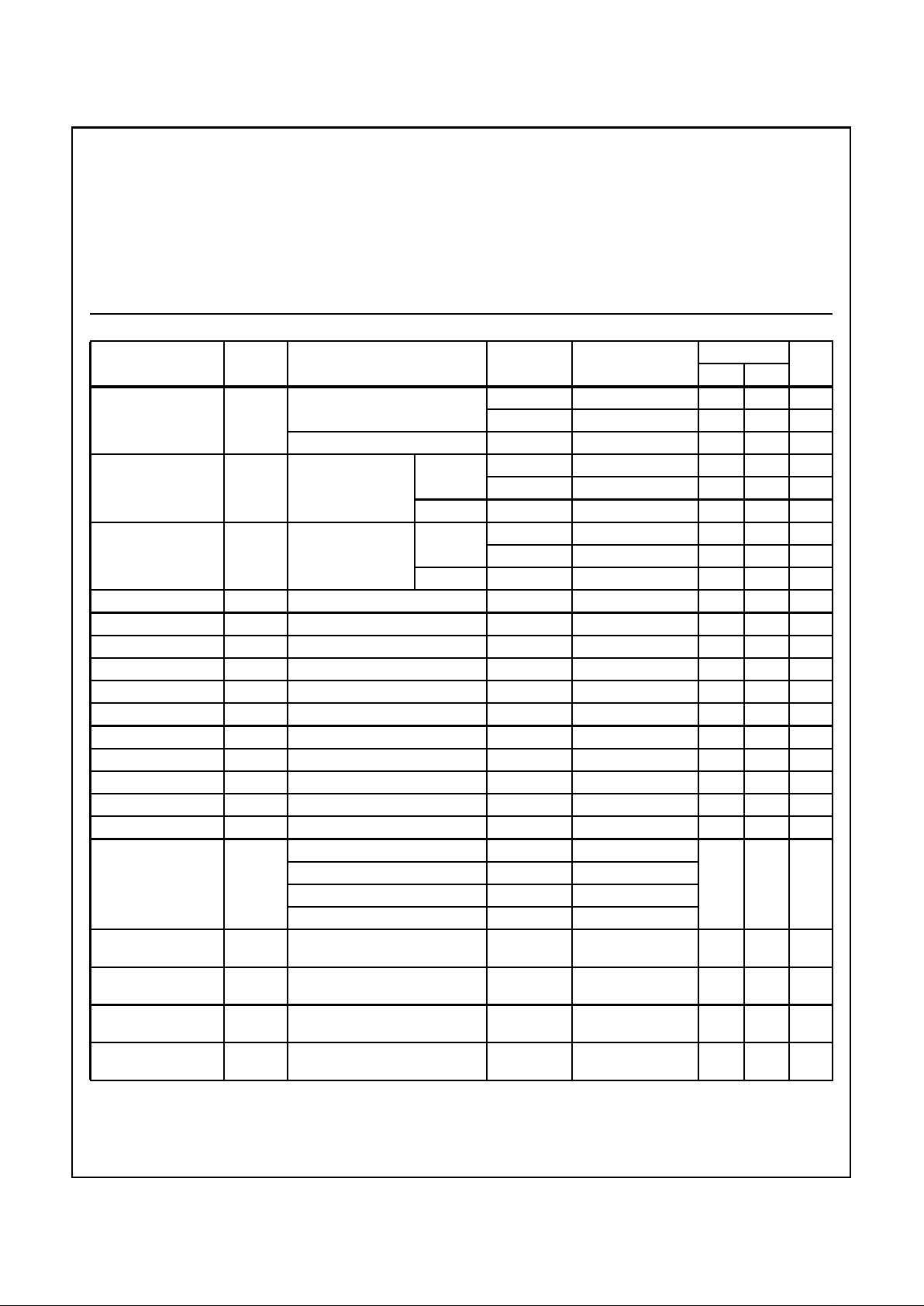

Functional Diagram

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

CLOCK B

Q4B

Q3A

Q2A

Q1A

RESET A

VSS

DATA A

VDD

RESET B

Q1B

Q2B

Q3B

Q4A

CLOCK A

DATA B

DATA A

CLOCK A

RESET A

DATA B

CLOCK B

RESET B

Q1A

Q2A

Q3A

Q4A

Q1B

Q2B

Q3B

Q4B

VSS

VDD

7

9

6

15

1

14

5

4

3

10

13

12

11

2

16

8

4

STAGE

4

STAGE

Features

• High-Voltage Type (20V Rating)

• Medium Speed Operation 12MHz (typ.) Clock Rate at

VDD - VSS = 10V

• Fully Static Operation

• 8 Master-Slave Flip-Flops Plus Input and Output Buffering

• 100% Tested For Quiescent Current at 20V

• 5V, 10V and 15V Parametric Ratings

• Standardized Symmetrical Output Characteristics

• Maximum Input Current of 1µA at 18V Over Full Package-Temperature Range; 100nA at 18V and 25

o

C

• Noise Margin (Full Package-Temperature Range) =

- 1V at VDD = 5V

- 2V at VDD = 10V

- 2.5V at VDD = 15V

• Meets All Requirements of JEDEC Tentative Standard

No. 13B, “Standard Specifications for Description of

‘B’ Series CMOS Devices”

Applications

• Serial-Input/Parallel-Output Data Queueing

• Serial to Parallel Data Conversion

• General-Purpose Register

Description

CD4015BMS consists of two identical, independent, 4-stage

serial-input/parallel output registers. Each register has independent CLOCK and RESET inputs as well as a single serial

DATA input. “Q” outputs are available from each of the four

stages on both registers. All register stages are D type, master-slave flip-flops. The logic level present at the DATA input

is transferred into the first register stage and shifted over one

stage at each positive-going clock transition. Resetting of all

stages is accomplished by a high level on the reset line.

Register expansion to 8 stages using one CD4015BMS

package, or to more than 8 stages using additional

CD4015BMS’s is possible.

The CD4015BMS is supplied in these 16 lead outline packages:

Braze Seal DIP H4X

Frit Seal DIP H1F

Ceramic Flatpack H6W

December 1992

File Number

3295

7-90

Specifications CD4015BMS

Absolute Maximum Ratings Reliability Information

DC Supply Voltage Range, (VDD) . . . . . . . . . . . . . . . -0.5V to +20V

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VDD +0.5V

DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Operating Temperature Range. . . . . . . . . . . . . . . . -55

o

C to +125oC

Package Types D, F, K, H

Storage Temperature Range (TSTG). . . . . . . . . . . -65

o

C to +150oC

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265

o

C

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for

10s Maximum

Thermal Resistance . . . . . . . . . . . . . . . . θ

ja

θ

jc

Ceramic DIP and FRIT Package. . . . . 80oC/W 20oC/W

Flatpack Package . . . . . . . . . . . . . . . . 70

o

C/W 20oC/W

Maximum Package Power Dissipation (PD) at +125oC

For TA = -55

o

C to +100oC (Package Type D, F, K). . . . . . 500mW

For TA = +100

o

C to +125oC (Package Type D, F, K) . . . . .Derate

Linearity at 12mW/oC to 200mW

Device Dissipation per Output Transistor . . . . . . . . . . . . . . . 100mW

For TA = Full Package Temperature Range (All Package Types)

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

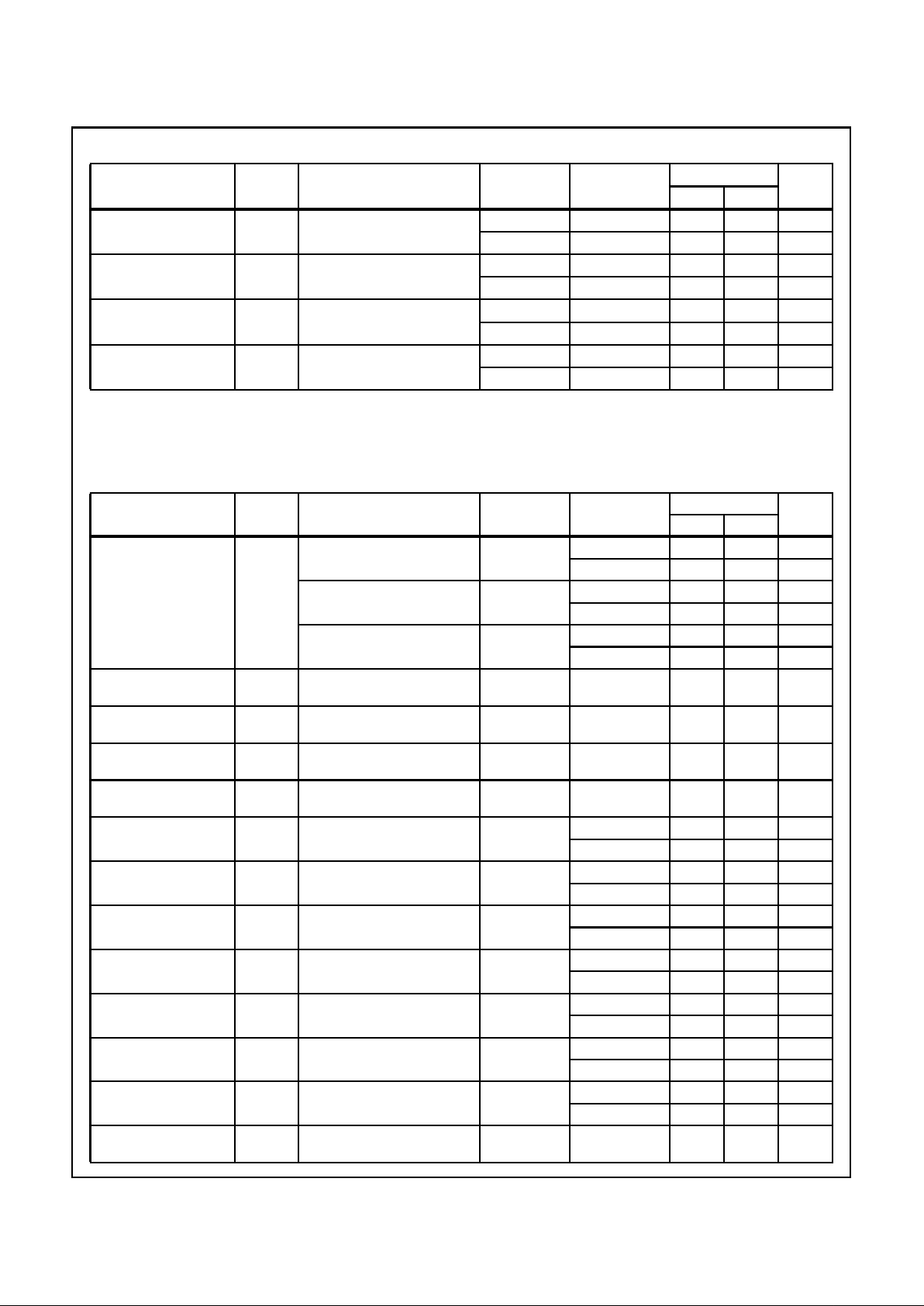

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1)

GROUP A

SUBGROUPS TEMPERATURE

LIMITS

UNITSMIN MAX

Supply Current IDD VDD = 20V, VIN = VDD or GND 1 +25

o

C-10µA

2 +125oC - 1000 µA

VDD = 18V, VIN = VDD or GND 3 -55oC-10µA

Input Leakage Current IIL VIN = VDD or GND VDD = 20 1 +25

o

C -100 - nA

2 +125oC -1000 - nA

VDD = 18V 3 -55oC -100 - nA

Input Leakage Current IIH VIN = VDD or GND VDD = 20 1 +25oC - 100 nA

2 +125oC - 1000 nA

VDD = 18V 3 -55oC - 100 nA

Output Voltage VOL15 VDD = 15V, No Load 1, 2, 3 +25oC, +125oC, -55oC - 50 mV

Output Voltage VOH15 VDD = 15V, No Load (Note 3) 1, 2, 3 +25oC, +125oC, -55oC 14.95 - V

Output Current (Sink) IOL5 VDD = 5V, VOUT = 0.4V 1 +25oC 0.53 - mA

Output Current (Sink) IOL10 VDD = 10V, VOUT = 0.5V 1 +25oC 1.4 - mA

Output Current (Sink) IOL15 VDD = 15V, VOUT = 1.5V 1 +25oC 3.5 - mA

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1 +25oC - -0.53 mA

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1 +25oC - -1.8 mA

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1 +25oC - -1.4 mA

Output Current (Source) IOH15 VDD = 15V, VOUT = 13.5V 1 +25oC - -3.5 mA

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1 +25oC -2.8 -0.7 V

P Threshold Voltage VPTH VSS = 0V, IDD = 10µA 1 +25oC 0.7 2.8 V

Functional F VDD = 2.8V, VIN = VDD or GND 7 +25oC VOH >

VDD/2

VOL <

VDD/2

V

VDD = 20V, VIN = VDD or GND 7 +25oC

VDD = 18V, VIN = VDD or GND 8A +125oC

VDD = 3V, VIN = VDD or GND 8B -55oC

Input Voltage Low

(Note 2)

VIL VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25oC, +125oC, -55oC - 1.5 V

Input Voltage High

(Note 2)

VIH VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25oC, +125oC, -55oC 3.5 - V

Input Voltage Low

(Note 2)

VIL VDD = 15V, VOH > 13.5V,

VOL < 1.5V

1, 2, 3 +25oC, +125oC, -55oC- 4 V

Input Voltage High

(Note 2)

VIH VDD = 15V, VOH > 13.5V,

VOL < 1.5V

1, 2, 3 +25oC, +125oC, -55oC11 - V

NOTES: 1. All voltages referenced to device GND, 100% testing being

implemented.

2. Go/No Go test with limits applied to inputs

3. For accuracy, voltage is measured differentially to VDD. Limit

is 0.050V max.

7-91

Specifications CD4015BMS

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1, 2)

GROUP A

SUBGROUPS TEMPERATURE

LIMITS

UNITSMIN MAX

Propagation Delay

Clock To Q

TPHL1

TPLH1

VDD = 5V, VIN = VDD or GND 9 +25oC - 320 ns

10, 11 +125oC, -55oC - 432 ns

Propagation Delay

Reset To Q

TPHL2 VDD = 5V, VIN = VDD or GND 9 +25oC - 400 ns

10, 11 +125oC, -55oC - 540 ns

Transition Time TTHL

TTLH

VDD = 5V, VIN = VDD or GND 9 +25oC - 200 ns

10, 11 +125oC, -55oC - 270 ns

Maximum Clock Input

Frequency

FCL VDD = 5V, VIN = VDD or GND 9 +25oC 3 - MHz

10, 11 +125oC, -55oC 3/1.35 - MHz

NOTES:

1. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

2. -55oC and +125oC limits guaranteed, 100% testing being implemented.

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

LIMITS

UNITSMIN MAX

Supply Current IDD VDD = 5V, VIN = VDD or GND 1, 2 -55oC, +25oC- 5 µA

+125oC - 150 µA

VDD = 10V, VIN = VDD or GND 1, 2 -55oC, +25oC- 10µA

+125oC - 300 µA

VDD = 15V, VIN = VDD or GND 1, 2 -55oC, +25oC- 10µA

+125oC - 600 µA

Output Voltage VOL VDD = 5V, No Load 1, 2 +25oC, +125oC,

-55oC

-50mV

Output Voltage VOL VDD = 10V, No Load 1, 2 +25oC, +125oC,

-55oC

-50mV

Output Voltage VOH VDD = 5V, No Load 1, 2 +25oC, +125oC,

-55oC

4.95 - V

Output Voltage VOH VDD = 10V, No Load 1, 2 +25oC, +125oC,

-55oC

9.95 - V

Output Current (Sink) IOL5 VDD = 5V, VOUT = 0.4V 1, 2 +125oC 0.36 - mA

-55oC 0.64 - mA

Output Current (Sink) IOL10 VDD = 10V, VOUT = 0.5V 1, 2 +125oC 0.9 - mA

-55oC 1.6 - mA

Output Current (Sink) IOL15 VDD = 15V, VOUT = 1.5V 1, 2 +125oC 2.4 - mA

-55oC 4.2 - mA

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1, 2 +125oC - -0.36 mA

-55oC - -0.64 mA

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1, 2 +125oC - -1.15 mA

-55oC - -2.0 mA

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1, 2 +125oC - -0.9 mA

-55oC - -1.6 mA

Output Current (Source) IOH15 VDD =15V, VOUT = 13.5V 1, 2 +125oC - -2.4 mA

-55oC - -4.2 mA

Input Voltage Low VIL VDD = 10V, VOH > 9V , VOL < 1V 1, 2 +25oC, +125oC,

-55oC

-3V

Loading...

Loading...