Intersil Corporation CD40103BMS, CD40102BMS Datasheet

December 1992

CD40102BMS

CD40103BMS

CMOS 8-Stage Presettable

Synchronous Down Counters

Features

• High Voltage Type (20V Rating)

• CD40102BMS: 2-Decade BCD Type

• CD40103BMS: 8-Bit Binary Type

• Synchronous or Asynchronous Preset

• Medium Speed Operation

- fCL = 3.6MHz (Typ) at 10V

• Cascadable

• 100% Tested for Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full Pack-

age Temperature Range; 100nA at 18V and +25

• Noise Margin (Over Full Package/Temperature Range)

- 1V at VDD = 5V

- 2V at VDD = 10V

- 2.5V at VDD = 15V

• Standardized Symmetrical Output Characteristics

• 5V, 10V and 15V Parametric Ratings

• Meets All Requirements of JEDEC Tentative Standard

No. 13B, “Standard Specifications for Description of

‘B’ Series CMOS Devices”

o

C

Description

CD40102BMS and CD40103BMS consist of an 8-stage synchronous down counter with a single output which is active

when the internal count is zero. The CD40102BMS is configured as two cascaded 4-bit BCD counters, and the

CD40103BMS contains a single 8-bit binary counter. Each

type has control inputs for enabling or disabling the clock, for

clearing the counter to its maximum count, and for presetting

the counter either synchronously or asynchronously. All control inputs and the CARRY-OUT/ZERO-DETECT output are

active-low logic.

In normal operation, the counter is decremented by one

count on each positive transition of the CLOCK. Counting is

inhibited when the CARRY-IN/COUNTER ENABLE (

inputs is high. The CARRY-OUT/ZERO-DETECT (

output goes low when the count reaches zero if the

input is low, and remains low for one full clock period.

When the SYNCHRONOUS PRESET-ENABLE (

is low, data at the JAM input is clocked into the counter on

the next positive clock transition regardless of the state of

the

CI/CE input. When the ASYNCHRONOUS PRESET-

ENABLE (

APE) input is low, data at the JAM inputs is asynchronously forced into the counter regardless of the state of

the

SPE, CI/CE, or CLOCK inputs. JAM inputs J0-J7 represent two 4-bit BCD words for the CD40102BMS and a single

8-bit binary word for the CD40103BMS.

CI/CE)

CO/ZD)

CI/CE

SPE) input

Applications

• Divide-By- “N” Counters

• Programmable Times

• Interrupt Timers

• Cycle/Program Counter

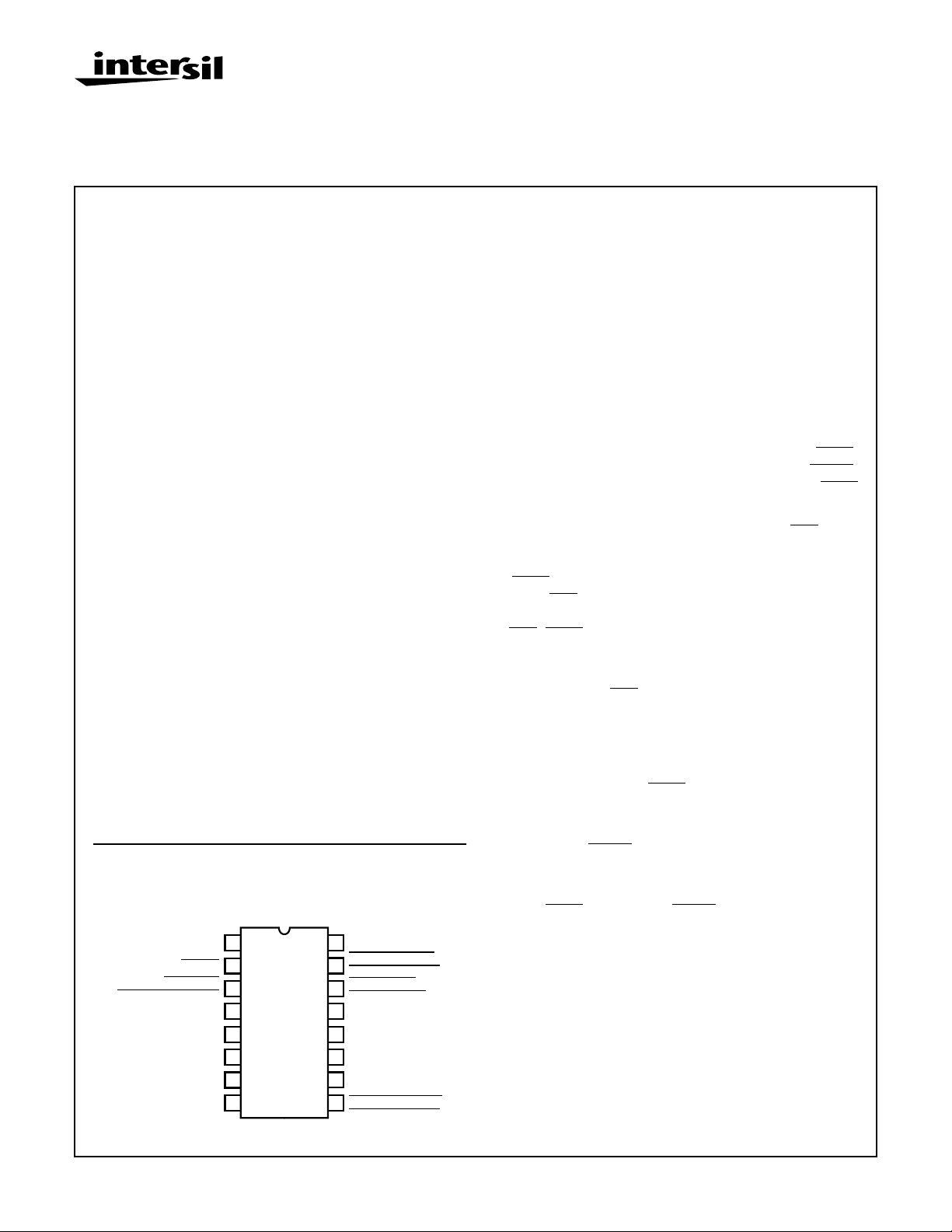

Pinout

CD40102BMS, CD40130BMS

TOP VIEW

VSS

1

2

3

4

J0

5

J1

6

J2

7

J3

8

CLOCK

CLEAR

CARRY IN/

COUNTER ENABLE

16

VDD

SYNCHRONOUS

15

PRESET ENABLE

CARRY OUT/

14

ZERO DETECT

J7

13

J6

12

J5

11

J4

10

9

ASYNCHRONOUS

PRESET ENABLE

When the CLEAR (

chronously cleared to its maximum count (99

CD40102BMS and 255

CLR) input is low, the counter is asyn-

for the

for the CD40103BMS) regardless

10

10

of the state of any other input. The precedence relationship

between control inputs is indicated in the truth table.

If all control inputs except

CI/CE are high at the time of zero

count, the counters will jump to the maximum count, giving a

counting sequence of 100 or 256 clock pulses long.

This causes the

CO/ZD output to go low to enable the clock

on each succeeding clock pulse.

The CD40102BMS and CD40103BMS may be cascaded

using the

CI/CE input and the CO/ZD output, in either a syn-

chronous or ripple mode as shown in Figures 16 and 17.

The CD40102MS and CD40103BMS are supplied in these

16-lead outline packages:

Braze Seal DIP *H4W †H4X

Frit Seal DIP *H1L †H1F

Ceramic Flatpack H6W

*CD40102B Only †CD40130B Only

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

7-1294

File Number 3351

Specifications CD40102BMS, CD40103BMS

Absolute Maximum Ratings Reliability Information

DC Supply Voltage Range, (VDD) . . . . . . . . . . . . . . . -0.5V to +20V

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . . . . . . . . . . .-0.5V to VDD +0.5V

DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . . . .±10mA

Operating Temperature Range. . . . . . . . . . . . . . . . -55oC to +125oC

Package Types D, F, K, H

Storage Temperature Range (TSTG). . . . . . . . . . . -65oC to +150oC

Lead Temperature (During Soldering) . . . . . . . . . . . . . . . . . +265oC

At Distance 1/16 ± 1/32 Inch (1.59mm ± 0.79mm) from case for

10s Maximum

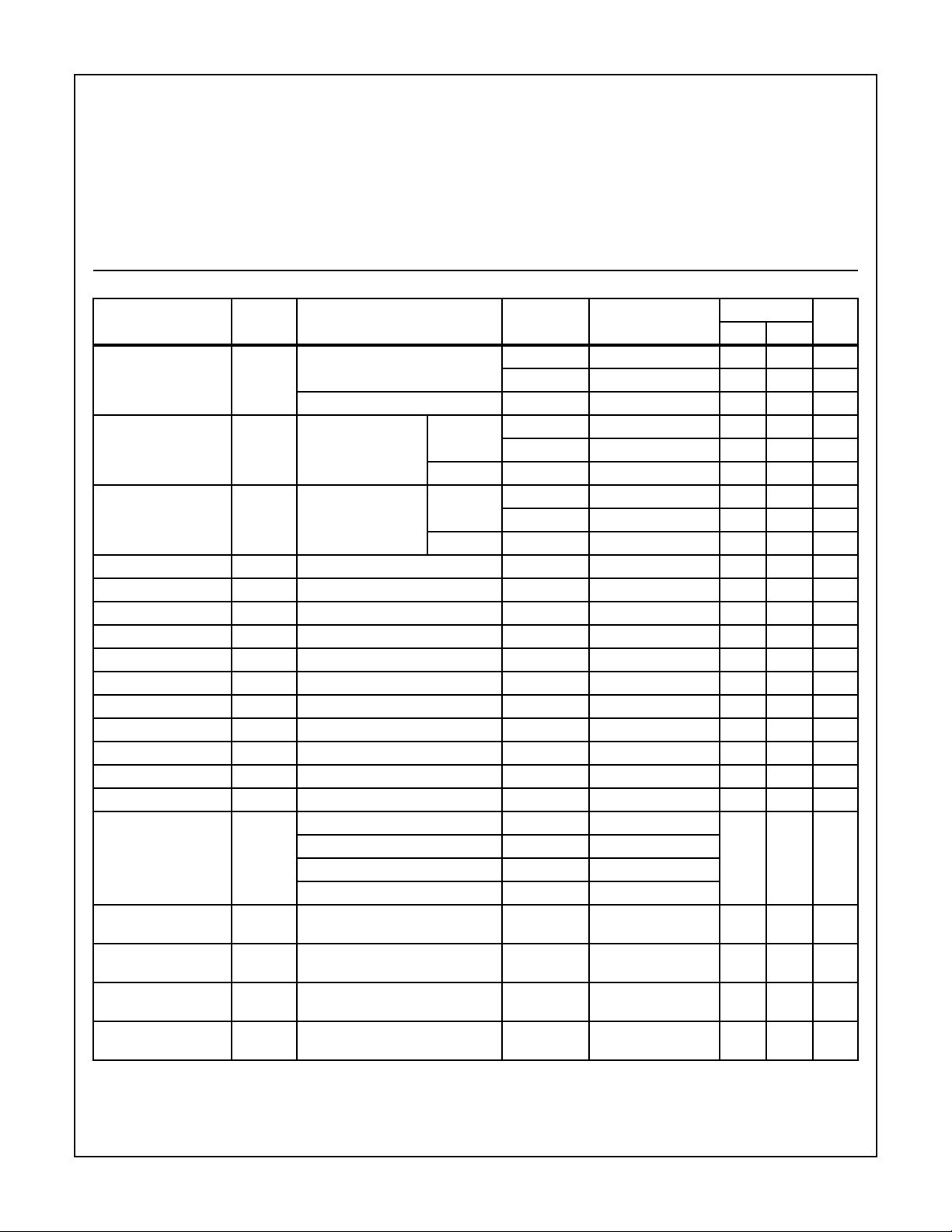

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1)

Supply Current IDD VDD = 20V, VIN = VDD or GND 1 +25oC-10µA

VDD = 18V, VIN = VDD or GND 3 -55oC-10µA

Input Leakage Current IIL VIN = VDD or GND VDD = 20V 1 +25oC -100 - nA

VDD = 18V 3 -55oC -100 - nA

Input Leakage Current IIH VIN = VDD or GND VDD = 20V 1 +25oC - 100 nA

VDD = 18V 3 -55oC - 100 nA

Output Voltage VOL15 VDD = 15V, No Load 1, 2, 3 +25oC, +125oC, -55oC - 50 mV

Output Voltage VOH15 VDD = 15V, No Load (Note 3) 1, 2, 3 +25oC, +125oC, -55oC 14.95 - V

Output Current (Sink) IOL5 VDD = 5V, VOUT = 0.4V 1 +25oC 0.53 - mA

Output Current (Sink) IOL10 VDD = 10V, VOUT = 0.5V 1 +25oC 1.4 - mA

Output Current (Sink) IOL15 VDD = 15V, VOUT = 1.5V 1 +25oC 3.5 - mA

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1 +25oC - -0.53 mA

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1 +25oC - -1.8 mA

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1 +25oC - -1.4 mA

Output Current (Source) IOH15 VDD = 15V, VOUT = 13.5V 1 +25oC - -3.5 mA

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1 +25oC -2.8 -0.7 V

P Threshold Voltage VPTH VSS = 0V, IDD = 10µA 1 +25oC 0.7 2.8 V

Functional F VDD = 2.8V, VIN = VDD or GND 7 +25oC VOH >

VDD = 20V, VIN = VDD or GND 7 +25oC

VDD = 18V, VIN = VDD or GND 8A +125oC

VDD = 3V, VIN = VDD or GND 8B -55oC

Input Voltage Low

(Note 2)

Input Voltage High

(Note 2)

Input Voltage Low

(Note 2)

Input Voltage High

(Note 2)

NOTES: 1. All voltages referenced to device GND, 100% testing being

implemented.

2. Go/No Go test with limits applied to inputs.

VIL VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25oC, +125oC, -55oC - 1.5 V

VIH VDD = 5V, VOH > 4.5V, VOL < 0.5V 1, 2, 3 +25oC, +125oC, -55oC 3.5 - V

VIL VDD = 15V, VOH > 13.5V,

VOL < 1.5V

VIH VDD = 15V, VOH > 13.5V,

VOL < 1.5V

Thermal Resistance θ

Ceramic DIP Package. . . . . . . . . . . . . 80oC/W 20oC/W

Flatpack Package . . . . . . . . . . . . . . . . 70oC/W 20oC/W

Maximum Package Power Dissipation (PD) at +125oC

For TA = -55oC to +100oC (Package Type D, F, K) . . . . . . 500mW

For TA = +100oC to +125oC (Package Type D, F, K). . . . . .Derate

Linearity at 12mW/oC to 200mW

Device Dissipation per Output Transistor . . . . . . . . . . . . . . . 100mW

For TA = Full Package Temperature Range (All Package Types)

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +175oC

GROUP A

SUBGROUPS TEMPERATURE

2 +125oC - 1000 µA

2 +125oC -1000 - nA

2 +125oC - 1000 nA

1, 2, 3 +25oC, +125oC, -55oC- 4 V

1, 2, 3 +25oC, +125oC, -55oC11 - V

3. For accuracy, voltage is measured differentially to VDD. Limit

is 0.050V max.

ja

LIMITS

VDD/2

VOL <

VDD/2

θ

jc

UNITSMIN MAX

V

7-1295

Specifications CD40102BMS, CD40103BMS

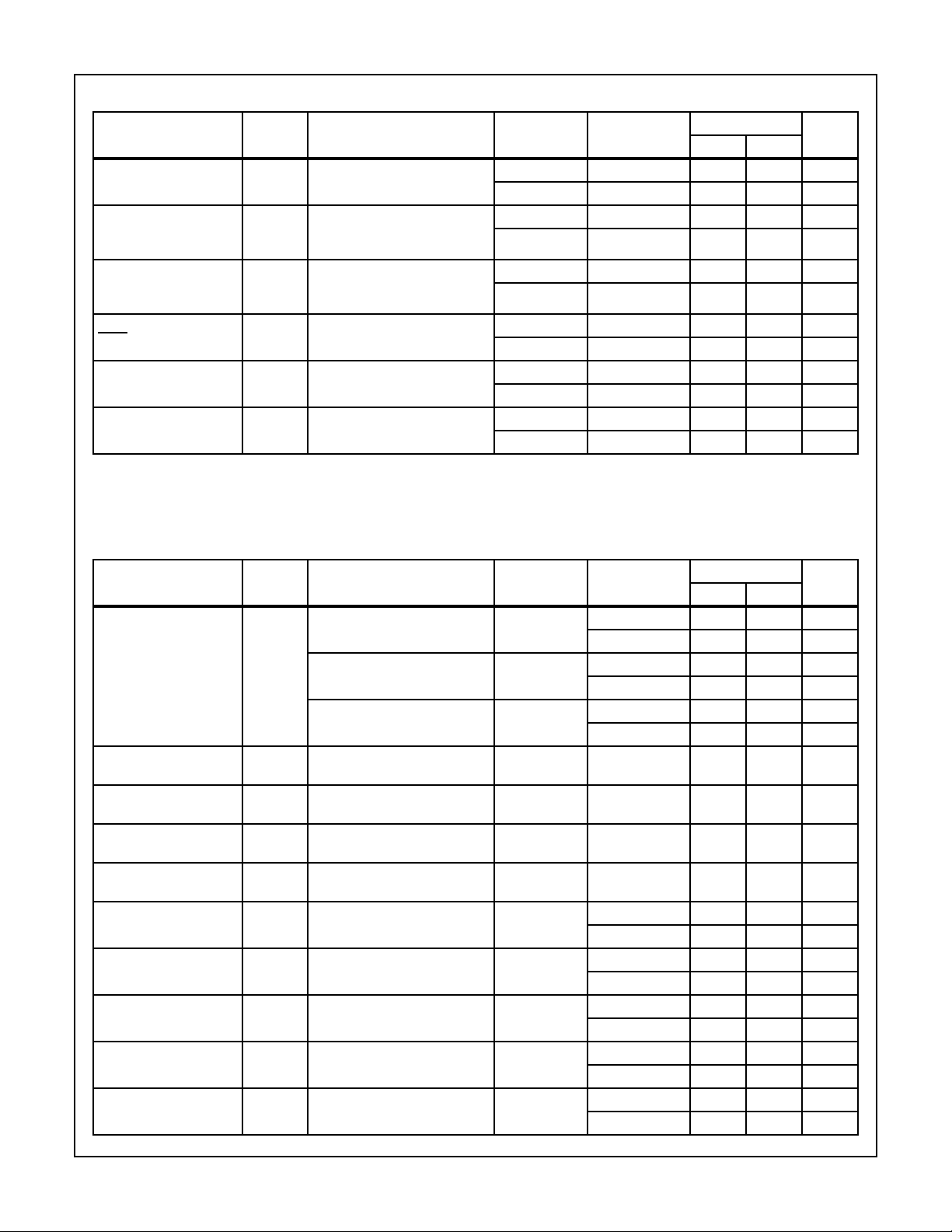

TABLE 2. AC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS (NOTE 1, 2)

Propagation Delay

Clock to Output

Propagation Delay

Carry In/Counter Enable

to Output

Propagation Delay

Asynchronous Preset

Enable to Output

Propagation Delay

Clear to Output

Transition Time TTHL

Maximum Clock Input

Frequency

NOTES:

1. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

2. -55oC and +125oC limits guaranteed, 100% testing being implemented.

TPHL1

TPLH1

TPHL2

TPLH2

TPHL3

TPLH3

TPLH4 VDD = 5V, VIN = VDD or GND 9 +25oC - 750 ns

TTLH

FCL VDD = 5V, VIN = VDD or GND 9 +25oC .7 - MHz

VDD = 5V, VIN = VDD or GND 9 +25oC - 600 ns

VDD = 5V, VIN = VDD or GND 9 +25oC - 400 ns

VDD = 5V, VIN = VDD or GND 9 +25oC - 1300 ns

VDD = 5V, VIN = VDD or GND 9 +25oC - 200 ns

GROUP A

SUBGROUPS TEMPERATURE

10, 11 +125oC, -55oC - 810 ns

10, 11 +125oC, -55oC - 540 ns

10, 11 +125oC, -55oC - 1755 ns

10, 11 +125oC, -55oC - 1012 ns

10, 11 +125oC, -55oC - 270 ns

10, 11 +125oC, -55oC .52 - MHz

LIMITS

UNITSMIN MAX

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

LIMITS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

Supply Current IDD VDD = 5V, VIN = VDD or GND 1, 2 -55oC, +25oC- 5 µA

+125oC - 150 µA

VDD = 10V, VIN = VDD or GND 1, 2 -55oC, +25oC- 10µA

+125oC - 300 µA

VDD = 15V, VIN = VDD or GND 1, 2 -55oC, +25oC- 10µA

+125oC - 600 µA

Output Voltage VOL VDD = 5V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Voltage VOL VDD = 10V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Voltage VOH VDD = 5V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Voltage VOH VDD = 10V, No Load 1, 2 +25oC, +125oC,

-55oC

Output Current (Sink) IOL5 VDD = 5V, VOUT = 0.4V 1, 2 +125oC 0.36 - mA

-55oC 0.64 - mA

Output Current (Sink) IOL10 VDD = 10V, VOUT = 0.5V 1, 2 +125oC 0.9 - mA

-55oC 1.6 - mA

Output Current (Sink) IOL15 VDD = 15V, VOUT = 1.5V 1, 2 +125oC 2.4 - mA

-55oC 4.2 - mA

Output Current (Source) IOH5A VDD = 5V, VOUT = 4.6V 1, 2 +125oC - -0.36 mA

-55oC - -0.64 mA

Output Current (Source) IOH5B VDD = 5V, VOUT = 2.5V 1, 2 +125oC - -1.15 mA

-55oC - -2.0 mA

-50mV

-50mV

4.95 - V

9.95 - V

UNITSMIN MAX

7-1296

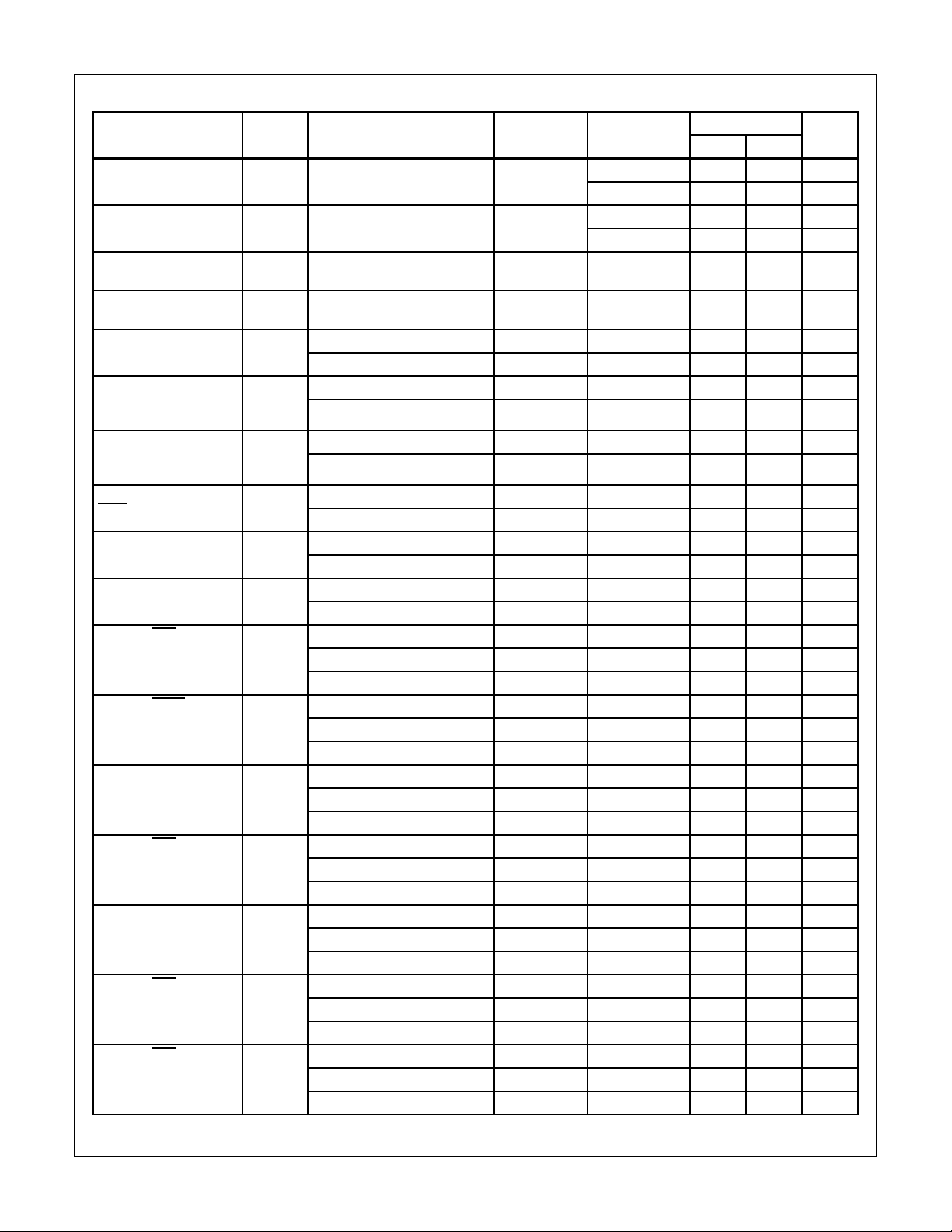

Specifications CD40102BMS, CD40103BMS

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS (Continued)

LIMITS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

Output Current (Source) IOH10 VDD = 10V, VOUT = 9.5V 1, 2 +125oC - -0.9 mA

-55oC - -1.6 mA

Output Current (Source) IOH15 VDD =15V, VOUT = 13.5V 1, 2 +125oC - -2.4 mA

-55oC - -4.2 mA

Input Voltage Low VIL VDD = 10V , VOH > 9V, VOL < 1V 1, 2 +25oC, +125oC,

-55oC

Input Voltage High VIH VDD = 10V , VOH > 9V, VOL < 1V 1, 2 +25oC, +125oC,

-55oC

Propagation Delay

Clock to Output

Propagation Delay

Carry In/Counter Enable

to Output

Propagation Delay

Asynchronous Preset Enable to Output

Propagation Delay

Clear to Output

Transition Time TTHL1

Maximum Clock Input

Frequency

Minimum SPE Setup

Time

Minimum CI/CE Setup

Time

Minimum Clock Pulse

Width

Minimum APE Pulse

Width

Minimum JAM Setup

Time (Synchronous Presetting)

Minimum APE Removal

Time

Minimum CLR Pulse

Width

TPHL1

TPLH1

TPHL2

TPLH2

TPHL3

TPLH3

TPLH4 VDD = 10V 1, 2, 3 +25oC - 360 ns

TTLH1

FCL VDD = 10V 1, 2 +25oC 1.8 - MHz

TSU VDD = 5V 1, 2, 3 +25oC - 280 ns

TSU VDD = 5V 1, 2, 3 +25oC - 500 ns

TW VDD = 5V 1, 2, 3 +25oC - 300 ns

TW VDD = 5V 1, 2, 3 +25oC - 360 ns

TSU VDD = 5V 1, 2, 3 +25oC - 200 ns

TREM VDD = 5V 1, 2, 3 +25oC - 220 ns

TW VDD = 5V 1, 2, 3 +25oC - 320 ns

VDD = 10V 1, 2, 3 +25oC - 260 ns

VDD = 15V 1, 2, 3 +25oC - 190 ns

VDD = 10V 1, 2, 3 +25oC - 180 ns

VDD = 15V 1, 2, 3 +25oC - 130 ns

VDD = 10V 1, 2, 3 +25oC - 600 ns

VDD = 15V 1, 2, 3 +25oC - 400 ns

VDD = 15V 1, 2, 3 +25oC - 200 ns

VDD = 10V 1, 2, 3 +25oC - 100 ns

VDD = 15V 1, 2, 3 +25oC - 80 ns

VDD = 15V 1, 2 +25oC 2.4 - MHz

VDD = 10V 1, 2, 3 +25oC - 140 ns

VDD = 15V 1, 2, 3 +25oC - 100 ns

VDD = 10V 1, 2, 3 +25oC - 250 ns

VDD = 15V 1, 2, 3 +25oC - 150 ns

VDD = 10V 1, 2, 3 +25oC - 180 ns

VDD = 15V 1, 2, 3 +25oC - 80 ns

VDD = 10V 1, 2, 3 +25oC - 160 ns

VDD = 15V 1, 2, 3 +25oC - 120 ns

VDD = 10V 1, 2, 3 +25oC - 80 ns

VDD = 15V 1, 2, 3 +25oC - 60 ns

VDD = 10V 1, 2, 3 +25oC - 100 ns

VDD = 15V 1, 2, 3 +25oC - 70 ns

VDD = 10V 1, 2, 3 +25oC - 160 ns

VDD = 15V 1, 2, 3 +25oC - 100 ns

-3V

7-V

UNITSMIN MAX

7-1297

Loading...

Loading...