Intersil Corporation CD22357A, CD22354A Datasheet

Semiconductor

CD22354A,

[ /Title

(CD22

354A,

CD223

57A)

/Subject

(CMO

S SingleChip,

FullFeature

PCM

CODE

C)

/

Author

()

/Keywords

(Harris

Semiconductor,

RSLIC

18,

Telecom,

SLICs,

SLACs

, Telephone,

Telephony,

WLL,

Wireless

Local

Loop,

OBSOLETE PRODUCT

NO RECOMMENDED REPLACEMENT

February 1999

Call Central Applications 1-800-442-7747

or email: centapp@harris.com

Features

• Meets or Exceeds All AT&T D3/D4 Specifications and CCITT

Recommendations

• Complete CODEC and Filtering Systems: No External Components

for Sample-and-Hold and Auto-Zero Functions. Receive Output Filter with (SIN X)/X Correction and Additional 8kHz Suppression

• Variable Data Clocks - From 64kHz. . . . . . . . . . . . . . . . . . . . . 2.1MHz

• Receiver Includes Power-Up Click Filter

• TTL or CMOS-Compatible Logic

• ESD Protection on All Inputs and Outputs

Applications

• PABX

• Central Office Switching Systems

• Accurate A/D and D/A Conversions

• Digital Telephones

• Cellular Telephone Switching Systems

• Voice Scramblers - Descramblers

• T1 Conference Bridges

• Voice Storage and Retrieval Systems

• Sound Based Security Systems

• Computerized Voice Analysis

• Mobile Radio Telephone Systems

• Microwave Telephone Networks

• Fiber-Optic Telephone Networks

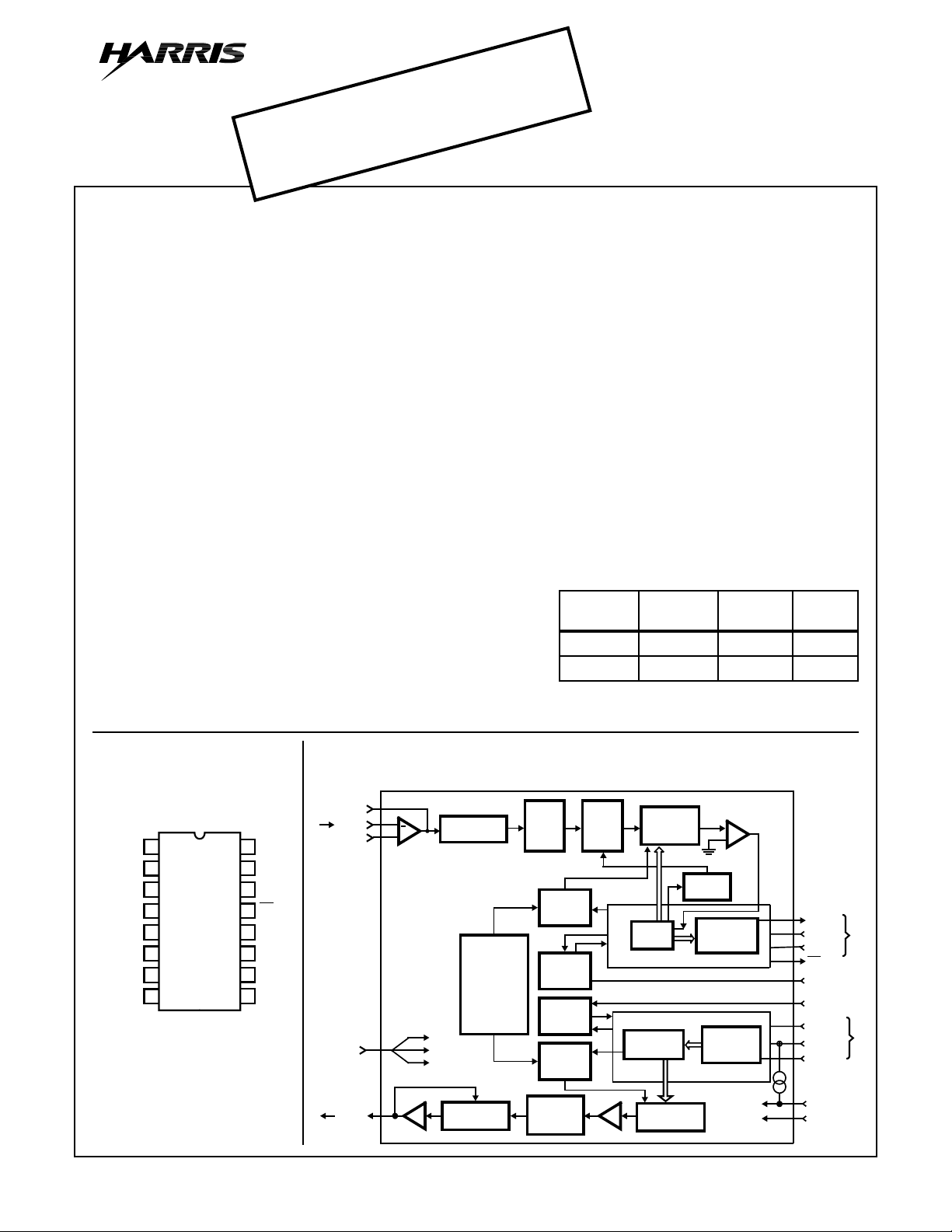

Pinout

CD22354A, CD22357A

TOP VIEW

V-

1

2

GND

3

VF

O

R

4

V+

5

FS

R

D

6

R

BCLKR/

CLKSEL

MCLK

PDN

7

8

/

R

(PDIP)

16

15

14

13

12

11

10

9

VFX1+

VF

GS

TS

FS

D

BCLK

MCLK

Functional Block Diagram

14

GS

X

15

1-

VF

X

VF

FROM SLICTO SLIC

1-

X

X

X

X

X

X

X

GND

16

1+

X

2

3

O

VF

R

+

ANTI-ALLAS

SMOOTHING

FILTER

BAND

GAP

REFERENCE

FILTER

CD22357A

Full-Feature PCM CODEC

Description

The CD22354A and CD22357A are monolithic silicongate, double-poly CMOS integrated circuits containing

the band-limiting filters and the companding A/D and D/A

conversion circuits that conform to the AT&T D3/D4

specifications and CCITT recommendations. The

CD22354A provides the AT&T µ-law and the CD22357A

provides the CCITT A-law companding characteristic.

The primary applications for the CD22354A and

CD22357A are in telephone systems. These circuits

perform the analog and digital conversions between the

subscriber loop and the PCM highway in a digital

switching system. The functional block diagram is

shown below .

With flexible features, including synchronous and

asynchronous operations and variable data rates, the

CD22354A and CD22357A are ideally suited for PABX,

central office switching system, digital telephones as

well as other applications that require accurate A/D and

D/A conversions and minimal conv ersion time.

Ordering Information

PART

NUMBER

CD22354AE -40 to 80 16 Ld PDIP E16.3

CD22357AE -40 to 80 16 Ld PDIP E16.3

FULL-FEATURE PCM CODEC

XMIT

LOW

PASS

FILTER

RECEIVE

LOW PASS

FILTER

XMIT

V

REF

XMIT

CLOCK

CIRCUIT

R

CV

CLOCK

CIRCUIT

R

CV

V

REF

XMIT

HIGH

PASS

FILTER

TEMP .

RANGE (oC) PACKAGE PKG. NO.

TRANSMIT

D/A

LADDER

S.A.R.

XMIT DIGITAL

D/A

REGISTER

RECEIVE

D/A LADDER

CMOS Single-Chip,

COMPARATOR

SIGN

BIT INT.

11

D

PARALLEL

TO

SERIAL

SERIAL

TO

PARALLEL

RCV DIGITAL

+5V

-5V

X

10

BCLK

FS

X

TS

X

MCLK

MCLKR/

PDN

FS

R

BCLKR/

CLKSEL

D

R

V+

V-

X

DDIGITAL OUT

X

12

13

9

8

5

7

6

4

1

DDIGITAL IN

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1999

4-165

File Number 1682.4

CD22354A, CD22357A

Absolute Maximum Ratings Thermal Information

DC Supply-Voltage, (V+) . . . . . . . . . . . . . . . . . . . . . . . . . .-0.5 to 7V

DC Supply-Voltage, (V-) . . . . . . . . . . . . . . . . . . . . . . . . . . .0.5 to -7V

DC Input Diode Current,

IIK (VI < V- -0.5V or VI > V+ 0.5V) . . . . . . . . . . . . . . . . . . . . . . . .±20mA

DC Output Diode Current,

IOK (VI < V- -0.5V or VO > V+ 0.5V). . . . . . . . . . . . . . . . . . . . . . .±20mA

DC Drain Current, Per Output

IO (V- -0.5V < VO < V+ 0.5V) . . . . . . . . . . . . . . . . . . . . . . . . . . . .±25mA

DC Supply/Ground Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . .±50mA

Power Dissipation Per Package (PD):

For TA = -40oC to 60oC. . . . . . . . . . . . . . . . . . . . . . . . . . . 500mW

For TA = 60oC to 85oC . . . . . . . . . . . . Derate Linearly at 8mW/oC

to 300mW

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Maximum Junction Temperature. . . . . . . . . . . . . . . . . . . . . . . 175oC

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150oC

Maximum Storage Temperature Range (T

). . . . .-65oC to 150oC

STG

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300oC

Operating Conditions

Operating-Temperature Range (TA) . . . . . . . . . . . . . .-40oC to 80oC

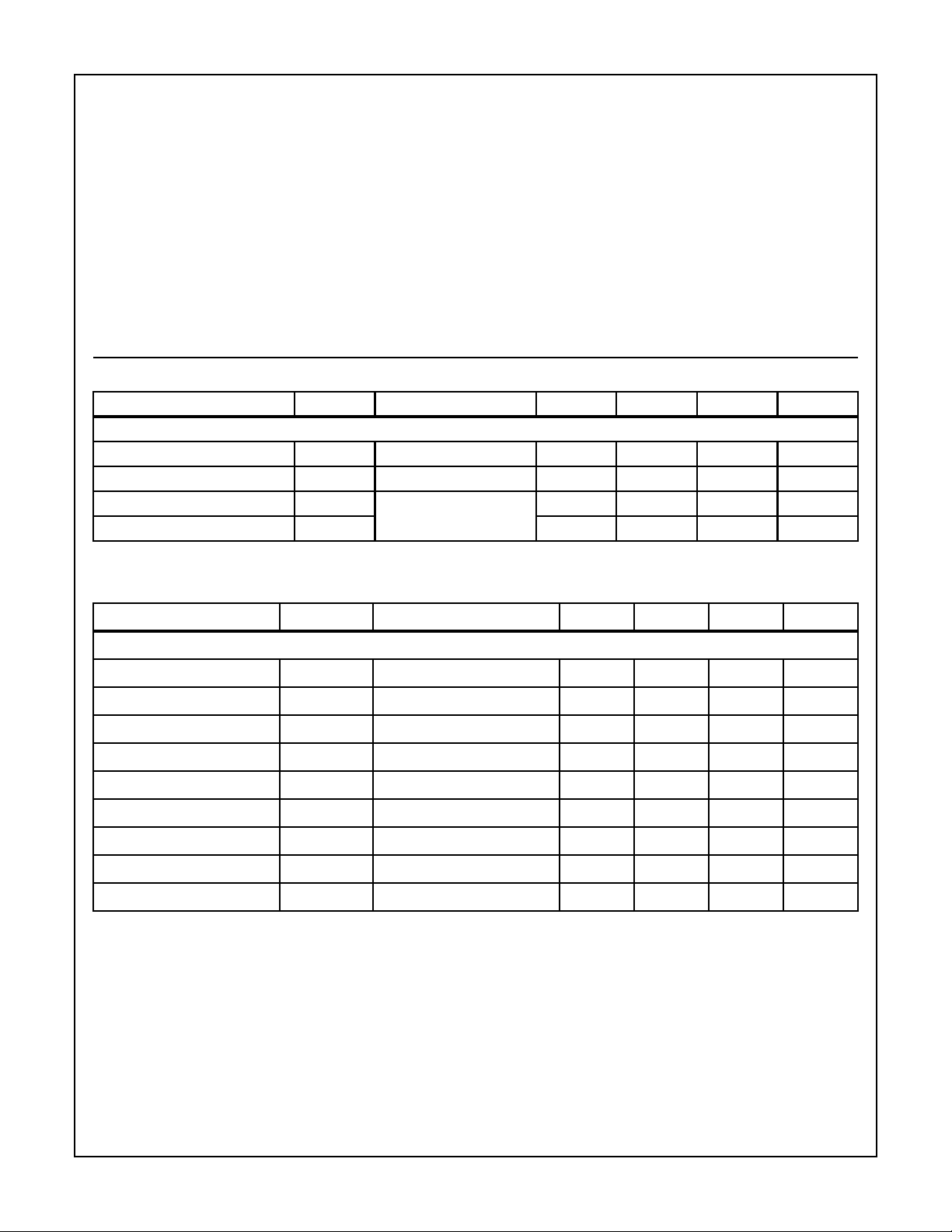

Electrical Specifications At T

= 25oC

A

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

STATIC SPECIFICATIONS

Positive Power Supply V+ 4.75 5 5.25 V

Negative Power Supply V- -4.75 -5 -5.25 V

Power Dissipation (Operating) P

Power Dissipation (Standby) P

Electrical Specifications At T

OPR

STBY

= 0oC to 70oC; V+ = 5V ±5%, V- = -5V ±5%

A

V+ = 5V - 75 90 mW

V- = -5V - 9 15 mW

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

STATIC SPECIFICATIONS

Analog Input Resistance R

Input Capacitance C

Input Leakage Current, Digital I

Low Level Input Voltage V

High Level Input Voltage V

Low Level Output Voltage V

High Level Output Voltage V

Open State Output Current I

Input Leakage Current, Analog I

INA

OL

OH

OZ

IN

I

IL

IH

All Logic and Analog Inputs - 5 - pF

VI = 0V or V+ -10 - 10 µA

IIL = ±10µA (Max) - - 0.8 V

IIH = ±10µA (Max) 2 - - V

IOL = 3.2mA - - 0.4 V

IOH = 1.0mA 2.4 - - V

GND < DX < V+ -10 - 10 µA

I

-2.5V ≤ VFX < 2.5V -200 - 200 nA

10 - - MΩ

4-166

CD22354A, CD22357A

Electrical Specifications V+ = 5V ±5%, V- = -5V ± 5%, BCLK

TA = 0oC to 70oC

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

TRANSMIT AND RECEIVE FILTER TRANSFER CHARACTERISTICS

Transmit Gain

(Relative to Gain at 1020Hz)

Input Amplifier Set to Unity Gain

Receive Gain

(Relative to Gain at 1020Hz)

(Includes (SIN X)/X Compensation)

G

RX

G

RR

f = 16Hz - - -40 dB

f = 50Hz - - -30 dB

f = 60Hz - - -26 dB

f = 200Hz -1.8 - -0.1 dB

f = 300Hz to 3000Hz -0.15 - 0.15 dB

f = 3300Hz -0.35 - 0.05 dB

f = 3400Hz -0.7 - 0 dB

f = 4000Hz - - -14 dB

f ≥ 4600Hz,

Measure 0 - 4kHz Response

f = 0Hz to 3000Hz -0.15 - 0.15 dB

f = 3300Hz -0.35 - 0.05 dB

= BCLKX = MCLKX = 1.544MHz, VIN = 0dBm0,

R

- - -32 dB

f = 3400Hz -0.9 - 0 dB

f = 4000Hz - - -14 dB

AC Specifications

Unless otherwise specified, the following conditions apply:

V+ = 5V ±5%, V- = -5V ±5%

GNDA, GNDD = 0V, FFX = 1020Hz at 0dBm0

Transmit input amplifier operating in a unity gain configuration

Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .0oC to 70oC

Receive output is measured single-ended. All output levels are

(SIN X)/X corrected.

Definition

AMPLITUDE RESPONSE

Absolute Levels Definition:

V

= -2.5V

REF

Nominal 0dBm0 level. . . . . . . . . . . . . . . . . . . . . . 4dBm into 600Ω

1.2276V

Maximum Overload Level:

Voltage reference (V

) of -2.5V . . . . . . . . . . . . . . . . 2.5V µ-Law

REF

2.49V A-Law

RMS

AC Specifications Encoding Format at DX Output

CD22357A

CD22354A

µ-LAW

VIN (at GSX) = +Full-Scale 1 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0

VIN (at GSX) = 0V 1111111111010101

0111111101010101

(INCLUDES EVEN BIT INVERSION)

A-LAW

VIN (at GSX) = -Full-Scale 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0

4-167

Loading...

Loading...