August 1997

CA3338, CA3338A

CMOS Video Speed, 8-Bit,

50 MSPS, R2R D/A Converters

Features

• CMOS/SOS Low Power

• R2R Output, Segmented for Low “Glitch”

• CMOS/TTL Compatible Inputs

1

• Fast Settling: (Typ) to

/2 LSB . . . . . . . . . . . . . . . .20ns

• Feedthrough Latch for Clocked or Unclocked Use

• Accuracy (Typ). . . . . . . . . . . . . . . . . . . . . . . . . ±0.5 LSB

• Data Complement Control

• High Update Rate (Typ). . . . . . . . . . . . . . . . . . . . 50MHz

• Unipolar or Bipolar Operation

Applications

• TV/Video Display

• High Speed Oscilloscope Display

• Digital Waveform Generator

• Direct Digital Synthesis

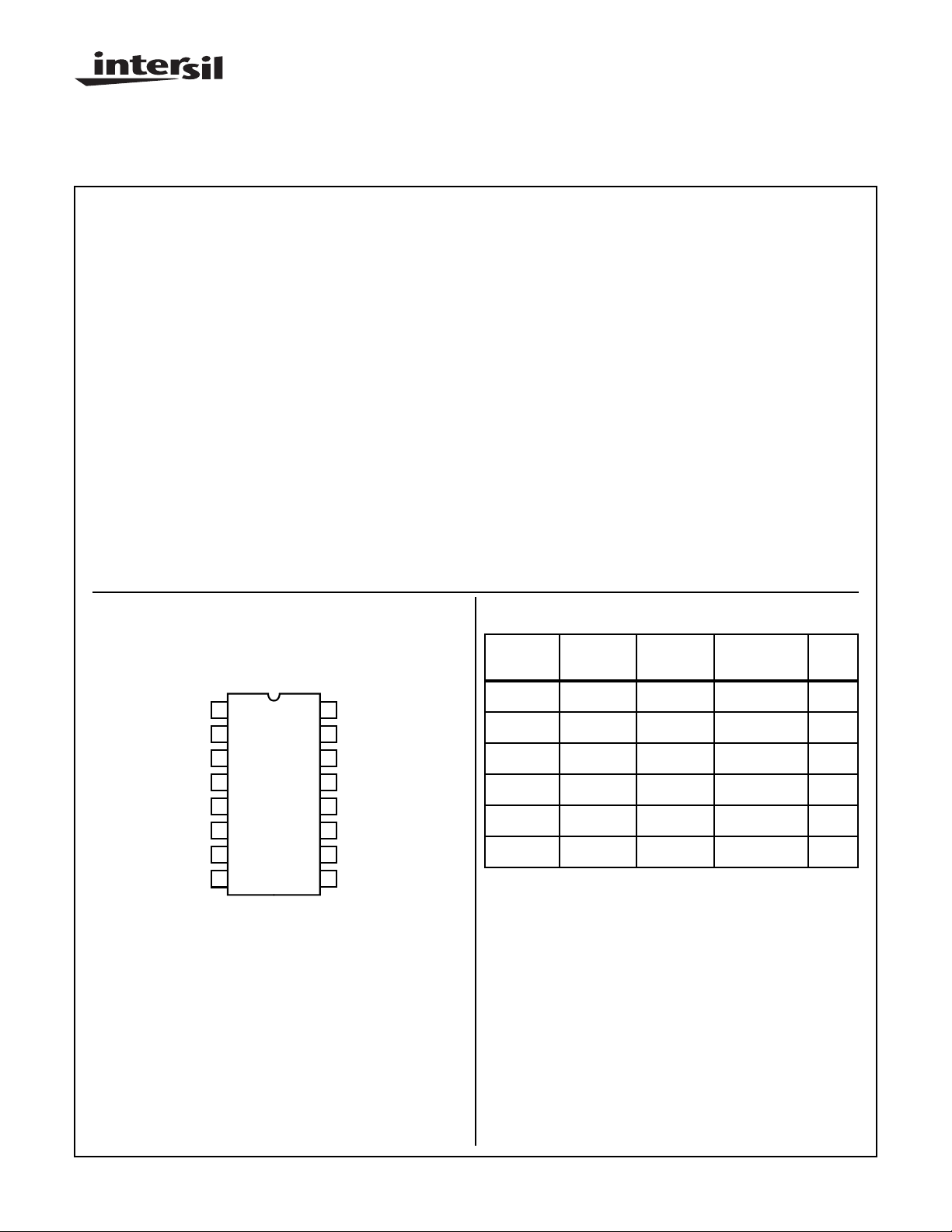

Pinout

CA3338, CA3338A

(PDIP, SBDIP, SOIC)

TOP VIEW

Description

The CA3338 family are CMOS/SOS high speed R2R voltage

output digital-to-analog converters. They can operate from a

single +5V supply, at video speeds, and can produce

“rail-to-rail” output swings. Internal level shifters and a pin for

an optional second supply provide for an output range below

digital ground. The data complement control allows the inversion of input data while the latch enable control provides

either feedthrough or latched operation. Both ends of the

R2R ladder network are available externally and may be

modulated for gain or offset adjustments. In addition, “glitch”

energy has been kept very low by segmenting and thermometer encoding of the upper 3 bits.

The CA3338 is manufactured on a sapphire substrate to give

low dynamic power dissipation, low output capacitance, and

inherent latch-up resistance.

Ordering Information

PART

NUMBER

LINEARITY

(INL, DNL)

TEMP.

RANGE (oC) PACKAGE

PKG.

NO.

V

1

D7

2

D6

3

D5

4

D4

5

D3

6

D2

7

D1

8

V

SS

16

15

14

13

12

11

10

9

DD

LE

COMP

V

REF

V

OUT

V

REF

V

EE

D0

+

-

CA3338E ±1.0 LSB -40 to 85 16 Ld PDIP E16.3

CA3338AE ±0.75 LSB -40 to 85 16 Ld PDIP E16.3

CA3338D ±1.0 LSB -55 to 125 16 Ld SBDIP D16.3

CA3338AD ±0.75 LSB -55 to 125 16 Ld SBDIP D16.3

CA3338M ±1.0 LSB -40 to 85 16 Ld SOIC M16.3

CA3338AM ±0.75 LSB -40 to 85 16 Ld SOIC M16.3

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

10-11

File Number 1850.2

Functional Diagram

CA3338, CA3338A

V

DD

LE

COMP

D7

D6

D5

D4

D3

D2

D1

D0

V

SS

16

8R

15

3-BIT

14

1

2

3

4

5

6

7

9

8

LEVEL

SHIFTERS

TO 7-LINE

THERMOMETER

ENCODER

FEEDTHROUGH

LATCHES

8R

8R

8R

4R

4R

2R

2R

2R

2R

2R

2R

R ≅160Ω

R

R

R

R

R

R

R

2R

13

V

+

REF

12

V

OUT

11

V

-

REF

10

V

EE

10-12

CA3338, CA3338A

Absolute Maximum Ratings Thermal Information

DC Supply-Voltage Range . . . . . . . . . . . . . . . . . . . . . . -0.5V to +8V

(VDD - VSS or VDD - VEE, Whichever is Greater)

Input Voltage Range

Digital Inputs (LE, COMP D0 - D7). . . . VSS - 0.5V to VDD + 0.5V

Analog Pins (V

REF

+, V

REF

-, V

). . . . VDD - 8V to VDD + 0.5V

OUT

DC Input Current

Digital Inputs (LE, COMP, D0 - D7). . . . . . . . . . . . . . . . . . ±20mA

Recommended Supply Voltage Range. . . . . . . . . . . . . .4.5V to 7.5V

Operating Conditions

Temperature Range (TA)

Ceramic Package, D suffix . . . . . . . . . . . . . . . . . . . -55oC to 125oC

Plastic Package, E suffix, M suffix . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

SBDIP Package. . . . . . . . . . . . . . . . . . 75 24

PDIP Package. . . . . . . . . . . . . . . . . . . 100 N/A

SOIC Package. . . . . . . . . . . . . . . . . . . 100 N/A

Maximum Junction Temperature

Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175oC

Plastic Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range, T

. . . . .-65oC to 150oC

STG

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . .300oC

(SOIC - Lead Tips Only)

Electrical Specifications T

= 25oC, VDD = 5V, V

A

+ = 4.608V, VSS = VEE = V

REF

- = GND, LE Clocked at 20MHz, RL≥ 1 MΩ,

REF

Unless Otherwise Specified

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

ACCURACY

Resolution 8 - - Bits

Integral Linearity Error See Figure 4

CA3338 - - ±1 LSB

CA3338A - - ±0.75 LSB

Differential Linearity Error See Figure 4

CA3338 - - ±0.75 LSB

CA3338A - - ±0.5 LSB

Gain Error Input Code = FF

, See Figure 3

HEX

CA3338 - - ±0.75 LSB

CA3338A - - ±0.5 LSB

Offset Error Input Code = 00

; See Figure 3 - - ±0.25 LSB

HEX

DIGITAL INPUT TIMING

Update Rate To Maintain1/2 LSB Settling DC 50 - MHz

Update Rate V

Set Up Time t

Set Up Time t

Hold Time t

Latch Pulse Width t

Latch Pulse Width t

SU1

SU2

H

W

W

OUTPUT PARAMETERS RL Adjusted for 1V

Output Delay t

Output Delay t

Rise Time t

Settling Time t

D1

D2

r

S

Output Impedance V

- = VEE = -2.5V, V

REF

+ = +2.5V DC 20 - MHz

REF

For Low Glitch - -2 - ns

For Data Store - 8 - ns

For Data Store - 5 - ns

For Data Store - 5 - ns

V

- = VEE = -2.5V, V

REF

P-P

+ = +2.5V - 25 - ns

REF

Output

From LE Edge - 25 - ns

From Data Changing - 22 - ns

10% to 90% of Output - 4 - ns

10% to Settling to1/2 LSB - 20 - ns

+ = 6V, VDD = 6V 120 160 200 Ω

REF

Glitch Area - 150 - pV/s

Glitch Area V

- = VEE = -2.5V,V

REF

+ = +2.5V - 250 - pV/s

REF

10-13

Loading...

Loading...