Intersil Corporation CA3304 Datasheet

August 1997

CA3304, CA3304A

4-Bit, 25 MSPS,

Flash A/D Converters

Features

• CMOS/SOS Low Power with Video Speed (Typ) . . 25mW

• Parallel Conversion Technique

• Single Power Supply Voltage . . . . . . . . . . . . 3V to 7.5V

• 25MHz Sampling Rate (40ns Conversion Time) at 5V

Supply

• 4-Bit Latched Three-State Output with Overflow and

Data Change Outputs

1

•

/8 LSB Maximum Nonlinearity (A Version)

• Inherent Resistance to Latch-Up Due to SOS Process

• Bipolar Input Range with Optional Second Supply

• Wide Input Bandwidth (Typ) . . . . . . . . . . . . . . . . 25MHz

Applications

• High Speed A/D Conversion

• Ultrasound Signature Analysis

• Transient Signal Analysis

• High Energy Physics Research

• General-Purpose Hybrid ADCs

• Optical Character Recognition

• Radar Pulse Analysis

• Motion Signature Analysis

• Robot Vision

• RSSI Circuits

Description

The Intersil CA3304 is a CMOS parallel (FLASH) analog-todigital converter designed for applications demanding both

low-power consumption and high speed digitization. Digitizing at 25MHz, for example, requires only about 35mW.

The CA3304 operates over a wide, full-scale signal input

voltage range of 0.5V up to the supply voltage. Power

consumption is as low as 10mW, depending upon the clock

frequency selected.

The intrinsic high conversion rate makes the CA3304 types

ideally suited for digitizing high speed signals. The overflow

bit makes possible the connection of two or more CA3304s

in series to increase the resolution of the conversion system.

A series connection of two CA3304s may be used to produce a 5-bit, 25MHz converter. Operation of two CA3304s in

parallel doubles the conversion speed (i.e., increases the

sampling rate from 25MHz to 50MHz). A data change pin

indicates when the present output differs from the previous,

thus allowing compaction of data storage.

Sixteen paralleled auto-balanced voltage comparators measure the input voltage with respect to a known reference to

produce the parallel-bit outputs in the CA3304. Fifteen comparators are required to quantize all input voltage le vels in this

4-bit converter, and the additional comparator is required for

the overflow bit.

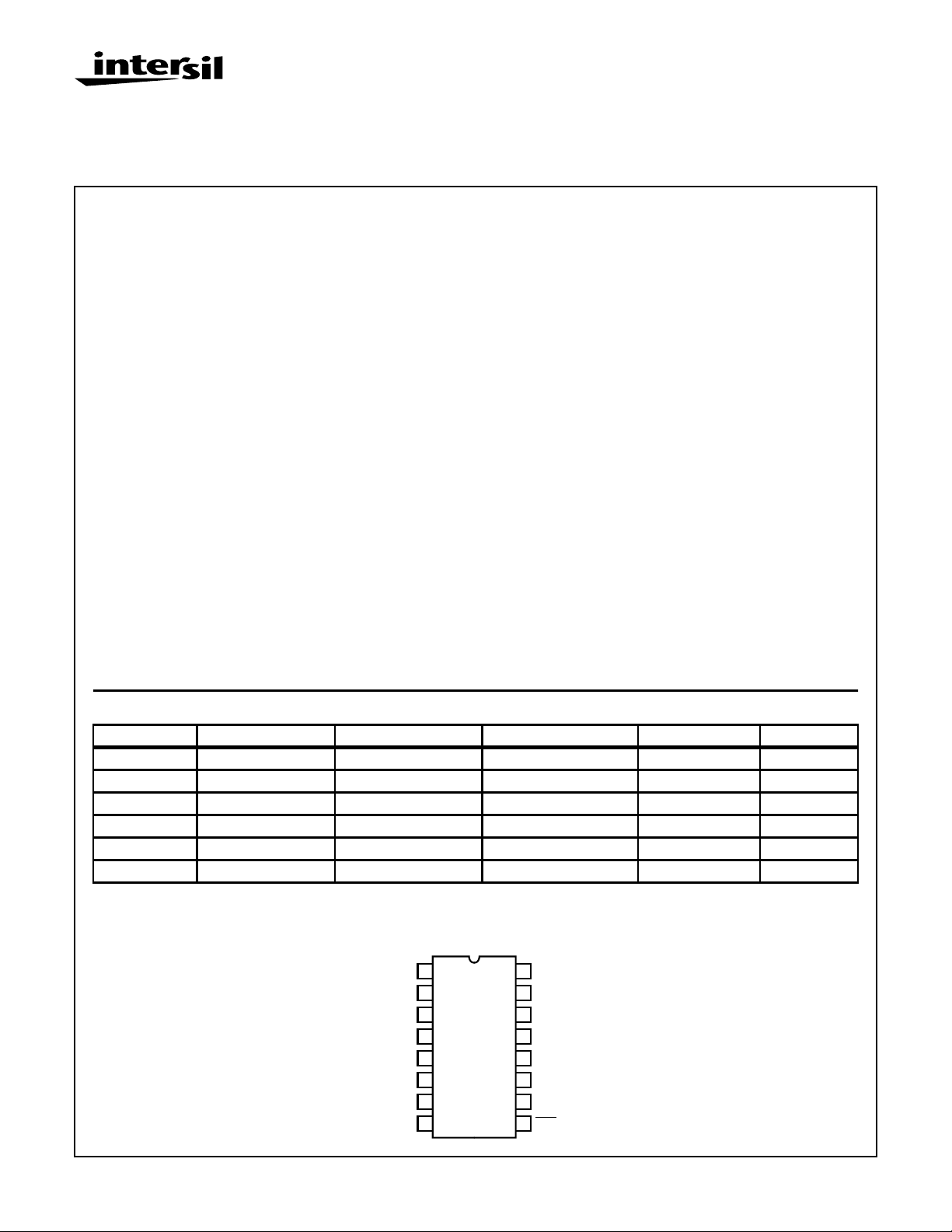

Ordering Information

PART NUMBER LINEARITY (INL, DNL) SAMPLING RATE TEMP. RANGE (oC) PACKAGE PKG. NO.

CA3304E ±0.25 LSB 25MHz (40ns) -40 to 85 16 Ld PDIP E16.3

CA3304AE ±0.125 LSB 25MHz (40ns) -40 to 85 16 Ld PDIP E16.3

CA3304M ±0.25 LSB 25MHz (40ns) -40 to 85 16 Ld SOIC (W) M16.3

CA3304AM ±0.125 LSB 25MHZ (40ns) -40 to 85 16 Ld SOIC (W) M16.3

CA3304D ±0.25 LSB 25MHz (40ns) -55 to 125 16 Ld SBDIP D16.3

CA3304AD ±0.125 LSB 25MHz (40ns) -55 to 125 16 Ld SBDIP D16.3

Pinout

CA3304 (SBDIP, PDIP, SOIC)

TOP VIEW

V

BIT 1 (LSB)

BIT 2

BIT 3

BIT 4

DATA CHANGE (DC)

OVERFLOW (OF)

CE2

V

SS

1

2

3

4

5

6

7

8

16

DD

15

CLK

14

VAA-

13

-

V

REF

12

V

+

REF

V

11

IN

10

VAA+

9

CE1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

4-7

File Number 1790.2

CA3304, CA3304A

Absolute Maximum Ratings Thermal Information

DC Supply Voltage Range (VDD or VAA+)

(Voltage Referenced to VSS or VAA- Terminal,

Whichever is More Negative) . . . . . . . . . . . . . . . . . . -0.5V to +8V

Input Voltage Range

CE1, CE2 Inputs. . . . . . . . . . . . . . . . . . . VSS -0.5V to VDD +0.5V

Clock, V

DC Input Current, Any Input. . . . . . . . . . . . . . . . . . . . . . . . . ±20mA

REF

+, V

-, VIN Inputs . . . . . VAA- -0.5V to VAA- +0.5V

REF

Operating Conditions

Recommended Supply Voltage Range (VDD or VAA+) . . . . .3V to 7.5V

Recommended VAA+ Voltage Range. . . . . . VDD -1V to VDD +2.5V

Recommended VAA- Voltage Range . . . . . . .VSS -2.5V to VSS +1V

Operating Temperature

CA3304D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CA3304E, CA3304M. . . . . . . . . . . . . . . . . . . . . . . . -40oC to 85oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 1) θJA (oC/W) θJC (oC/W)

SBDIP Package. . . . . . . . . . . . . . . . . . . . 80 22

PDIP Package. . . . . . . . . . . . . . . . . . . . . 90 N/A

SOIC Package. . . . . . . . . . . . . . . . . . . . . 100 N/A

Maximum Junction Temperature

Ceramic Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175oC

Plastic Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range (T

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

) . . . -65oC to 150oC

STG

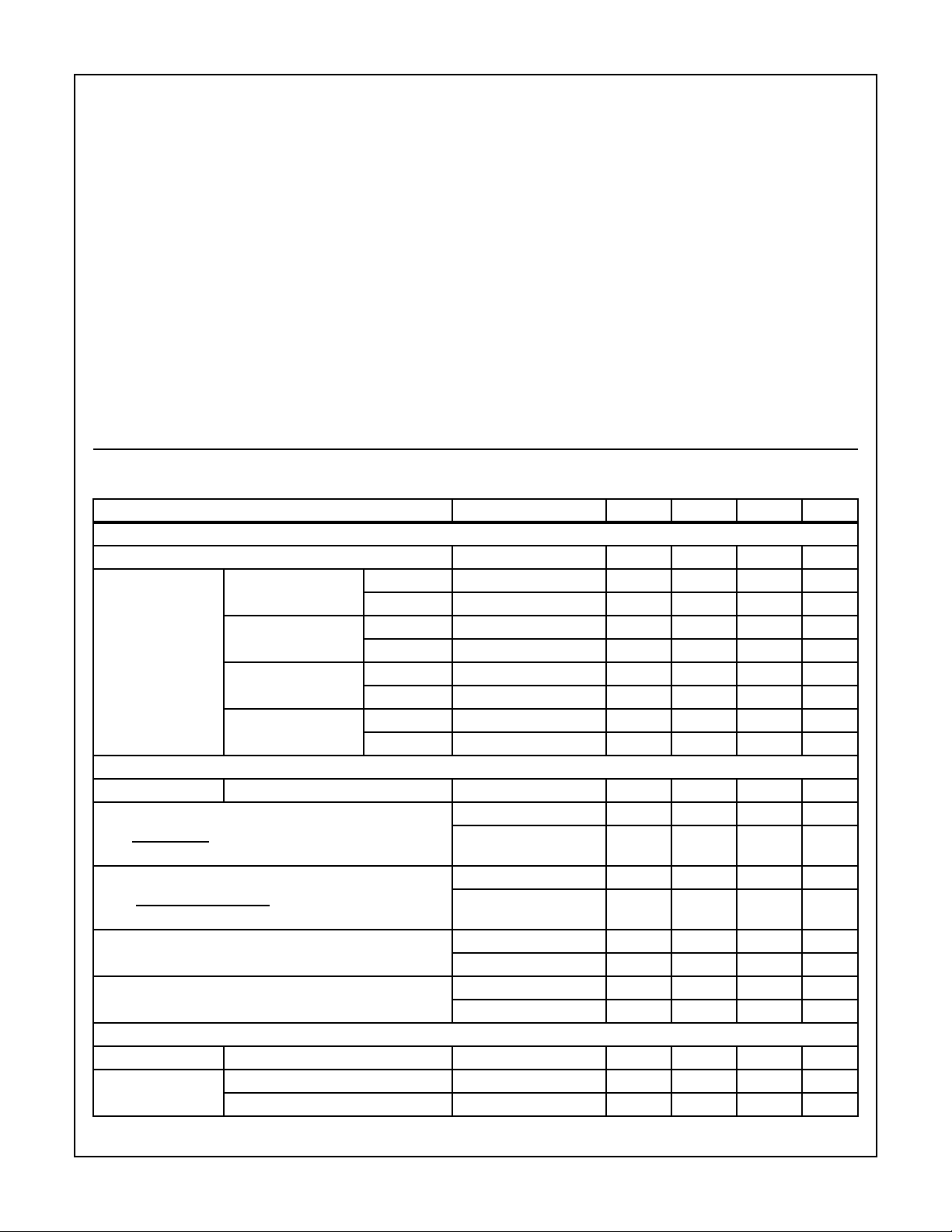

Electrical Specifications T

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

SYSTEM PERFORMANCE

Resolution 4 - - Bits

Input Errors Integral Linearity

Error

Differential Linearity

Error

Offset Error

(Unadjusted)

Gain Error

(Unadjusted)

DYNAMIC CHARACTERISTICS (Input Signal Level 0.5dB Below Full Scale)

Conversion Timing Aperture Delay - 3 - ns

Signal to Noise Ratio, SNR

RMS Signal

=

RMS Noise

Signal to Noise Ratio, SINAD

RMS Signal

=

RMS Noise + Distortion

Total Harmonic Distortion, THD fS = 25MHz, fIN = 100kHz - -34.5 - dBc

Effective Number of Bits, ENOB fS = 25MHz, fIN = 100kHz - 3.67 - Bits

ANALOG INPUTS

Input Range Full Scale Input Range (Notes 1, 4) 0.5 - V

Input Loading Input Capacitance - 10 - pF

Input Current VIN = 2V (Note 2) - 150 200 µA

= 25oC, V

A

Unless Otherwise Specified

+ = 2V, VDD = VAA+ = 5V, VAA- = V

REF

CA3304A - ±0.1 ±0.125 LSB

CA3304 - ±0.125 ±0.25 LSB

CA3304A - ±0.1 ±0.125 LSB

CA3304 - ±0.125 ±0.25 LSB

CA3304A - - ±0.75 LSB

CA3304 - - ±1.0 LSB

CA3304A - - ±0.75 LSB

CA3304 - - ±1.0 LSB

- = VSS = GND, f

REF

fS = 25MHz, fIN = 100kHz - 23.7 - dB

fS = 25MHz, fIN = 5MHz - 23.6 - dB

fS = 25MHz, fIN = 100kHz - 23.4 - dB

fS = 25MHz, fIN = 5MHz - 22.8 - dB

fS = 25MHz, fIN = 5MHz - -31.0 - dBc

fS = 25MHz, fIN = 5MHz - 3.57 - Bits

CLK

= 25MHz

AA

V

4-8

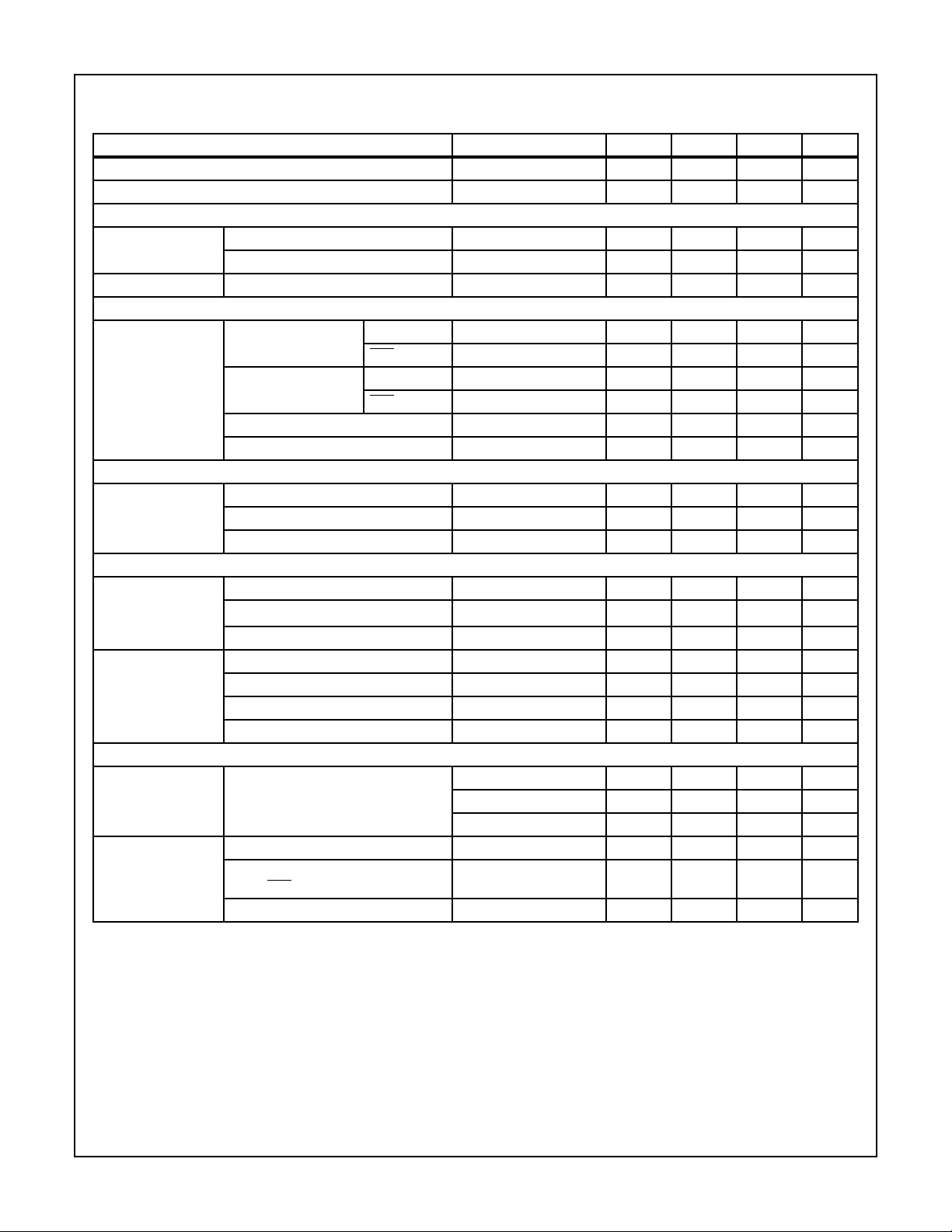

CA3304, CA3304A

Electrical Specifications T

= 25oC, V

A

+ = 2V, VDD = VAA+ = 5V, VAA- = V

REF

- = VSS = GND, f

REF

CLK

= 25MHz

Unless Otherwise Specified (Continued)

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

Allowable Input Bandwidth (Note 4) - 25 f

/2 MHz

CLK

-3dB Input Bandwidth - 40 - MHz

REFERENCE INPUTS

Input Range V

+ Range (Note 4) VAA- +0.5 - VAA+V

REF

V

- Range (Note 4) VAA--V

REF

+ -0.5 V

AA

Input Loading Resistor Ladder Impedance VIN = 5V, CLK = Low 640 - 960 Ω

DIGITAL INPUTS

Digital Input Maximum VIN, Low CLOCK (Notes 3, 4) - - 0.3 x V

CE1, CE2 (Note 4) - - 0.3 x V

Minimum VIN, High CLOCK (Notes 3, 4) 0.7 x V

CE1, CE2 (Note 4) 0.7 x V

AA

DD

--V

--V

AA

DD

Input Leakage, Except CLK V = 0V, 5V - - ±1 µA

Input Leakage, CLK (Note 3) - ±100 ±150 µA

DIGITAL OUTPUTS

Digital Outputs Output Low (Sink) Current VO = 0.4V 6 - - mA

Output High (Source) Current VO = 4.6V -3 - - mA

Three-State Leakage Current VO = 0V, 5V - ±0.2 ±5 µA

TIMING CHARACTERISTICS

Conversion Timing Maximum Conversion Speed CLK = Square Wave 25 35 - MSPS

Auto-Balance Time (φ1) 20 -

-

Sample Time (φ2) 20 - 5000 ns

Output Timing Data Valid Delay (Note 4) - 30 40 ns

Data Hold Time (Note 4) 15 25 - ns

Output Enable Time - 15 - ns

Output Disable Time - 10 - ns

POWER SUPPLY CHARACTERISTICS

Device Current, I

AA

Continuous Clock - 5.5 - mA

Continuous φ2 - 0.4 - mA

Continuous φ1-2-mA

Device Current, I

DD

VAA+ = 5V,

Continuous Clock - 1.5 - mA

Continuous φ2-510mA

VSS = CE1 = VAA- = CLK = GND

VAA+ = 7V Continuous φ1-520mA

NOTES:

1. Full scale input range, V

REF

+ - V

-, may be in the range of 0.5V to VAA+ -VAA- volts. Linearity errors increase at lower full scale ranges,

REF

however.

2. Input current is due to energy transferred to the input at the start of the sample period. The average value is dependent on input and V

voltage.

3. The CLK input is a CMOS inverter with a 50kΩ feedback resistor. It operates from the VAA+ and VAA- supplies. It may be AC-coupled

with a 1V

minimum source.

P-P

4. Parameter not tested, but guaranteed by design or characterization.

V

V

ns

DD

4-9

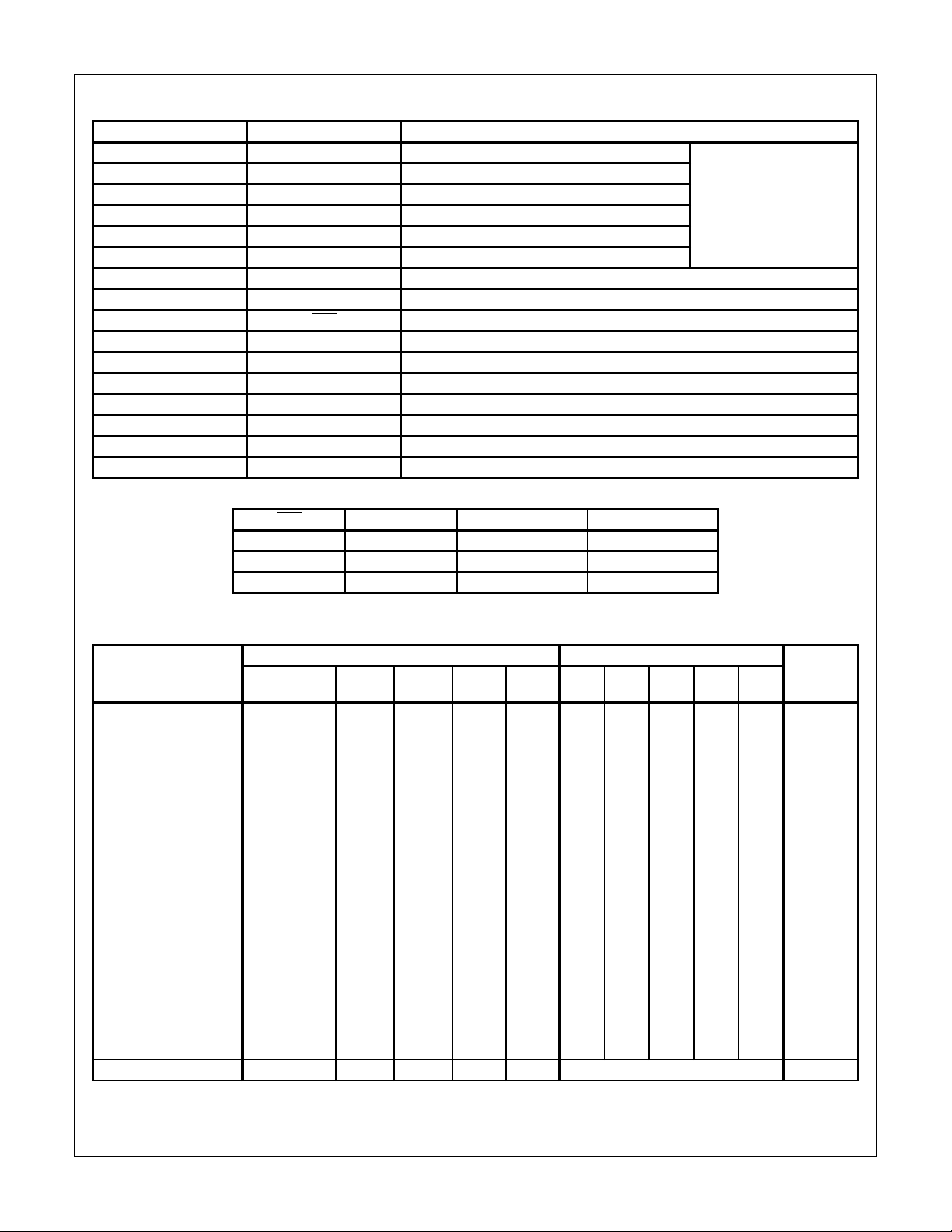

CA3304, CA3304A

Pin Descriptions

PIN NUMBER NAME DESCRIPTION

1 Bit 1 Bit 1 (LSB).

2 Bit 2 Bit 2.

3 Bit 3 Bit 3.

4 Bit 4 Bit 4 (MSB).

5 DC Data Change.

6 OF Overflow.

7 CE2 Three-State Output Enable Input, active low. See the Chip Enable Truth Table.

8V

9 CE1 Three-State Output Enable Input, active high. See the Chip Enable Truth Table.

10 VAA+ Analog Power Supply, +5V.

11 V

12 V

13 V

14 VAA- Analog Ground.

15 CLK Clock Input.

16 V

SS

IN

+ Reference Voltage Positive Input.

REF

- Reference Voltage Negative Input.

REF

DD

Digital Ground.

Analog Signal Input.

Digital Power Supply, +5V.

CHIP ENABLE TRUTH TABLE

Output Data Bits

(High = True)

CE1 CE2 BIT 1 - BIT 4 DC, OF

0 1 Valid Valid

1 1 Three-State Valid

X 0 Three-State Three-State

X = Don't Care

TABLE 1. OUTPUT CODE TABLE

INPUT VOLTAGE (V) OUTPUT CODE

CODE

DESCRIPTION

Zero -1.000 0 0 0 0 00000 0

1 LSB -0.875 0.1 0.125 0.2 0.3 00001 1

2 LSB -0.750 0.2 0.250 0.4 0.6 00010 2

• • • • • • ••••• •

• • • • • • ••••• •

• • • • • • ••••• •

• • • • • • ••••• •

1

/2 Full Scale -1 LSB -0.125 0.7 0.875 1.4 2.1 00111 7

1

/2 Full Scale 0 0.8 1.000 1.6 2.4 01000 8

1

/2 Full Scale +1 LSB 0.125 0.9 1.125 1.8 2.7 01001 9

• • • • • • ••••• •

• • • • • • ••••• •

• • • • • • ••••• •

• • • • • • ••••• •

Full Scale -1 LSB 0.750 1.4 1.750 2.8 4.2 01110 14

Full Scale 0.875 1.5 1.875 3.0 4.5 01111 15

Overflow 1.000 1.6 2.000 3.2 4.8 11111 31

Step Size 0.125 0.1 0.125 0.2 0.3

NOTE:

1. The voltages listed are the ideal centers of each output code shown as a function of its associated reference voltage See Ideal Transfer

Curve Figure 6. The output code should exist for an input equal to the ideal center voltage±1/2 of the step size.

V

V

REF

REF

+ = 1V

- = -1V

1.6V

0V

2V

0V

3.2V0V4.8V

0V OF B4 B3 B2 B1

DECIMAL

COUNT

4-10

Loading...

Loading...