Intersil Corporation CA3274 Datasheet

April 1994

CA3274

Current Limiting Power Switch

with Current Limiter Sense Flag

Features

• Drive-Current Limiting at Output

• Current-Sense Buffer and Reference

• 200mA Driver Current Capability

• Logic-Level Control Input

• Current Limiting Flag Output

• 50dB Minimum PSRR

•5µs Typical Switch Time

• Separate Signal and Power Grounds

Applications

• Solenoid Switch Driver

• Relay Driver

• Lamp Control Switch

• Ignition Coil Pre-Driver

• Constant Current Driver

• Current Limiting Switch

• Fault Output Sense Appliance

• Power Supply Fault Mode Control

Ordering Information

TEMPERATURE

PART NUMBER

CA3274E -40oC to +85oC 8 Lead Plastic DIP

RANGE PACKAGE

Description

The CA3274 is a controlled current switch and may be used in

general purpose switching applications that require specified

maximum levels of current. The functional block diagram of

the CA3274 is shown and a typical application circuit is shown

in Figure 1. An internal emitter follower has 200mA of source

drive output capability. The Control Input is a Schmitt trigger

buffer amplifier for noise immunity in the environments typical

of industrial and automotive control systems.

Current sensing in the emitter circuit of a power-darlington

output stage is fed back from a sampling resistor to the sense

input of the CA3274 which has a 335mV typical offset. For the

example shown in Figure 1, a sampling resistor of 0.056Ω

permits 6.0A (0.335/0.056) of current in the emitter of the output

driver. When the current limiter is activated, the flag output

changes state conditionally. If the control input is the “0” state,

the flag output will remain in a “1” state. If the control input is in

the “1” state and the sense input is less than the voltage

reference level of 335mV, the flag output will remain in the “1”

state. If the control input is the “1” state and the sense input is

equal to or greater than the 335mV reference level, the flag

output goes to the “0” state. The output flag switch may be used

to accurately establish dwell timing in automotive applications.

When the control input goes to “0”, the flag is reset to “1”. Noiseimmunity hold-off is used to prevent pre-triggering of the flag

output and is noted as t

The flag output may be used for diagnostic feedback via the

current sense input to detect a fault mode. In this case the

sampled drive current is either from the emitter of the CA3274

internal power transistor or an external output amplifier, such as

a darlington power transistor or power-FET output stage. The

CA3274 has separate power and signal grounds to minimize

transient-loop feedback to the input ground and thus prevent

false triggering of the output. Optionally, the output from the

CA3274 may be taken from the open collector (DRIVE IN) at

pin 6. An external resistor at pin 6 may be used to set the level

at which Q2 will saturate, providing additional limiting protection

for the maximum forward-drive from the CA3274.

in the timing diagram of Figure 2.

D

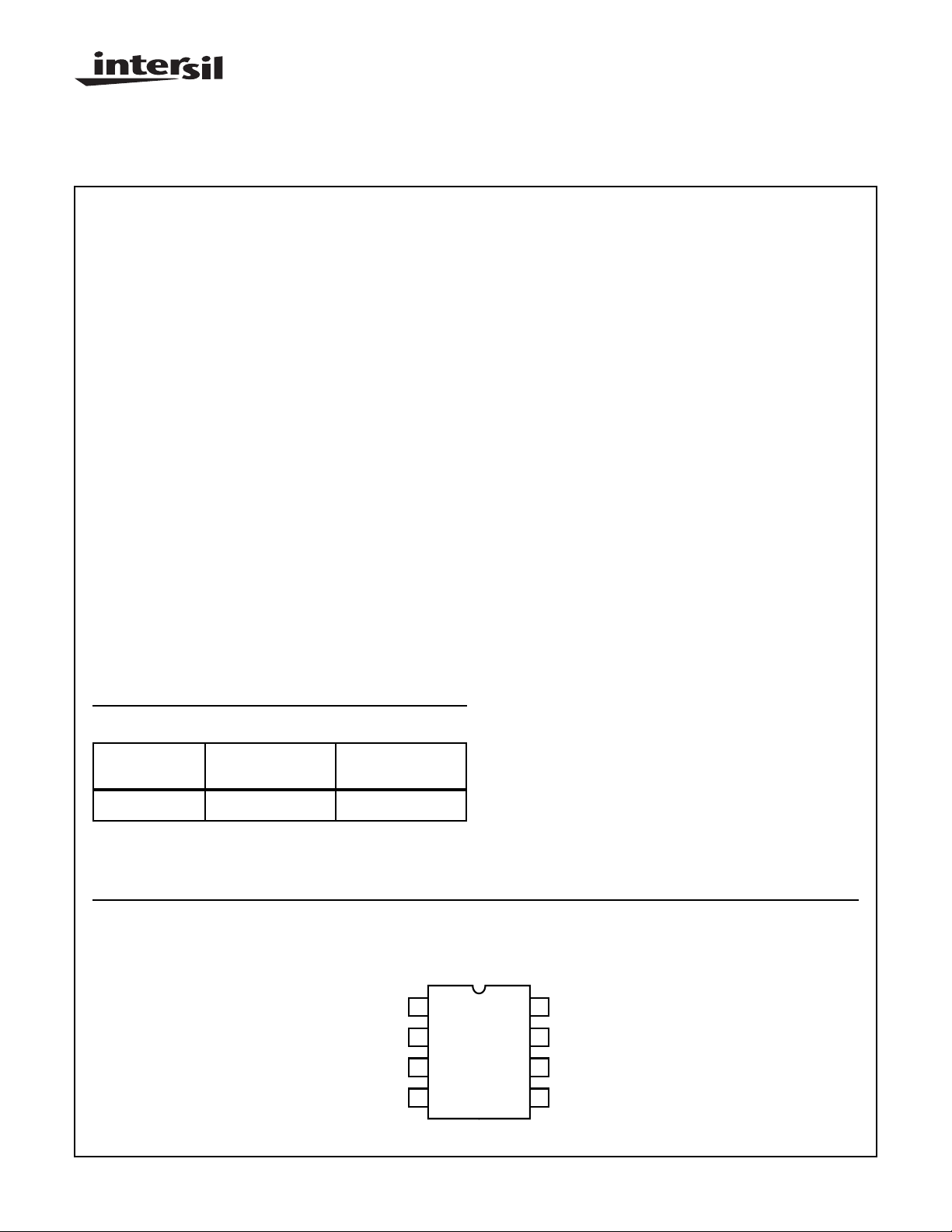

Pinout

CA3274 (PDIP)

TOP VIEW

FLAG OUT

SENSE IN

POWER GND

SIGNAL GND

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

1

2

3

4

10-40

VCC SUPPLY

8

7

CONTROL IN

6

DRIVE IN

5

DRIVE OUT

File Number 2222.2

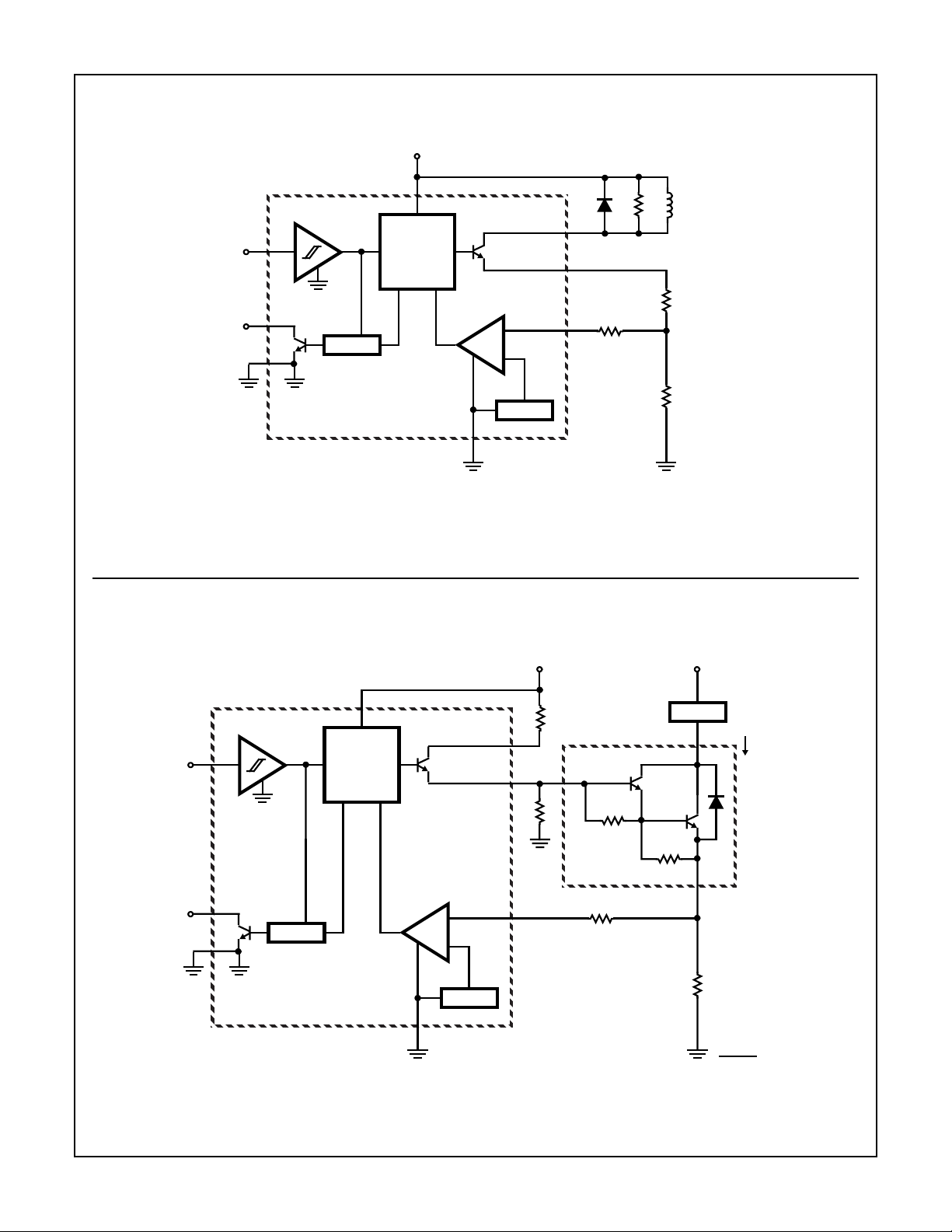

Block Diagram

V

CC

8

CA3274

CONTROL

FLAG

OUT

SIGNAL

GROUND

D1 R4

7

IN

1

Q1

4

LATCH

CONTROL

LOGIC AND

CURRENT

LIMITER

3

Q2

-

SENSE

+

335mV

POWER

GROUND

6

DRIVE IN

5

2

IN

DRIVE OUT

R2

RELAY OR

SOLENOID LOAD

R3

SENSE

R1

CONTROL

FLAG

OUT

SIGNAL

GROUND

V

CC

8

7

IN

1

Q1

4

LATCH

CONTROL

LOGIC &

CURRENT

LIMITER

3

Q2

DRIVE

-

SENSE

+

335mV

POWER

GROUND

6

5

DARLINGTON

2

IN

V

CC1

LOAD

6A

0.056Ω

SENSE LEVEL EQUALS

335mV

= 6A

0.056Ω

FIGURE 1. TYPICAL APPLICATION AS A POWER SWITCH PRE-DRIVER SWITCH

10-41

Loading...

Loading...