Intersil Corporation CA3194 Datasheet

May 1997

Semiconductor

T RECOMMENDED FOR NEW DESIGNS

NO

CA3194

Single Chip PAL

Luminance/Chroma Processor

Features

• All PAL Luminance and Chrominance Processing

Circuitry on a Single Chip in a 24-Lead Plastic

Package

• Phase-Locked Subcarrier Regeneration Utilizing

Sample-and-Hold

• DC Controls for Brightness, Contrast, and Color

Saturation Functions

• Input for Average Beam-Current Limiting

• Contrast Control Having Excellent Tracking of

Luma and Chroma Channels

• Low-lmpedance RGB Outputs with Excellent

Tracking for Direct Coupling to Video Driver

Circuitry

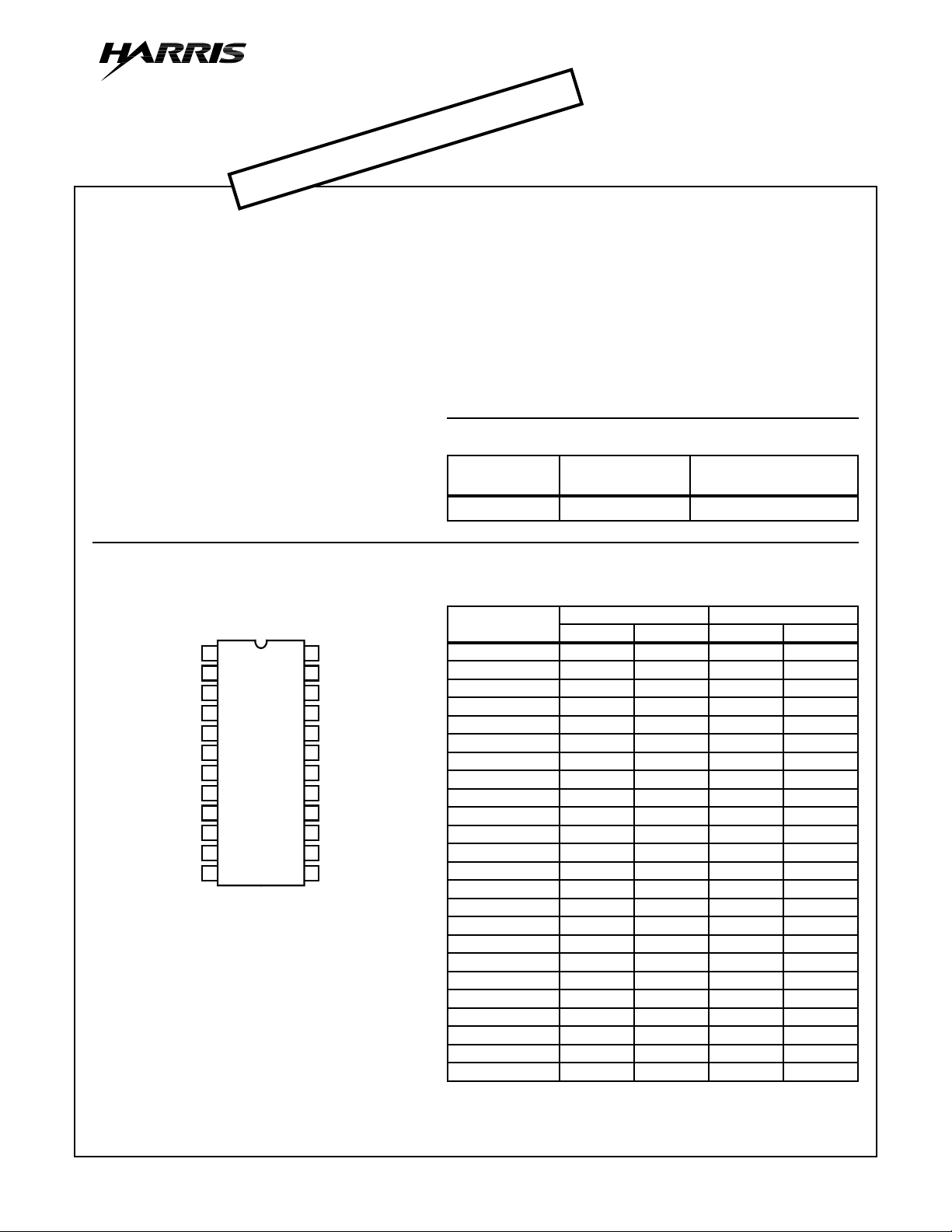

Pinout

CA3194

(PDIP)

TOP VIEW

AVER. BEAM

GND

CHROMA OUT

SAT. CONTR.

CHROMA INPUT

ACC FILTER

ACC FILTER

APC FILTER

APC FILTER

o

90

INPUT

o

0

INPUT

OUTPUT

V

CO

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

24

INFO

BRIGHTNESS

23

CONTROL

PICTURE CONTROL

22

LOW PASS

21

FILTER

LUMA INPUT

20

PEAK BEAM

19

LEVEL

R OUTPUT

18

17

G OUTPUT

16

B OUTPUT

15

INPUT

V

R-Y

14

INPUT

V

B-Y

13

SANDCASTLE

Description

The Harris CA3194E is a silicon monolithic integrated circuit

designed to perform all of the signal processing functions for both

the chroma and luminance signals of PAL color television receivers.

This circuit performs all the functions needed between the video

detector and the video RGB output stages. DC contrast, brightness, and saturation controls and average beam limiting functions

are included. The RGB buffer stages are capable of delivering

5mA of current into the video output stages.

NOTE: Formerly Dev. No. TA10313.

Ordering Information

PART

NUMBER

CA3194E -40oC to +85oC 24 Lead PDIP

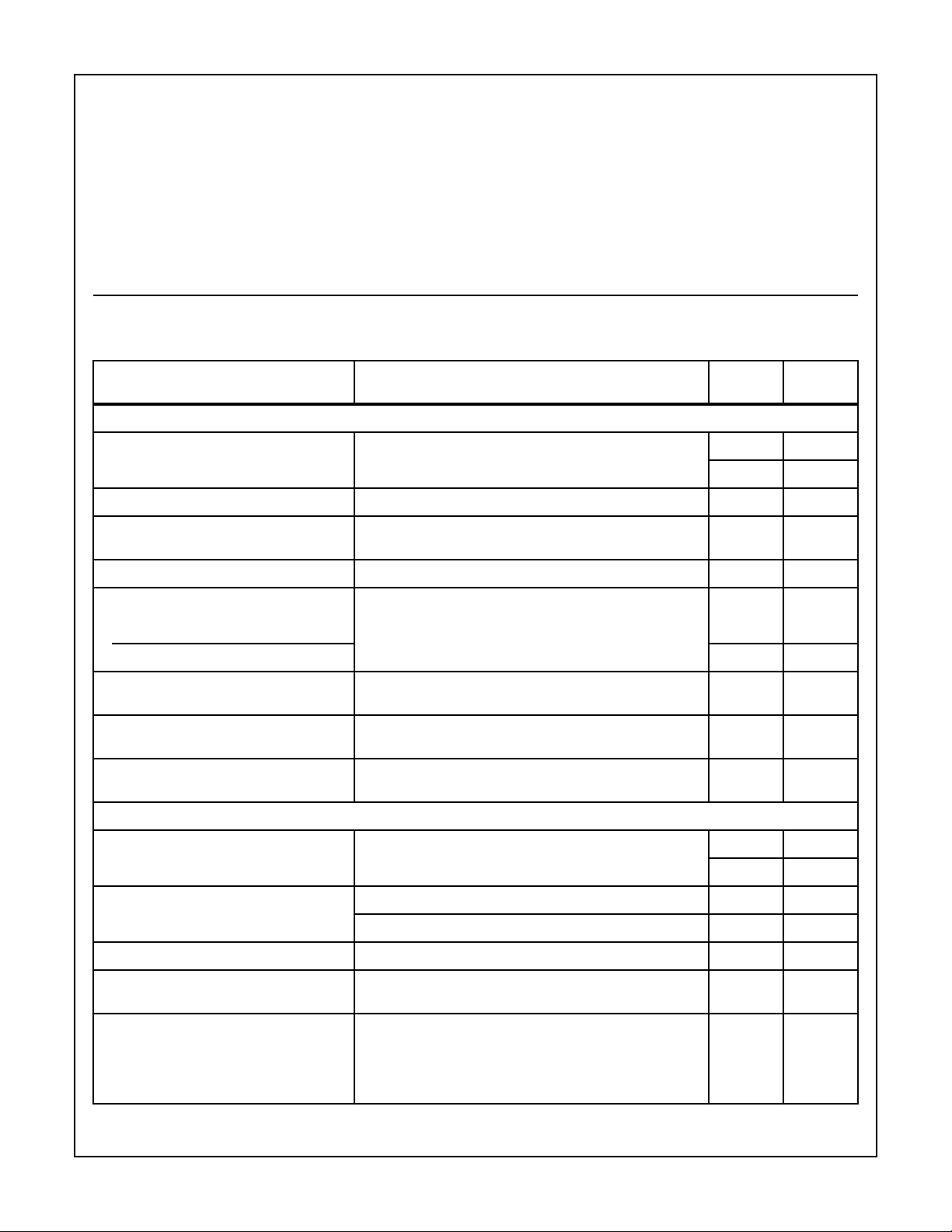

TERMINAL VOLTAGE AND CURRENT RATINGS

TERMINAL

1 ---2 0 13 0 30

30810405-5 0 Note - 6 - - 0.1 0.5

7 0 Note - 8 0 Note - -

908-10 0 8 - 0.7

11 0 13 - 10

12 0 13 - 13 0 12 - 14 0 5 - 1.5

15 0 5 - 1.5

16 0 13 - 10

17 0 13 - 10

18 0 13 - 10

19 0 Note - 20 0 5 - 21 0 Note - 22 0 8 - 23 0 5 - 24 0 12 - -

NOTE:

1. The maximum should not exceed the V

Terminal 1 for VCC (Terminal 12) of 12V ±10%.

TEMPERATURE

RANGE PACKAGE

VOLTAGE (NOTE 1) -V CURRENT - mA

MIN MAX I

voltage. V oltage with respect to

CC

IN

I

OUT

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1997

7-56

File Number 1270.3

Specifications CA3194

Absolute Maximum Ratings Operating Conditions

Supply Voltage and Current

Pin 12 Voltage Range. . . . . . . . . . . . . . . . 11V (Min) to 13V (Max)

Pin 12 Current Range. . . . . . . . . . . . . 44mA (Typ) to 60mA (Max)

Power Dissipation

Up to TA = +25oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 825mW

Above TA = +25oC. . . . . . . . . . . . . . . . Derate Linearly 8.7mW/oC

Junction Temperature (Plastic Package) . . . . . . . . . . . . . . . +150oC

Storage Temperature Range . . . . . . . . . . . . . . . . . -65oC to +150oC

Lead Temperature (Soldering 10s). . . . . . . . . . . . . . . . . . . . +300oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Operating Temperature Range . . . . . . . . . . . . . . . . .-40oC to +85oC

Thermal Package Characteristics (oC/W) θ

JA

PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Electrical Specifications T

= +25oC, VCC = 12V, VS = 2.85V, VC = 2.85V, VAB = VPB = VCC, VB adjusted for V18 = 6.3V, CX adjusted

A

for F

= 4.43361875MHz, Sandcastle: VBG = 8.0V, V

OSC

= 3.5V - Burst Gate centered on Burst.

BLANK

These conditions exist except as otherwise noted. See Figure 19 for test circuit

TYPICAL

PARAMETER TEST CONDITIONS

VALUE UNITS

LUMINANCE SECTION

Input Impedance (Terminal 20) 6kΩ

5pF

Luminance Channel Input Voltage Luma Input Signal = 30% Sync. 0.5 V

Bandwidth of Luminance Channel Luma Input Signal: 0.5V

(30% Sync) modulated CW

P-P

8 MHz

P-P

Adj. modulation frequency for -3dB at color outputs.

Brightness Control Range (Terminal 23) For Control Characteristics, See Figures 1 and 2. 0 - 3.5 V

Output Black Level Luma Input Signal: 0.5V

(30% Sync)

P-P

DC

VB 0V - 5V,Measured at Pin 18 black level.

Range 5.9-9.7 V

Offset 0.6 Max. V

Contrast Control Range (Terminal 22) Luminance Input: 0.5V

See Figures 1 and 2.

(30% Sync), for Control Characteristics.

P-P

0 - 5 V

DC

DC

DC

See Figure 3

Luminance Gain Control Range Luminance Input: 0.5V

(30% Sync), VC = 0.5V - 5V measure

P-P

32 dB

Pin 18 black level to maximum white level. See Figure 4.

RGB Output Swing Luminance Input: 0.5V

(30% Sync), VC = 5V, read black

P-P

4V

level to peak white. See Figures 5 and 6.

CHROMlNANCE SECTION

Input Impedance (Terminal 4) See Figures 7 and 8. 4.5 kΩ

5pF

Chroma Channel Input Voltage Chroma 220 mV

Burst 100 mV

ACC Range +6 - (-20) dB

Input Burst Level for Kill (Note 1) Adjust chroma input Pin 4 until Pin 2 ≤25mV

P-P

.

10 mV

Measure Burst level at Pin 4.

Contrast Control Chroma/Luma Tracking Chroma Input: Burst = 100mV

Luminance Input: 0.35V

Pin 18 = 2V

. VC is adjusted for luminance at Pin 18 = 2V

P-P

P-P

, Chroma = 220mV

P-P

P-P

, VS adjusted for Chroma at

.

P-P

±5%

,

VC is again adjusted for luminance of +6 and -9dB.

Then read chroma percentage difference. See Figure 9.

7-57

P-P

P-P

P-P

P-P

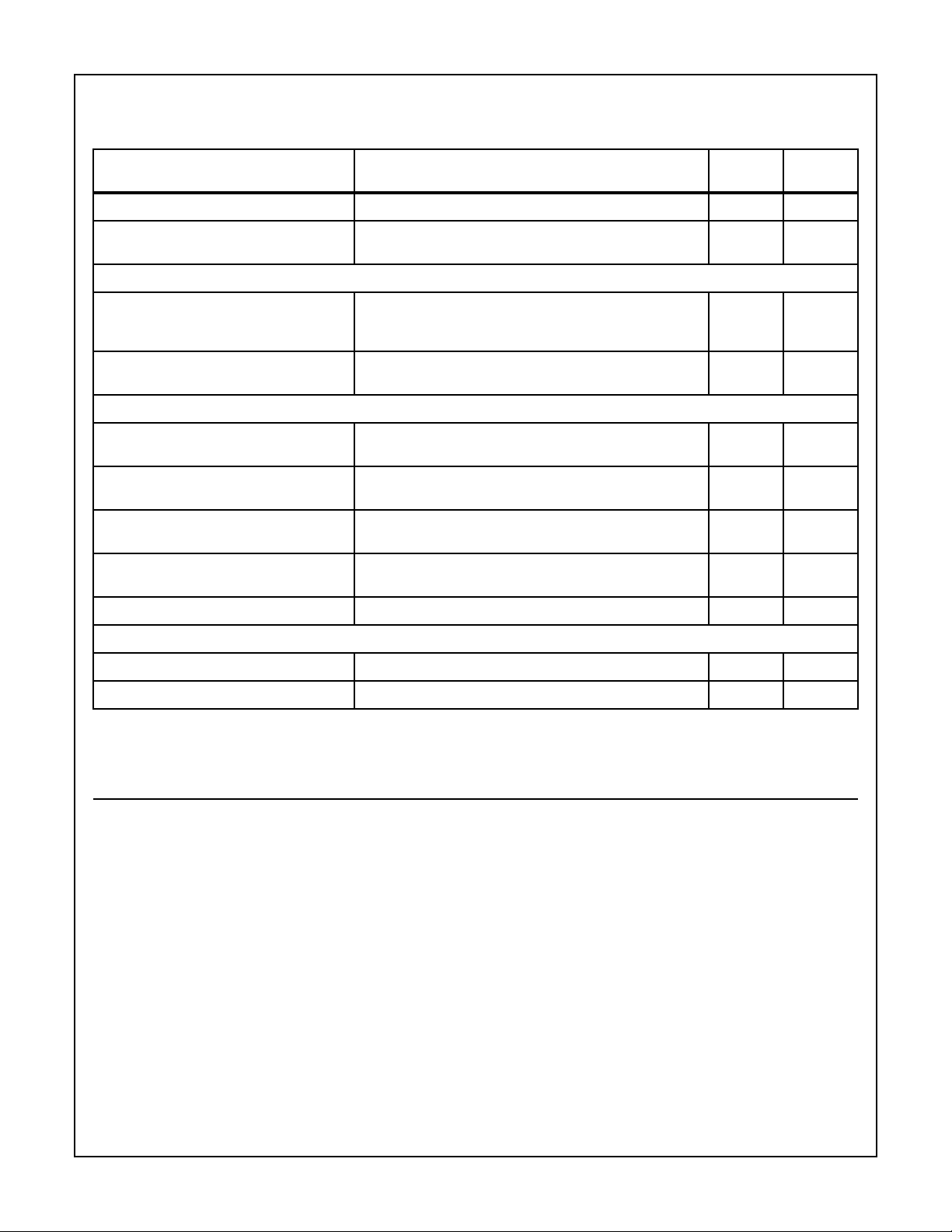

Specifications CA3194

Electrical Specifications T

PARAMETER TEST CONDITIONS

Saturation Control Range (Terminal 3) For control characteristic, see Figure 10. 0 - 5 V

Maximum Chroma Output V oltage (Terminal 2) Chroma Input: Burst = 100mV

OSCILLATOR SECTION

Pull-In Range Chroma Input: Burst = 100mV

Static Phase Error 2 Deg./

DEMODULATOR SECTION

R-Y Demodulator Conversion Gain Chroma Input: Burst =100mV, Chroma = 220mV

B-Y Demodulator Conversion Gain Chroma Input: Burst = 100mV

G-Y/B-Y Matrix Ratio Chroma Input: Burst =100mV

= +25oC, VCC = 12V, VS = 2.85V, VC = 2.85V, VAB = VPB = VCC, VB adjusted for V18 = 6.3V, CX adjusted

A

for F

These conditions exist except as otherwise noted. See Figure 19 for test circuit (Continued)

= 4.43361875MHz, Sandcastle: VBG = 8.0V, V

OSC

Adjust VC and VS for maximum Pin 2 output.

Adjust CX for HI/LO f

Apply signal to lock.

Adjust VC for V18 = 1V. Read V15. Calculate V18/V15.

Calculate V16/V14. VC remains as for R-Y gain.

read V17 and V16, Calculate V17/V16. VC remains as above.

without Chroma signal.

OSC

P-P

= 3.5V - Burst Gate centered on Burst.

BLANK

, Chroma = 220mV

P-P

, Chroma = 220mV

P-P

P-P

, Uø. Read V16 and V14.

P-P

, Chroma = 220mV

P-P

P-P

,Vø.

P-P

.

.

, Uø

TYPICAL

VALUE UNITS

2.5 V

±500 Hz

100Hz

10 Ratio

18 Ratio

0.2 Ratio

DC

P-P

G-Y/R-Y Matrix Ratio Chroma Input: Burst =100mV

Read V17 and V18. Calculate V17/V18. VC remains as above.

Sub-Carrier and Harmonic Content at Outputs No Chroma or Luma Input. Read residual carrier at outputs. 30 mV

SANDCASTLE PULSE

Horizontal and Vertical Blanking Pedestal 2 - 5 V

Burst Gate Pulse 6.5 - V

NOTES:

1. If a different value is desired, see the Threshold Adjustment Circuit of Figure 17.

2. Use of the circuit of Figure 18 is suggested to prevent increased color saturation at low level RF signals.

3. The reference voltage can be adjusted by changing the values of the voltage divider.

Circuit Description

The chroma signal is externally separated from the video

signal by means of a bandpass or high-pass filter and

applied to pin 4. The burst is separated in the first chroma

stage and applied to the synchronous detector which provides information to sample-and-hold circuits for APC

(phase-locked loop), ACC (automatic chroma gain control)

and identification and killing. The 4.43MHz crystal oscillator

is phase-locked to the burst and provides 0 degrees and 90

degrees (via an external phase shifter) carriers to the

chroma demodulators. The burst and chroma amplitude at

the output of the first chroma amplifier is kept constant by

(See Block Diagram and Figure 20)

A buffer stage drives the exter nal PAL delay line. The separated U and V signals are applied to pins 14 and 15, respectively, and demodulated. A standard G-Y matrix is included

on the chip.

The luminance signal passes through the subcarrier trap

and through the luminance delay line and enters the chip at

pin 20. Contrast and brightness control is provided before

the luminance signal is combined with the color difference

signals in the Y matrix. Average and peak beam limiting circuits are controlled from pins 24 and 19.

, Chroma = 220mV

P-P

P-P

, Vø.

0.5 Ratio

CC

the automatic gain control.

P-P

V

The second chroma stage provides saturation control (pin 3)

which tracks the contrast control in the luminance channel.

This stage is also used for color killing.

7-58

Loading...

Loading...