Intersil Corporation CA3127 Datasheet

CA3127

August 1996

Features

• Gain Bandwidth Product (fT). . . . . . . . . . . . . . . . >1GHz

• Power Gain. . . . . . . . . . . . . . . . . 30dB (Typ) at 100MHz

• Noise Figure. . . . . . . . . . . . . . . . 3.5dB (Typ) at 100MHz

• Five Independent Transistors on a Common Substrate

Applications

• VHF Amplifiers

• Multifunction Combinations - RF/Mixer/Oscillator

• Sense Amplifiers

• Synchronous Detectors

• VHF Mixers

• IF Converter

• IF Amplifiers

• Synthesizers

• Cascade Amplifiers

High Frequency NPN Transistor Array

Description

The CA3127 consists of five general purpose silicon NPN

transistors on a common monolithic substrate. Each of the

completely isolated transistors exhibits low 1/f noise and a

value of f

from DC to 500MHz. Access is provided to each of the terminals for the individual transistors and a separate substrate

connection has been provided for maximum application fle xibility. The monolithic construction of the CA3127 provides

close electrical and thermal matching of the five transistors.

Ordering Information

NUMBER

(BRAND)

CA3127E -55 to 125 16 Ld PDIP E16.3

CA3127M

(3127)

CA3127M96

(3127)

in excess of 1GHz, making the CA3127 useful

T

PART

TEMP.

RANGE (oC) PACKAGE

-55 to 125 16 Ld SOIC M16.15

-55 to 125 16 Ld SOIC T ape and Reel M16.15

PKG.

NO.

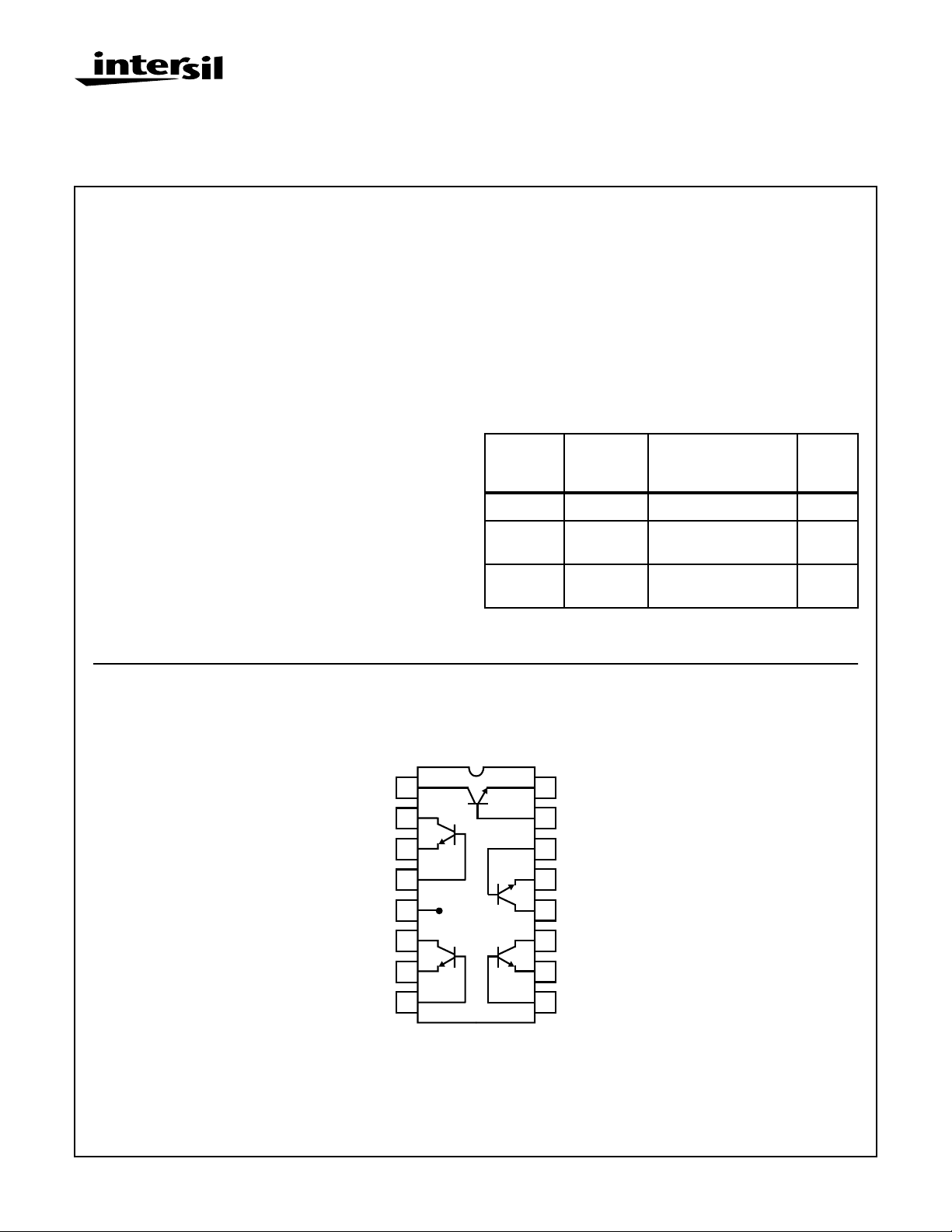

Pinout

SUBSTRATE

1

2

Q

3

4

5

6

Q

7

8

CA3127

(PDIP, SOIC)

TOP VIEW

Q

1

2

3

16

15

14

13

Q

5

12

11

Q

4

10

9

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

5-1

File Number 662.3

CA3127

Absolute Maximum Ratings Thermal Information

The following ratings apply for each transistor in the device

Collector-to-Emitter Voltage, V

Collector-to-Base Voltage, V

Collector-to-Substrate Voltage, V

. . . . . . . . . . . . . . . . . . . . . 15V

CEO

. . . . . . . . . . . . . . . . . . . . . . . 20V

CBO

(Note 1). . . . . . . . . . . . . 20V

CIO

Collector Current, IC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20mA

Operating Conditions

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. The collector of each transistor of the CA3127 is isolated from the substrate by an integr al diode . The substr ate (Terminal 5) must be connected to the most negative point in the external circuit to maintain isolation between transistors and to provide f or normal transistor action.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 2) θJA (oC/W)

PDIP Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

SOIC Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Maximum Power Dissipation, PD (Any One Transistor). . . . . . 85mW

Maximum Junction Temperature (Die) . . . . . . . . . . . . . . . . . . 175oC

Maximum Junction Temperature (Plastic Packages). . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s). . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

Electrical Specifications T

= 25oC

A

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

DC CHARACTERISTICS (For Each Transistor)

Collector-to-Base Breakdown Voltage I

Collector-to-Emitter Breakdown Voltage I

Collector-to-Substrate Breakdown-Voltage I

Emitter-to-Base Breakdown Voltage (Note 3) I

Collector-Cutoff-Current V

Collector-Cutoff-Current V

DC Forward-Current Transfer Ratio V

Base-to-Emitter Voltage V

Collector-to-Emitter Saturation Voltage I

Magnitude of Difference in V

Magnitude of Difference in I

BE

B

= 10µA, IE = 0 20 32 - V

C

= 1mA, IB = 0 15 24 - V

C

= 10µA, IB = 0, IE = 0 20 60 - V

C1

= 10µA, IC = 0 4 5.7 - V

E

= 10V IB = 0 - - 0.5 µA

CE

= 10V, IE = 0 - - 40 nA

CB

= 6V IC = 5mA 35 88 -

CE

= 1mA 40 90 -

I

C

= 0.1mA 35 85 -

I

C

= 6V IC = 5mA 0.71 0.81 0.91 V

CE

= 1mA 0.66 0.76 0.86 V

I

C

= 0.1mA 0.60 0.70 0.80 V

I

C

= 10mA, IB = 1mA - 0.26 0.50 V

C

Q1 and Q2 Matched

VCE = 6V, IC = 1mA

- 0.5 5 mV

- 0.2 3 µA

DYNAMIC CHARACTERISTICS

Noise Figure f = 100kHz, R

Gain-Bandwidth Product V

Collector-to-Base Capacitance V

Collector-to-Substrate Capacitance V

Emitter-to-Base Capacitance V

Voltage Gain V

= 6V, IC = 5mA - 1.15 - GHz

CE

= 6V, f = 1MHz - See

CB

= 6V, f = 1MHz - - pF

CI

= 4V, f = 1MHz - - pF

BE

= 6V, f = 10MHz, RL = 1kΩ, IC = 1mA - 28 - dB

CE

Power Gain Cascode Configuration

Noise Figure - 3.5 - dB

f = 100MHz, V+ = 12V, I

Input Resistance Common-Emitter Configuration

Output Resistance - 4.6 - kΩ

VCE = 6V, IC = 1mA, f = 200 MHz

= 500Ω, IC = 1mA - 2.2 - dB

S

-pF

Fig. 5

27 30 - dB

= 1mA

C

- 400 - Ω

Input Capacitance - 3.7 - pF

Output Capacitance -2-pF

Magnitude of Forward Transadmittance - 24 - mS

NOTE:

3. When used as a zener for reference voltage, the device must not be subjected to more than 0.1mJ of energy from any possible capacitance

or electrostatic discharge in order to prevent degradation of the junction. Maximum operating zener current should be less than 10mA.

5-2

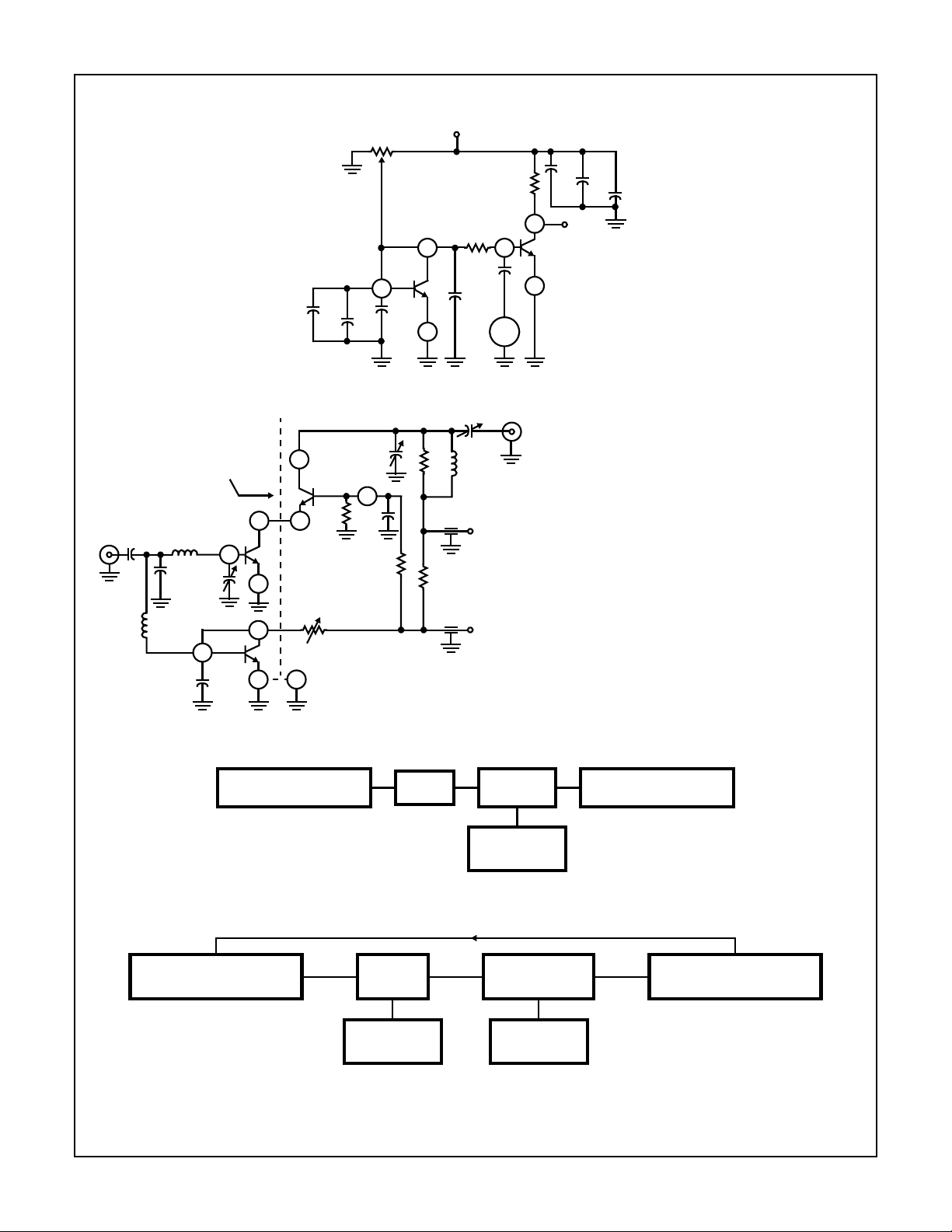

Test Circuits

CA3127

V+

10kΩ

470

pF

L

2

Q

2

3

V

O

0.01

µF

1µF

V

O

2

NOTES:

4. This circuit was chosen because it conveniently represents a close approximation in performance to a properly unilateralized single transistor of this type. The use of

Q3 in a current-mirror configuration facilitates simplified

biasing. The use of the cascode circuit in no way implies

that the transistors cannot be used individually.

1µF

BIAS-CURRENT

ADJ

8

470pF

0.01

µF

6

0.01µF

Q

3

470pF

7

51Ω

V

R

4

GEN

I

FIGURE 1. VOLTAGE-GAIN TEST CIRCUIT USING CURRENT-MIRROR BIASING FOR Q

1.5 - 8pF

C

2

620Ω

25kΩ

(NOTE 5)

14

1000

pF

560Ω

SHIELD

V

I

0.3µH1000pF

1.8pF

(NOTE 5)

OHMITE

Z144

4

C

1

8

1000

pF

12

Q

5

2 13

Q

2

3

6

Q

3

7 5

8.2

kΩ

1000

1000

pF

750Ω

1%

pF

0.47µH

TEST

POINT

+12V

5. E.F. Johnson number 160-104-1 or equivalent.

FIGURE 2. 100MHz POWER-GAIN AND NOISE-FIGURE TEST CIRCUIT

GENERAL RADIO 1021-P1

100MHz GENERATOR

VHF NOISE SOURCE

HEWLETT PACKARD HP343A

FIGURE 3. BLOCK DIAGRAMS OF POWER-GAIN AND NOISE-FIGURE TEST SET-UPS

ATTN

100MHz BOONTON 91C

TEST SET

12V

DC

POWER SUPPLY

RF VOLTMETER

FIGURE 3A. POWER GAIN SET-UP

100MHz 100MHz NOISE FIGURE METER

TEST SET HEWLETT PACKARD HP342A

12V

DC

POWER SUPPLY

POST AMPLIFIER

15V

DC

POWER SUPPLY

FIGURE 3B. NOISE FIGURE SET-UP

5-3

Loading...

Loading...