Intersil Corporation CA3094A, CA3094 Datasheet

CA3094, CA3094A, CA3094B

Data Sheet April 1999 File Number 598.7

30MHz, High Output Current Operational

Transconductance Amplifier (OTA)

The CA3094 is a differential input power control

switch/amplifier with auxiliary circuit features for ease of

programmability. For example, an error or unbalance signal

can be amplified by the CA3094 to provide an on-off signal or

proportional control output signal up to 100mA. This signal is

sufficient to directly drive high current thyristors, relays, DC

loads, or power transistors. The CA3094 has the generic

characteristics of the CA3080 operational amplifier directly

coupled to an integral Darlington power transistor capable of

sinking or driving currents up to 100mA.

The gain of the differential input stage is proportional to the

amplifier bias current (I

variation of the integrated circuit sensitivity with either digital

and/or analogprogramming signals.For example, at anI

of 100µA, a 1mV change at the input will change the output

from 0 to 100µA (typical).

The CA3094 is intended for operation up to 24V and is

especially useful for timing circuits, in automotive equipment,

and in other applications where operation up to 24V is a

primary design requirement (see Figures 28, 29 and 30 in

Typical Applications text). The CA3094A and CA3094B are

like the CA3094 but are intended for operation up to 36V and

44V, respectively (single or dual supply).

), permitting programmable

ABC

ABC

Features

• CA3094E, M for Operation Up to 24V

• CA3094AT, E, M for Operation Up to 36V

• CA3094BT, M for Operation Up to 44V

• Designed for Single or Dual Power Supply

• Programmable: Strobing, Gating, Squelching, AGC

Capabilities

• Can Deliver 3W (Average)or 10W (Peak) to External Load

(in Switching Mode)

• High Power, Single Ended Class A Amplifier will Deliver

Pow er Output of 0.6W (1.6W Device Dissipation)

• Total Harmonic Distortion (THD) at 0.6W in Class A

Operation 1.4% (Typ)

Applications

• Error Signal Detector: Temperature Control with

Thermistor Sensor; Speed Control for Shunt Wound DC

Motor

• Over Current, Over Voltage, Over Temperature Protectors

• Dual Tracking Power Supply with CA3085

• Wide Frequency Range Oscillator

• Analog Timer

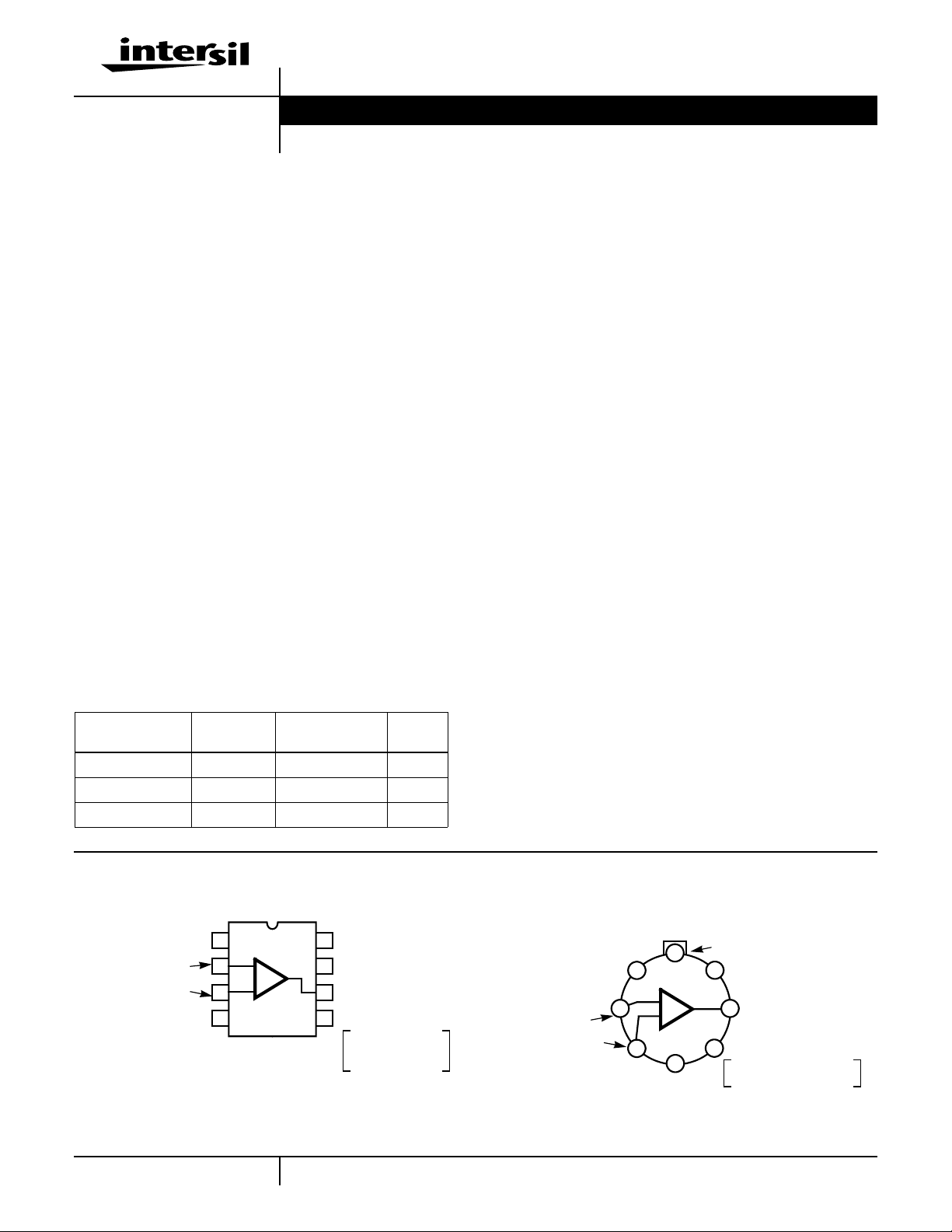

Ordering Information

PART NUMBER

(BRAND)

CA3094AT, BT -55 to 125 8 Pin Metal Can T8.C

CA3094E, AE -55 to 125 8 Ld PDIP E8.3

CA3094M, BM -55 to 125 8 Ld SOIC M8.15

TEMP.

RANGE (oC) PACKAGE

PKG.

Pinouts

CA3094 (PDIP, SOIC)

TOP VIEW

EXT. FREQUENCY

COMPENSATION

OR INHIBIT INPUT

DIFFERENTIAL

VOLTAGE INPUTS

GND (V- IN DUAL

SUPPLY OPERATION)

1

2

3

4

SINK OUTPUT

8

(COLLECTOR)

V+

7

DRIVE OUTPUT

6

(EMITTER)

5

I

CURRENT

ABC

PROGRAMMABLE

INPUT

(STROBE OR AGC)

NO.

• Level Detector

• Alarm Systems

• Voltage Follower

• Ramp Voltage Generator

• High Power Comparator

• Ground Fault Interrupter (GFI) Circuits

CA3094 (METAL CAN)

TOP VIEW

SINK OUTPUT

(COLLECTOR)

EXT. FREQUENCY

COMPENSATION OR

INHIBIT INPUT

2

DIFFERENTIAL

VOLTAGE INPUTS

GND (V- IN DUAL

SUPPLY OPERATION)

NOTE: Pin 4 is connected to case.

8

1

3

4

TAB

7

V+

DRIVE OUTPUT

6

(EMITTER)

5

CURRENT

I

ABC

PROGRAMMABLE INPUT

(STROBE OR AGC)

3-12

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Copyright © Intersil Corporation 1999

CA3094, CA3094A, CA3094B

Absolute Maximum Ratings Thermal Information

Supply Voltage (Between V+ and V- Terminals)

CA3094 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24V

CA3094A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36V

CA3094B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44V

Differential Input Voltage (Terminals 2 and 3, Note 1) . . . . . . . . . 5V

DC Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V+ to V-

Input Current (Terminals 2 and 3) . . . . . . . . . . . . . . . . . . . . . . ±1mA

Amplifier Bias Current (Terminal 5) . . . . . . . . . . . . . . . . . . . . . . 2mA

Average Output Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100mA

Peak Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300mA

Operating Conditions

Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. Exceeding this voltage rating will not damage the device unless the peak input signal current (1mA) is also exceeded.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 2) θJA (oC/W) θJC (oC/W)

PDIP Package . . . . . . . . . . . . . . . . . . . 130 N/A

SOIC Package . . . . . . . . . . . . . . . . . . . 170 N/A

Metal Can Package . . . . . . . . . . . . . . . 175 100

Maximum Junction Temperature (Metal Can Package) . . . . . . .175oC

Maximum Junction Temperature (Plastic Package) . . . . . . . .150oC

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

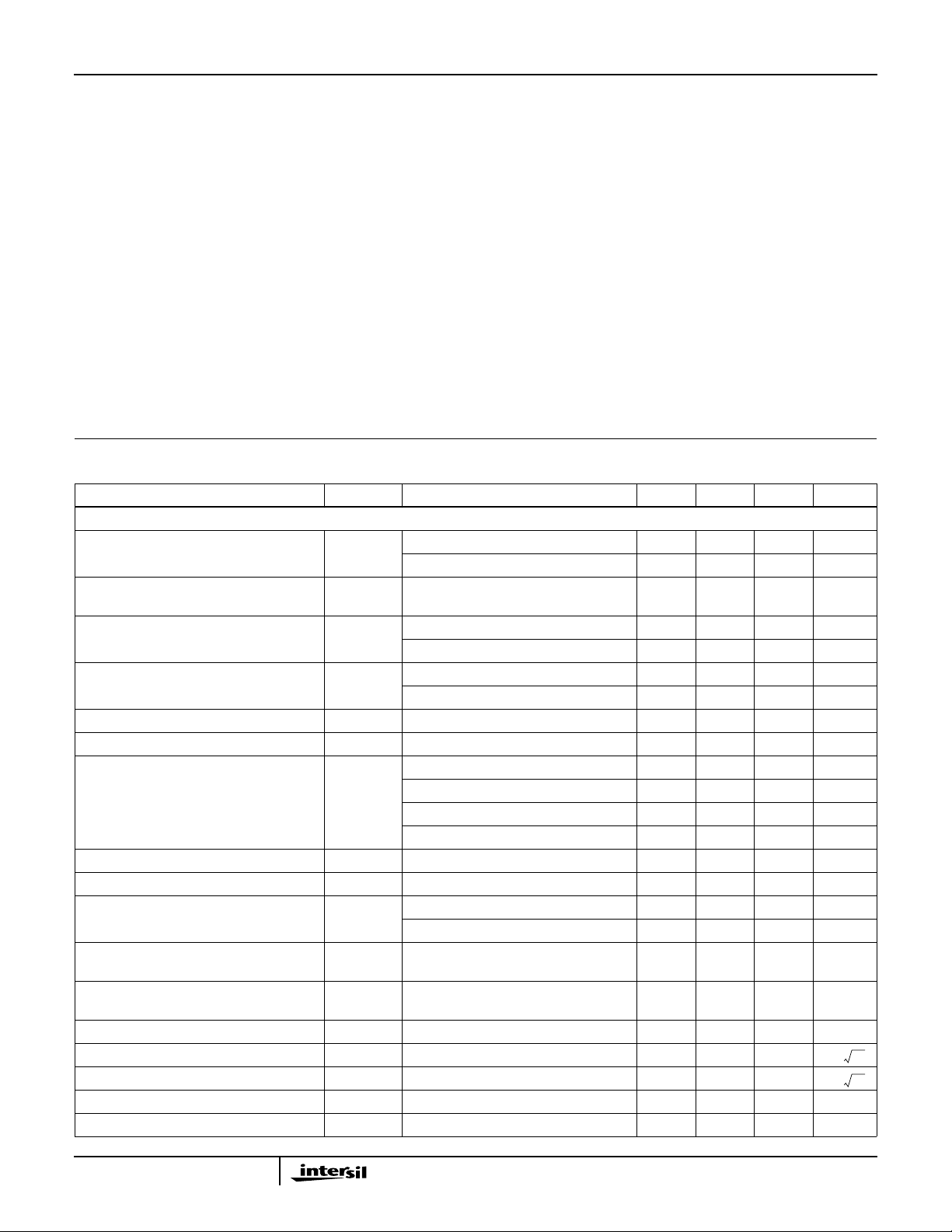

Electrical Specifications T

= 25oC for Equipment Design. Single Supply V+ = 30V, Dual Supply V

A

SUPPLY

= ±15V , I

= 100µA Unless

ABC

Otherwise Specified

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

INPUT PARAMETERS

Input Offset Voltage V

TA = 25oC - 0.4 5.0 mV

IO

TA = 0oC to 70oC - - 7.0 mV

Input Offset Voltage Change |∆VIO| Change in VIO between I

Input Offset Current I

and I

IO

TA = 25oC - 0.02 0.2 µA

ABC

= 5µA

ABC

= 100µA

- 1 8.0 mV

TA = 0oC to 70oC - - 0.3 µA

Input Bias Current I

TA = 25oC - 0.2 0.50 µA

I

TA = 0oC to 70oC - - 0.70 µA

Device Dissipation P

I

D

= 0mA 8 10 12 mW

OUT

Common Mode Rejection Ratio CMRR 70 110 - dB

Common Mode Input Voltage Range V

ICR

V+ = 30V (High) 27 28.8 - V

V- = 0V (Low) 1.0 0.5 - V

V+ = 15V 12 13.8 - V

V- = -15V -14 -14.5 - V

Unity Gain Bandwidth f

Open Loop Bandwidth at -3dB Point BW

Total Harmonic Distortion

THD PD = 220mW - 0.4 - %

(Class A Operation)

Amplifier Bias Voltage

V

ABC

IC = 7.5mA, VCE = 15V, I

T

OLIC

= 7.5mA, VCE = 15V, I

= 500µA - 30 - MHz

ABC

= 500µA - 4 - kHz

ABC

PD = 600mW - 1.4 - %

- 0.68 - V

(Terminal 5 to Terminal 4)

Input Offset Voltage Temperature

∆VIO/∆T-4-µV/oC

Coefficient

Power Supply Rejection ∆VIO/∆V - 15 150 µV/V

1/F Noise Voltage E

1/F Noise Current I

Differential Input Resistance R

Differential Input Capacitance C

f = 10Hz, I

N

f = 10Hz, I

N

I

I

I

= 20µA 0.50 1.0 - MΩ

ABC

f = 1MHz, V+ = 30V - 2.6 - pF

= 50µA - 18 -

ABC

= 50µA - 1.8 -

ABC

nV/ Hz

pA/ Hz

3-13

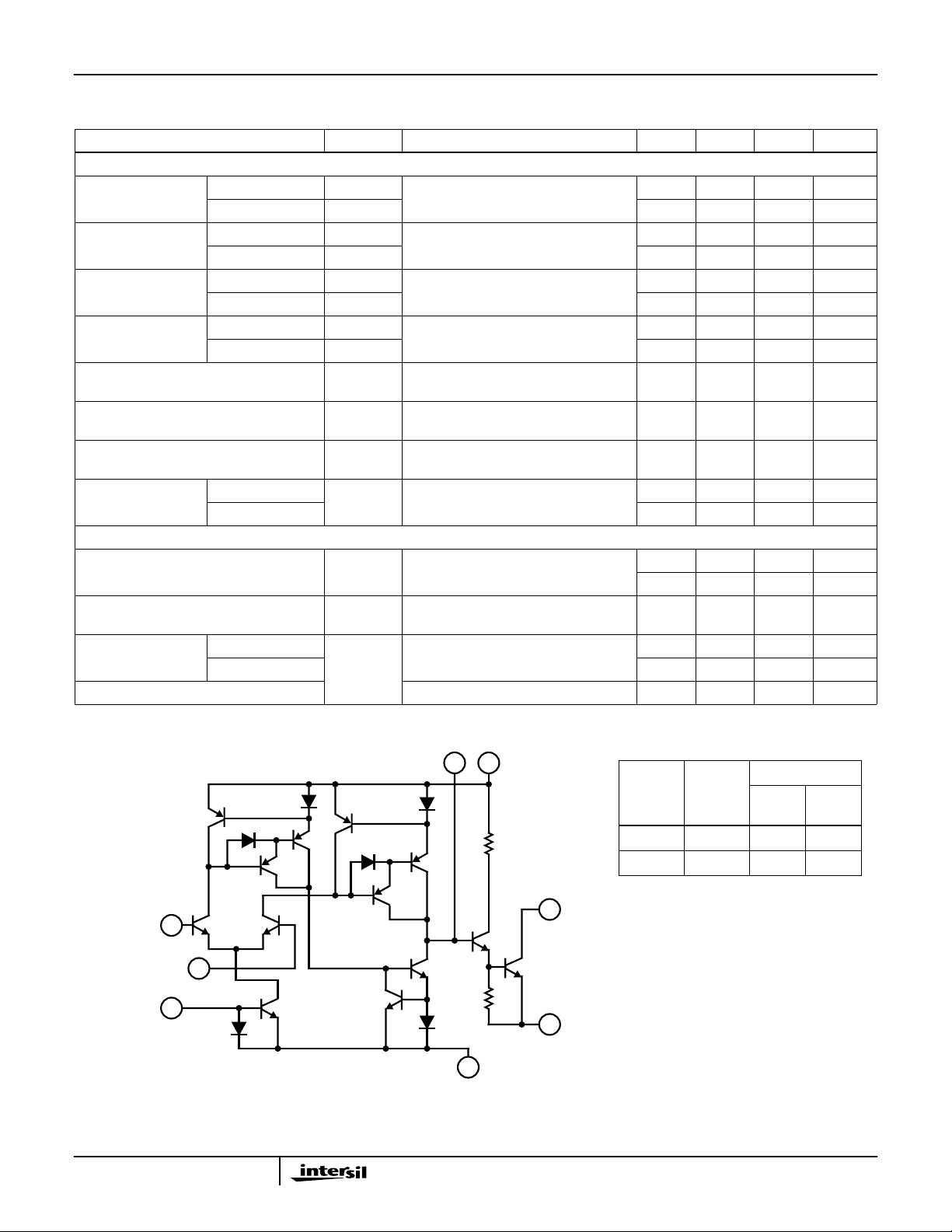

CA3094, CA3094A, CA3094B

Electrical Specifications T

= 25oC for Equipment Design. Single Supply V+ = 30V, Dual Supply V

A

Otherwise Specified (Continued)

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

OUTPUT PARAMETERS (Differential Input Voltage = 1V)

Peak Output Voltage

(Terminal 6)

Peak Output Voltage

(Terminal 6)

Peak Output Voltage

(Terminal 8)

Peak Output Voltage

(Terminal 8)

Collector-to-Emitter Saturation Voltage

(Terminal 8)

Output Leakage Current

With Q13 “ON” VOM+ V+ = 30V, RL = 2kΩ to GND 26 27 - V

With Q13 “OFF” VOM- - 0.01 0.05 V

Positive VOM+ V+ = 15V, V- = -15V, RL = 2kΩ to -15V 11 12 - V

Negative VOM- - -14.99 -14.95 V

With Q13 “OFF” VOM+ V+ = 30V, RL = 2kΩ to 30V 29.95 29.99 - V

With Q13 “ON” VOM- - 0.040 - V

Positive VOM+ V+ = 15V, V- = -15V,

Negative VOM- - -14.96 - V

V

CE(

RL = 2kΩ to 15V

V+ = 30V, IC = 50mA, Terminal 6

)

SAT

Grounded

V+ = 30V - 2 10 µA

(Terminal 6 to Terminal 4)

Composite Small Signal Current Transfer

Ratio (Beta) (Q12 and Q13)

Output Capacitance Terminal 6 C

Terminal 8 - 17 - pF

h

FE

V+ = 30V, VCE = 5V, IC = 50mA 16,000 100,000 -

f = 1MHz, All Remaining Terminals Tied

O

to Terminal 4

TRANSFER PARAMETERS

Voltage Gain A V+ = 30V, I

RL = 2kΩ

Forward Transconductance to

Terminal 1

Slew Rate (Open

Loop)

Positive Slope SR I

Negative Slope - 50 - V/µs

Unity Gain (Non-Inverting Compensated) I

g

M

= 500µA, RL = 2kΩ - 500 - V/µs

ABC

= 500µA, RL = 2kΩ - 0.70 - V/µs

ABC

= 100µA, ∆V

ABC

OUT

= 20V,

SUPPLY

= ±15V , I

= 100µA Unless

ABC

14.95 14.99 - V

- 0.17 0.80 V

- 5.5 - pF

20,000 100,000 - V/V

86 100 - dB

1650 2200 2750 µS

Schematic Diagram

Q

4

DIFFERENTIAL

VOLTAGE

DIFFERENTIAL

AMPLIFIER

BIAS INPUT

INPUT

VOLTAGE

INPUT

I

ABC

2

Q

1

3

5

D

1

COMPENSATION OR INHIBIT INPUT

D

2

Q

2

EXTERNAL FREQUENCY

D

3

Q

7

Q

6

Q

5

Q

3

D

4

Q

Q

11

3-14

V+

71

D

5

R

1

R

47kΩ

4

2kΩ

8

“SINK”

Q

OUTPUT

12

Q

13

2

6

“SOURCE”

(DRIVE)

V-

OUTPUT

Q

8

9

Q

10

D

6

OUTPUT

MODE

“Source” 6 2 3

“Sink” 8 3 2

OUTPUT

TERM

INPUTS

INV

NON-

INV

CA3094, CA3094A, CA3094B

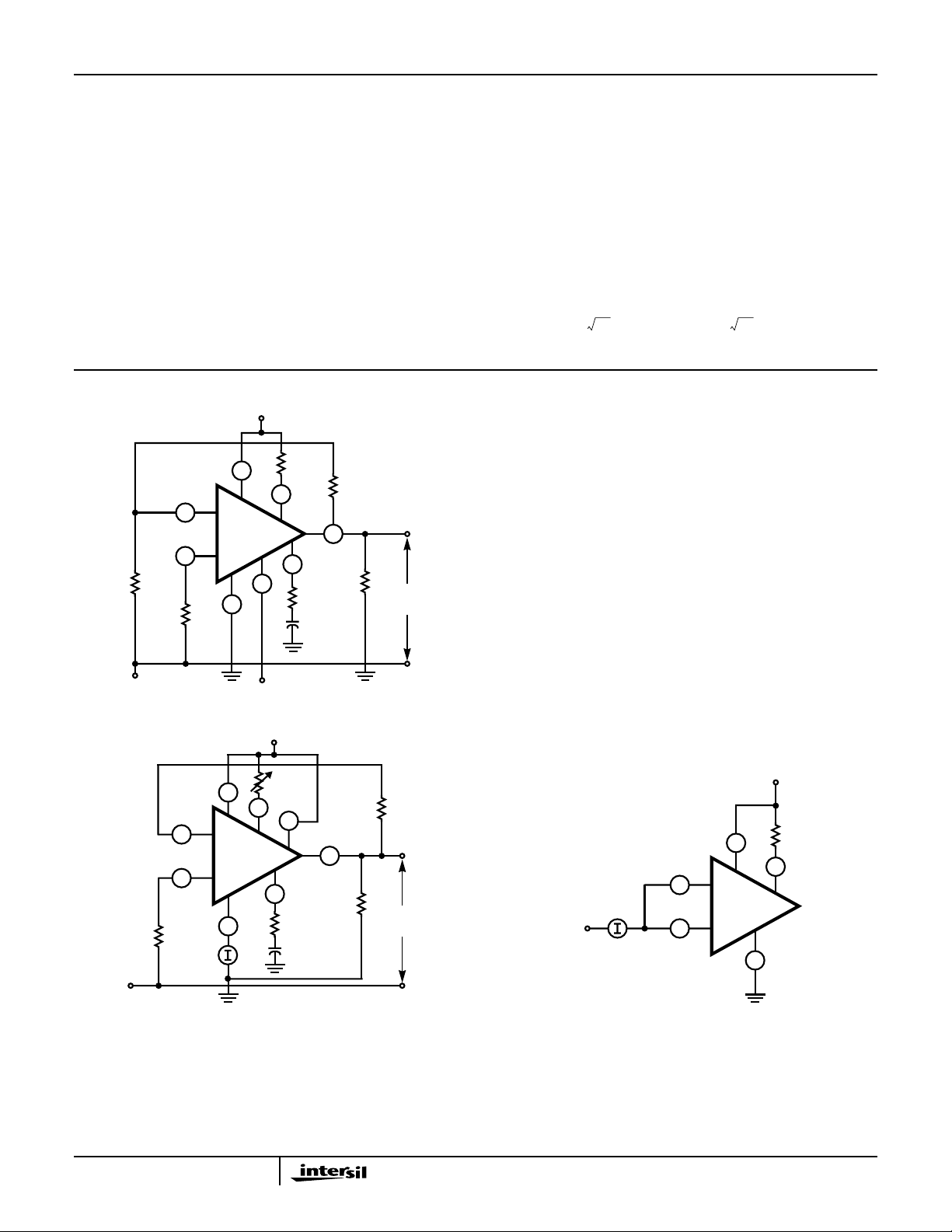

Operating Considerations

The “Sink” Output (Terminal 8) and the “Drive” Output

(Terminal 6) of the CA3094 are not inherently current (or

power) limited. Therefore, if a load is connected between

Terminal 6 and Terminal 4 (V- or Ground), it is important to

connect a current limiting resistor between Terminal 8 and

Terminal 7 (V+) to protect transistor Q13 under shorted load

conditions. Similarly,if a load is connected between Terminal

8 and Terminal 7 (V+), the current limiting resistor should be

connected between Terminal 6 and Terminal 4 or ground. In

circuit applications where the emitter of the output transistor

is not connected to the most negative potential in the

system, it is recommended that a 100Ω current limiting

resistor be inserted between Terminal 7 and the V+ supply.

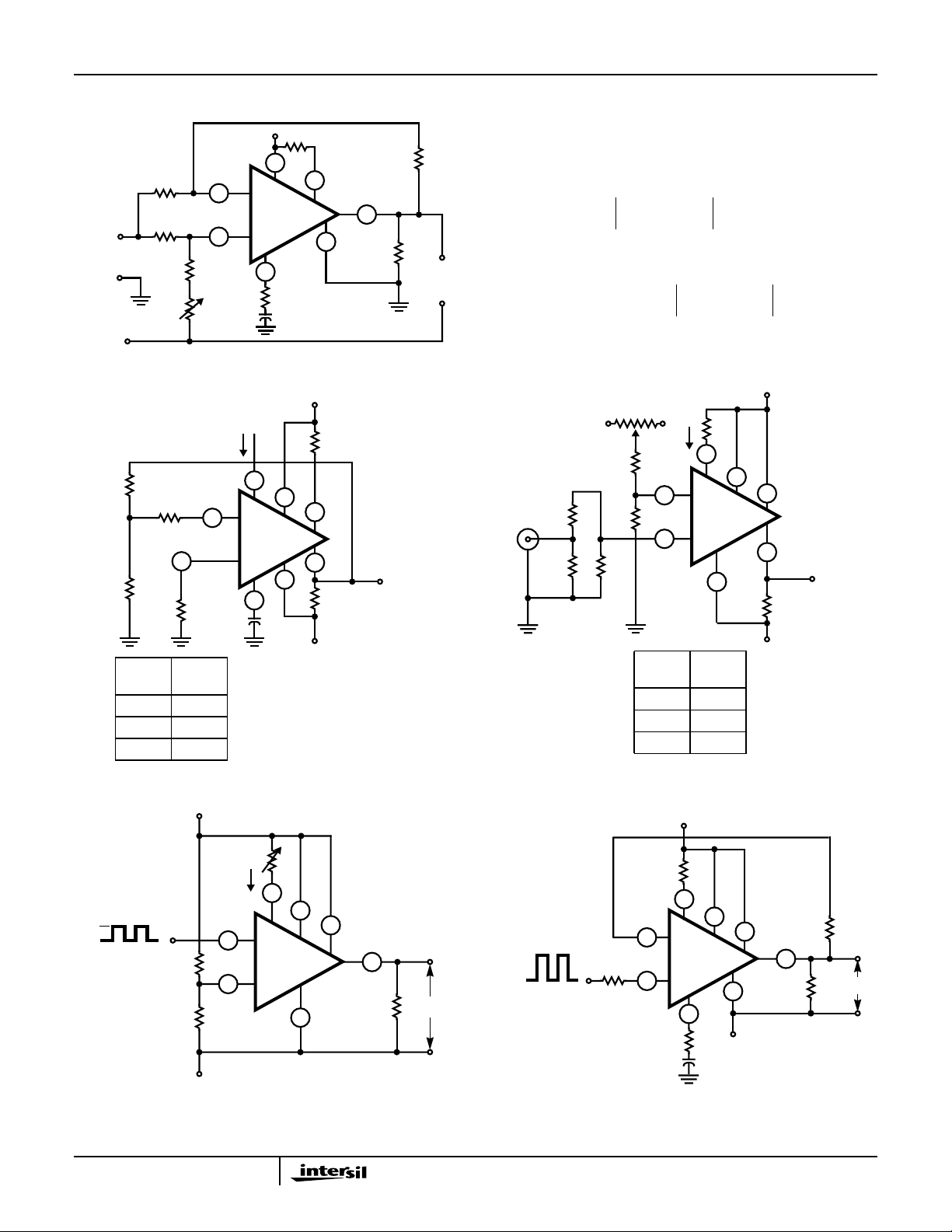

Test Circuits

30V

300kΩ

1kΩ

100pF

6

10kΩ

9.9kΩ

E

OUT

5

1

8

30V

100Ω

15V

100Ω

7

2

CA3094

3

4

1/F Noise Measurement Circuit

When using the CA3094, A, or B audio amplifier circuits, it is

frequently necessary to consider the noise performance of the

device.Noise measurements are made in the circuit shown in

Figure 20. This circuit is a 30dB, non-inverting amplifier with

emitter follower output and phase compensation from

Terminal 2 to ground. Source resistors (R

) are set to 0Ω or

S

1MΩ for E noise and I noise measurements, respectiv ely.

These measurements are made at frequencies of 10Hz,

100Hz and 1kHz with a 1Hz measurement bandwidth. Typical

values for 1/f noise at 10Hz and 50µA I

EN18nV Hz⁄= IN1.8pA Hz⁄=

NOTES:

3. Input Offset Voltage: .

4. For Power Supply Rejection Test: (1) vary V+ by -2V; then (2)

vary V- by +2V.

5. Equations:

(1)

V+ Rejection

(2)

V- Rejection

6. Power Supply Rejection: .

and .

E

IO

200

dB()20

200

-----------------=

OUT

100

V

E0OUT E1OUT–

------------------------------------------------ -=

E0OUT E2OUT–

------------------------------------------------ -=

are:

ABC

1

---------------------------------------------

log=

V

REJECTION

†

† Maximum Reading of Step 1 or Step 2

FIGURE 1. INPUT OFFSET VOLTAGE AND POWER SUPPLY REJECTION TEST CIRCUIT

30V

R

5

1

8. I

ABC

8

220Ω

0.001µF

OS

6

150kΩ

--------------------------------=

10

E

6

15V

NOTES:

7. P

DISSIPATION

2

3

1MΩ

= (V+)(I)

7

CA3094

4

FIGURE 2. INPUT OFFSET CURRENT TEST CIRCUIT

OUT

VOLTS

---------------------

AMPS

1MΩ

E

OUT

30V

300kΩ

5

4

15V

NOTE: I

7

2

-

CA3094A

+

3

I

-- -=

I

2

FIGURE 3. INPUT BIAS CURRENT TEST CIRCUIT

3-15

Test Circuits (Continued)

30V

100Ω

100Ω

V

CMR

0.8V TO 27.2V

15V

2

3

9.9kΩ

200Ω

FIGURE 4. COMMON MODE RANGE AND REJECTION RATIO TEST CIRCUIT

7

-

CA3094

+

1

1kΩ

100pF

4.7kΩ

CA3094, CA3094A, CA3094B

10kΩ

8

6

4

10kΩ

E

OUT

NOTES:

9. .

CMRR

100 26V×

=

--------------------------------------------

E

–

2OUTE1OUT

10. Input Voltage Range for CMRR = 1V to 27V.

11. .

CMRR (dB) 20

100 26V×

log=

--------------------------------------------

E

2OUTE1OUT

–

3.6kΩ

120Ω

I

ABC

R

S

(NOTE)

3

R

S

(NOTE)

I

(µA)

ABC

C

COMP

(pF)

50

50 50

5

7

2

-

CA3094A

+

4

1

C

C

NOTE:

RS= 1MΩ

(1/F Noise Current Test).

RS= 0Ω

(1/F Noise Voltage Test).

500 500

FIGURE 5. 1/F NOISE TEST CIRCUIT

+15V

8

6

+15V

500Ω

3kΩ

-15V

OUTPUT

(RMS)

+15V

7

8

6

OUTPUT

R

= 2kΩ

L

-15V

10kΩ

91Ω

100Ω 10Ω

10kΩ

10Ω

R

(Ω)

+15V-15V

R

S

5

I

ABC

2

-

CA3094A

3

+

4

I

S

ABC

(µA)

56K 500

560K 50

56M 5

FIGURE 6. OPEN LOOP GAIN vs FREQUENCY TEST CIRCUIT

+15V

I

ABC

5

2V

0V

2

13kΩ

3

15kΩ

-15V

7

-

CA3094A

+

4

FIGURE 7. OPEN LOOP SLEW RATE vs I

3-16

8

6

2kΩ

TEST CIRCUIT

ABC

E

OUT

56kΩ

5

±10V

10kΩ

2

3

220Ω

0.001µF

-

CA3094A

+

1

7

8

4

-15V

10kΩ

6

2kΩ

FIGURE 8. SLEW RATEvs NON-INVERTING UNITY GAIN

TEST CIRCUIT

E

OUT

Loading...

Loading...