Intersil Corporation CA3083M96, CA3083M, CA3083 Datasheet

CA3083

Data Sheet September 1998 File Number 481.4

General Purpose High Current NPN

Transistor Array

The CA3083 is a versatile array of five high current (to

100mA) NPN transistors on a common monolithic substrate.

In addition, two of these transistors (Q

and Q2) are

1

matched at low current (i.e., 1mA) for applications in which

offset parameters are of special importance.

Independent connections for each transistor plus a separate

terminal for thesubstratepermit maximum flexibility in circuit

design

.

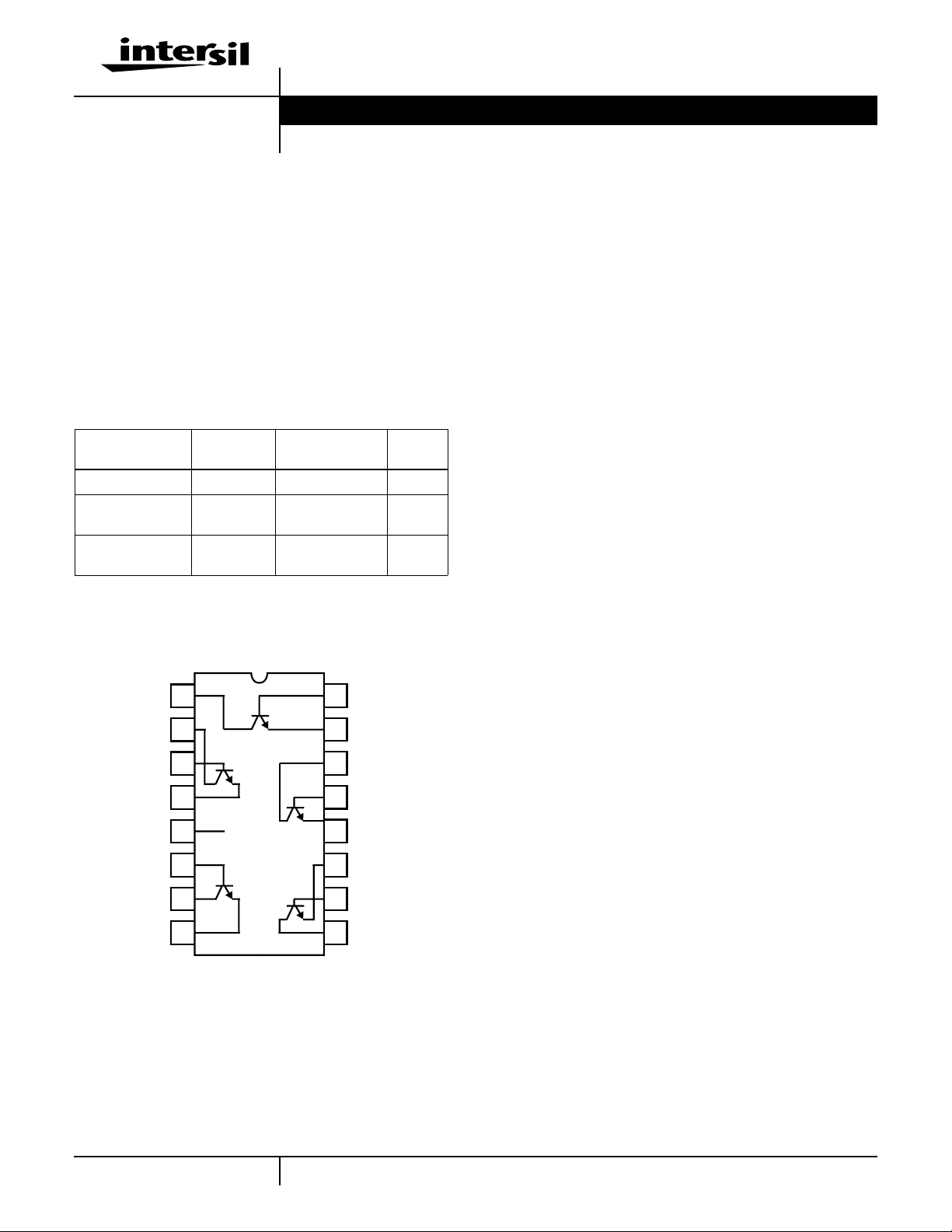

Ordering Information

PART NUMBER

(BRAND)

CA3083 -55 to 125 16 Ld PDIP E16.3

CA3083M

(3083)

CA3083M96

(3083)

TEMP.

RANGE (oC) PACKAGE

-55 to 125 16 Ld SOIC M16.15

-55 to 125 16 Ld SOIC Tape

and Reel

PKG.

M16.15

NO.

Pinout

CA3083

(PDIP, SOIC)

TOP VIEW

Features

• High IC . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100mA (Max)

•Low V

• Matched Pair (Q

-V

IO

-I

IO

(at 50mA). . . . . . . . . . . . . . . . . . 0.7V (Max)

CE sat

and Q2)

1

(VBE Match). . . . . . . . . . . . . . . . . . . . ±5mV (Max)

(at 1mA). . . . . . . . . . . . . . . . . . . . . . . . 2.5µA (Max)

• 5 Independent Transistors Plus Separate Substrate

Connection

Applications

• Signal Processing and Switching Systems Operating from

DC to VHF

• Lamp and Relay Driver

• Differential Amplifier

• Temperature Compensated Amplifier

• Thyristor Firing

• See Application Note AN5296 “Applications of the

CA3018 Circuit Transistor Array” for Suggested

Applications

SUBSTRATE

1

2

3

4

5

6

7

8

Q

1

Q

2

Q

3

Q

4

16

15

14

13

Q

5

12

11

10

9

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143

| Copyright © Intersil Corporation 1999

CA3083

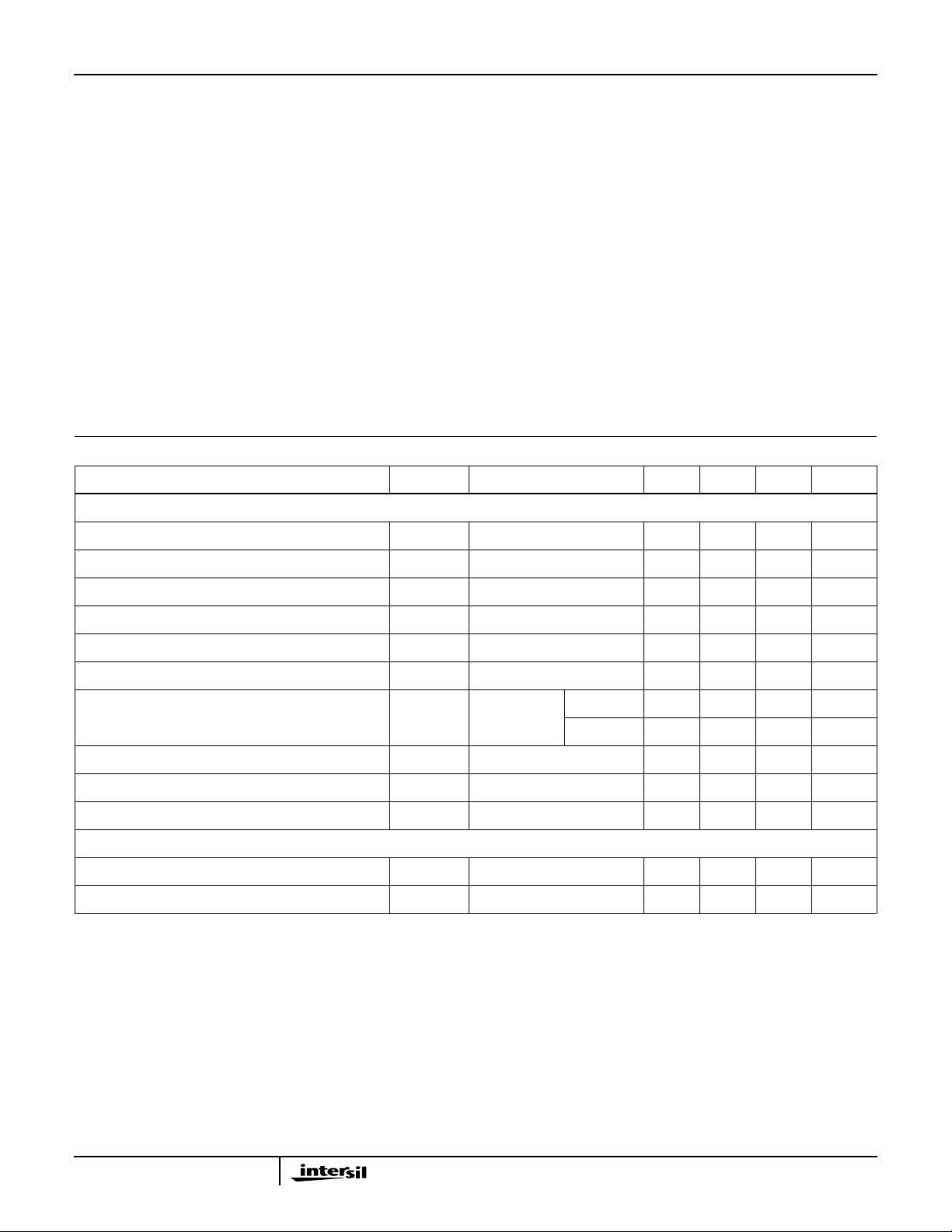

Absolute Maximum Ratings Thermal Information

The following ratings apply for each transistor in the device:

Collector-to-Emitter Voltage, V

Collector-to-Base Voltage, V

Collector-to-Substrate Voltage, V

Emitter-to-Base Voltage, V

Collector Current (I

Base Current (I

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100mA

C

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20mA

B

. . . . . . . . . . . . . . . . . . . . . . 15V

CEO

. . . . . . . . . . . . . . . . . . . . . . . . 20V

CBO

(Note 1). . . . . . . . . . . . . . 20V

CIO

. . . . . . . . . . . . . . . . . . . . . . . . . . 5V

EBO

Operating Conditions

Temperature Range. . . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

1. The collector of each transistor of the CA3083 is isolated from the substrate by an integral diode. The substrate must be connected to a voltage

which is more negative than any collector voltage in order to maintain isolation between transistors and provide normal transistor action. Toavoid

undesired coupling between transistors, the substrate Terminal (5) should be maintained at either DC or signal (AC) ground. A suitable bypass

capacitor can be used to establish a signal ground.

2. θJA is measured with the component mounted on an evaluation PC board in free air.

Thermal Resistance (Typical, Note 2) θJA (oC/W) θJC (oC/W)

PDIP Package . . . . . . . . . . . . . . . . . . . 135 N/A

SOIC Package . . . . . . . . . . . . . . . . . . . 200 N/A

Maximum Power Dissipation (Any One Transistor) . . . . . . . 500mW

Maximum Junction Temperature (Plastic Package) . . . . . . . 150

o

Maximum Storage Temperature Range. . . . . . . . . . -65oC to 150oC

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

C

Electrical Specifications For Equipment Design, T

= 25oC

A

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

FOR EACH TRANSISTOR

Collector-to-Base Breakdown Voltage V

Collector-to-Emitter Breakdown Voltage V

Collector-to-Substrate Breakdown Voltage V

Emitter-to-Base Breakdown Voltage V

(BR)CBOIC

(BR)CEOIC

(BR)CIOICI

(BR)EBOIE

Collector-Cutoff-Current I

Collector-Cutoff-Current I

DC Forward-Current Tr ansf er Ratio (Note 3) (Figure 1) h

CEO

CBO

FE

= 100µA, IE = 0 20 60 - V

= 1mA, IB = 0 15 24 - V

= 100µA, IB = 0, IE = 0 20 60 - V

= 500µA, IC = 0 5 6.9 - V

VCE = 10V, IB = 0 - - 10 µA

VCB = 10V, IE = 0 - - 1 µA

VCE = 3V IC = 10mA 40 76 -

IC = 50mA 40 75 Base-to-Emitter Voltage (Figure 2) V

Collector-to-Emitter Saturation V oltage (Figures 3, 4) V

CE SATIC

Gain Bandwidth Product f

BE

VCE = 3V, IC = 10mA 0.65 0.74 0.85 V

= 50mA, IB = 5mA - 0.40 0.70 V

VCE = 3V, IC = 10mA - 450 - MHz

T

FOR TRANSISTORS Q1 AND Q2(As a Differential Amplifier)

Absolute Input Offset Voltage (Figure 6) |VIO|VCE = 3V, IC = 1mA - 1.2 5 mV

Absolute Input Offset Current (Figure 7) |IIO|VCE = 3V, IC = 1mA - 0.7 2.5 µA

NOTE:

3. Actual forcing current is via the emitter for this test.

2

Loading...

Loading...