®

www.BDTIC.com/Intersil

BBT3821

Data Sheet July 20, 2005

Octal 2.488Gbps to 3.187Gbps/

Lane Retimer

Features

• 8 Lanes of Clock & Data Recovery and Retiming; 4 in

Each Direction

• Differential Input/Output

• Wide Operating Data Rate Range: 2.488Gbps to

3.1875Gbps, and 1.244Gbps to 1.59325Gbps

• Ultra Low-Power Operation (195mW typical per lane,

1550mW typical total consumption)

• Low Power Version Available for LX4 Applications

• 17mm Square Low Profile 192 pin 1.0mm Pitch EBGA

Package

• Compliant to the IEEE 802.3 10GBASE-LX4(WWDM),

10GBASE-CX4, and XAUI Specifications

• Reset Jitter Domain

• Meets 802.3ae and 802.3ak Jitter Requirements with

Significant Margin

• Received Data Aligned to Local Reference Clock for

Retransmission

• Increase Driving Distance

• LX4: Up to 40 inches of FR-4 Traces or 500 Meters of

MMF Fiber at 3.1875Gbps

• CX4: Over 15 meters of Compatible Cable

• Deskewing and Lane-to-Lane Alignment

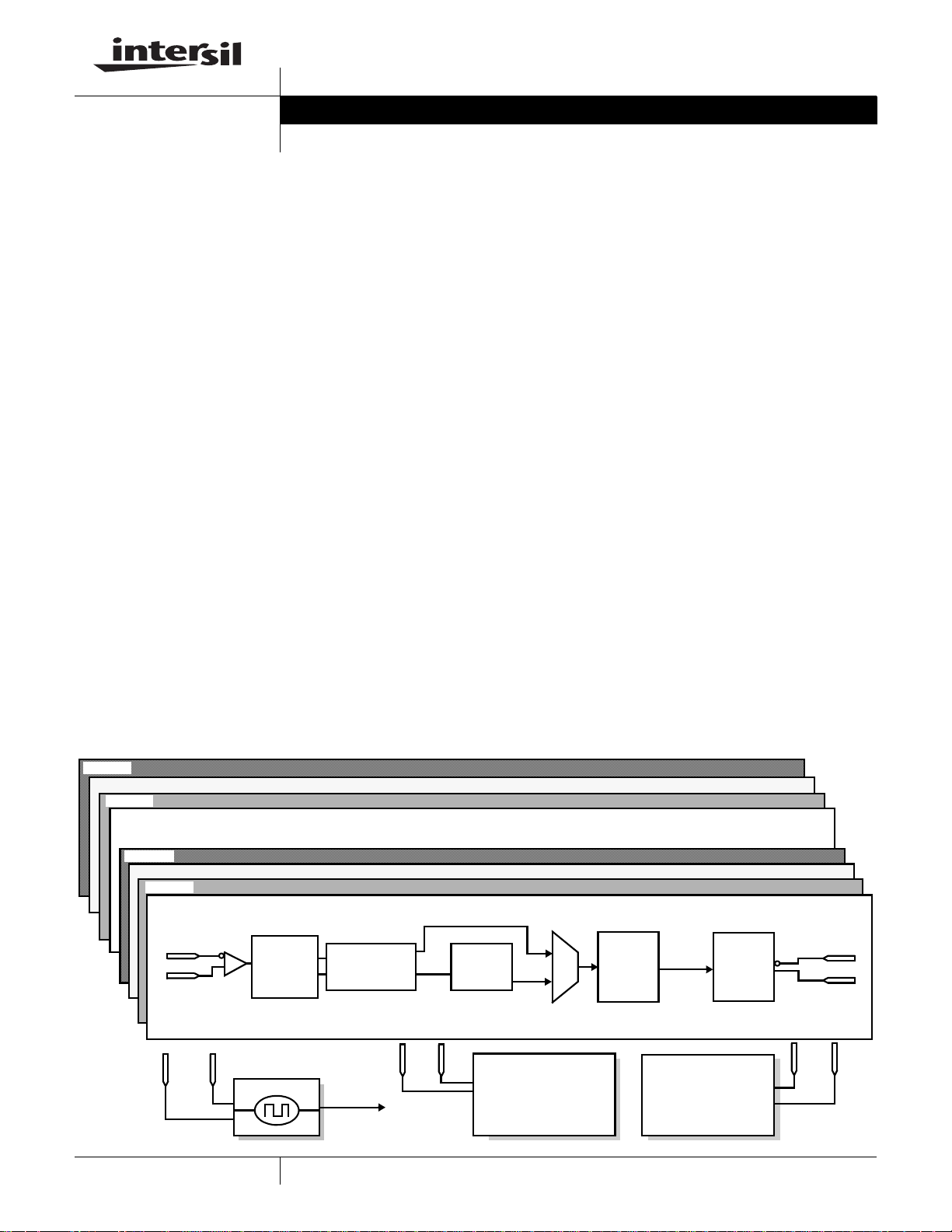

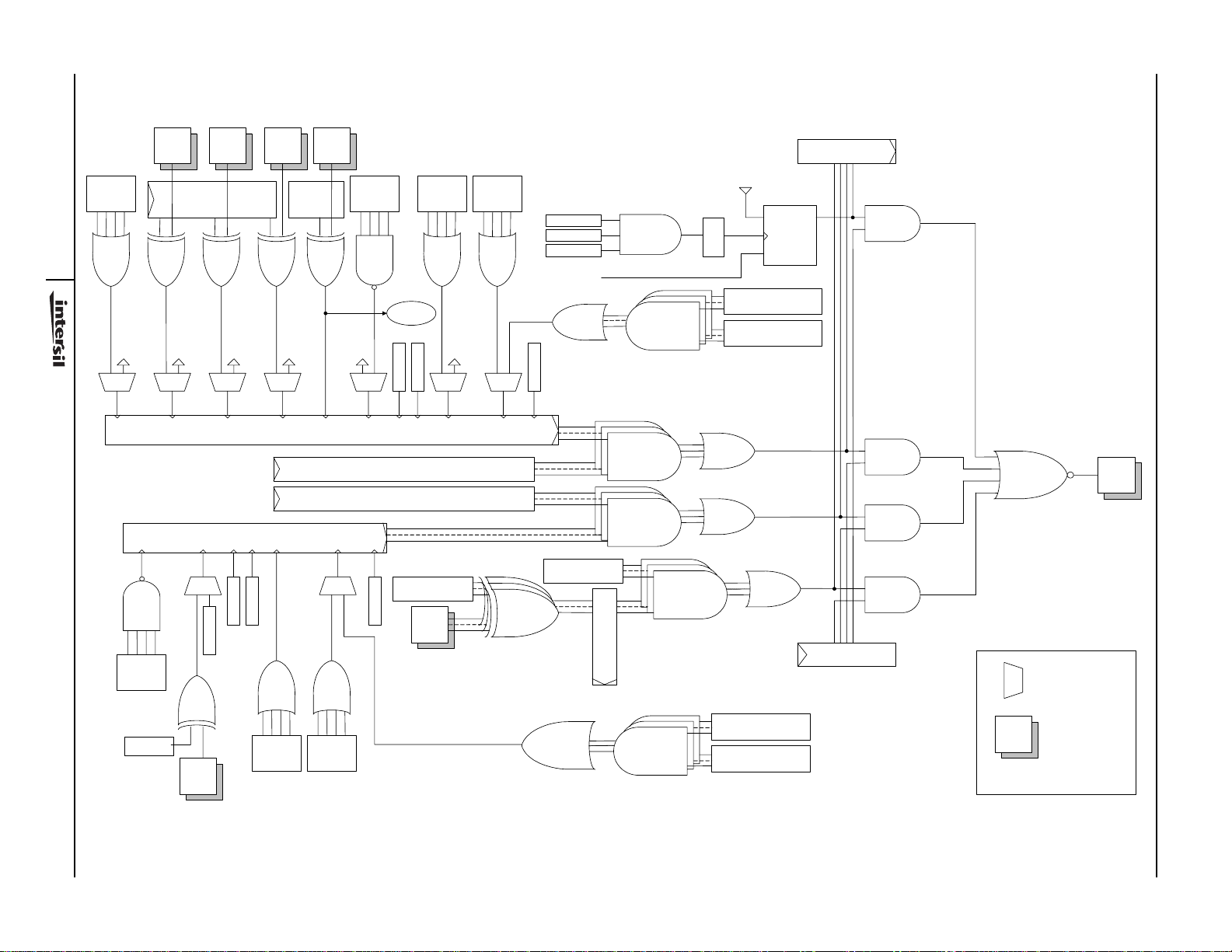

Figure 1. FUNCTIONAL BLOCK DIAGRAM

FN7483.2

• 0.13mm Pure-Digital CMOS Technology

• 1.5V Core Supply, Control I/O 2.5V Tolerant

• Clock Compensation

• Tx/Rx Rate Matching via IDLE Insertion/Deletion up to

±100ppm Clock Difference

• Receive Signal Detect and 16 Levels of Receiver

Equalization for Media Compensation

• CML CX4 Transmission Output with 16 Settable Levels of

Pre-Emphasis, Eight on XAUI Side

• Single-Ended or Differential Input Lower-Speed Reference

Clock

• Ease of Testing

• Complete Suite of Ingress-Egress Loopbacks

• Full 802.3ae Pattern Generation and Test, including

CJ PAT & CR PAT

• PRBS (both 2

Error Flags and Count Output

• JTAG and AC-JTAG Boundary Scan

• Long Run Length (512 bit) Frequency Lock Ideal for

Proprietary Encoding Schemes

• Extensive Configuration and Status Reporting via 802.3

Clause 45 Compliant MDC/MDIO Serial Interface

• Automatic Load of BBT3821 Control and all XENPAK

Registers from EEPROM or DOM Circuit

23

-1 and 13458 byte) Built-In Self Tests,

Egress 3

Egress 2

Egress 1

Egress 0

Ingress 3

Ingress 2

Ingress 1

Ingress 0

RX0N

RX0P

RFCP RFCN

Clock &

Data

Recovery

Clock Multiplier

1

Deserializer

and Comma

Detector

3.125G

8B/10B

Decoder

MDCMDIO SDA SCL

MDIO/MDC

Register File

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-352-6832

| Intersil (and design) is a registered trademark of Intersil Americas Inc.

All other trademarks mentioned are the property of their respective owners.

Receive

Parallel

Receive

FIFO

Data

I2C Interface

Copyright Intersil Americas Inc. 2005. All Rights Reserved

8B/10B

Encoder

& Mux

TX0N

TX0P

BBT3821

www.BDTIC.com/Intersil

Table of Contents

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

List of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Receiver Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Loss of Signal Detection, Termination & Equalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Clock and Data Recovery. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Byte Alignment (Code-Group Alignment) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

8b/10b Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Receive FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Deskew (Lane to Lane) Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Clock Compensation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Transmitter Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

8b/10b Encoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Pre-Emphasis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

8b/10b Coding and Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

8 Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

10 Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Error Indications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Loss of Signal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Byte or Lane Synchronization Failure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Channel Fault Indications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Coding Violation, Disparity & FIFO Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Loopback Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

PMA Loopback (1.0.0 & 1.C004.[11:8]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

PHY XS (Serial) Loopback (4.0.14 & 4.C004.[11:8]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

PCS Parallel Network Loopback (3.C004.[3:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

PCS (Parallel) Loopback (4.C004.[3:0] & Optionally 3.0.14) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Serial Test Loopbacks (1.C004.12 & 4.C004.12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Serial Management Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

MDIO Register Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

I2C Space Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

NVR Registers & EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Auto-Configuring Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

DOM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

General Purpose (GPIO) Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

LASI Registers & I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Reading Additional EEPROM Space Via the I2C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Writing EEPROM Space through the I2C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2

BBT3821

www.BDTIC.com/Intersil

Block Writes to EEPROM Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Byte Writes to EEPROM Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

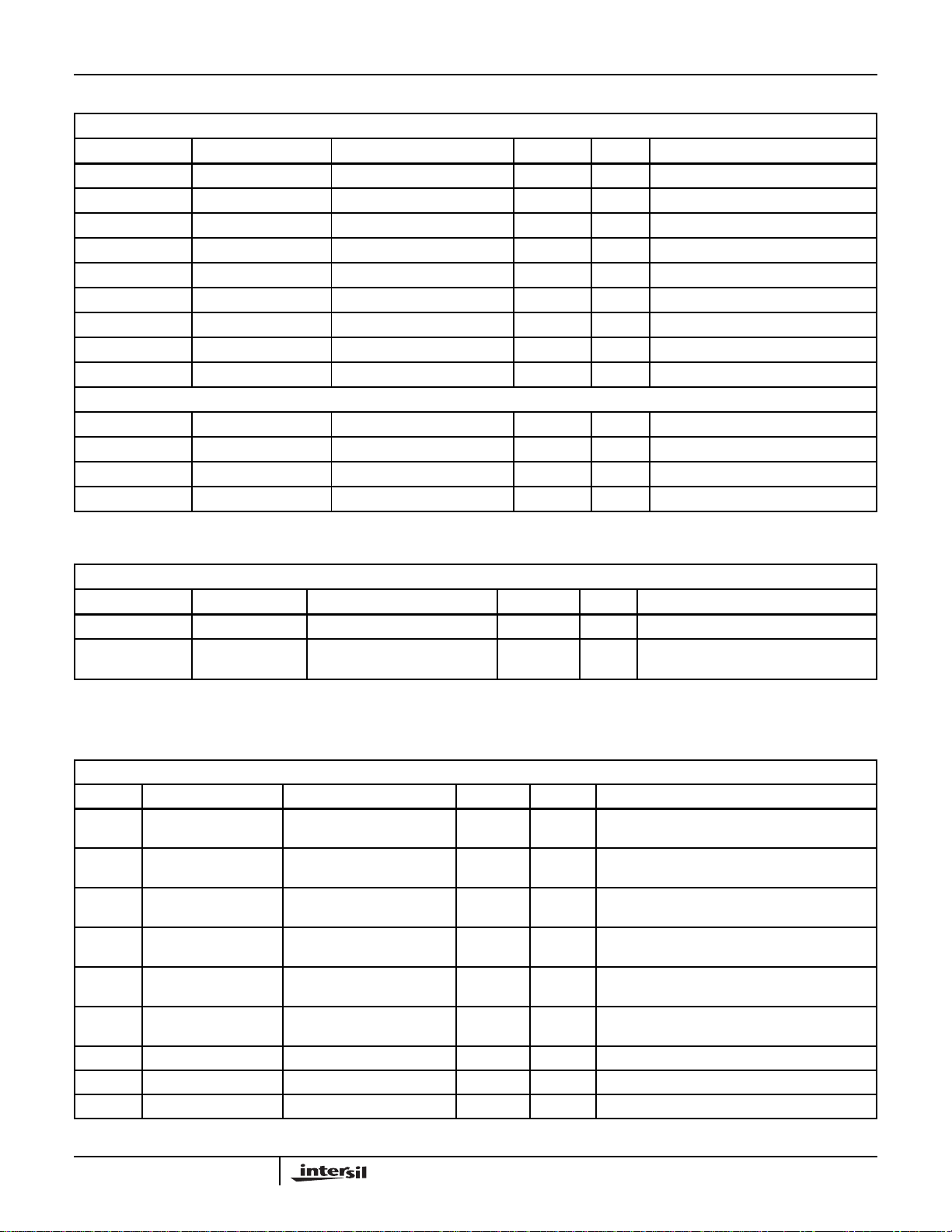

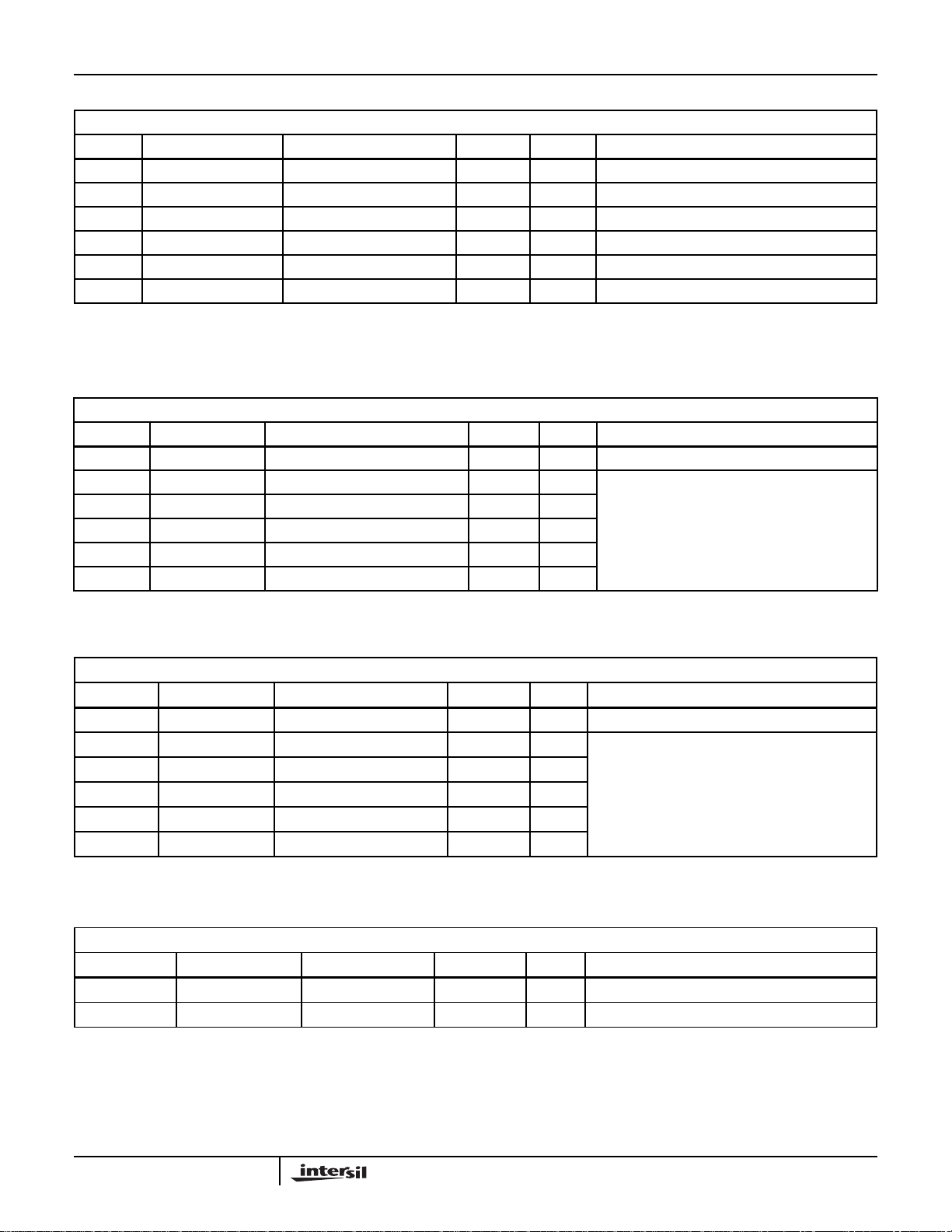

MDIO Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

PMA/PMD DEVICE 1 MDIO REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

IEEE PMA/PMD Registers (1.0 to 1.15/1.000F’h). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

XENPAK-Defined Registers (1.8000’h to 1.8106’h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

XENPAK LASI and DOM Registers (1.9000’h to 1.9007’h & 1.A000’h to 1.A100’h). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Vendor-Specific PMA/PMD and GPIO Registers (1.C001’h to 1.C01D’h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

PCS DEVICE 3 MDIO REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

IEEE PCS Registers (3.0 to 3.25/3.0019’h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Vendor-Specific PCS Registers (3.C000’h to 3.C00E’h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

PHY XS DEVICE 4 MDIO REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

IEEE PHY XS Registers (4.0 to 4.25/4.0019’h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Vendor-Specific PHY XS Registers (4.C000’h to 4.C00B’h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Auto-Configure Register List. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

JTAG & AC-JTAG Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

BIST Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Pin Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Pin Diagram 17x17mm (16*16 Ball Matrix) 192-pin EBGA-B Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

AC and Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Timing Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Applications Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

CX4/LX4/XAUI Re-timer Setup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Recommended Analog Power and Ground Plane Splits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Recommended Power Supply Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

XENPAK/XPAK/X2 Interfacing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

CX4 Interfacing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

LX4 Interfacing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

MDIO/MDC Interfacing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

I2C Interfacing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

DOM Interfacing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

LASI Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

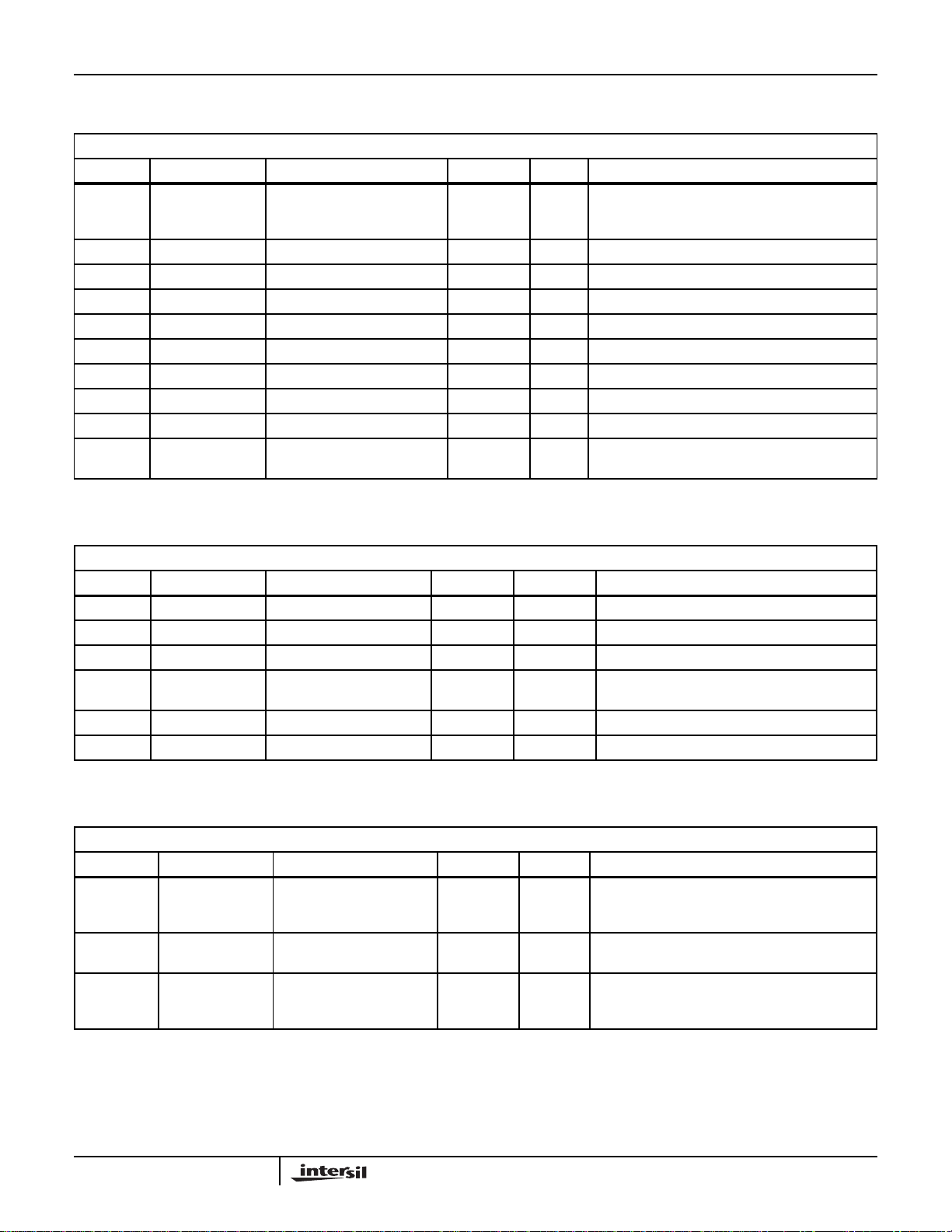

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Intersil Corporation Contact Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

3

BBT3821

www.BDTIC.com/Intersil

List of Figures

Figure 1. FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

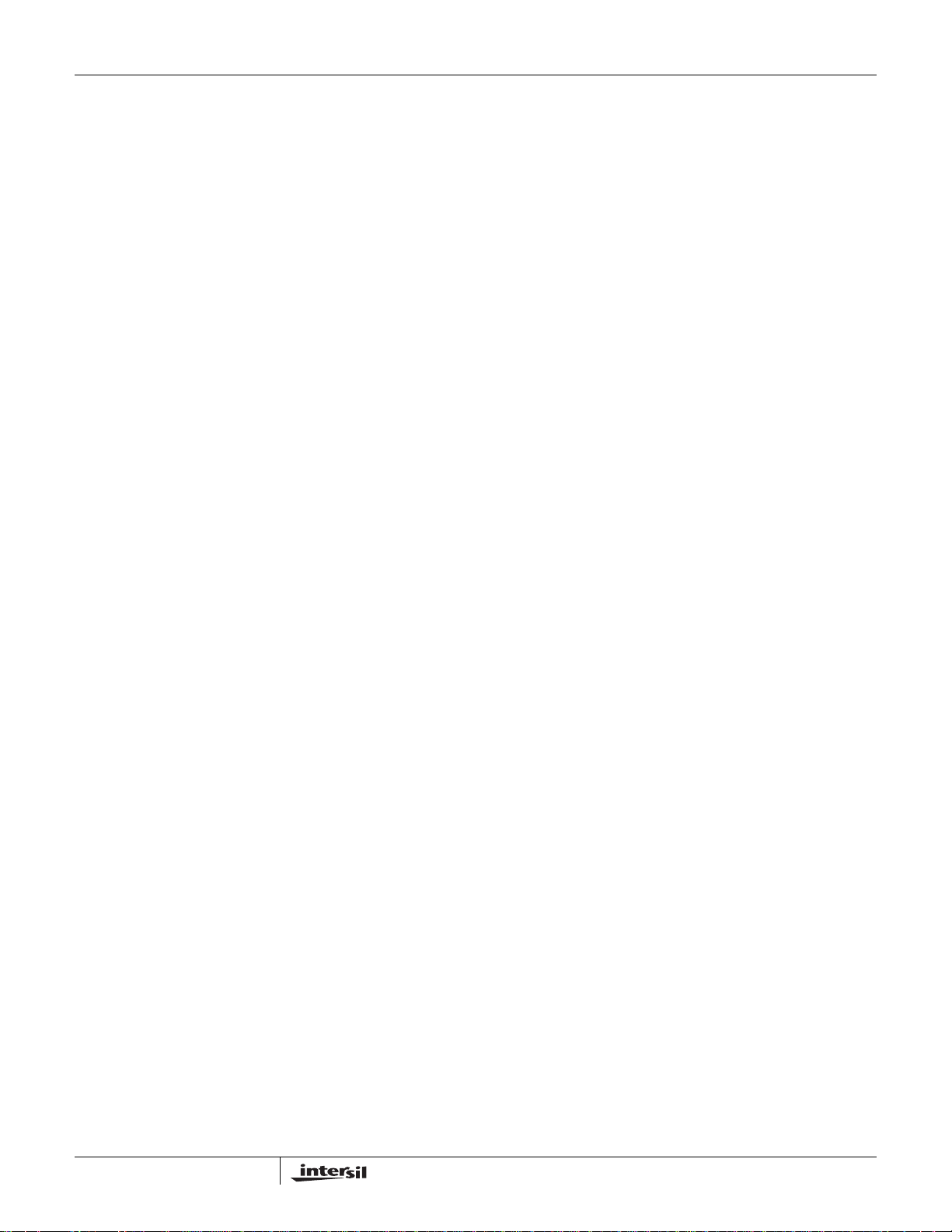

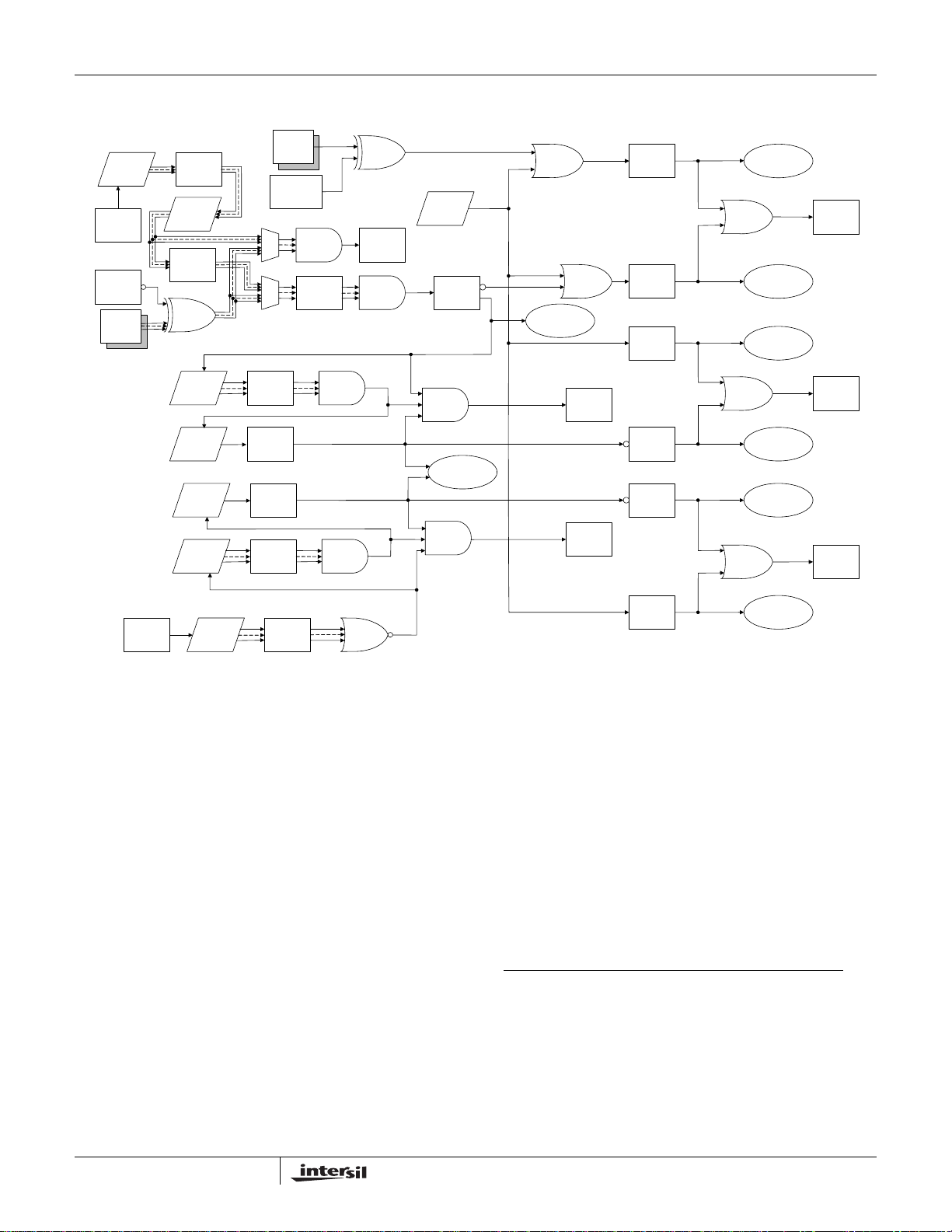

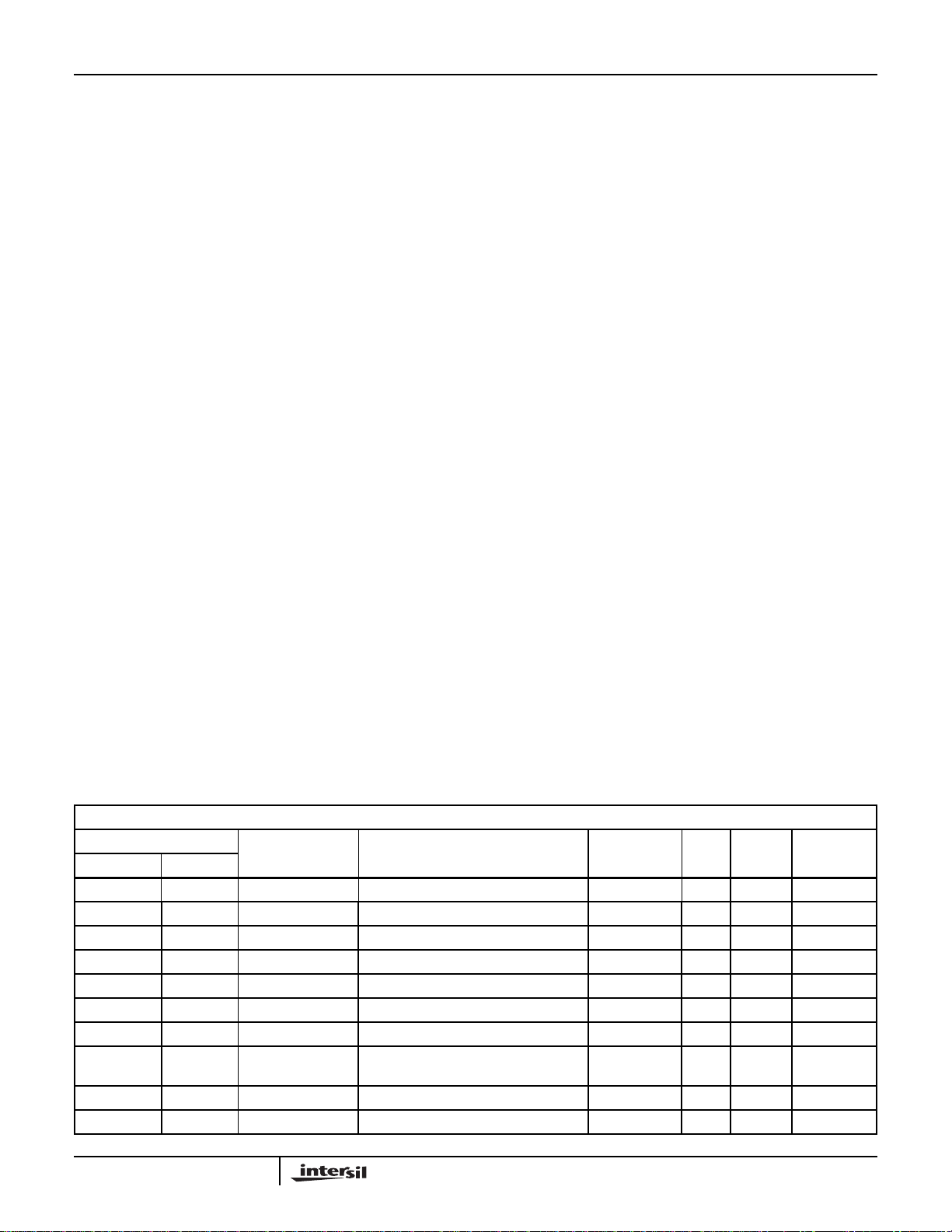

Figure 2. DETAILED FUNCTIONAL BLOCK DIAGRAM (BIST OMITTED) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

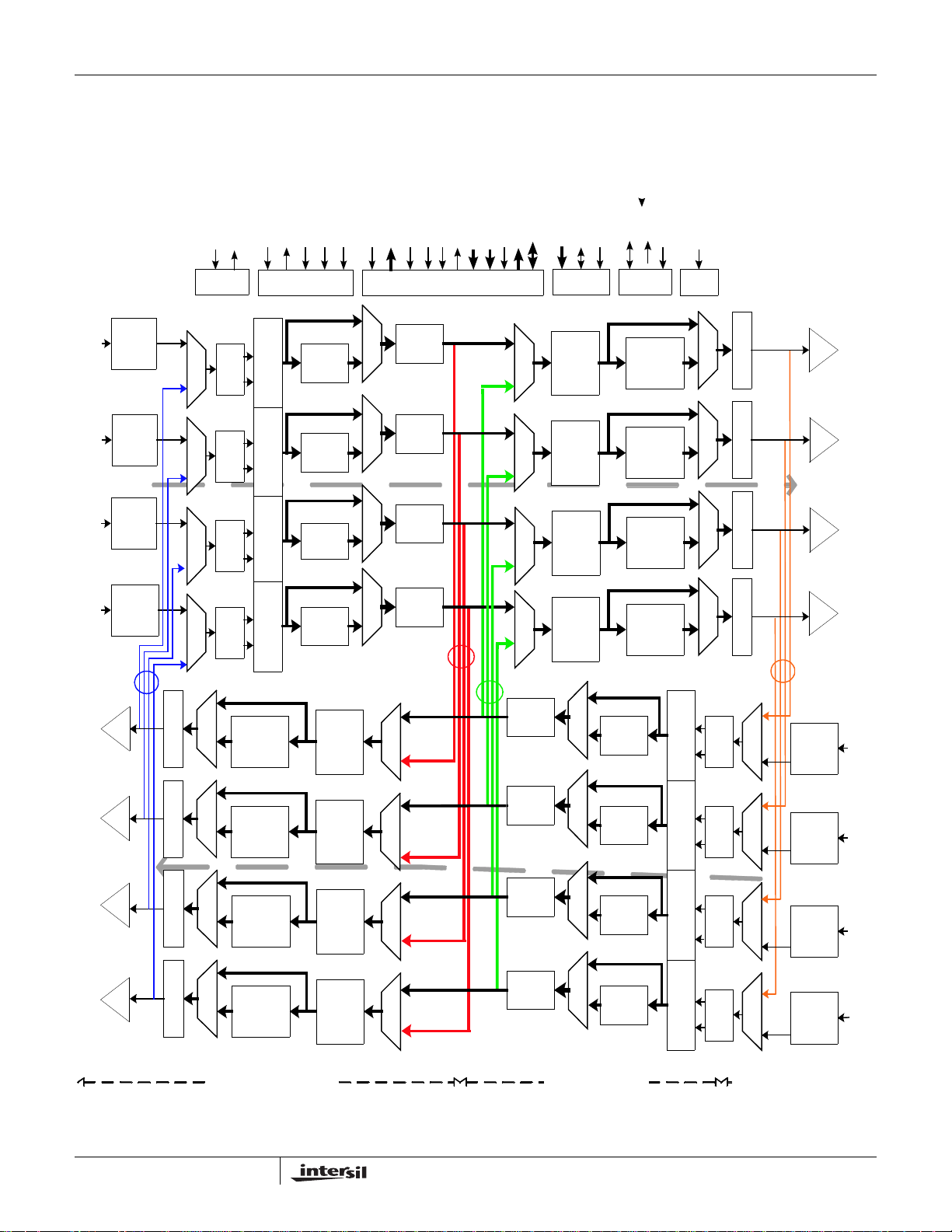

Figure 3. PRE-EMPHASIS OUTPUT ILLUSTRATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

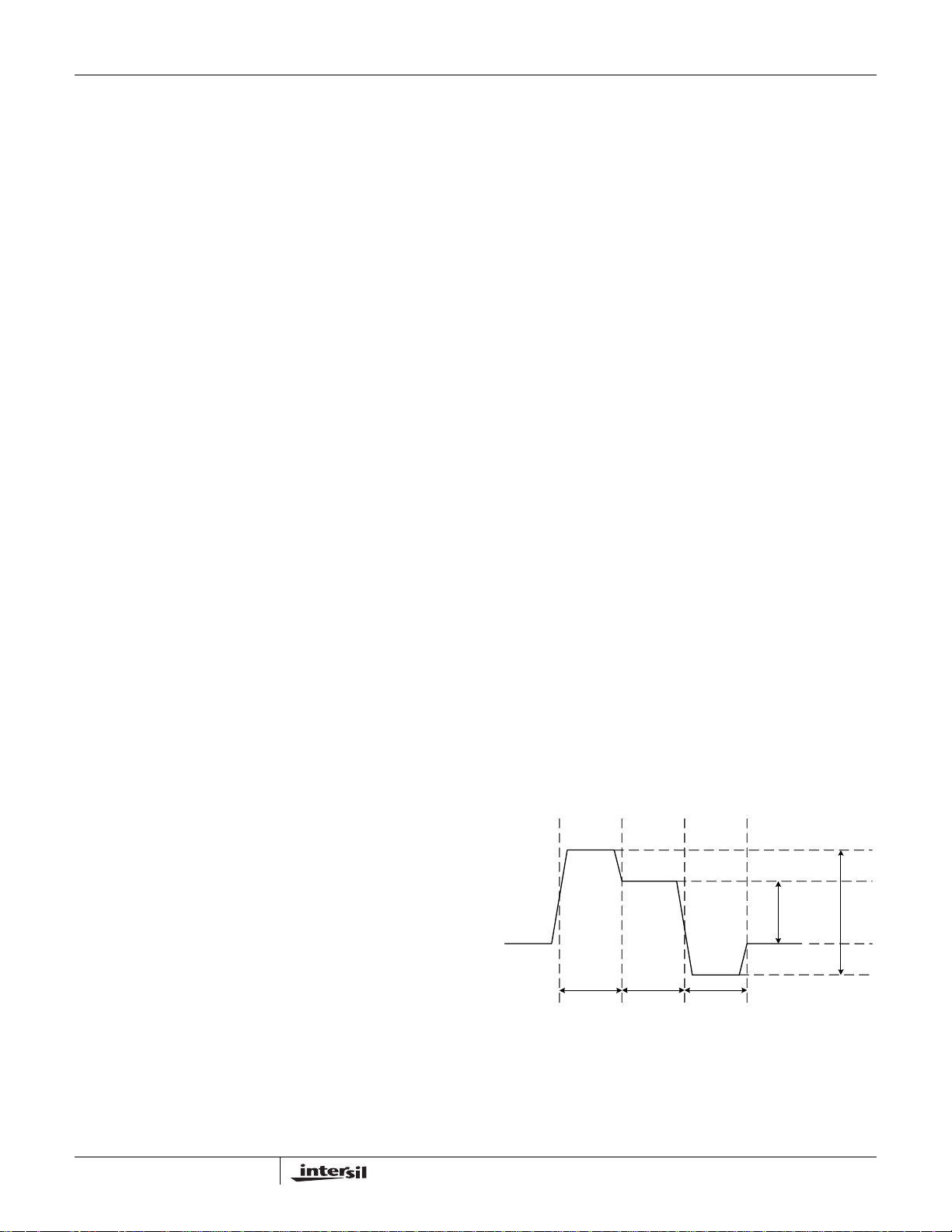

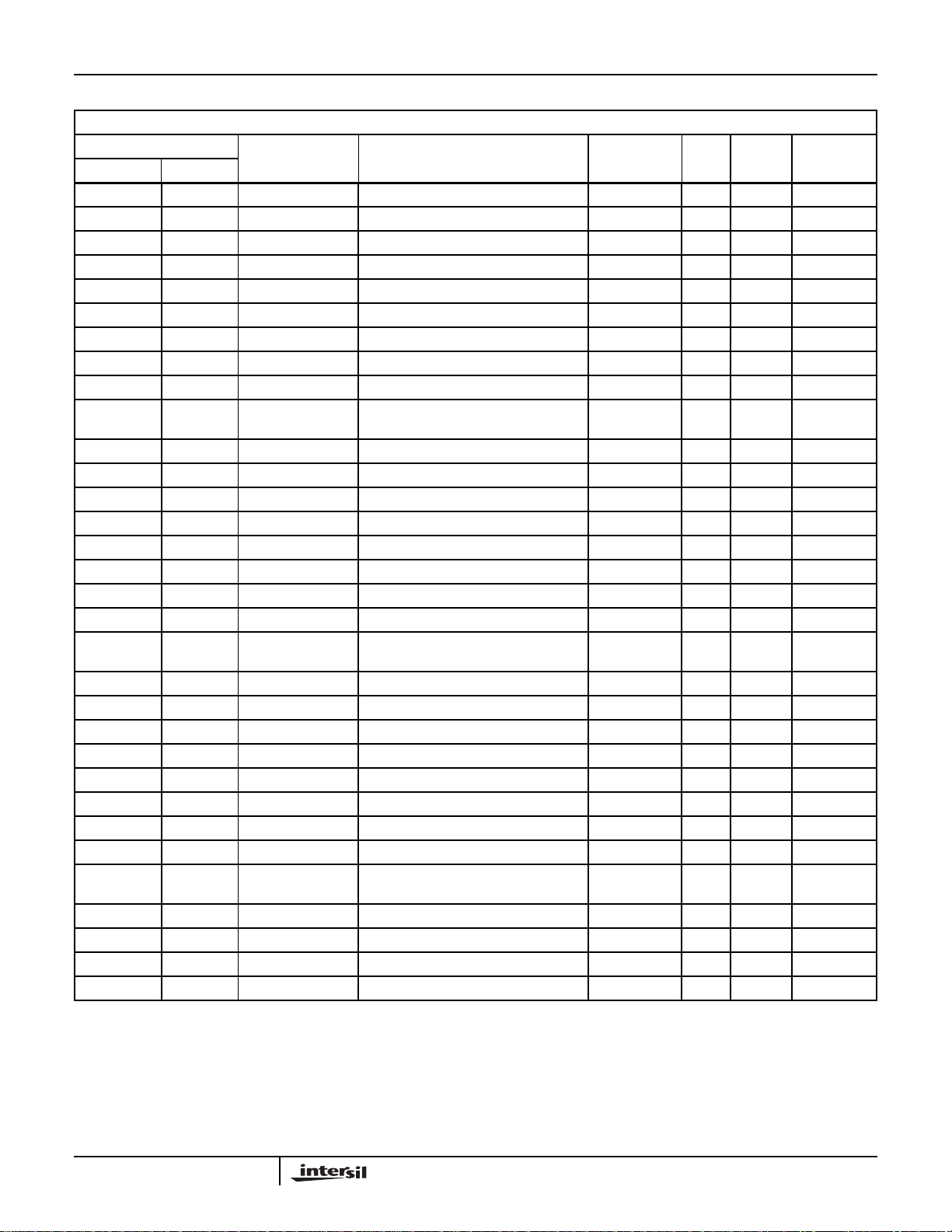

Figure 4. IEEE AND VENDOR SPECIFIC FAULT AND STATUS REGISTERS (EQUIVALENT SCHEMATIC). . . . . . . . . . . . . . 14

Figure 5. LASI EQUIVALENT SCHEMATIC. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 6. BLOCK DIAGRAM OF BIST OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Figure 7. TOP VIEW OF PINOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 8. EBGA-192 PACKAGE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Figure 9. DIFFERENTIAL OUTPUT SIGNAL TIMING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 10. LANE TO LANE DIFFERENTIAL SKEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 11. EYE DIAGRAM DEFINITION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 12. BYTE SYNCHRONIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 13. LANE-LANE ALIGNMENT OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 14. RETRANSMIT LATENCY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 15. MDIO FRAME AND REGISTER TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 16. MDIO INTERFACE TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 17. MDIO TIMING AFTER SOFT RESET (D.0.15). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 18. BEGINNING I2C NVR READ AT THE END OF RESET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 19. I2C BUS INTERFACE PROTOCOL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Figure 20. NVR/DOM SEQUENTIAL READ OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 21. NVR SEQUENTIAL WRITE ONE PAGE OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 22. I2C SINGLE BYTE READ OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 23. SINGLE BYTE WRITE OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 24. I2C OPERATION TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 25. VDDPR CLAMP CIRCUIT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 26. RESISTIVE DIVIDER CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4

BBT3821

www.BDTIC.com/Intersil

List of Tables

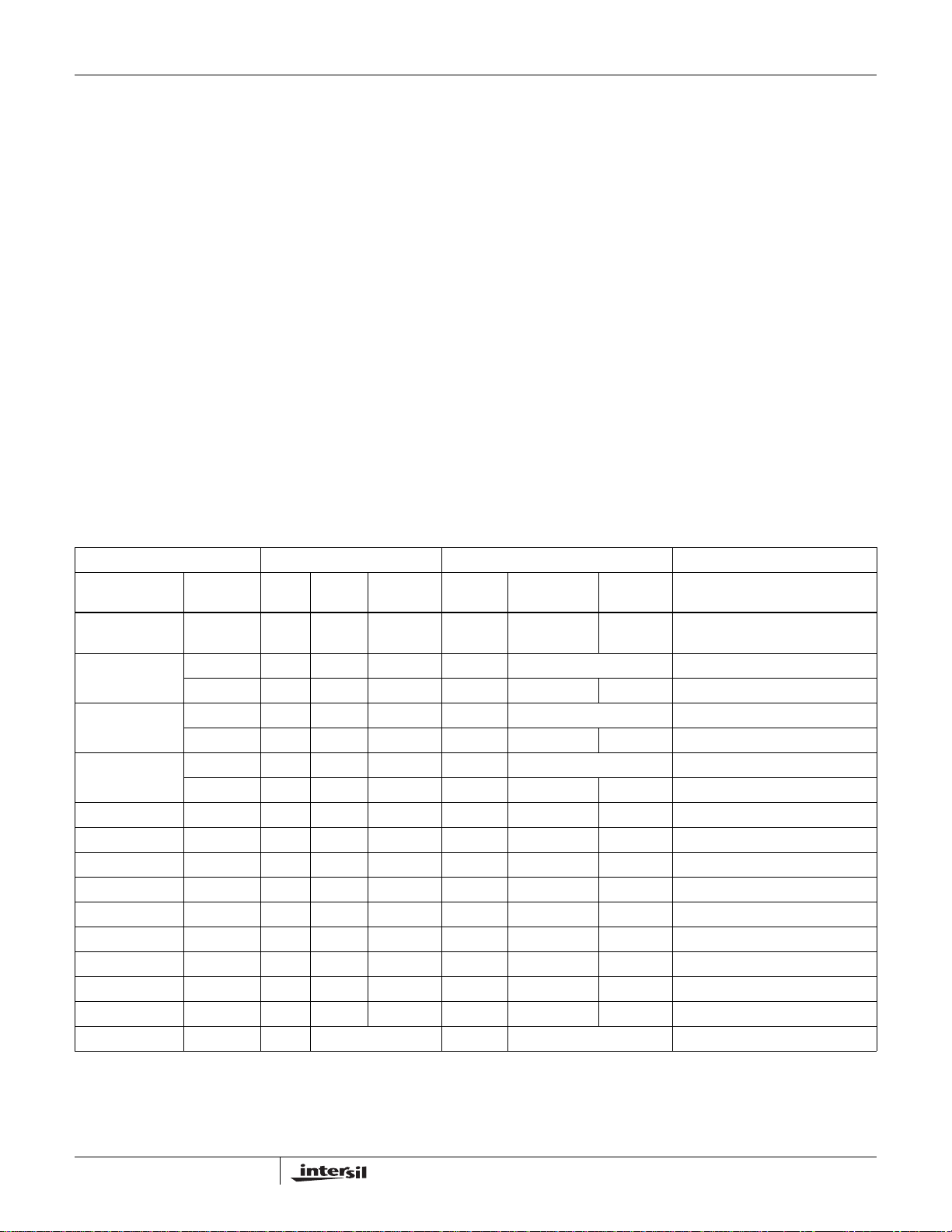

Table 1. VALID 10b/8b DECODER & ENCODER PATTERNS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 2. DEVAD DEVICE ADDRESS TABLE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 3. MDIO MANAGEMENT FRAME FORMATS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 4. MDIO PMA/PMD DEVAD 1 REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 5. IEEE PMA/PMD CONTROL 1 REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 6. IEEE PMA/PMD STATUS 1 REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 7. IEEE PMA/PMD, PCS, PHY XS, SPEED ABILITY REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 8. IEEE DEVICES IN PACKAGE REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 9. IEEE PMA/PMD TYPE SELECT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 10. IEEE PMA/PMD STATUS 2 DEVICE PRESENT & FAULT SUMMARY REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 11. IEEE TRANSMIT DISABLE REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 12. IEEE PMD SIGNAL DETECT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 13. IEEE EXTENDED PMA/PMD CAPABILITY REGISTER(1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 14. IEEE PACKAGE IDENTIFIER REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 15. XENPAK NVR CONTROL & STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 16. I2C ONE-BYTE OPERATION DEVICE ADDRESS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 17. I2C ONE-BYTE OPERATION MEMORY ADDRESS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 18. I2C ONE-BYTE OPERATION READ DATA REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 19. I2C ONE-BYTE OPERATION WRITE DATA REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 20. NVR I2C OPERATION CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 21. NVR I2C OPERATION STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 22. XENPAK NVR REGISTER COPY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 23. XENPAK DIGITAL OPTICAL MONITORING (DOM) CAPABILITY REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 24. XENPAK LASI RX_ALARM CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 25. XENPAK LASI TX_ALARM CONTROL REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 26. XENPAK LASI CONTROL REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 27. XENPAK LASI RX_ALARM STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 28. XENPAK LASI TX_ALARM STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 29. XENPAK LASI STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 30. XENPAK DOM TX_FLAG CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 31. XENPAK DOM RX_FLAG CONTROL REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 32. XENPAK DOM ALARM & WARNING THRESHOLD REGISTERS COPY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 33. XENPAK DOM MONITORED A/D VALUES REGISTER COPY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 34. XENPAK OPTIONAL DOM STATUS BITS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 35. XENPAK DOM EXTENDED CAPABILITY REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 36. XENPAK DOM ALARM FLAGS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 37. XENPAK DOM WARNING FLAGS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 38. XENPAK DOM OPERATION CONTROL AND STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 39. PMA CONTROL 2 REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 40. PMA SERIAL LOOP BACK CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 41. PMA PRE-EMPHASIS CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 42. PMA PRE-EMPHASIS CONTROL SETTINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 43. PMA/PMD EQUALIZATION CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 44. PMA SIG_DET AND LOS DETECTOR STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 45. PMA/PMD MISCELLANEOUS ADJUSTMENT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 46. PMA/PMD/PCS/PHY XS SOFT RESET REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5

BBT3821

www.BDTIC.com/Intersil

Table 47. GPIO PIN DIRECTION CONFIGURE REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 48. GPIO PIN INPUT STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 49. TX_FAULT & GPIO PIN TO LASI CONFIGURE REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 50. GPIO PIN OUTPUT REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 51. DOM CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 52. DOM PERIODIC UPDATE WAITING TIME VALUES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 53. DOM INDIRECT MODE START ADDRESS REGISTERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 54. DOM INDIRECT MODE DEVICE ADDRESS REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 55. OPTICAL STATUS & CONTROL PIN POLARITY REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 56. MDIO PCS DEVAD 3 REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 57. IEEE PCS CONTROL 1 REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 58. IEEE PCS STATUS 1 REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 59. IEEE PCS TYPE SELECT REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 60. IEEE PCS STATUS 2 DEVICE PRESENT & FAULT SUMMARY REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 61. IEEE 10GBASE-X PCS STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 62. IEEE 10GBASE-X PCS TEST CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 63. PCS CONTROL REGISTER 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 64. PCS CONTROL REGISTER 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 65. PCS or PHY XS XAUI_EN CONTROL OVERRIDE FUNCTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 66. PCS INTERNAL ERROR CODE REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 67. PCS INTERNAL IDLE CODE REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 68. PCS PARALLEL NETWORK LOOP BACK CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 69. PCS RECEIVE PATH TEST AND STATUS FLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 70. PMA/PCS OUTPUT CONTROL & TEST FUNCTION REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 71. PCS/PHY XS HALF RATE CLOCK CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 72. BIST CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 73. BIST ERROR COUNTER REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 74. MDIO PHY XS DEVAD 4 REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 75. IEEE PHY XS CONTROL 1 REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 76. IEEE PHY XS STATUS 1 REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 77. IEEE PHY XS STATUS 2 DEVICE PRESENT & FAULT SUMMARY REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 78. IEEE 10GBASE-X PHY XGXS STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 79. IEEE 10GBASE-X PHY XGXS TEST CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 80. PHY XS CONTROL REGISTER 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 81. PHY XS CONTROL REGISTER 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 82. PHY XS INTERNAL ERROR CODE REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 83. PHY XS INTERNAL IDLE CODE REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 84. PHY XS MISCELLANEOUS LOOP BACK CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 85. PHY XS PRE-EMPHASIS CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 86. PHY XS XAUI PRE-EMPHASIS CONTROL SETTINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 87. PHY XS EQUALIZATION CONTROL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 88. PHY XS RECEIVE PATH TEST AND STATUS FLAGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 89. PHY XS OUTPUT AND TEST FUNCTION CONTROL REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 90. PHY XS STATUS 4 LOS DETECTOR REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 91. PHY XS CONTROL REGISTER 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 92. AUTO-CONFIGURE REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 93. JTAG OPERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 94. CLOCK PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6

BBT3821

www.BDTIC.com/Intersil

Table 95. XAUI (XENPAK/XPAK/X2) SIDE SERIAL DATA PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 96. PMA/PMD (CX4/LX4) SIDE SERIAL DATA PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 97. JTAG INTERFACE PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 98. MANAGEMENT DATA INTERFACE PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 99. MISCELLANEOUS PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 100. I2C 2-WIRE SERIAL DATA INTERFACE PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 101. VOLTAGE SUPPLY PINS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 102. ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 103. RECOMMENDED OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 104. POWER DISSIPATION AND THERMAL RESISTANCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 105. PMA SERIAL PIN I/O ELECTRICAL SPECIFICATIONS, CX4 MODE (3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 106. PMA SERIAL PIN I/O ELECTRICAL SPECIFICATIONS, LX4 MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 107. PHY XS SERIAL PIN I/O ELECTRICAL SPECIFICATIONS, XAUI MODE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 108. EXTERNAL 1.2V CMOS OPEN DRAIN I/O ELECTRICAL SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 109. 1.5V CMOS INPUT/OUTPUT ELECTRICAL SPECIFICATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 110. 2.5V TOLERANT OPEN DRAIN CMOS INPUT/OUTPUT ELECTRICAL SPECIFICATIONS . . . . . . . . . . . . . . . . . . 62

Table 111. OTHER DC ELECTRICAL SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 112. REFERENCE CLOCK REQUIREMENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 113. TRANSMIT SERIAL DIFFERENTIAL OUTPUTS (SEE Figure 9, Figure 10 AND Figure 11). . . . . . . . . . . . . . . . . . . 63

Table 114. RECEIVE SERIAL DIFFERENTIAL INPUT TIMING REQUIREMENTS (SEE Figure 11) . . . . . . . . . . . . . . . . . . . . . 63

Table 115. MDIO INTERFACE TIMING (FROM IEEE802.3AE) (SEE Figure 15 TO Figure 17) . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 116. RESET AND MDIO TIMING (SEE Figure 17). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 117. RESET AND I2C SERIAL INTERFACE TIMING (SEE Figure 18 AND Figure 24). . . . . . . . . . . . . . . . . . . . . . . . . . . 64

7

BBT3821

www.BDTIC.com/Intersil

FIGURE 2. DETAILED FUNCTIONAL BLOCK DIAGRAM (BIST OMITTED)

(See also Figure 4 & Figure 5 for MDIO and LASI blocks and Figure 6 for BIST operation)

WRTP

SDC

RFC P/N

TXCK20

TDI

TDO

TMS

TCLK

TRSTN

LX4_MODE

RSTN

XP_ENA

MF[3:0]

TX_ENC

LASI

OPTxxx(3 pins)

GPIO[4:0]

TX_FAULT

TX_ENA[3:0]

OPRxxx(5 pins)

MDIO

PADR[4:0]

MDC

SDA

BIST_ENA

RXP0P/N

RXP1P/N

Egress

RXP2P/N

RXP3P/N

Loopback

TXP0 P/N

TXP1 P/N

Ingress

TXP2 P/N

TXP3 P/N

Equalizer

Signal

Detect

Equalizer

Signal

Detect

Equalizer

Signal

Detect

Equalizer

Signal

Detect

PHY XS

(Serial)

Serializer

Serializer

Serializer

Serializer

20X or 10X

Clock

CDR

CDR

CDR

CDR

Deserializer &

Deserializer &

Deserializer &

Deserializer &

8B/10B

Encoder,

AKR

Generator

8B/10B

Encoder,

AKR

Generator

8B/10B

Encoder,

AKR

Generator

8B/10B

Encoder,

AKR

Generator

Comma

Detector

Comma

Detector

Comma

Detector

Comma

Detector

10B/8B

Decoder

10B/8B

Decoder

10B/8B

Decoder

10B/8B

Decoder

TXFIFO &

Error and

Orderset

Detector

TXFIFO &

Error and

Orderset

Detector

TXFIFO &

Error and

Orderset

Detector

TXFIFO &

Error and

Orderset

Detector

MDIO Register, LASI & Common LogicJTAG

RX FIFO

Deskew

RX FIFO

Deskew

MDIO

Engine

TXFIFO &

Error and

Orderset

Detector

TXFIFO &

Error and

Orderset

Detector

I2C

8B/10B

Encoder,

Generator

8B/10B

Encoder,

Generator

BIST

AKR

AKR

LX4/CX4XAUI

Serializer

TCX0 P/N

Serializer

TCX1 P/N

Egress

CDR

CDR

CDR

CDR

S erializ er

TCX2 P/N

S erializ er

TCX3 P/N

PMA

Loop

back

Equalizer

Signal

Detect

Equalizer,

Signal

Detect

RCX0 P/N

RCX1 P/N

Ingress

Equalizer,

Signal

Detect

Equalizer,

Signal

Detect

RCX2 P/N

RCX3 P/N

RX FIFO

Deskew

RX FIFO

Deskew

PCS //

(PHY XS)

Loopback

TXFIFO &

Error and

Orderset

Detector

TXFIFO &

Error and

Orderset

Detector

PCS // Network

Loopback

RX FIFO

Deskew

RX FIFO

Deskew

RX FIFO

Deskew

RX FIFO

Deskew

10B/8B

Decoder

10B/8B

Decoder

10B/8B

Decoder

10B/8B

Decoder

8B/10B

Encoder,

AKR

Generator

8B/10B

Encoder,

AKR

Generator

Deserializer &

Detector

Comma

D es er ializ er &

Detector

Comma

Deserializer &

Detector

Comma

Deserializer &

Detector

Comma

Device Address 3 PCSDevice Address 4 PHY XGXS

8

Device Address 1 PMA/PMD

BBT3821

www.BDTIC.com/Intersil

General Description

The nLiten BBT3821 is a fully integrated octal 2.488Gbps to

3.1875Gbps Clock and Data Recovery (CDR) circuit and

Retimer ideal for high bandwidth serial electrical or optical

communications systems. It extracts timing information and

data from serial inputs at 2.488Gbps to 3.1875Gbps,

covering 10 Gigabit Fiber Channel (10GFC) and IEEE 802.3

specified 10 Gigabit Ethernet eXtended Attachment Unit

Interface (XAUI) rates.

Each BBT3821 accepts two sets of four high-speed

differential serial signals, re-times them with a local

Reference Clock, reduces jitter, and delivers eight clean

high-speed signals. The BBT3821 provides a full-function

XAUI-to-10GBASE-CX4 PMA/PMD (compatible with the

IEEE 802.3ak specification), and also can be configured to

provide the electrical portion of a XAUI-to-10GBASE-LX4

PMA/PMD, needing only laser drivers and photo detectors to

be added. In both these applications, the XAUI side can be

configured to implement the XENPAK MSA_R3.0

specification, including full NVR and DOM support. The

XPAK and X2 specifications currently all reference the

XENPAK specification, and are supported in exactly the

same manner. The BBT3821 can also be used to enhance a

single full-duplex 10 Gigabit XAUI link, extending the driving

distance of the high-speed (2.488Gbps to 3.1875Gbps)

differential traces to 40 inches of FR4 PCB (assuming a

proper impedance-controlled layout).

Each lane can operate independently with a data transfer

rate of within ±100ppm of either 20x or 10x the local

Reference Clock. The reference clock should be 156.25MHz

for 10 Gigabit Ethernet XAUI applications, and 159.375MHz

for 10 Gigabit Fiber Channel. Other reference frequencies

can be used for proprietary rates. For other applications,

each of the 8 lanes can be operated independently, within

the same data rate and clock restrictions.

The nLiten BBT3821 contains eight clock & data recovery

units, 8B/10B decoders and encoders, and elastic buffers

which provide the user with a simple interface for transferring

data serially and recovering it on the receive side. When

recovering an 8B/10B stream, a receive FIFO aligns all

incoming serial data to the local reference clock domain,

adding or removing IDLE sequences as required. This

simplifies implementation of an upstream ASIC by removing

the requirement to deal with multiple clock domains. The

Retimer can also be configured to operate as eight nonencoded 10-bit Retimers. Allowing long strings of

consecutive 1’s or 0’s (up to 512 bits), the nLiten BBT3821

has the capacity to accommodate proprietary encoded data

links at any data rate between 2.488Gbps and 3.1875Gbps

(and for half rate operation from 1.244Gbps to

1.59375Gbps).

The device configuration can be done through the use of the

two line Management Data Input/Output (MDIO) Interface

specified in IEEE 802.3 Clause 45. The BBT3821 supports a

5-bit Port Address, and DEVice ADdresses (DEVAD) 1, 3 & 4.

The initial values of the registers default to values controlled,

where appropriate, by external configuration pins, and set to

optimize the initial configuration for XAUI, CX4, and

XENPAK/XPAK/X2 use. Optionally, the BBT3821

configuration can be loaded at power-on or reset from the

NVR EEPROM or DOM used for the XENPAK/XPAK/X2

registers.

A full suite of loopback configurations is provided, including

the (802.3ae required) XAUI-transmit to XAUI-receive

loopback, and also the (802.3ae optional) PHY XGXS

loopback (effectively CX4/LX4-receive to CX4/LX4 transmit).

Lane-by-lane diagnostic loopback is available through

vendor-specific MDIO registers.

The low-power version BBT3821LP-JH is selected for

operation as an LX4 device at lowered supply voltages.

Functions

The nLiten BBT3821 serves three main functions:

• Pre-emphasize the output and equalize the input in order

to “re-open” the data eye, thus allowing CX4 operation,

and also increasing the available driving distance of the

high-speed traces in XAUI links.

• Clock compensation by insertion and deletion of IDLE

characters when 8B/10B encoding and decoding is

enabled.

• Automatic Byte and Lane Alignment, using both disparities

of /K/ for Byte alignment and either ||A|| or IDLE to DATA

transitions for lane alignment.

Receiver Operations

Loss of Signal Detection, Termination & Equalization

Each receiver lane detects and recovers the serial clock

from the received data stream. An equalizer has been added

to each receiver input buffer, which boosts high frequency

edge response. The boost factor can be selected from 16

values (none to full) through the MDIO Registers, (see

Table 43 for the PMA/PMD and Table 87 for the PHY XS).

A nominally 100Ω on-chip transmission line terminating

resistor is integrated with the input equalizer. This eliminates

the requirement of external termination resistors. It greatly

improves the effectiveness of the termination, providing the

best signal integrity possible.

There are also signal detect functions on each input lane,

whose “Loss Of Signal” (LOS) and “Signal Detect”

(SIG_DET) outputs appear in the MDIO Vendor-Specific

registers at address 1.C00A’h (Table 44) and 4.C00A’h

(Table 90). The LOS indication reflects the standard XAUI

specification, while the SIG_DET indication (CX4 inputs

only) implements the CX4 function. These signals can also

9

BBT3821

www.BDTIC.com/Intersil

be routed to the MF[3:0] pins (see Table 81 and Table 99).

The PMA configuration determines which of these signals

will be reflected in the IEEE PMD Receive signal detect

register at 1.10 (see Table 12), and contribute to the

RX_FAULT bit in the IEEE Status Register 2 at address 1.8

(see Table 10) and the LOCAL_FLT bit in the IEEE

PMA/PMD Status 1 Register, at address 1.1, (see Table 6).

The PHY XGXS LOS will be reflected in the IEEE Status

Registers at addresses 4.8 and 4.1 (see Table 77 and

Table 76). The threshold of the LOS detectors is controlled

via the 'LOS_TH' bits in the MDIO registers at 1.C001'h, see

Table 39, for the PMA/PMD, and for the PHY XS at

4.C001'h, see Table 81.

Clock and Data Recovery

When the 8B/10B coding is used, the line rate receive clock

is extracted from the transition rich 10-bit coded serial data

stream independently on each lane. When 8B/10B coding is

not used, longer run length (up to 512 1’s and 0’s) can be

supported. The data rate of the received serial bit stream

must be within ±100ppm of the nominal bit rate (strictly

within ±200 ppm of the multiplied local reference clock) to

guarantee proper reception. The receive clock locks to the

input within 2µs after a valid input data stream is applied.

The received data is de-serialized and byte aligned.

Byte Alignment (Code-Group Alignment)

Unless the CDET bits of the MDIO Registers at address

3.C000’h (for PCS, see Table 63) or 4.C000’h (for PHY XS,

see Table 80) are turned off, the respective Byte Alignment

Units are activated. Each Byte Alignment Unit searches the

coded incoming serial stream for a sequence defined in

IEEE 802.3-2002 Clause 36 as a “comma”. A comma is the

sequ ence “0011111” or “1100000” depending o n dis parity,

and is uniquely located in a valid 8B/10B coded data stream,

appearing as the start of some control symbols, including the

/K/ IDLE (K28.5). Comma disparity action can be controlled

via the same CDET bits of the registers [3:4].C000’h (see

Table 63 and Table 80). Any proprietary encoding scheme

used should either incorporate these codes, or arrange byte

alignment differently.

Upon detection of a comma, the Byte Alignment Unit shifts

the incoming data to align the received data properly in the

10-bit character field. Two possible algorithms may be used

for byte alignment. The default is that specified in the

IEEE802.3ae-2002 clause 48 specification, and is very

robust. This algorithm relies on the 10b/8b decoder, and

should not be used with proprietary encoding/decoding

schemes. The alternative is to byte-align on any comma

pattern. Although quick to align, and normally quite reliable,

this method is susceptible to realignment on certain single bit

errors or on successive K28.7 characters, but could be

preferable for proprietary coding schemes, or during debug.

The algorithm selection is controlled via MDIO register

PCS_SYNC_EN bits, for the PCS at address 3.C000’h

(Table 63), for the PHY XS at address 4.C000’h (Table 80),

unless overridden by the respective XAUI_EN bits in the

[3,4].C001’h registers (Table 64 and Table 81). Up to a full

code group may be deleted or modified while aligning the

“comma” code group correctly to the edges of the RefClock.

A comma received at any odd or even byte location, but at

the proper byte boundary, will not cause any byte realignment.

8b/10b Decoding

The internal 10b decoding specified in the IEEE802.3-2002

specification, section 36.2.4 in Tables 36-1 & 36-2, and

discussed in more detail in “8b/10b Coding and Decoding”

page 12, is enabled by default in the PCS and PHY XS

through the setting of the respective CODECENA bits to 1’b,

and may be disabled through the MDIO registers

[3,4].C000’h (Table 63 and Table 80) by setting the

respective bit to 0’b. Note that the transmit encoding will also

be disabled. Although Comma detection will still operate

normally, the PCS_SYNC engine (see above) may not

operate correctly on a proprietary coding scheme, unless

byte sync is performed on K28.5 characters, and no code

violations are to be expected in the proprietary data, and so

should normally be disabled if the 8b/10b coding is turned

off. The ‘fallback’ byte sync operations described above can

still be used, if the encoding scheme meets the “comma”

rules; otherwise they should be disabled also via the CDET

bits, and the user should expect unsynchronized 10-bit data

to be forwarded to the transmitter. No clock compensation is

then possible, and a synchronous reference clock should be

used throughout.

Receive FIFO

The Receive FIFO performs two functions:

1. Lane to Lane Alignment

2. Clock Compensation

Deskew (Lane to Lane) Alignment

Trunking, also known as deskewing, means the alignment of

packet data across multiple lanes. 8 bytes of RXFIFO are

dedicated for this lane to lane alignment in each direction.

During high-speed transmission, different active and passive

elements in the links may impart varying delays in the four

lanes. In trunking mode, multiple lanes share the same clock

(the local reference clock), which is used to transfer data for

output on the serial transmitter.

Deskewing is accomplished by monitoring the contents of

the FIFOs to detect either an /A/ code-group on every lane

(an ||A|| Ordered_Set), or the boundary between IDLE

sequences and any non-IDLE data (see Table 1); the latter

boundary defines the beginning of the packet. The choice of

which alignment markers to use can be controlled by the

A_ALIGN_DIS bits in MDIO [3,4].C000’h (see for PCS

Table 63 and for PHY XS Table 80), unless overridden by

the respective XAUI_EN bits in the [3,4].C001’h registers

(Table 64 and Table 81) to align on ||A||. When this alignment

10

BBT3821

www.BDTIC.com/Intersil

data is detected in all four lanes within the span of the

Alignment FIFO, the deskewing (lane to lane) alignment

operation is performed, and will be held until another ||A|| or

IDLE-to- non-IDLE transition is detected again on the lanes.

During this alignment, up to four code groups may be

deleted on any lane. For correct operation, the XAUI Lane 0

signals should be connected to the BBT3821 Lane 0 pins.

The deskew algorithm state machines (each implemented

according to IEEE 802.3ae) are enabled by setting the

DSKW_SM_EN bits (Address [3,4].C000’h, see Table 63

and/or Table 80) to 1 or overriding them with the respective

XAUI_EN bits in the [3,4].C001’h registers (Table 64 and

Table 81). Note that when one side’s DSKW_SM_EN is set

to 1, the same side CAL_EN bit (Address [3,4].C000’h,

Table 63/Table 80) is ignored. When a DSKW_SM_EN bit is

set to 0, lane deskew can still be enabled by setting

CAL_EN, but the deskew action will be carried out without

hysteresis.

The user has the option to disable trunking, or to enable

trunking across each set of 4 lanes, in the PCS (device 3)

and PHY XGXS (device 4), under control of the respective

PSYNC bits in registers [3,4].C000h. In trunking mode, the

lanes may have phase differences, but they are expected to

be frequency synchronous. In non-trunking mode, each

received serial stream need only be within ±100ppm of the

nominal bit rate (2.488Gbps to 3.1875Gbps in full-speed

mode or 1.244Gbps to 1.59375Gbps in half-speed mode).

Setting the PSYNC bits high will enable the trunking mode,

so that all transmitted data will be synchronized to the same

clock. Note that trunking mode is only possible if 8B/10B

Coding is activated, and all lanes have the same half-rate

setting (See Table 71).

Clock Compensation

In addition to deskew, the Receive FIFOs also compensate

for clock differences. Since the received serial streams can,

under worst case conditions, be off by up to ±200ppm from

the local clock domain, the received data must be adjusted

to the local reference clock frequency.

Another 8 bytes of RXFIFO are dedicated for clock

compensation. The FIFOs achieve clock tolerance by

identifying any of the IDLE patterns (/K/, /A/ or /R/ as defined

by the IEEE 802.3ae standard) in the received data and then

adding or dropping IDLEs as needed. The Receive FIFO

does not store the actual IDLE sequences received but

generates the number of IDLEs needed to compensate for

clock tolerance differences. The IDLE patterns retransmitted

will be determined according to the IEEE 802.3ae algorithm

if the appropriate AKR_SM_EN bit is set in Registers

[3,4].C001’h (see Table 64 and Table 81).

Transmitter Operations

8b/10b Encoding

The internal 10b encoding specified in the IEEE802.3-2002

specification, section 36.2.4 in Tables 36-1 & 36-2, and

discussed in more detail in “8b/10b Coding and Decoding”

page 12, is enabled by default in the PCS and PHY XS

through the setting of the respective CODECENA bits to 1’b,

and may be disabled through the MDIO registers

[3,4].C000’h (see Table 63 and Table 80) by setting the

respective bit to 0’b. Note that the receive decoding will also

be disabled. The (decoded, synchronized and aligned) data

is transferred via the transmit FIFOs, (normally) encoded,

serialized and re-transmitted on the Serial Output pins,

whose effective output impedance is nominally 100Ω

differential.

Pre-Emphasis

In order to compensate for the loss of the high frequency

signal component through PCB traces or the CX4 Cable

Assembly, sixteen levels of programmable pre-emphasis

have been provided on the CX4/LX4 PMA serial transmit

lanes, and eight levels on the XAUI PHY XS serial transmit

lanes. The output signal is boosted immediately after any

transition (see Figure 3). This maximizes the data eye

opening at the receiver inputs and enhances the bit error

rate performance of the system. The MDIO Registers at

Addresses [1,4].C005’h (see Table 41 and Table 85) control

the level of pre-emphasis for the PMA/PMD (sixteen levels)

and PHY XGXS (eight levels) respectively, settable from

none to the maximum. The initial default values of the

PMA/PMD register depend on the LX4_MODE configuration

pin, and are set to the optimum values for CX4 or XAUI

(assumed best for LX4 drivers). Both these registers may be

auto-loaded (see Auto-Configuring Control Registers

page 16) from an NVR EEPROM on start-up or RESET.

FIGURE 3. PRE-EMPHASIS OUTPUT ILLUSTRATION

1

Bit

Time

1

Bit

Time

00

V

LOW-pp

Bit

Time

V

HI-pp

11

BBT3821

www.BDTIC.com/Intersil

8b/10b Coding and Decoding

another column containing a non-idle is received. If in

addition either of the AKR_SM_EN or XAUI_EN bits in the

8 Bit Mode

If 8B/10B encoding/decoding is turned on, the nLiten

BBT3821 expects to receive a properly encoded serial bit

stream. The serial bit stream must be ordered “abcdeifghj”

with “a” being the first bit received and “j” the last. If the

received data contains an error, the Retimer will re-transmit it

as an ERROR or /E/ character. The character transmitted

may be controlled via the ERROR code Registers

[3,4].C002’h, Table 66 and Table 82. The internal decoding

into, and encoding from, the FIFOs is listed in Table 1 below.

If the TRANS_EN bit or XAUI_EN bit (MDIO Registers at

addresses [3,4].C001’h, see Table 64 and Table 81 are set,

all incoming XAUI or CX4/LX4 IDLE patterns will be

converted to the (internal) XGMII IDLE pattern set by the

respective PCS or PHY XS control registers at addresses

[3,4].C003’h, with a default value 107’h, the standard XGMII

IDLE code (see Table 67 and Table 83) in the internal FIFOs.

The first full column of IDLES after any column containing a

non-IDLE will be stored in the respective elasticity FIFO, and

all subsequent full IDLE columns will repeat this pattern, until

Table 1. VALID 10b/8b DECODER & ENCODER PATTERNS

RECEIVING SERDES INTERNAL DATA TRANSMITTING SERDES NOTES

SERIAL CODE,

CHARACTER

Valid Data X 0 0 0-FF’h X See 802.3

/K/ (Sync) K28.5 1 0 1 07’h

/A/ (Align) K28.3 1 0 1 07’h

/R/ (Skip) K28.0 1 0 1 07’h

/S/ K27.7 X 0 1 FB 1 /S/ K27.7 Start

/T/ K29.7 X 0 1 FD 0 /T/ K29.7 Terminate

K28.1 X 0 1 3C X K28.1 Extra comma

/F/ K28.2 X 0 1 5C X /F/ K28.2 Signal Ordered_Set

/Q/ K28.4 X 0 1 9C X /Q/ K28.4 Sequence Ordered_Set

K28.6 X 0 1 DC X K28.6

K28.7 X 0 1 FC X K28.7 Repeat has False Comma

K23.7 X 0 1 F7 X K23.7

/E/ K30.7 X 1 1 FE X /E/ K30.7 Error Code

Any other X 1 = ERROR reg.

Note (1): First incoming IDLE only, subsequent IDLEs in that block repeat first received code.

Note (2): Default value, actually set by ‘Internal Idle’ register, [3:4].C003’h, see Table 67 and Table 83.

Note (3): Value set by ‘ERROR Code’ register, [3:4].C002’h, see Table 66 and Table66. The XAUI_EN bit forces it to 1FE’h.

Note (4): If the XAUI_EN bit is set, the BBT3821 acts as though both the TRANS_EN and AKR_EN bits are set.

TRANS_EN

(4)

BIT

001BC

0017C

0011C

E-BIT K-BIT

INTERNAL

FIFO DATA

AKR_SM_

(2)

(1)

(2)

(1)

(2)

(1)

(3)

respective MDIO registers at Addresses [3,4].C001’h is set

(see Table 64 and Table 81, these IDLEs will be sequenced

on transmission into a pseudo-random pattern of ||A||, ||K||,

and ||R|| codes according to the IEEE 802.3ae specified

algorithm. If neither of the AKR_SM_EN and XAUI_EN bits

are set, the internal IDLEs will all be transmitted as /K/

codes. Elasticity will be achieved by adding or deleting

columns of internal IDLEs.

If neither the TRANS_EN bit nor the XAUI_EN bit is set (for

either the PCS or the PHY XS), the incoming XAUI IDLE

codes will all be decoded to the appropriate XGMII control

code values in the respective internal FIFO. If the AKR_EN

or XAUI_EN bits are set, they will be sequenced into a

pseudo-random pattern of ||A||, ||K||, and ||R|| codes and

retransmitted, if not, the Inter Packet Gap (IPG) will be

retransmitted as the same XAUI codes as in the first full

IDLE column.

For most applications, the XAUI_EN bit high configuration is

the most desirable, and is the default.

(4)

EN

1 /A/ /K/ /R/ IEEE802.3ae algorithm

0 /K/ K28.5 Comma (Sync)

1 /A/ /K/ /R/ IEEE802.3ae algorithm

0 /A/ K28.3 Align

1 /A/ /K/ /R/ IEEE802.3ae algorithm

0 /R/ K28.0 Alternate Idle (Skip)

X Invalid code Error Code

SERIAL

CHARACTER

Table

SERIAL

CODE DESCRIPTION

Valid Data Same Data Value as Received

12

BBT3821

www.BDTIC.com/Intersil

10 Bit Mode

If a PCS or PHY XS 8B/10B codec is inactive (the respective

XAUI_EN AND CODECENA bits are disabled, see

Table 63/Table 64 & Table 80/Table 81), no 8b/10b coding or

decoding is performed. The incoming bits will be arbitrarily split

into 10 bit bundles in the internal FIFO, optionally based on any

commas received, but otherwise not checked, and must be

retransmitted in the same clock domain, since no elasticity is

possible. Therefore the local reference clock must be frequency

synchronous with the data source. Only the jitter domain will be

reset. System designers must ensure that the data stream is

adequately DC-balanced and contains sufficient transition

density for proper operation, including synchronization.

Error Indications

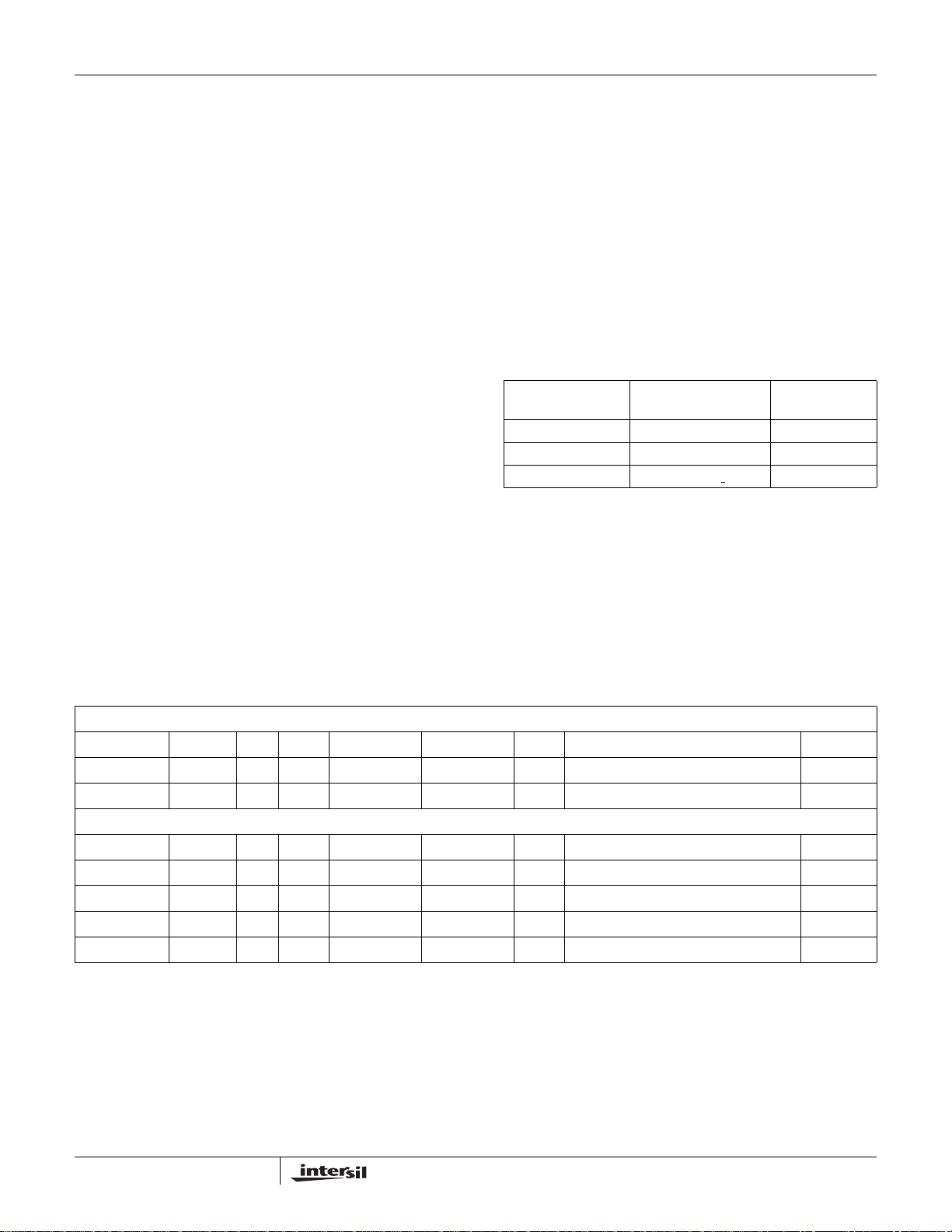

An equivalent schematic of the various IEEE-defined and

Vendor Specific Fault and Status registers in the BBT3821 is

shown in Figure 4. Those register signals that also contribute to

the LASI system are indicated (see Figure 5).

Loss of Signal

If the reference clock is missing or at an out-of-range frequency,

the PLL in the CMU will fail to lock. This is the only possible

internal cause of a PMA ‘TX Local Fault ‘ indication in bit 1.8.11

(Table 10), and will cause ‘RX Local Fault’ in bit 1.8.10 and

other consequent fault indications (see Table 6, Table 27 and

Table 28).

Loss of the input signal may be caused by poor connections,

insufficient voltage swings, or excessive channel loss. If any of

these conditions occurs, the Loss Of Signal (LOS) and (CX4)

SIG_DET detector outputs on the lane will indicate the fault,

and may be monitored via the MDIO system (see Table 6,

Table 10, Table 27, Table 28, Table 76 and Table 77). See also

the section on “Loss of Signal Detection, Termination &

Equalization“ on page 9 above. In addition, the MDIO MF_SEL

and MF_CTRL register bits (address 4.C001’h, see Table 81)

may be set to provide the LOS/SIG_DET indication on the

MF[3:0] pins.

Channel Fault Indications

Any of the above faults (LOS/SIG_DET, Byte Sync, or Lane

Align), will (by default) cause a local fault in the relevant

receiver. If the PCS_SYNC_EN bit at address [3,4]C000’h (or

the XAUI_EN bit at [3:4].C001’h) (see Table 63 to

Table 65 and/or Table 80 to Table 81) is set, the internal FIFOs

will propagate the local fault indication specified in the

IEEE802.3ae-2002 specification (Sections 46.3.4 and 48.2.4.2)

as the Sequence Ordered_Set ||LF|| (see Table 48-4),

/K28.4/D0.0/D0.0/D1.0/, which will be transmitted as the

appropriate XAUI or LX4/CX4 TX output. The BBT3821 lanes

0-3 must be connected to XAUI and LX4/CX4 lanes 0-3 in strict

order. Any Sequence Ordered_Set (including ||LF|| and ||RF||)

received on an input channel will be retransmitted unchanged

on the appropriate output channel.

Coding Violation, Disparity & FIFO Errors

The 8b/10b decoder will detect any code violation, and replace

the invalid character by the error character /E/. In the case of a

disparity error, the error may be propagated and only flagged at

the end of a packet (according to the IEEE 802.3 rules). The

BBT3821 will handle this according to those rules. In addition,

the MDIO system includes a flag, in registers [3,4].C007’h on

bits 11:8 (see Table 69 and Table 88). Similarly, an error in the

PCS or PHY XS Elastic (clock compensation) FIFOs will be

flagged in bits 7:4 of the same registers. The FIFO errors may

also be flagged on the MF[3:0] pins via the MDIO MF_SEL and

MF_CTRL register bits (address 4.C001’h, see Table 81).

If a PCS or PHY XS 8B/10B codec is inactive, disparity error

and coding violation errors do not apply, and the FIFOs have no

active error source.

Loopback Modes

In addition to the IEEE 802.3ae-required loopback modes,

the BBT3821 provides a number of additional modes. Each

mode is described in detail below, by reference to the

Detailed Functional Block Diagram in Figure 2, together with

the register bits controlling it.

Byte or Lane Synchronization Failure

The MDIO system can indicate a failure to achieve Byte

Synchronization on any lane, in the PCS register bits 3.24.3:0

(Table 61) or in the PHY XS register bits 4.24.3:0 (Table 78),

which shows the lane-by-lane Byte Sync status. A failure here,

if not caused by any of the above ‘Loss of Signal’ conditions,

would normally reflect a very high bit error rate, or incorrectly

coded data.

Failure of Lane Synchronization is indicated for the PCS by

register bit 3.24.12 (Table 61) or for the PHY XS by register bit

4.24.12 (Table 78), and can be caused by failure to detect /A/

characters on every lane of a channel, by excessive skew

between /A/s on the lanes of a channel, or by inconsistent

skews.

13

PMA Loopback (1.0.0 & 1.C004.[11:8])

The PMA loopback is implemented from the output of the

TCX[3:0] serializers to the input multiplexers in front of the

RCX[3:0] CDRs. All four lanes are controlled by bit 1.0.0,

while the individual lanes can be controlled (one at a time)

by the 1.C004’h.[11:8] bits. Assuming that this is the only

loopback enabled, and that the BIST and test pattern

generation features are not enabled, the signal flow is from

the RXP[3:0][P/N] pins through almost all the ‘egress’

channel to the input of the (still active) TCX[3:0] output

drivers, then (bypassing the RCX[3:0][P/N] inputs, the

equalizers and LOS detectors) back from the CDRs through

almost all the ‘ingress’ channel to the TXP[3:0][P/N] pins.

BBT3821

www.BDTIC.com/Intersil

FIGURE 4. IEEE AND VENDOR SPECIFIC FAULT AND STATUS REGISTERS (EQUIVALENT SCHEMATIC)

PMA/PMD

SIGNAL

DETECT

level

REG

1.C001.10:8

REG

1.C01D.6

OPRLOS

[3:0]

REG

1.C00A.3:0

CX4

SIGNAL_

DETECT

REG

1.C00A.7:4

PCS

BYTE

SYNC

PCS

LANE

ALIGN

PHY XS

LANE

ALIGN

PHY XS

BYTE

SYNC

TXFAULT

IEEE REG

1.10.4:1

PLL LOCK

FAIL

IEEE REG

1.1.2

IEEE REG

1.10.0

See LASI

IEEE REG

3.1.2

See LASI

IEEE REG

4.1.2

POLARITY

CX4

LX4

CX4

LX4

IEEE REG

3.24.3:0

IEEE REG

3.24.12

IEEE REG

4.24.12

IEEE REG

4.24.3:0

REG

1.C012h.13

IEEE REG

1.8.11

IEEE REG

1.8.10

IEEE REG

3.8.11

IEEE REG

3.8.10

IEEE REG

4.8.11

See LASI

See LASI

See LASI

See LASI

See LASI

IEEE REG

1.1.7

IEEE REG

3.1.7

IEEE REG

4.1.7

REG

3.C001.10:8

level

PHY XS

SIGNAL

DETECT

REG

4.C00A.3:0

PHY XS (Serial) Loopback (4.0.14 & 4.C004.[11:8])

The PHY XS loopback is implemented from the output of the

TXP[3:0] serializers to the input multiplexers in front of the

RXP[3:0] CDRs. All four lanes are controlled by bit 4.0.14,

while the individual lanes can be controlled (one at a time) by

the 4.C004’h.[11:8] bits. Assuming that this is the only

loopback enabled, and that the BIST and test pattern

generation features are not enabled, the signal flow is from

the RCX[3:0][P/N] pins through almost all the ‘ingress’

channel to the input of the (still active) TXP[3:0] output drivers,

then (bypassing the RXP[3:0][P/N] inputs, the equalizers and

LOS detectors) back from the CDRs through almost all the

‘egress’ channel to the TCX[3:0][P/N] pins.

PCS Parallel Network Loopback (3.C004.[3:0])

This loopback is implemented (at the internal XGMII-like level)

from the output of the RXFIFOs in the ‘ingress’ channel to the

input of the TXFIFOs in the ‘egress’ channel. The individual

lanes can be controlled (one at a time) by the 3.C004’h.[3:0]

bits. Assuming that this is the only loopback enabled, and that

the BIST and test pattern generation features are not enabled,

the signal flow is from the RCX[3:0][P/N] pins through the

PMA/PMD and PCS and again PMA/PMD to the

TCX[3:0][P/N] pins. This could also be seen as a ‘short’

loopback at the XGMII input of the PHY XS.

IEEE REG

4.8.10

See LASI

PCS (Parallel) Loopback (4.C004.[3:0] & Optionally

3.0.14)

This loopback is implemented (at the internal XGMII-like level)

from the output of the RXFIFOs in the ‘egress’ channel to the

input of the TXFIFOs in the ‘ingress’ channel. The individual

lanes can be controlled (one at a time) by the 4.C004’h.[3:0]

bits. If the enable bit in 3.C001.7 (Table 64) is set, all four

lanes can be controlled by bit 3.0.14. Since the latter is

specifically excluded by subclause 45.2.3.1.2 of the IEEE

802.3ae-2002 specification for a 10GBASE-X PCS, the

default is to NOT enable this loopback bit, and if it is enabled,

the BBT3821 does not conform to the IEEE specification. A

maintenance request has been submitted to the IEEE to

enable this loopback bit as optional, and to allow a ‘PCS

Loopback Capability’ bit in register bit 3.24.10 (see

http://www.ieee802.org/3/maint/requests/maint_1113.pdf

this has so far been rejected, and may never be approved.

Assuming that this is the only loopback enabled, and that the

BIST and test pattern generation features are not enabled, the

signal flow is from the RXP[3:0][P/N] pins through the full PHY

XS via the internal XGMII to the TXP[3:0][P/N] pins. This

could also be seen as a ‘short’ loopback at the XGMII input of

the PCS.

), but

14

BBT3821

www.BDTIC.com/Intersil

Serial Test Loopbacks (1.C004.12 & 4.C004.12)

In addition to the above loopbacks, the BBT3821 also offers

two serial loopbacks directly between the serial inputs and

outputs. These loopbacks use the recovered clock as the

timing for the outputs (instead of the multiplied reference

clock), so do not reset the jitter or clock domains, and in

addition do NOT provide any pre-emphasis on the outputs.

Furthermore, on the PMA/PMD side (1.C004.12) the lanes

are internally swapped (so the Lane 3 output is from the

Lane 0 input, etc.). Because of their limited utility, they are

not illustrated in Figure 2 or Figure 6. They are mainly useful

for debugging an otherwise intractable system problem. The

reference clock still needs to be within locking range of the

input frequency. The remainder of the signal path will remain

active (as normal), so that if for example 1.C004.12 is set,

data coming in on RCX[3:0], in addition to emerging on

TCX[0:3] without retiming, etc., will also emerge from

TXP[3:0] retimed, as usual.

Serial Management Interface

The nLiten BBT3821 implements the MMD Management

Interface defined in IEEE 802.3-2002 Clauses 22 &

enhanced in IEEE 802.3ae-2002 Clause 45. This two-pin

interface allows serial read/write of the internal control

registers and consists of the MDC clock and MDIO data

terminals. The PADR[4..0] pins are used to select the ‘Port

address’ to which a given nLiten BBT3821 device responds.

The BBT3821 will ignore Clause 22 format frames (on a

frame-by-frame basis), based on the second ST (start) bit

value. The two formats are shown in Table 3, together with

the references to the respective IEEE 802.3 specifications.

MDIO Register Addressing

The PADR[4..0] hardware address pins control the PRTAD

(Port Address) value, each port normally consisting of a

series of MDIO Managed Devices (MMDs). Each Port may

include up to 31 different devices, of which the current

specification defines 8 types, and allows vendor

specification of two others. The BBT3821 device

corresponds to the PMA/PMD, PCS and PHY XGXS defined

types, so responds to DEVAD values of 1, 3 and 4

respectively. The Clause 45-accessible registers are listed

for each Device Address in the tables referenced in Table 2.

Many of these register addresses are IEEE-defined; the

‘Vendor Defined’ registers are arranged to be as DEVAD

independent as possible.

Table 2. DEVAD DEVICE ADDRESS TABLE

REGISTER LIST