Intersil Corporation ACTS20MS Datasheet

April 1995

ACTS20MS

Radiation Hardened

Dual 4-Input NAND Gate

Features

• 1.25 Micron Radiation Hardened SOS CMOS

• Total Dose 300K RAD (Si)

• Single Event Upset (SEU) Immunity

<1 x 10

• SEU LET Threshold >80 MEV-cm

• Dose Rate Upset >10

-10

Errors/Bit-Day (Typ)

11

RAD (Si)/s, 20ns Pulse

2

/mg

• Latch-Up Free Under Any Conditions

o

• Military Temperature Range: -55

C to +125oC

• Significant Power Reduction Compared to ALSTTL Logic

• DC Operating Voltage Range: 4.5V to 5.5V

• Input Logic Levels

- VIL = 0.8V Max

- VIH = VCC/2V Min

• Input Current ≤1µA at VOL, VOH

Description

The Intersil ACTS20MS is a radiation hardened dual 4-input

NAND gate. A low on any input forces the output to a high logic

state.

The ACTS20MS utilizes advanced CMOS/SOS technology to

achieve high-speed operation. This device is a member of the

radiation hardened, high-speed, CMOS/SOS Logic Family.

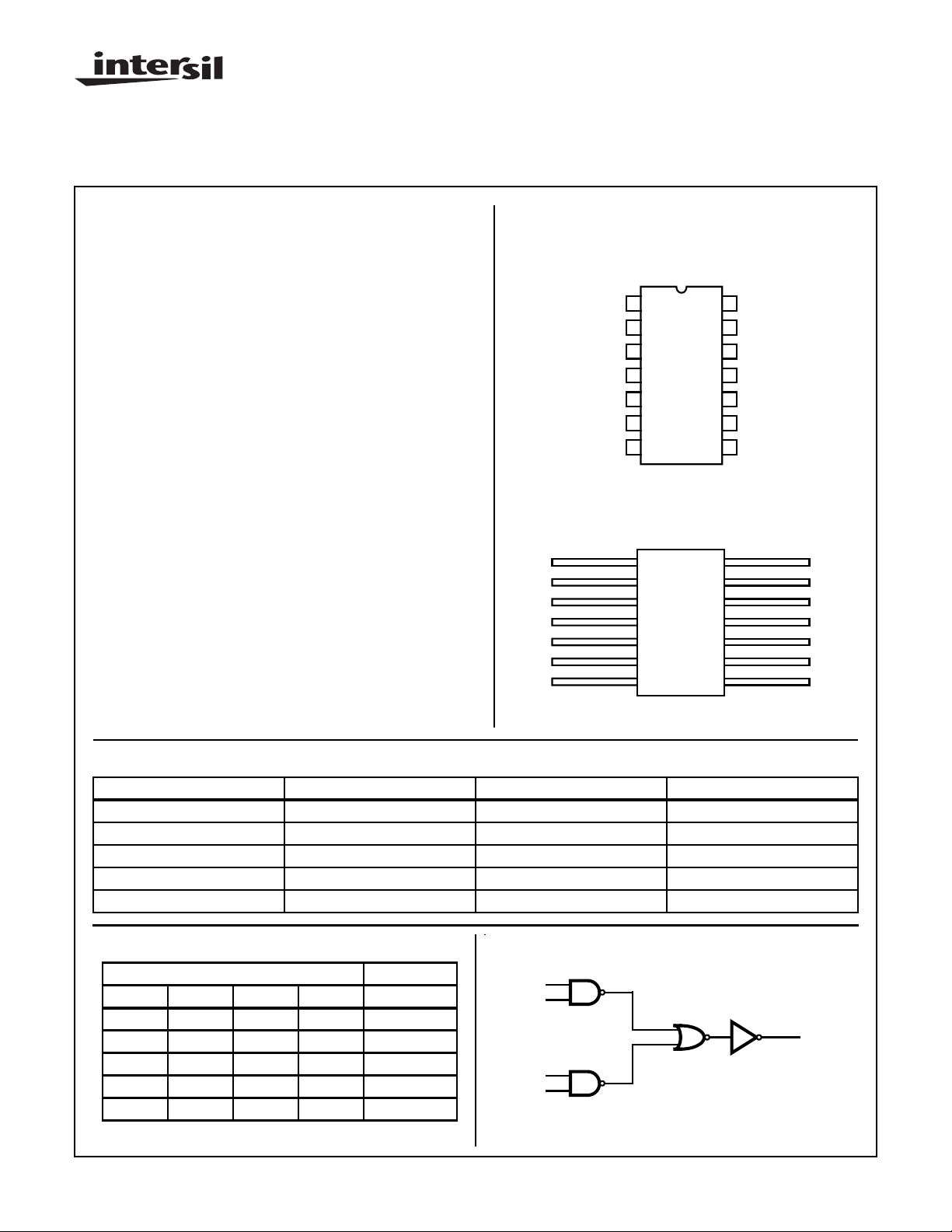

Pinouts

14 LEAD CERAMIC DUAL-IN-LINE

MIL-STD-1835 DESIGNATOR, CDIP2-T14, LEAD FINISH C

TOP VIEW

A1

1

2

B1

3

NC

4

C1

5

D1

6

Y1

7

GND

14 LEAD CERAMIC FLATPACK

MIL-STD-1835 DESIGNATOR, CDFP3-F14, LEAD FINISH C

TOP VIEW

A1

B1

NC

C1

D1

Y1

GND

1

2

3

4

5

6

7

14

VCC

13

D2

12

C2

11

NC

10

B2

9

A2

8

Y2

14

13

12

11

10

9

8

VCC

D2

C2

NC

B2

A2

Y2

Ordering Information

PART NUMBER TEMPERATURE RANGE SCREENING LEVEL PACKAGE

ACTS20DMSR -55oC to +125oC Intersil Class S Equivalent 14 Lead SBDIP

ACTS20KMSR -55oC to +125oC Intersil Class S Equivalent 14 Lead Ceramic Flatpack

ACTS20D/Sample +25oC Sample 14 Lead SBDIP

ACTS20K/Sample +25oC Sample 14 Lead Ceramic Flatpack

ACTS20HMSR +25oC Die Die

Truth Table

INPUTS OUTPUT

An Bn Cn Dn Yn

LXXX H

XLXX H

XXLX H

XXXL H

HHHH L

NOTE: L = Logic Level Low, H = Logic level High, X = Don’t Care

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

| Copyright © Intersil Corporation 1999

Functional Diagram

(1, 9)

An

Bn

(2, 10)

(4, 12)

Cn

Dn

(5, 13)

1

Spec Number 518824

File Number 3611

(6, 8)

Yn

Loading...

Loading...